# **3-Phase Half-Bridge Gate-Drive IC**

# FAN73895

#### Description

The FAN73895 is a monolithic three-phase half-bridge gate-drive IC designed for high-voltage, high-speed, driving MOSFETs and IGBTs operating up to +600 V.

ON Semiconductor's high-voltage process and common-mode noise-canceling technique provide stable operation of high-side drivers under high-dv/dt noise circumstances.

An advanced level-shift circuit allows high-side gate driver operation up to  $V_S = -9.8 V$  (typical) for  $V_{BS} = 15 V$ .

The protection functions include under-voltage lockout and inverter over-current trip with an automatic fault-clear function. Over-current protection that terminates all six outputs can be derived from an external current-sense resistor. An open-drain fault signal is provided to indicate that an over-current or under-voltage shutdown has occurred. The UVLO circuits prevent malfunction when VDD and VBS are lower than the threshold voltage.

Output drivers typically source and sink 350 mA and 650 mA, respectively; which is suitable for three-phase half-bridge applications in motor drive systems.

#### Features

- Floating Channel for Bootstrap Operation to +600 V

- Typically 350 mA/650 mA Sourcing/Sinking Current-Driving Capability for All Channels

- Extended Allowable Negative V<sub>S</sub> Swing to -9.8 V for Signal Propagation at  $V_{DD} = V_{BS} = 15 \text{ V}$

- Output In-Phase with Input Signal

- Over-Current Shutdown Turns Off All Six Drivers

- Matched Propagation Delay for All Channels

- 3.3 V and 5.0 V Input Logic Compatible

- Adjustable Fault-Clear Timing

- Built-in Advanced Input Filter

- Built-in Shoot-Through Prevention Logic

- Built-in Soft Turn-Off Function

- Common-Mode dv/dt Noise-Canceling Circuit

- Built-in UVLO Functions for All Channels

- This is a Pb–Free Device

## **ON Semiconductor®**

www.onsemi.com

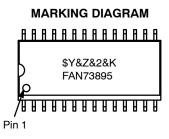

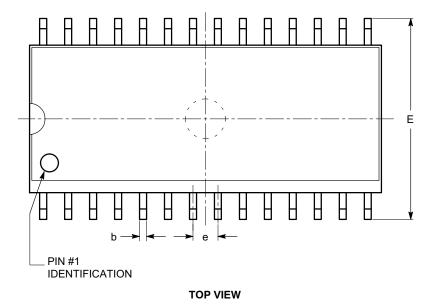

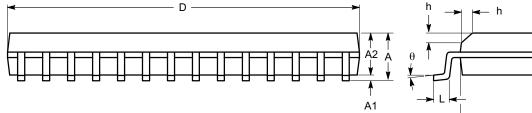

SOIC-28, 300 mils CASE 751BM-01

- FAN73895 = Specific Device Code

- = ON Semiconductor Logo \$Y &Z

- = Assembly Plant Code

- = 2-Digit Date Code Format

- &K = 2-Digits Lot Run Traceability Code

#### Applications

&2

- 3-Phase Motor Inverter Driver

- Air Conditioner, Washing Machine, Refrigerator, Dish Washer

- Industrial Inverter Sewing Machine, Power Tool

- General-Purpose Three-Phase Inverter

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 15 of this data sheet.

| Part                                                      | FAN73893MX                      | FAN73894MX            | FAN73895MX                      | FAN73896MX            |

|-----------------------------------------------------------|---------------------------------|-----------------------|---------------------------------|-----------------------|

| INPUT Type                                                | Inverted                        | Inverted              | Non-inverted                    | Non-inverted          |

| V <sub>DDUV+</sub> / V <sub>BSUV+</sub> (Min / Typ / Max) | 7.5 / 8.5 / 9.3 [V]             | 10.2 / 11.2 / 12 [V]  | 7.5 / 8.5 / 9.3 [V]             | 10.2 / 11.2 / 12 [V]  |

| V <sub>DDUV-</sub> / V <sub>BSUV-</sub> (Min / Typ / Max) | 7 / 8 / 8.7 [V]                 | 9.7 / 10.7 / 11.4 [V] | 7 / 8 / 8.7 [V]                 | 9.7 / 10.7 / 11.4 [V] |

| Note                                                      | (Replacement for<br>FAN73892MX) | _                     | (Replacement for<br>FAN7389MX1) | _                     |

#### Table 1. COMPARISION TABLE

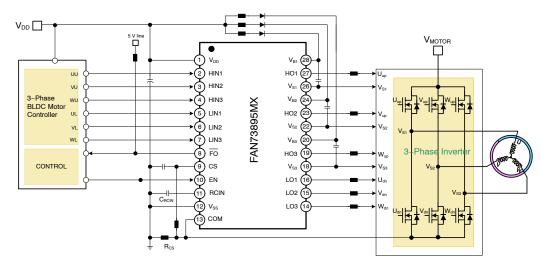

## **TYPICAL APPLICATION DIAGRAM**

Figure 1. 3–Phase BLDC Motor Drive Application

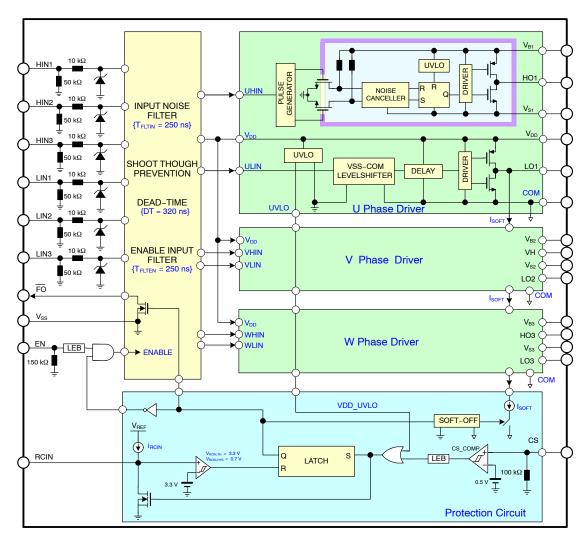

### INTERNAL BLOCK DIAGRAM

Figure 2. Functional Block Diagram

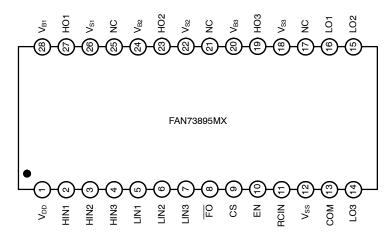

## **PIN CONFIGURATION**

Figure 3. Pin Assignments

## **PIN DEFINITIONS**

| Pin        | Symbol          | Description                                                                      |

|------------|-----------------|----------------------------------------------------------------------------------|

| 1          | V <sub>DD</sub> | Logic and low-side gate driver power supply voltage                              |

| 2          | HIN1            | Logic Input 1 for high-side gate 1 driver                                        |

| 3          | HIN2            | Logic Input 2 for high-side gate 2 driver                                        |

| 4          | HIN3            | Logic Input 3 for high-side gate 3 driver                                        |

| 5          | LIN1            | Logic Input 1 for low-side gate 1 driver                                         |

| 6          | LIN2            | Logic Input 2 for low-side gate 2 driver                                         |

| 7          | LIN3            | Logic Input 3 for low-side gate 3 driver                                         |

| 8          | FO              | Fault output with open drain (indicates over-current and low-side under-voltage) |

| 9          | CS              | Analog input for over-current shutdown                                           |

| 10         | EN              | Logic input for shutdown functionality                                           |

| 11         | RCIN            | An external RC network input used to define the fault-clear delay                |

| 12         | V <sub>SS</sub> | Logic ground                                                                     |

| 13         | COM             | Low-side driver return                                                           |

| 14         | LO3             | Low-side gate driver 3 output                                                    |

| 15         | LO2             | Low-side gate driver 2 output                                                    |

| 16         | LO1             | Low-side gate driver 1 output                                                    |

| 17, 21, 25 | NC              | No connect                                                                       |

| 18         | V <sub>S3</sub> | High-side driver 3 floating supply offset voltage                                |

| 19         | HO3             | High-side driver 3 gate driver output                                            |

| 20         | V <sub>B3</sub> | High-side driver 3 floating supply                                               |

| 22         | V <sub>S2</sub> | High-side driver 2 floating supply offset voltage                                |

| 23         | HO2             | High-side driver 2 gate driver output                                            |

| 24         | V <sub>B2</sub> | High-side driver 2 floating supply                                               |

| 26         | V <sub>S1</sub> | High-side driver 1 floating supply offset voltage                                |

| 27         | HO1             | High-side driver 1 gate driver output                                            |

| 28         | V <sub>B1</sub> | High-side driver 1 floating supply                                               |

| Symbol              | Parameter                                              | Min                       | Мах                       | Unit |

|---------------------|--------------------------------------------------------|---------------------------|---------------------------|------|

| VS                  | High-Side Floating Offset Voltage                      | V <sub>B1,2,3</sub> – 25  | V <sub>B1,2,3</sub> + 0.3 | V    |

| VB                  | High-Side Floating Supply Voltage                      | -0.3                      | 625.0                     | V    |

| $V_{DD}$            | Low-Side and Logic-Fixed supply voltage                | -0.3                      | 25.0                      | V    |

| V <sub>HO</sub>     | High-Side Floating Output Voltage V <sub>HO1,2,3</sub> | V <sub>S1,2,3</sub> – 0.3 | V <sub>B1,2,3</sub> + 0.3 | V    |

| $V_{LO}$            | Low-Side Floating Output Voltage VLO1,2,3              | -0.3                      | V <sub>DD</sub> + 0.3     | V    |

| V <sub>IN</sub>     | Input Voltage (HINx, LINx, CS, and EN) (Note 1)        | -0.3                      | 5.5                       | V    |

| V <sub>FO</sub>     | Fault Output Voltage (FO)                              | -0.3                      | V <sub>DD</sub> + 0.3     | V    |

| dV <sub>S</sub> /dt | Allowable Offset Voltage Slew Rate                     | -                         | ±50                       | V/ns |

| PD                  | Power Dissipation (Note 2, 3)                          | -                         | 1.4                       | W    |

| $\theta_{JA}$       | Thermal Resistance                                     | -                         | 70                        | °C/W |

| TJ                  | Junction Temperature                                   | -                         | 150                       | °C   |

| T <sub>STG</sub>    | Storage Temperature                                    | -55                       | 150                       | °C   |

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise specified)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All input voltage (HINx, LINx, CS, and EN) are referenced to  $V_{SS}$  and do not exceed maximum voltage rating. 2. Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass epoxy material). *Refer to the following standards:*

Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass epoxy material). Refer to the following stand JESD51-2: Integral circuit's thermal test method environmental conditions, natural convection; JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.

3. Do not exceed maximum power dissipation ( $\dot{P}_D$ ) under any circumstances.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol               | Parameter                                   | Min                      | Max                      | Unit |

|----------------------|---------------------------------------------|--------------------------|--------------------------|------|

| V <sub>B1,2,3</sub>  | High-Side Floating Supply Voltage           | V <sub>S1,2,3</sub> + 10 | V <sub>S1,2,3</sub> + 20 | V    |

| V <sub>S1,2,3</sub>  | High-Side Floating Supply Offset Voltage    | 6 – V <sub>DD</sub>      | 600                      | V    |

| $V_{DD}$             | Low-Side and Logic Fixed Supply Voltage     | 10                       | 20                       | V    |

| V <sub>HO1,2,3</sub> | High-Side Output Voltage                    | V <sub>S1,2,3</sub>      | V <sub>B1,2,3</sub>      | V    |

| V <sub>LO1,2,3</sub> | Low-Side Output Voltage                     | COM                      | V <sub>DD</sub>          | V    |

| V <sub>FO</sub>      | Fault Output Voltage (FO)                   | V <sub>SS</sub>          | V <sub>DD</sub>          | V    |

| V <sub>CS</sub>      | Current-Sense Pin Input Voltage             | V <sub>SS</sub>          | 5                        | V    |

| V <sub>IN</sub>      | Logic Input Voltage (HIN1,2,3 and LIN1,2,3) | V <sub>SS</sub>          | 5                        | V    |

| COM                  | Low-Side Driver Return                      | -5                       | 5                        | V    |

| T <sub>A</sub>       | Ambient Temperature                         | -40                      | +125                     | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**ELECTRICAL CHARACTERISTICS** ( $V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS1,2,3}$ ) = 15.0 V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to all six channels. The  $V_O$  and  $I_O$  parameters are referenced to  $V_{S1,2,3}$  and COM and are applicable to the respective output leads: HO1,2,3 and LO1,2,3. The  $V_{DDUV}$  parameters are referenced to  $V_{S1,2,3}$ . The  $V_{BSUV}$  parameters are referenced to  $V_{S1,2,3}$ .

| Symbol             | Parameter                                                               | Condition                                                              | Min | Тур      | Max  | Unit     |

|--------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|-----|----------|------|----------|

| _OW-SIDE           | POWER SUPPLY SECTION                                                    |                                                                        |     |          |      |          |

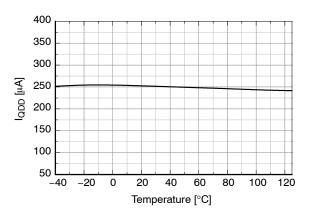

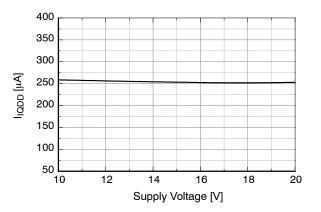

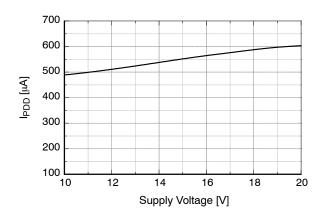

| I <sub>QDD</sub>   | Quiescent V <sub>DD</sub> Supply Current                                | V <sub>LIN1,2,3</sub> = 0 V or 5 V, EN = 0 V                           | -   | 250      | 400  | μA       |

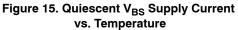

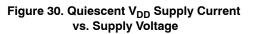

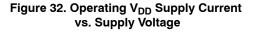

| I <sub>PDD</sub>   | Operating V <sub>DD</sub> Supply Current                                | C <sub>LOAD</sub> = 1 nF, f <sub>LIN1,2,3</sub> = 20 kHz,<br>rms Value | -   | 550      | 750  | μA       |

| $V_{DDUV+}$        | V <sub>DD</sub> Supply Under-Voltage Positive-Going Threshold           | V <sub>DD</sub> = Sweep                                                | 7.5 | 8.5      | 9.3  | V        |

| V <sub>DDUV-</sub> | V <sub>DD</sub> Supply Under–Voltage Negative–Going Threshold           | V <sub>DD</sub> = Sweep                                                | 7.0 | 8.0      | 8.7  | V        |

| V <sub>DDHYS</sub> | V <sub>DD</sub> Supply Under-Voltage Lockout Hysteresis                 | V <sub>DD</sub> = Sweep                                                | -   | 0.5      | -    | V        |

| BOOTSTRA           | APPED POWER SUPPLY SECTION                                              |                                                                        |     |          |      |          |

| $V_{BSUV+}$        | V <sub>BS</sub> Supply Under–Voltage Positive–Going Threshold           | V <sub>BS1,2,3</sub> = Sweep                                           | 7.5 | 8.5      | 9.3  | V        |

| $V_{BSUV-}$        | V <sub>BS</sub> Supply Under–Voltage Negative–Going Threshold           | V <sub>BS1,2,3</sub> = Sweep                                           | 7.0 | 8.0      | 8.7  | V        |

| V <sub>BSHYS</sub> | V <sub>BS</sub> Supply Under-Voltage Lockout Hysteresis                 | V <sub>BS1,2,3</sub> = Sweep                                           | -   | 0.5      | -    | V        |

| I <sub>LK</sub>    | Offset Supply Leakage Current                                           | V <sub>B1,2,3</sub> = V <sub>S1,2,3</sub> = 600 V                      | -   | -        | 10   | μA       |

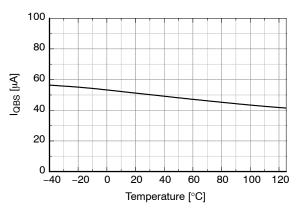

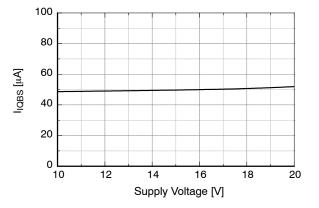

| I <sub>QBS</sub>   | Quiescent V <sub>BS</sub> Supply Current                                | $V_{HIN1,2,3} = 0 V \text{ or } 5 V, EN = 0 V$                         | 10  | 50       | 80   | μA       |

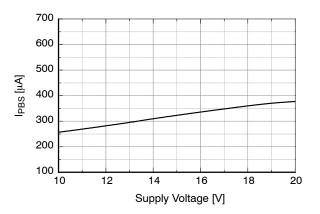

| I <sub>PBS</sub>   | Operating V <sub>BS</sub> Supply Current                                | C <sub>LOAD</sub> = 1 nF, f <sub>HIN1,2,3</sub> = 20 kHz,<br>rms Value | 200 | 320      | 480  | μA       |

| GATE DRIV          | ER OUTPUT SECTION                                                       |                                                                        |     |          |      |          |

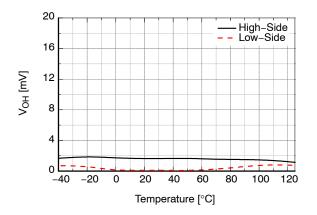

| V <sub>OH</sub>    | High-Level Output Voltage, V <sub>BIAS</sub> - V <sub>O</sub>           | I <sub>O</sub> = 0 mA (No Load)                                        | -   | -        | 100  | mV       |

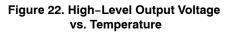

| V <sub>OL</sub>    | Low-Level Output Voltage, VO                                            | I <sub>O</sub> = 0 mA (No Load)                                        | -   | -        | 100  | mV       |

| I <sub>O+</sub>    | Output HIGH Short-Circuit Pulse Current (Note 4)                        | $V_O$ = 15 V, $V_{IN}$ = 0 V with PW $\leq$ 10 $\mu s$                 | 250 | 350      | -    | mA       |

| I <sub>O-</sub>    | Output LOW Short-Circuit Pulsed Current (Note 4)                        | $V_{O}$ = 0 V, $V_{IN}$ = 5 V with PW $\leq$ 10 $\mu s$                | 500 | 650      | -    | mA       |

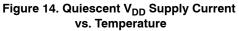

| $V_{S}$            | Allowable Negative $V_{S}$ Pin Voltage for HIN Signal Propagation to HO |                                                                        | -   | -9.8     | -9.0 | V        |

|                    | UT SECTION                                                              |                                                                        |     |          |      |          |

| V <sub>IH</sub>    | Logic "1" Input Voltage HIN1,2,3, LIN1,2,3                              |                                                                        | 2.5 | -        | -    | V        |

| VIL                | Logic "0" Input Voltage HIN1,2,3, LIN1,2,3                              |                                                                        | -   | -        | 0.8  | V        |

| I <sub>IN+</sub>   | Logic Input Bias Current (HO = LO = HIGH)                               | V <sub>IN</sub> = 5 V                                                  | 77  | 100      | 143  | μA       |

| I <sub>IN-</sub>   | Logic Input Bias Current (HO = LO = LOW)                                | V <sub>IN</sub> = 0 V                                                  | -   | -        | 2    | μA       |

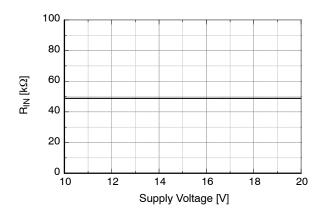

| R <sub>IN</sub>    | Logic Input Pull-Up Resistance                                          |                                                                        | 35  | 50       | 65   | kΩ       |

| ENABLE C           | ONTROL SECTION (EN)                                                     |                                                                        |     |          |      |          |

| $V_{\text{EN+}}$   | Enable Positive-Going Threshold Voltage                                 |                                                                        | 2.5 | -        | -    | V        |

| $V_{EN-}$          | Enable Negative-Going Threshold Voltage                                 |                                                                        | -   | -        | 0.8  | V        |

| I <sub>EN+</sub>   | Logic Enable "1" Input Bias Current                                     | V <sub>EN</sub> = 5 V (Pull–Down = 150 kΩ)                             | 15  | 33       | 50   | μA       |

| I <sub>EN-</sub>   | Logic Enable "0" Input Bias Current                                     | V <sub>EN</sub> = 0 V                                                  | _   | -        | 2    | μA       |

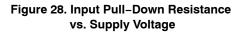

| R <sub>EN</sub>    | Logic Input Pull-Down Resistance                                        |                                                                        | 100 | 150      | 333  | kΩ       |

|                    | RENT PROTECTION SECTION                                                 | 1                                                                      |     | <u>n</u> |      | <u> </u> |

| V <sub>CSTH+</sub> | Over-Current Detect Positive Threshold                                  |                                                                        | 450 | 500      | 550  | mV       |

| V <sub>CSTH-</sub> | Over-Current Detect Negative Threshold                                  |                                                                        | -   | 440      | -    | mV       |

| V <sub>CSHYS</sub> | Over-Current Detect Hysteresis                                          |                                                                        | _   | 60       | -    | mV       |

| I <sub>CSIN</sub>  | Short-Circuit Input Current                                             | V <sub>CSIN</sub> = 1 V                                                | 5   | 10       | 15   | μA       |

| I <sub>SOFT</sub>  | Soft Turn-Off Sink Current                                              |                                                                        | 25  | 40       | 55   | mA       |

**ELECTRICAL CHARACTERISTICS** ( $V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS1,2,3}$ ) = 15.0 V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to  $V_{SS}$  and are applicable to all six channels. The  $V_O$  and  $I_O$  parameters are referenced to  $V_{S1,2,3}$  and COM and are applicable to the respective output leads: HO1,2,3 and LO1,2,3. The  $V_{DDUV}$  parameters are referenced to  $V_{SS}$ . The  $V_{BSUV}$  parameters are referenced to  $V_{S1,2,3}$ . (continued)

| Symbol               | Parameter                                      | Condition                                       | Min | Тур | Max | Unit |  |  |

|----------------------|------------------------------------------------|-------------------------------------------------|-----|-----|-----|------|--|--|

| FAULT OUT            | AULT OUTPUT SECTION                            |                                                 |     |     |     |      |  |  |

| V <sub>RCINTH+</sub> | RCIN Positive-Going Threshold Voltage          |                                                 | 2.7 | 3.3 | 3.9 | V    |  |  |

| V <sub>RCINTH-</sub> | RCIN Negative-Going Threshold Voltage (Note 4) |                                                 | -   | 2.6 | -   | V    |  |  |

| V <sub>RCINHYS</sub> | RCIN Hysteresis Voltage (Note 4)               |                                                 | -   | 0.7 | -   | V    |  |  |

| I <sub>RCIN</sub>    | RCIN Internal Current Source                   | C <sub>RCIN</sub> = 2 nF                        | 3   | 5   | 7   | μΑ   |  |  |

| V <sub>FOL</sub>     | Fault Output Low Level Voltage                 | V <sub>CS</sub> = 1 V, I <sub>FO</sub> = 1.5 mA | -   | 0.2 | 0.5 | V    |  |  |

| R <sub>DSRCIN</sub>  | RCIN On Resistance                             | I <sub>RCIN</sub> = 1.5 mA                      | 50  | 75  | 100 | Ω    |  |  |

| R <sub>DSFO</sub>    | Fault Output On Resistance                     | I <sub>FO</sub> = 1.5 mA                        | 90  | 130 | 170 | Ω    |  |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. These parameters are guaranteed by design.

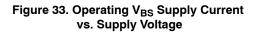

**DYNAMIC ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ ,  $V_{BIAS}$  ( $V_{DD}$ ,  $V_{BS1,2,3}$ ) = 15.0 V,  $V_{S1,2,3} = COM$ ,  $C_{RCIN} = 2$  nF, and  $C_{Load} = 1000$  pF unless otherwise specified.)

| Symbol              | Parameter                                                    | Condition                                                                      | Min | Тур  | Max  | Unit |

|---------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|-----|------|------|------|

| t <sub>ON</sub>     | Turn-On Propagation Delay                                    | V <sub>LIN1,2,3</sub> = V <sub>HIN1,2,3</sub> = 5 V, V <sub>S1,2,3</sub> = 0 V | 350 | 500  | 650  | ns   |

| t <sub>OFF</sub>    | Turn-Off Propagation Delay                                   | V <sub>LIN1,2,3</sub> = V <sub>HIN1,2,3</sub> = 0 V, V <sub>S1,2,3</sub> = 0 V | 350 | 500  | 650  | ns   |

| t <sub>R</sub>      | Turn-On Rise Time                                            | V <sub>LIN1,2,3</sub> = V <sub>HIN1,2,3</sub> = 5 V                            | 20  | 50   | 100  | ns   |

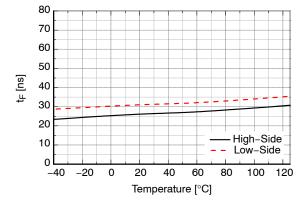

| t <sub>F</sub>      | Turn-Off Fall Time                                           | V <sub>LIN1,2,3</sub> = V <sub>HIN1,2,3</sub> = 0 V                            | 10  | 30   | 80   | ns   |

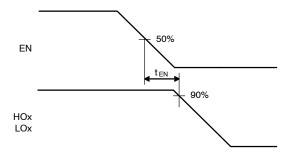

| t <sub>EN</sub>     | Enable LOW to Output Shutdown Delay                          |                                                                                | 400 | 500  | 600  | ns   |

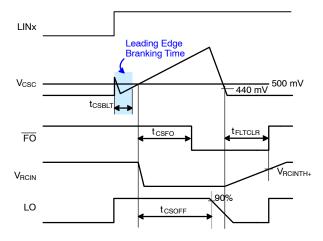

| t <sub>CSBLT</sub>  | CS Pin Leading-Edge Blanking Time                            |                                                                                | 400 | 650  | 850  | ns   |

| t <sub>CSFO</sub>   | Time from CS Triggering to FO                                | From $V_{CSC} = 1 V$ to FO Turn–Off                                            | -   | 850  | 1300 | ns   |

| t <sub>CSOFF</sub>  | Time from CS Triggering to Low–Side Gate<br>Outputs Turn–Off | From V <sub>CSC</sub> = 1 V to Starting Gate<br>Turn-Off                       | -   | 850  | 1300 | ns   |

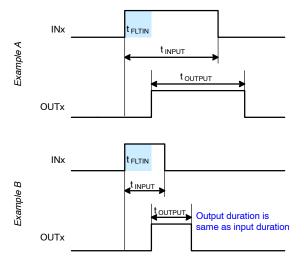

| t <sub>FLTIN</sub>  | Input Filtering Time (Note 5) (HINx, LINx, EN)               |                                                                                | 170 | 250  | 330  | ns   |

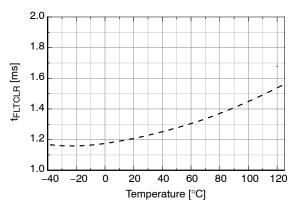

| t <sub>FLTCLR</sub> | Fault-Clear Time                                             |                                                                                | -   | 1.30 | 2.35 | ms   |

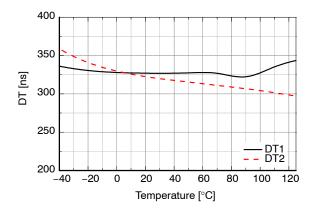

| DT                  | Dead Time                                                    |                                                                                | 230 | 320  | 400  | ns   |

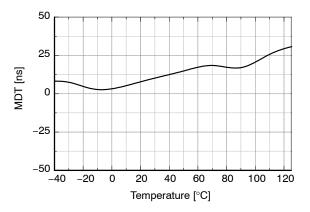

| MDT                 | Dead-Time Matching (All Six Channels) (Note 6)               |                                                                                | -   | -    | 50   | ns   |

| MT                  | Delay Matching (All Six Channels) (Note 7)                   |                                                                                | -   | -    | 50   | ns   |

| PM                  | Output Pulse-Width Matching (Note 8)                         | PW <sub>IN</sub> > 1 μs                                                        | -   | 50   | 100  | ns   |

5. The minimum width of the input pulse should exceed 500 ns to ensure the filtering time of the input filter is exceeded.

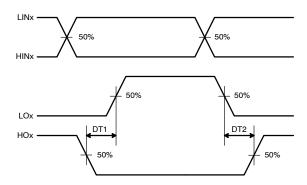

6. MDT is defined as | DT1-DT2 | referenced to Figure 37.

7. MT is defined as an absolute value of matching delay time between High-side and Low-side.

8. PM is defined as an absolute value of matching pulse-width between Input and Output.

## **TYPICAL CHARACTERISTICS**

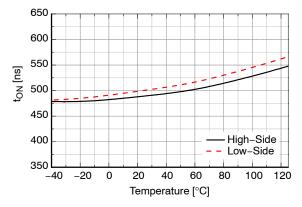

Figure 4. Turn–On Propagation Delay vs. Temperature

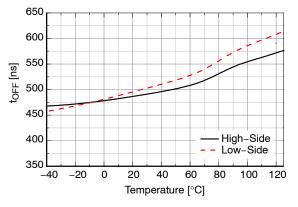

Figure 5. Turn-Off Propagation Delay vs. Temperature

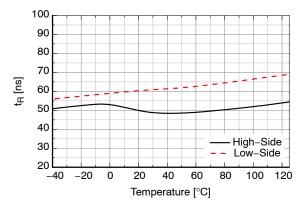

Figure 6. Turn–On Rise Time vs. Temperature

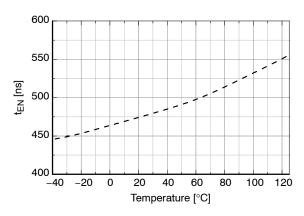

Figure 8. Enable LOW to Output Shutdown Delay vs. Temperature

Figure 7. Turn-Off Fall Time vs. Temperature

Figure 9. Fault-Clear Time vs. Temperature

Figure 10. Dead Time vs. Temperature

Figure 11. Dead-Time Matching vs. Temperature

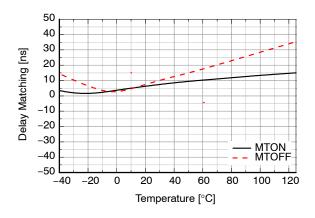

Figure 12. Delay Matching vs. Temperature

Figure 13. Allowable Negative V<sub>S</sub> Voltage vs. Temperature

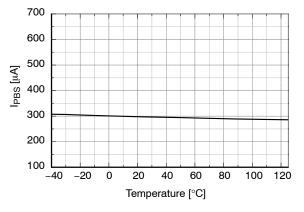

Figure 17. Operating V<sub>BS</sub> Supply Current vs. Temperature

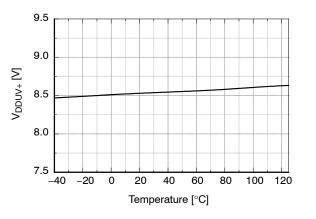

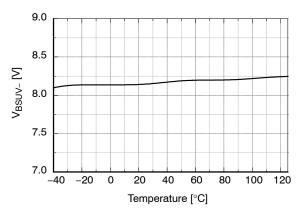

Figure 18. V<sub>DD</sub> UVLO+ vs. Temperature

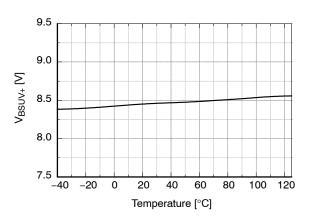

Figure 20. V<sub>BS</sub> UVLO+ vs. Temperature

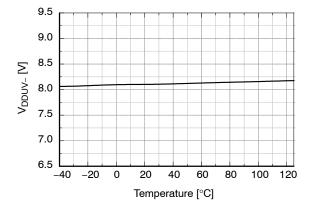

Figure 19. V<sub>DD</sub> UVLO- vs. Temperature

Figure 21.  $V_{BS}$  UVLO– vs. Temperature

Figure 23. Low-Level Output Voltage vs. Temperature

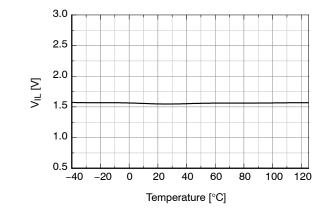

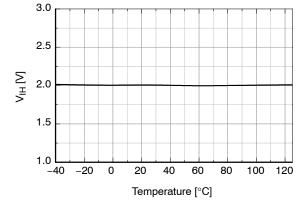

Figure 25. Logic LOW Input Voltage vs. Temperature

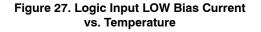

Figure 24. Logic HIGH Input Voltage vs. Temperature

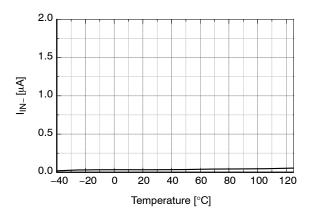

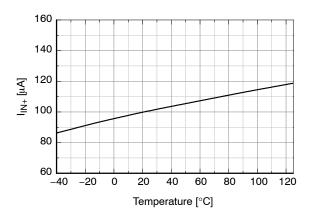

Figure 26. Logic Input HIGH Bias Current vs. Temperature

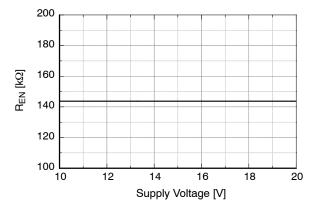

Figure 29. Enable Pin Pull–Down Resistance vs. Supply Voltage

Figure 31. Quiescent V<sub>BS</sub> Supply Current vs. Supply Voltage

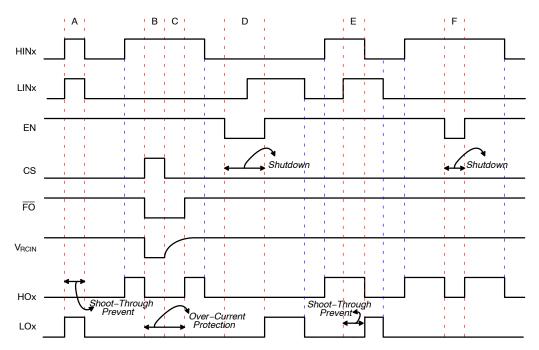

### SWITCHING TIME DEFINITIONS

#### APPLICATIONS INFORMATION

#### **Dead Time**

Dead time is automatically inserted whenever the dead time of the external two input signals (between HINx and LINx signals) is shorter than internal fixed dead times (DT1 and DT2). Otherwise, external dead times larger than internal dead times are not modified by the gate driver and internal dead-time waveform definition is shown in Figure 37.

Figure 37. Internal Dead-Time Definitions

#### **Protection Function**

#### Fault Out (FO) and Under-Voltage Lockout

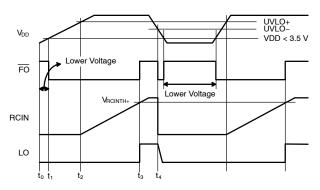

The high- and low-side drivers include under-voltage lockout (UVLO) protection circuitry that monitors the supply voltage for  $V_{DD}$  and  $V_{BS}$  independently. It can be designed to prevent malfunction when  $V_{DD}$  and  $V_{BS}$  are lower than the specified threshold voltage. The UVLO hysteresis prevents chattering during power-supply transitions. Moreover, the fault signal (power supply voltage  $\overline{FO}$ ) goes to LOW state to operate reliably during power-on events when the power supply ( $V_{DD}$ ) is below the under-voltage lockout high threshold voltage for the circuit (during  $t_1$ - $t_2$ ). The UVLO circuit is not otherwise activated; shown Figure 38. If VDD is lower than 3.5 V, the fault signal cannot be driven to LOW state because VDD is not enough to drive internal circuit.

Figure 38. Waveforms for Under-Voltage Lockout

#### Shoot-Through Protection

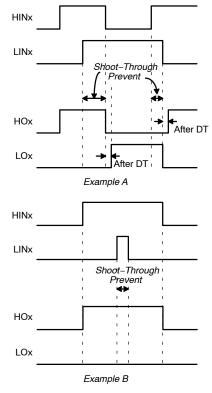

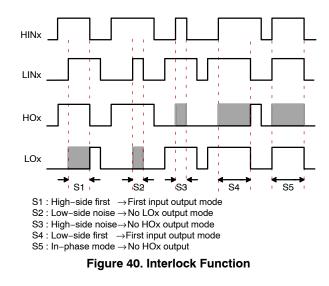

The shoot-through protection circuitry prevents both high- and low-side switches from conducting at the same time, as shown Figure 39.

Figure 39. Shoot-Through Protection

An interlock function is a device used to prevent both high– and low–side switches from conducting at the same time as shown Figure 40. In most applications an interlock is used to help prevent a device from harming its operator or damaging itself by when two input signals of a same leg are activated simultaneously, only one output is activated.

#### Enable Input

When the EN pin is in HIGH state, the gate driver operates normally. When a condition occurs that should shut down the gate driver, the EN pin should be LOW. The enable circuitry has an input filter; the minimum input duration is specified by  $t_{FLTIN}$  (typically 250 ns).

Figure 41. Output Enable Timing Waveform

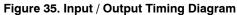

#### Fault-Out (FO) and Over-Current Protection

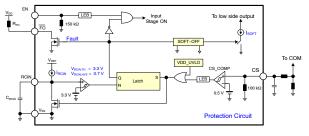

FAN73895 provides an integrated fault output ( $\overline{FO}$ ) and an adjustable fault–clear timer (t<sub>FLTCLR</sub>). There are two situations that cause the gate driver to report a fault via the  $\overline{FO}$  pin. The first is an under–voltage condition of low–side gate driver supply voltage (V<sub>DD</sub>) and the second is when the current–sense pin (CS) recognizes a fault. If a fault condition occurs, the  $\overline{FO}$  pin is internally pulled to COM, the fault–clear timer is activated, and all outputs (HO1, 2, 3 and LO1, 2, 3) of the gate driver are turned off. The fault output stays LOW until the fault condition has been removed and the fault–clear timer expires. Once the fault–clear timer expires, the voltage on the  $\overline{FO}$  pin returns to pull–up voltage.

The fault-clear time  $(t_{FLTCLR})$  is determined by an internal current source  $(I_{RCIN} = 5 \ \mu A)$  and an external  $C_{RCIN}$  at the RCIN pin, as shown as:

$$t_{FLTCLR} = \frac{C_{RCIN} \times V_{RCIN,TH}}{I_{RCIN}} \text{ [s]} \tag{eq. 1}$$

The  $R_{DSRCIN}$  of the MOSFET is a characteristic discharge curve with respect to the external capacitor  $C_{RCIN}$ . The time constant is defined by the external capacitor  $C_{RCIN}$  and the  $R_{DSRCIN}$  of the MOSFET.

The output of current-sense comparator (CS\_COMP) passes a noise filter, which inhibits an over-current shutdown caused by parasitic voltage spikes of  $V_{CS}$ .

This corresponds to a voltage level at the comparator of  $V_{CSTH+} - V_{CSHYS} = 500 \text{ mV} - 60 \text{ mV} = 440 \text{ mV}$ , where  $V_{CSHYS} = 60 \text{ mV}$  is the hysteresis of the current comparator (CS\_COMP), as shown in Figure 42.

Figure 42. Over–Current Protection

Figure 43 shows the waveform definitions of RCIN,  $\overline{FO}$ , and the low-side driver; which uses a soft turn-off method when an under-voltage condition of the low-side gate driver supply voltage (V<sub>DD</sub>) or the current-sense pin (CS) recognizes a fault. If a fault condition occurs, the  $\overline{FO}$  Pin is internally pulled to COM and all outputs (HO1, 2, 3 and LO1, 2, 3) of the gate driver are turned off. Low-side outputs decline linearly by the internal sink current source (I<sub>SOFT</sub> = 40 mA) for soft turn-off, as shown in Figure 43.

Figure 43. R<sub>CIN</sub> and Fault–Clear Waveform Definition

#### **Noise Filter**

#### Input Noise Filter

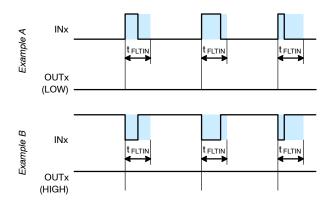

Figure 44 shows the input noise filter method, which has symmetry duration between the input signal ( $t_{INPUT}$ ) and the output signal ( $t_{OUTPUT}$ ) and helps to reject noise spikes and short pulses. This input filter is applied to the HINx, LINx, and EN inputs. The upper pair of waveforms (Example A) shows input signal duration ( $t_{INPUT}$ ) much longer than input filter time ( $t_{FLTIN}$ ); it is approximately the same duration between the input signal time ( $t_{INPUT}$ ) and the output signal time ( $t_{OUTPUT}$ ). The lower pair of waveforms (Example B) shows an input signal time ( $t_{INPUT}$ ) slightly longer than input filter time ( $t_{FLTIN}$ ); it is approximately the same duration between input signal time ( $t_{INPUT}$ ) and the output signal time ( $t_{OUTPUT}$ ).

Figure 44. Input Noise Filter Definition

Short-Pulsed Input Noise Rejection Method

The input filter circuitry provides protection against short–pulsed input signals (HINx, LINx and EN) on the input signal lines by applied noise signal.

If the input signal duration is less than input filter time (t<sub>FLTIN</sub>), the output does not change states.

Example A and B of the Figure 45 show the input and output waveforms with short–pulsed noise spikes with a duration less than input filter time; the output does not change states.

Figure 45. Noise Rejecting Input Filter Definition

#### **ORDERING INFORMATION**

| Part Number         | Package                                                           | Operating Temperature | Shipping <sup>†</sup> |

|---------------------|-------------------------------------------------------------------|-----------------------|-----------------------|

| FAN73895MX (Note 9) | 28–Lead, Small Outline<br>Integrated Circuit, (SOIC)<br>(Pb–Free) | -40 to +125°C         | 1000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

9. These devices passed wave-soldering test by JESD22A-111.

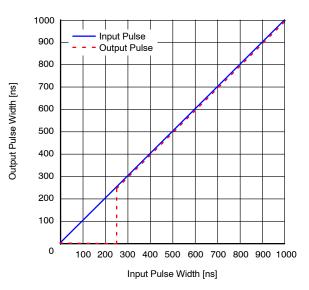

Figure 46 shows the characteristics of the input filters while receiving narrow ON and OFF pulses. If input signal pulse duration,  $PW_{IN}$ , is less than input filter time,  $t_{FLTIN}$ ; the output pulse,  $PW_{OUT}$ , is zero. The input signal is rejected by input filter. Once the input signal pulse duration,  $PW_{IN}$ , exceeds input filter time,  $t_{FLTIN}$ , the output pulse durations,  $PW_{OUT}$ , matches the input pulse durations,  $PW_{IN}$ . FAN73895 input filter time,  $t_{FLTIN}$ , is about 250 ns for the high– and low–side outputs.

Figure 46. Input Filter Characteristic of Narrow ON

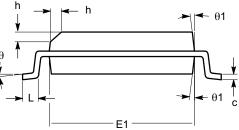

SOIC-28, 300 mils CASE 751BM-01 ISSUE O

DATE 19 DEC 2008

| SYMBOL | MIN   | NOM      | MAX   |

|--------|-------|----------|-------|

| A      | 2.35  |          | 2.65  |

| A1     | 0.10  |          | 0.30  |

| A2     | 2.05  |          | 2.55  |

| b      | 0.31  |          | 0.51  |

| с      | 0.20  |          | 0.33  |

| D      | 17.78 |          | 18.03 |

| E      | 10.11 |          | 10.51 |

| E1     | 7.34  |          | 7.60  |

| е      |       | 1.27 BSC |       |

| h      | 0.25  |          | 0.75  |

| L      | 0.40  |          | 1.27  |

| θ      | 0°    |          | 8°    |

| θ1     | 5°    |          | 15°   |

SIDE VIEW

END VIEW

## Notes:

All dimensions are in millimeters. Angles in degrees.

Complies with JEDEC MS-013.

| DOCUMENT NUMBER:                                                                  | 98AON34296E                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                             |                                                     |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| DESCRIPTION:                                                                      | SOIC-28, 300 MILS PAGE                                                                      |                                                                                                                                                                                                                                                                                                                |                                                     |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>incidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>circuit, and specifically |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Onsemi: FAN73895MX