# Dual-Phase Synchronous Boost Controller with Programmable Gate Drive and I<sup>2</sup>C

#### **General Description**

The MAX25203 automotive dual-phase synchronous boost controller enables infotainment systems to stay in regulation during cold-crank or start-stop operation all the way down to a battery input of 1.8V. It can also be used to generate backlight voltage and Class D audio amplifier voltages. This device can start with an input voltage supply from 4.5V to 42V and can operate down to 1.8V after start-up, and has a low 5µA shutdown supply current.

The MAX25203 operates at up to 2.1MHz frequency to allow small external components and reduced output ripple, and to guarantee no AM band interference. The switching frequency is resistor adjustable (220kHz to 2100kHz) or it can be synchronized on-the-fly to an external clock.

The MAX25203 has a spread-spectrum option for frequency modulation to minimize EMI interference. A 90° out-of-phase clock output enables synchronizing a second MAX25203 for quad-phase operation.

Pass-through operation has over 98% efficiency when the supply voltage exceeds the output regulation voltage. Programmable current-limit blanking handles high peak loads without oversizing the inductor.

The MAX25203 features a power-OK monitor and undervoltage lockout. Protection features include cycle-by-cycle current limit and thermal shutdown. It operates over the -40°C to +125°C automotive temperature range.

## **Applications**

- Infotainment Systems

- Automotive Audio Amplifier

#### **Benefits and Features**

- Meets Stringent OEM Module Power Consumption and Performance Specifications

- · ±1.5% Output-Voltage Accuracy at FB

- Output Voltage Adjustable Between 12V and 65V (70V Abs Max)

- 5µA Shutdown Supply Current

- · High Efficiency and Current Sharing

- Pass-Through for >98% Efficiency

- OTP Gate Drive Voltage from 6.5V to 10V Allows User to Optimize External MOSFETs and Improve Efficiency

- Current Sharing Accuracy of ±5% Between Phases to Improve System Efficiency

- Programmable Current-Limit Blanking Handles High Peak Loads without Oversizing Inductor

- EMI-Reduction Features Reduce Interference with Sensitive Radio Bands without Sacrificing Wide Input Voltage Range

- · Spread-Spectrum Option

- · On-the-Fly Frequency-Synchronization Input

- Resistor-Programmable Frequency between 220kHz and 2.1MHz

- Synchronization Output Provides 90° Out-of-Phase Clock for Quad-Phase Operation

- Integration and Thermally Enhanced Package Saves Board Space and Cost

- Current-Mode Controllers with Forced-Continuous and Skip Modes

- · Side-Wettable, 32-Pin TQFN-EP Package

- Protection Features and I<sup>2</sup>C Diagnostics for Improved System Reliability

- · Supply Undervoltage Lockout

- Die Temperature Monitoring through I<sup>2</sup>C

- Short-Circuit Protection with True Shutdown<sup>TM</sup>

- Individual Phase Current Monitoring through I<sup>2</sup>C

Ordering Information appears at end of data sheet.

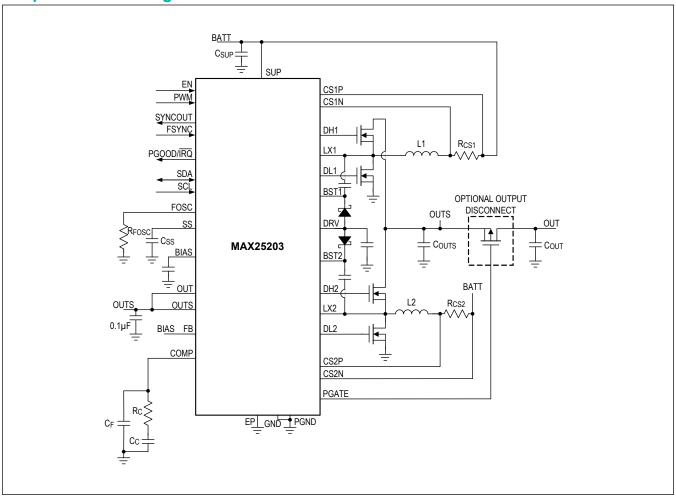

## **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| General Description                                    |    |

|--------------------------------------------------------|----|

| Applications                                           | 1  |

| Benefits and Features                                  | 1  |

| Simplified Block Diagram                               |    |

| Absolute Maximum Ratings                               | 6  |

| Recommended Operating Conditions                       | 6  |

| Package Information                                    | 6  |

| SW-TQFN                                                | 6  |

| Electrical Characteristics                             | 7  |

| Electrical Characteristics—MAX25203Q                   |    |

| Typical Operating Characteristics                      |    |

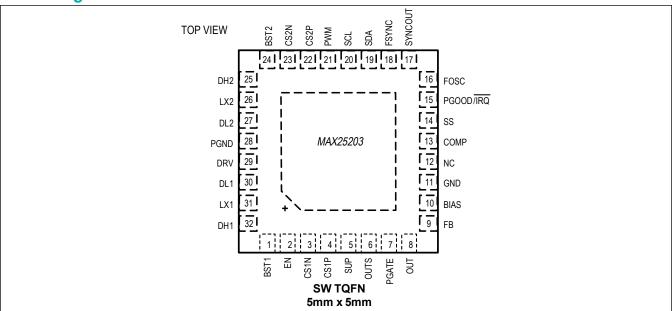

| Pin Configuration                                      | 13 |

| Pin Description                                        |    |

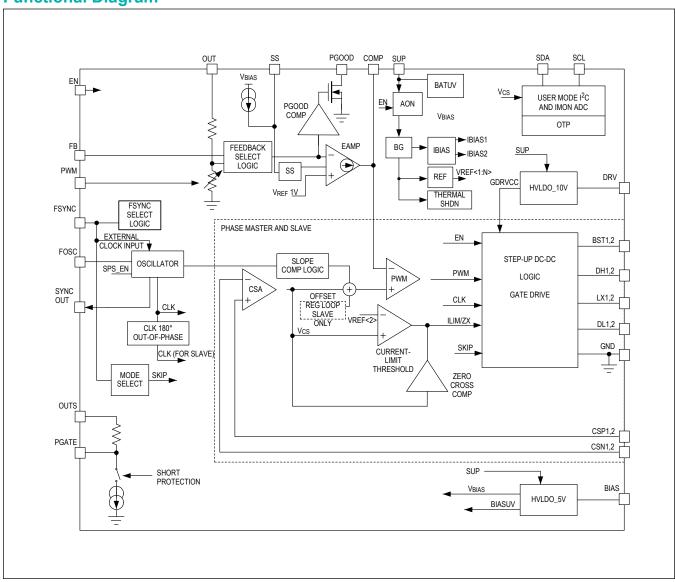

| Functional Diagram                                     |    |

| Detailed Description                                   | 17 |

| Current-Mode Control Loop                              | 17 |

| Fixed 5V Linear Regulator (BIAS)                       | 17 |

| Gate Drive LDO (DRV)                                   | 17 |

| Start-Up Operation/UVLO/EN                             | 17 |

| Soft-Start                                             | 18 |

| Oscillator Frequency/External Synchronization          | 18 |

| Pass-Through                                           | 18 |

| Spread Spectrum                                        |    |

| MOSFET Drivers (DH and DL)                             | 18 |

| High-Side Gate-Driver Supply (BST)                     | 18 |

| p-Channel MOSFET Output Disconnect                     |    |

| Current Limiting and Current-Sense Inputs (SUP and CS) |    |

| Output Voltage Monitor (PGOOD)                         |    |

| Interrupt Request Output (IRQ)                         |    |

| Protection Features                                    |    |

| I <sup>2</sup> C Fault Flags                           |    |

| Overvoltage Protection                                 | 20 |

| Overcurrent Protection                                 | 20 |

| Thermal-Overload Protection                            | 20 |

| I <sup>2</sup> C Interface                             | 20 |

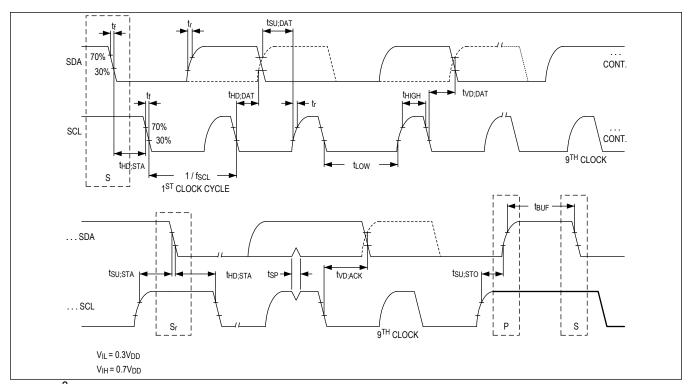

| I <sup>2</sup> C Timing Diagram                        | 20 |

| Bit Transfer                                           | 21 |

| START and STOP Conditions                              | 21 |

| Clock Stretching                                       | 21 |

www.maximintegrated.com

## TABLE OF CONTENTS (CONTINUED)

|                                                         | <u> </u> |          |

|---------------------------------------------------------|----------|----------|

| Slave Address                                           |          | <br>21   |

| Acknowledge                                             |          | <br>. 21 |

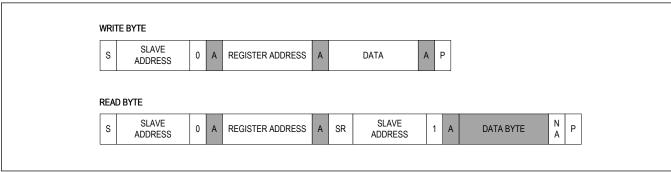

| Write Data Format                                       |          | <br>. 21 |

| Read Data Format                                        |          | <br>. 21 |

| I <sup>2</sup> C Data Format                            |          | <br>. 22 |

| Register Map                                            |          | <br>23   |

| MAX25203                                                |          | <br>23   |

| Register Details                                        |          | <br>23   |

| Applications Information                                |          | <br>. 27 |

| Setting and Controlling the Output Voltage              |          | <br>. 27 |

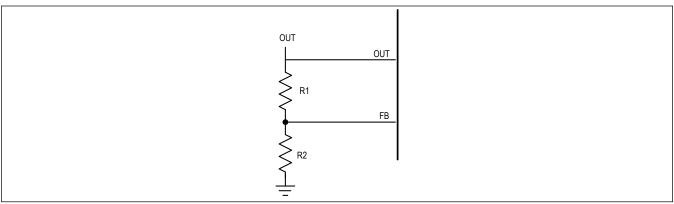

| External Feedback Divider                               |          | <br>. 27 |

| I <sup>2</sup> C Voltage Setting                        |          | <br>. 27 |

| PWM Voltage Control                                     |          | <br>. 27 |

| Inductor Selection                                      |          | <br>. 28 |

| Input Capacitor Selection                               |          | <br>. 28 |

| Output Capacitor Selection                              |          | <br>. 29 |

| Current-Sense Resistor Selection                        |          | <br>. 29 |

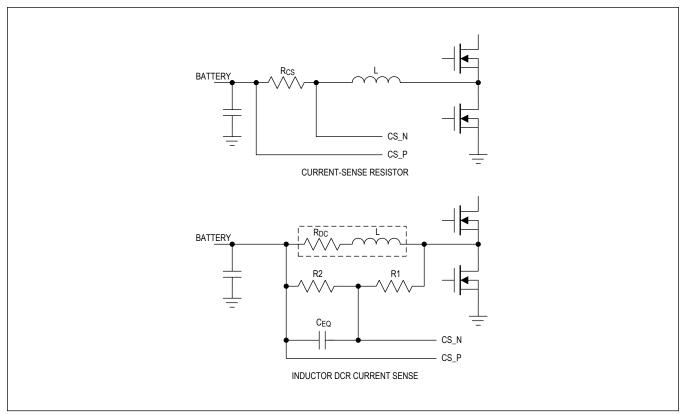

| Current-Sense Configurations                            |          | <br>. 30 |

| Inductor DCR Current Sense                              |          | <br>. 30 |

| Boost Converter Compensation                            |          | <br>. 30 |

| MOSFET Selection                                        |          | <br>. 32 |

| Threshold Voltage                                       |          | <br>. 32 |

| Maximum Drain-to-Source Voltage (V <sub>DS(MAX)</sub> ) |          | <br>. 32 |

| Current Capability                                      |          | <br>. 32 |

| Low-Voltage Operation                                   |          | <br>. 32 |

| Quad-Phase Operation                                    |          | <br>. 32 |

| Layout Recommendations                                  |          | <br>. 33 |

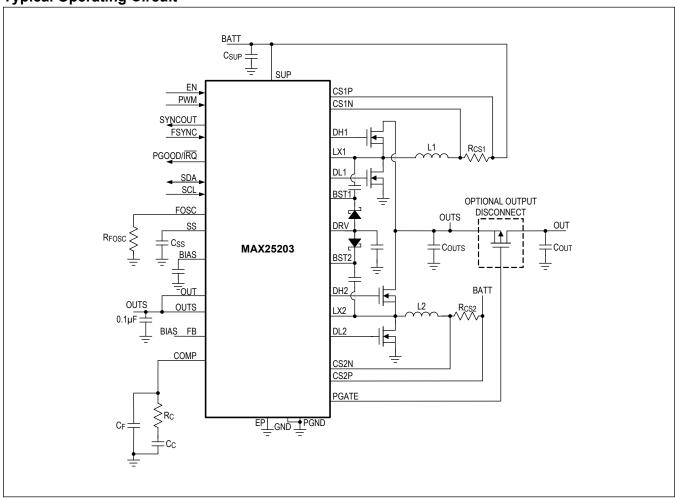

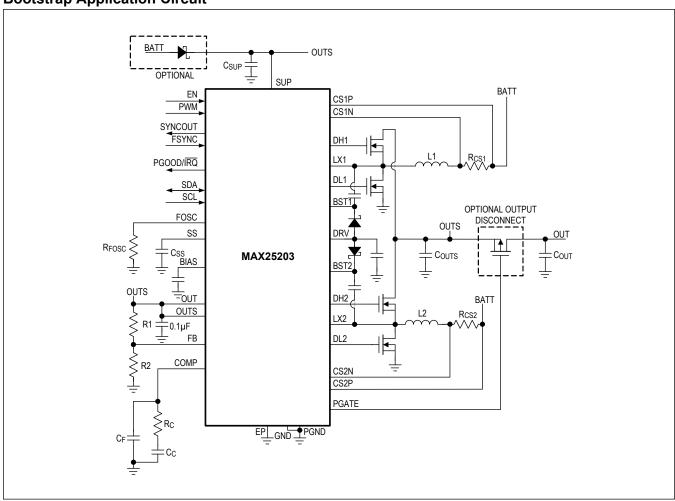

| Typical Application Circuits                            |          | <br>. 33 |

| Typical Operating Circuit                               |          | <br>. 33 |

| Bootstrap Application Circuit                           |          | <br>34   |

| Ordering Information                                    |          | <br>. 35 |

| Revision History                                        |          | <br>. 36 |

# Dual-Phase Synchronous Boost Controller with Programmable Gate Drive and I<sup>2</sup>C

| LIST OF FIGURES                           |      |

|-------------------------------------------|------|

| Figure 1. I <sup>2</sup> C Timing Diagram | . 20 |

| Figure 2. I <sup>2</sup> C Data Format    | . 22 |

| Figure 3. External Feedback Divider       | . 2  |

| Figure 4. Current-Sense Configurations    | . 30 |

### **Absolute Maximum Ratings**

| SUP, CS_P, EN to GNDOUT, OUTS, LX_ to GND |                     |

|-------------------------------------------|---------------------|

| PGATE to OUTS                             |                     |

| CS_P to CS_N                              | 0.3V to 0.3V        |

| BIAS, FOSC, PWM, SDA, SCL, PGOOD,         | SS, FB to GND0.3V   |

|                                           | to 6V               |

| SYNCOUT, FSYNC, COMP to GND               | 0.3V to BIAS + 0.3V |

| BST_ to LX                                | 0.3V to 12V         |

| DH_ to LX                                 | 0.3V to BST_ + 0.3V |

| DRV to GND                                | 0.3V to 12V         |

| DL_ to PGND                               | 0.3V to DRV + 0.3V  |

| PGND to GND                               | 0.3V to 0.3V        |

Package Thermal Characteristics T3255Y+4C Continuous Power Dissipation

| Continuou   | s Power Di   | ssipation       |                         |          |         |

|-------------|--------------|-----------------|-------------------------|----------|---------|

| TQFN        | (derate      | 34.5mW/°C       | (Note                   | <u> </u> | above   |

| +70°C).     |              |                 |                         | 275      | 58.6mW  |

| Junction-to | o-Case The   | rmal Resistanc  | æ (θ <sub>JC</sub> )    | <i>'</i> | 1.7°C/W |

| Junction-to | o-Ambient 7  | Thermal Resista | ance (θ <sub>JA</sub> ) | )        | 29°C/W  |

| Operating   | Temperatu    | re Range        | 4(                      | )°C to   | +125°C  |

|             |              | ·               |                         |          |         |

| Storage To  | emperature   | Range           | 65                      | 5°C to   | +150°C  |

| Soldering   | Temperatui   | re (reflow)     |                         |          | +260°C  |

| Lead Tem    | perature (so | oldering, 10s)  |                         |          | +300°C  |

| ESD Ratin   | ig Human B   | ody Model       |                         |          | 2.5kV   |

| ESD Ratin   | g Charged    | Device Model .  |                         |          | 1000V   |

|             |              |                 |                         |          |         |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal consideration see <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

| PARAMETER                 | SYMBOL | CONDITION | TYPICAL<br>RANGE | UNIT |

|---------------------------|--------|-----------|------------------|------|

| Ambient Temperature Range |        |           | -40 to<br>+125   | °C   |

Note: These limits are not guaranteed.

## **Package Information**

#### **SW-TQFN**

| OH I GI II                             |                  |

|----------------------------------------|------------------|

| Package Code                           | T3255Y+4C        |

| Outline Number                         | <u>21-100214</u> |

| Land Pattern Number                    | 90-100082        |

| Thermal Resistance, Four-Layer Board:  |                  |

| Junction to Ambient (θ <sub>JA</sub> ) | 29°C/W           |

| Junction to Case (θ <sub>JC</sub> )    | 1.7°C/W          |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{SUP} = 14V, \ V_{EN} = 14V, \ V_{DRV} = 10V \ (MAX25203ATJA), \ 6.5V \ (MAX25203BATJA), \ C_{BIAS} = 2.2\mu F, \ C_{BST} = 0.1\mu F, \ T_{J} = -40^{\circ}C \ to +150^{\circ}C, \ unless \ otherwise \ noted \ (\underline{\textit{Note 2}}, \ \underline{\textit{Note 3}}), \ typical \ values \ are \ at \ T_{A} = +25^{\circ}C.)$

| PARAMETER                                               | SYMBOL              | CONDITIONS                                                                                                                | MIN   | TYP   | MAX   | UNITS |

|---------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| SYNCHRONOUS STEP-L                                      | IP CONTROLLE        | R                                                                                                                         | •     |       |       |       |

|                                                         |                     | Initial startup, V <sub>SUP</sub> voltage                                                                                 | 4.5   |       | 36    |       |

| Supply Voltage Range                                    | $V_{SUP}$           | Bootstrap mode after initial startup condition is satisfied, V <sub>BAT</sub> voltage                                     | 1.8   |       | 36    | V     |

| Output Overvoltage<br>Threshold                         |                     | Detected with respect to V <sub>FB</sub> rising                                                                           | 104   | 108   | 111   | %     |

| Cumply Cumput                                           |                     | V <sub>EN</sub> = V <sub>SUP</sub> , V <sub>SUP</sub> > V <sub>OUT</sub> , no load (not including the FB divider current) |       | 600   |       |       |

| Supply Current                                          | I <sub>SUP</sub>    | V <sub>EN</sub> = 0V, shutdown (not including FB divider current)                                                         |       | 5     | 10    | μA    |

| Output Voltage<br>Adjustable Range                      |                     |                                                                                                                           | 3.5   |       | 65    | ٧     |

| Regulated Feedback<br>Voltage                           | V <sub>FB</sub>     | T <sub>A</sub> = -40°C to +125°C                                                                                          | 0.987 | 1     | 1.012 | ٧     |

| Feedback Leakage<br>Current                             | I <sub>FB</sub>     | T <sub>A</sub> = +25°C                                                                                                    |       | 0.01  | 0.5   | μA    |

| Feedback Line<br>Regulation Error                       |                     | V <sub>IN</sub> = 3.5V to 36V, V <sub>FB</sub> = 1V                                                                       |       | 0.01  |       | %/V   |

| Transconductance (from FB to COMP)                      | gm_boost            | V <sub>FB</sub> = 1V, V <sub>BIAS</sub> = 5V ( <u>Note 2</u> )                                                            | 170   | 260   | 370   | μS    |

| Dead Time                                               |                     | DL low to DH rising                                                                                                       |       | 40    |       | ns    |

| Dead Time                                               |                     | DH low to DL rising                                                                                                       |       | 30    |       |       |

| DH and DL Rise Time                                     |                     | C <sub>LOAD</sub> = 3nF                                                                                                   |       | 20    |       | ns    |

| DH and DL Fall Time                                     |                     | C <sub>LOAD</sub> = 3nF                                                                                                   |       | 10    |       | ns    |

| Minimum Off Time                                        |                     | MAX25203ATJA                                                                                                              |       | 200   |       |       |

| Minimum Off Time                                        | <sup>t</sup> OFFBST | MAX25203BATJA/VY+                                                                                                         |       | 85    |       | ns    |

| Switching Frequency Range                               | f <sub>SW</sub>     | Forced-PWM, resistor programmable                                                                                         | 0.22  |       | 2.1   | MHz   |

| Switching Frequency<br>Accuracy                         |                     | $R_{FOSC}$ = 17.5k $\Omega$ , $V_{BIAS}$ = 5V, 3.8V                                                                       | 360   | 400   | 440   | kHz   |

| CS Current-Limit<br>Voltage Threshold                   | V <sub>LIMIT</sub>  | Averaged $V_{CSP}$ - $V_{CSN}$ ; $V_{BIAS}$ = 5V, $V_{BATT}$ > 2.5V                                                       | 40    | 50    | 60    | mV    |

| Current Sharing<br>Accuracy                             |                     | V <sub>CSP</sub> V <sub>CSN</sub> _ > 25mV, t <sub>ON</sub> > 300ns                                                       | -5    |       | 5     | %     |

| Cycle-by-Cycle CS<br>Current-Limit Voltage<br>Threshold | V <sub>LIMIT2</sub> | Peak $V_{CSP}$ - $V_{CSN}$ ; $V_{BIAS}$ = 5V, $V_{BATT} > 2.5V$                                                           |       | 90    |       | mV    |

| Soft-Start Current                                      | I <sub>SS</sub>     |                                                                                                                           | 8     | 10    | 12    | μA    |

| LX Leakage Current                                      |                     | V <sub>LX</sub> = V <sub>PGND</sub> or V <sub>SUP</sub> , T <sub>A</sub> = +25°C                                          |       | 0.001 | 5     | μA    |

| DOOOD Threehold                                         | PGOOD_H             | % of FB, rising                                                                                                           | 93    | 95    | 97    | 0/    |

| PGOOD Threshold                                         | PGOOD_F             | % of FB, falling                                                                                                          | 91    | 93    | 95    | - %   |

| PGOOD Leakage<br>Current                                |                     | V <sub>PGOOD</sub> = 5V, T <sub>A</sub> = +25°C                                                                           |       |       | 1     | μA    |

### **Electrical Characteristics (continued)**

$(V_{SUP}=14V,\,V_{EN}=14V,\,V_{DRV}=10V\,\,(\text{MAX25203ATJA}),\,6.5V\,\,(\text{MAX25203BATJA}),\,C_{BIAS}=2.2\mu\text{F},\,C_{BST}=0.1\mu\text{F},\,T_{J}=-40^{\circ}\text{C}\,\,\text{to}\\ +150^{\circ}\text{C},\,\text{unless otherwise noted}\,\,(\underline{\textit{Note 2}},\,\underline{\textit{Note 3}}),\,\text{typical values are at}\,T_{A}=+25^{\circ}\text{C}.)$

| PARAMETER                    | SYMBOL    | CONDITIONS                                                         | MIN | TYP  | MAX  | UNITS |

|------------------------------|-----------|--------------------------------------------------------------------|-----|------|------|-------|

| PGOOD Output Low<br>Voltage  |           | I <sub>SINK</sub> = 1mA                                            |     |      | 0.2  | V     |

| PGOOD Debounce<br>Time       |           | Fault detection, rising and falling                                |     | 150  |      | μs    |

| PGOOD Timeout                |           | Output in regulation to PGOOD high                                 |     | 1    |      | ms    |

| FSYNC INPUT                  |           |                                                                    |     |      |      |       |

| FSYNC Input Frequency        |           | Minimum sync pulse of 100ns, f <sub>OSC</sub> = 2.1MHz             | 1.8 |      | 2.6  | MHz   |

| Range                        |           | Minimum sync pulse of 100ns,<br>f <sub>OSC</sub> = 400kHz          | 250 |      | 550  | kHz   |

| FSYNC Switching              |           | High threshold                                                     | 1.4 |      |      | V     |

| Thresholds                   |           | Low threshold                                                      |     |      | 0.4  | v     |

| INTERNAL LDO BIAS            |           |                                                                    |     |      |      |       |

| Internal BIAS Voltage        |           | V <sub>IN</sub> > 6V                                               |     | 5    |      | V     |

| BIAS UVLO Threshold          |           | V <sub>BIAS</sub> rising                                           |     |      | 4.5  | V     |

| BIAS OVEO TITESTICIO         |           | V <sub>BIAS</sub> falling                                          | 3   | 3.3  |      | ]     |

| BIAS Current Capability      |           | V <sub>BIAS</sub> = 5V                                             | 10  |      |      | mA    |

| GATE DRIVE LDO               |           |                                                                    |     |      |      |       |

|                              |           | Factory programmable                                               |     | 6.5  |      | V     |

| DRV Voltage Options          |           | Factory programmable                                               |     | 8    |      |       |

|                              |           | Factory programmable                                               |     | 10   |      |       |

| DDV Output Voltage           | V         | MAX25203ATJA, V <sub>SUP</sub> = 14V,<br>I <sub>DRV</sub> = 1mA    | 9.6 | 10   | 10.3 | V     |

| DRV Output Voltage           | $V_{DRV}$ | MAX25203BATJA, V <sub>SUP</sub> = 14V,<br>I <sub>DRV</sub> = 150mA | 6   | 6.5  | 7    | \ \ \ |

| DRV Dropout Voltage          |           | V <sub>SUP</sub> = 6V, I <sub>DRV</sub> = 100mA                    |     |      | 1    | V     |

| UVLO Threshold               |           | DRV rising                                                         |     |      | 4.5  | V     |

| Hysteresis                   |           |                                                                    |     | 0.85 |      | V     |

| PGATE DRIVER                 |           |                                                                    |     |      |      |       |

| PGATE Turn-On Time           |           | From turn-on to 500mA current                                      |     | 15   |      | μs    |

| PGATE Turn-Off Time          |           | From turn-off to less than 1mA                                     |     | 0.1  |      | ms    |

| PGATE VGS Drive<br>Voltage   |           | V <sub>BIAS</sub> > 4V                                             |     | 5    |      | V     |

| PWM VOLTAGE POSITIO          | NING      |                                                                    | •   |      |      | •     |

| PWM Switching<br>Threshold   |           | Low threshold                                                      |     |      | 0.4  | V     |

| PWM Switching<br>Thresholds  |           | High threshold                                                     | 1.4 |      |      | V     |

| PWM Input Frequency<br>Range |           | Minimum PWM pulse of 100ns                                         | 200 |      | 800  | kHz   |

### **Electrical Characteristics (continued)**

$(V_{SUP}=14V,\,V_{EN}=14V,\,V_{DRV}=10V\,\,(\text{MAX25203ATJA}),\,6.5V\,\,(\text{MAX25203BATJA}),\,C_{BIAS}=2.2\mu\text{F},\,C_{BST}=0.1\mu\text{F},\,T_{J}=-40^{\circ}\text{C}\,\,\text{to}\\ +150^{\circ}\text{C},\,\text{unless otherwise noted}\,\,(\underline{\textit{Note 2}},\,\underline{\textit{Note 3}}),\,\text{typical values are at}\,T_{A}=+25^{\circ}\text{C}.)$

| PARAMETER                                              | SYMBOL              | CONDITIONS                                                                                  | MIN           | TYP                   | MAX | UNITS |

|--------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|---------------|-----------------------|-----|-------|

| I <sup>2</sup> C-COMPATIBLE INTER                      | RFACE TIMING        | CHARACTERISTICS (SCL, SDA)                                                                  |               |                       |     |       |

| SCL Clock Frequency                                    | f <sub>SCL</sub>    |                                                                                             | 0             |                       | 400 | kHz   |

| Bus-Free Time Between<br>a STOP and START<br>Condition | <sup>t</sup> BUF    |                                                                                             | 1.3           |                       |     | μѕ    |

| Hold Time for a<br>Repeated START                      | t <sub>HD;STA</sub> |                                                                                             | 0.6           |                       |     | μs    |

| SCL Pulse Width Low                                    | $t_{LOW}$           |                                                                                             | 1.3           |                       |     | μs    |

| SCL Pulse Width High                                   | tHIGH               |                                                                                             | 0.6           |                       |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition        | t <sub>SU;STA</sub> |                                                                                             | 0.6           |                       |     | μs    |

| Data Hold Time                                         | t <sub>HD;DAT</sub> |                                                                                             | 0             |                       |     | ns    |

| Data Setup Time                                        | tsu;dat             |                                                                                             | 100           |                       |     | ns    |

| Data Valid Time                                        | t <sub>VD,DAT</sub> |                                                                                             |               |                       | 900 | ns    |

| SDA and SCL Receiving<br>Rise Time                     | t <sub>R</sub>      | Incoming signals (from master)                                                              | 20 +<br>CB/10 |                       | 300 | ns    |

| SDA and SCL Receiving Fall Time                        | t <sub>F</sub>      | Incoming signals (from master)                                                              | 20 +<br>CB/10 |                       | 300 | ns    |

| SDA Transmitting Fall<br>Time                          | t <sub>F</sub>      |                                                                                             | 20 +<br>CB/10 |                       | 250 | ns    |

| Setup Time for STOP<br>Condition                       | tsu;sto             |                                                                                             | 0.6           |                       |     | μs    |

| Bus Capacitance<br>Allowed                             | C <sub>B</sub>      | 2.5V ≤ V <sub>DDIO</sub> ≤ 5.5V                                                             | 0             |                       | 900 | pF    |

| Pulse Width of a<br>Suppressed Spike                   |                     | Width of spikes that must be suppressed by the input filter of both the SDA and SCL signals |               | 50                    |     | ns    |

| Input High Voltage                                     | V <sub>IH</sub>     |                                                                                             | 1.2           |                       |     | V     |

| Input Low Voltage                                      | V <sub>IL</sub>     |                                                                                             |               |                       | 0.5 | V     |

| Output Low Voltage                                     | V <sub>OL</sub>     | I <sub>SINK</sub> = 4mA                                                                     |               |                       | 0.2 | V     |

| THERMAL OVERLOAD                                       |                     |                                                                                             |               |                       |     |       |

| Thermal Shutdown Temperature                           |                     |                                                                                             |               | 170                   |     | °C    |

| Thermal Shutdown<br>Hysteresis                         |                     |                                                                                             |               | 20                    |     | °C    |

| EN LOGIC INPUT                                         |                     |                                                                                             |               |                       |     |       |

| High Threshold                                         |                     | EN                                                                                          | 1.8           |                       |     | V     |

| Low Threshold                                          |                     | EN                                                                                          |               |                       | 0.8 | V     |

| EN Input Bias Current                                  |                     | EN logic inputs only, T <sub>A</sub> = +25°C                                                |               | 0.01                  | 1   | μA    |

| SPREAD SPECTRUM                                        |                     |                                                                                             |               |                       |     |       |

| Spread Spectrum                                        |                     | SPS_EN = 0b1; SPS_RANGE = 0b1                                                               |               | f <sub>OSC</sub> ± 6% |     |       |

#### **Electrical Characteristics—MAX25203Q**

$(V_{SUP} = 14V, V_{EN} = 14V, V_{DRV} = 10V, C_{BIAS} = 2.2 \mu F, C_{BST} = 0.1 \mu F, T_{J} = -40 ^{\circ}C \text{ to } +150 ^{\circ}C, \text{ unless otherwise noted } (\underline{\textit{Note 2}}, \underline{\textit{Note 3}}), \text{ typical values are at } T_{A} = +25 ^{\circ}C.)$

| PARAMETER                                               | SYMBOL              | CONDITIONS                                                                                         | MIN | TYP   | MAX  | UNITS |

|---------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|-----|-------|------|-------|

| SYNCHRONOUS STEP-L                                      | JP CONTROLL         | ER                                                                                                 |     |       |      |       |

|                                                         |                     | Initial startup, V <sub>SUP</sub> voltage                                                          | 4.5 |       | 36   |       |

| Supply Voltage Range                                    | $V_{SUP}$           | Bootstrap mode after initial startup condition is satisfied, V <sub>BAT</sub> voltage              | 1.8 |       | 36   | V     |

| Supply Current                                          | I <sub>SUP</sub>    | V <sub>EN</sub> = 0V, shutdown (not including FB divider current)                                  |     | 5     | 10   | μA    |

| Dood Time                                               |                     | DL low to DH rising                                                                                |     | 40    |      | no    |

| Dead Time                                               |                     | DH low to DL rising                                                                                |     | 30    |      | ns    |

| DH and DL Rise Time                                     |                     | C <sub>LOAD</sub> = 3nF                                                                            |     | 20    |      | ns    |

| DH and DL Fall Time                                     |                     | C <sub>LOAD</sub> = 3nF                                                                            |     | 10    |      | ns    |

| Minimum Off-Time                                        | toffbst             |                                                                                                    |     | 200   |      | ns    |

| CS Current-Limit<br>Voltage Threshold                   | V <sub>LIMIT</sub>  | Averaged V <sub>CSP</sub> - V <sub>CSN</sub> ; V <sub>BIAS</sub> = 5V,<br>V <sub>BATT</sub> > 2.5V | 40  | 50    | 60   | mV    |

| Current Sharing<br>Accuracy                             |                     | V <sub>CSP</sub> V <sub>CSN</sub> _ > 25mV, t <sub>ON</sub> > 300ns                                | -5  |       | 5    | %     |

| Cycle-by-Cycle CS<br>Current Limit Voltage<br>Threshold | V <sub>LIMIT2</sub> | Peak V <sub>CSP</sub> -V <sub>CSN</sub> ; V <sub>BIAS</sub> = 5V,<br>V <sub>BATT</sub> > 2.5V      |     | 90    |      | mV    |

| LX Leakage Current                                      |                     | V <sub>LX</sub> = V <sub>PGND</sub> or V <sub>SUP</sub> , T <sub>A</sub> = +25°C                   |     | 0.001 | 5    | μA    |

| FSYNC INPUT                                             |                     |                                                                                                    | 1   |       |      | •     |

| FSYNC Input Frequency                                   |                     | Minimum sync pulse of 100ns, f <sub>OSC</sub> = 2.1MHz                                             | 1.8 |       | 2.6  | MHz   |

| Range                                                   |                     | Minimum sync pulse of 100ns, f <sub>OSC</sub> = 400kHz                                             | 250 |       | 550  | kHz   |

| FSYNC Switching                                         |                     | High threshold                                                                                     | 1.4 |       |      | V     |

| Thresholds                                              |                     | Low threshold                                                                                      |     |       | 0.4  | v     |

| INTERNAL LDO BIAS                                       |                     |                                                                                                    |     |       |      |       |

| Internal BIAS Voltage                                   |                     | V <sub>IN</sub> > 6V                                                                               |     | 5     |      | V     |

| BIAS UVLO Threshold                                     |                     | V <sub>BIAS</sub> rising                                                                           |     |       | 4.5  | V     |

| DIAS OVEO TITESTICIO                                    |                     | V <sub>BIAS</sub> falling                                                                          | 3   | 3.3   |      | V     |

| BIAS Current Capability                                 |                     | V <sub>BIAS</sub> = 5V                                                                             | 10  |       |      | mA    |

| GATE DRIVE LDO                                          |                     |                                                                                                    |     |       |      |       |

|                                                         |                     | Factory programmable                                                                               |     | 6.5   |      |       |

| DRV Voltage Options                                     |                     | Factory programmable                                                                               |     | 8     |      | V     |

|                                                         |                     | Factory programmable                                                                               |     | 10    |      | 7     |

| DRV Output Voltage                                      | V <sub>DRV</sub>    | V <sub>SUP</sub> = 14V, I <sub>DRV</sub> = 1mA                                                     | 9.6 | 10    | 10.3 | V     |

| DRV Dropout Voltage                                     |                     | V <sub>SUP</sub> = 6V, I <sub>DRV</sub> = 100mA                                                    |     |       | 1    | V     |

| UVLO Threshold                                          |                     | DRV rising                                                                                         |     |       | 4.5  | V     |

| Hysteresis                                              |                     |                                                                                                    |     | 0.85  |      | V     |

| I <sup>2</sup> C-COMPATIBLE INTER                       | FACE TIMING         | CHARACTERISTICS (SCL, SDA)                                                                         |     |       |      |       |

| SCL Clock Frequency                                     | f <sub>SCL</sub>    |                                                                                                    | 0   |       | 400  | kHz   |

### **Electrical Characteristics—MAX25203Q (continued)**

$(V_{SUP} = 14V, V_{EN} = 14V, V_{DRV} = 10V, C_{BIAS} = 2.2 \mu F, C_{BST} = 0.1 \mu F, T_{J} = -40 ^{\circ}C \text{ to } +150 ^{\circ}C, \text{ unless otherwise noted } (\underline{\textit{Note 2}}, \underline{\textit{Note 3}}), \text{ typical values are at } T_{A} = +25 ^{\circ}C.)$

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                                  | MIN           | TYP  | MAX | UNITS |

|--------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|---------------|------|-----|-------|

| Bus-Free Time Between a STOP and START Condition | t <sub>BUF</sub>    |                                                                                             | 1.3           |      |     | μs    |

| Hold Time for a<br>Repeated START                | t <sub>HD;STA</sub> |                                                                                             | 0.6           |      |     | μs    |

| SCL Pulse Width Low                              | t <sub>LOW</sub>    |                                                                                             | 1.3           |      |     | μs    |

| SCL Pulse Width High                             | tHIGH               |                                                                                             | 0.6           |      |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition  | t <sub>SU;STA</sub> |                                                                                             | 0.6           |      |     | μs    |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                                                                                             | 0             |      |     | ns    |

| Data Setup Time                                  | tsu;dat             |                                                                                             | 100           |      |     | ns    |

| Data Valid Time                                  | t <sub>VD;DAT</sub> |                                                                                             |               |      | 900 | ns    |

| SDA and SCL Receiving Rise Time                  | t <sub>R</sub>      | Incoming signals (from master)                                                              | 20 +<br>CB/10 |      | 300 | ns    |

| SDA and SCL Receiving Fall Time                  | t <sub>F</sub>      | Incoming signals (from master)                                                              | 20 +<br>CB/10 |      | 300 | ns    |

| SDA Transmitting Fall Time                       | t <sub>F</sub>      |                                                                                             | 20 +<br>CB/10 |      | 250 | ns    |

| Setup Time for STOP<br>Condition                 | tsu;sto             |                                                                                             | 0.6           |      |     | μs    |

| Bus Capacitance<br>Allowed                       | $C_{B}$             | 2.5V ≤ V <sub>DDIO</sub> ≤ 5.5V                                                             | 0             |      | 900 | pF    |

| Pulse Width of a<br>Suppressed Spike             |                     | Width of spikes that must be suppressed by the input filter of both the SDA and SCL signals |               | 50   |     | ns    |

| Input High Voltage                               | V <sub>IH</sub>     |                                                                                             | 1.2           |      |     | V     |

| Input Low Voltage                                | V <sub>IL</sub>     |                                                                                             |               |      | 0.5 | V     |

| Output Low Voltage                               | V <sub>OL</sub>     | I <sub>SINK</sub> = 4mA                                                                     |               |      | 0.2 | V     |

| THERMAL OVERLOAD                                 |                     |                                                                                             |               |      |     |       |

| Thermal Shutdown<br>Temperature                  |                     |                                                                                             |               | 170  |     | °C    |

| Thermal Shutdown<br>Hysteresis                   |                     |                                                                                             |               | 20   |     | °C    |

| EN LOGIC INPUT                                   |                     |                                                                                             |               |      |     |       |

| High Threshold                                   |                     | EN                                                                                          | 1.8           |      |     | V     |

| Low Threshold                                    |                     | EN                                                                                          |               |      | 8.0 | V     |

| EN Input Bias Current                            |                     | EN logic inputs only, T <sub>A</sub> = +25°C                                                |               | 0.01 | 1   | μA    |

Note 2: All units are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltages are guaranteed by design and characterization.

Note 3: The device is designed for continuous operation up to  $T_J$  = +125°C for 95,000 hours and  $T_J$  = +150°C for 5,000 hours.

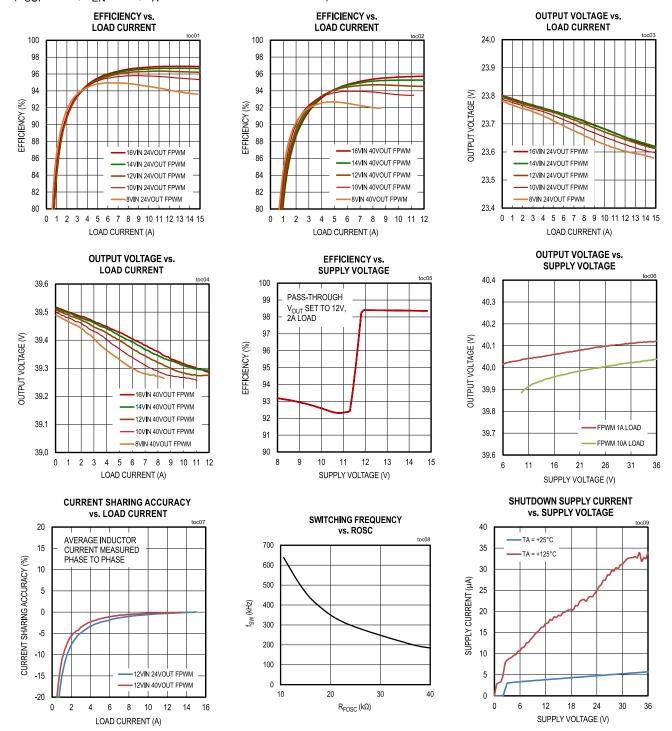

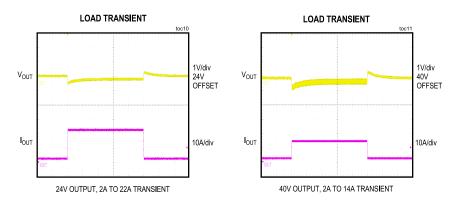

### **Typical Operating Characteristics**

$(V_{SUP} = 14V; V_{EN} = 14V; T_A = +25^{\circ}C \text{ unless otherwise noted.})$

### **Typical Operating Characteristics (continued)**

$(V_{SUP} = 14V; V_{EN} = 14V; T_A = +25^{\circ}C \text{ unless otherwise noted.})$

## **Pin Configuration**

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BST1 | Boost Flying Capacitor Connection for High-Side Gate Voltage. Connect a high-voltage diode between DRV and BST1. Connect a ceramic capacitor between BST1 and LX1. See the <u>High-Side Gate-Driver Supply (BST)</u> section.                                                                                                                                                                                                                                                                                 |

| 2   | EN   | High-Voltage Tolerant, Active-High Digital Enable Input for Controller. Driving EN low disables the boost controller. EN also has a very accurate threshold of ±3% for both rising and falling voltages. A resistor-divider can be used to control the turn ON and OFF of the boost controller in hardware by using a resistor-divider. When EN is low, the MAX25203 is powered off, including BIAS and I <sup>2</sup> C interface. Bring EN high to enable the MAX25203 and power up into the default state. |

# **Pin Description (continued)**

| PIN | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 3   | CS1N      | Negative Current-Sense Input for Phase 1. Connect CS1N to the negative side of the current-sense element. See the <i>Current Limiting and Current-Sense Inputs (SUP and CS)</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 4   | CS1P      | Positive Current-Sense Input for Phase 1. Connect CS1P to the positive side of the current-sense element. See the <u>Current Limiting and Current-Sense Inputs (SUP and CS)</u> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 5   | SUP       | pply Input. Connect SUP to the main battery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 6   | OUTS      | rue Shutdown PFET's Source Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 7   | PGATE     | External p-Channel MOSFET Gate Connection. Connect PGATE to the gate of the external p-channel output disconnect switch. Connect PGATE to GND if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 8   | OUT       | Output Voltage Sense for Internal Feedback Divider. Connect OUT to the boost output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 9   | FB        | Boost Converter Feedback Input. Connect FB to BIAS to use the I <sup>2</sup> C programmed output voltage or PWM voltage control. For external feedback, connect FB to the center tap of a resistor-divider between the boost regulator output. FB regulates to 1V (typ). See the <u>Setting and Controlling the Output Voltage</u> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 10  | BIAS      | 5V Internal Linear Regulator Output. Bypass BIAS to GND with a low-ESR ceramic capacitor of 1µF minimum value. BIAS provides the power to the internal circuitry and external loads. See the <i>Fixed 5V Linear Regulator (BIAS)</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 11  | GND       | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 12  | NC        | Leave this pin unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 13  | COMP      | Boost Controller Error Amplifier Output. Connect an RC network to COMP to compensate the boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 14  | SS        | Soft-Start. Connect a capacitor from SS to GND to set the soft-start time. See the <u>Soft-Start</u> section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 15  | PGOOD/IRQ | Open-Drain Power-Good Output or Interrupt Request. This pin is configured as either a power-good (PGOOD) output or interrupt request (IRQ) output (see the Ordering Information table). To obtain a logic signal, pull up PGOOD/IRQ with an external resistor connected to a positive voltage lower than 5.5V.  PGOOD pulls low when OUT is more than 93% (typ) below the normal regulation point. PGOOD is low during soft-start and in shutdown. PGOOD becomes high impedance when OUT is in regulation.  IRQ pulls low when OUT is more than 93% (typ) below the normal regulation point and when a fault is reported in the FAULT register. IRQ is low during shutdown, and remains low after startup until the FAULT register has been read. IRQ becomes high impedance after reading the FAULT_STAT register when OUT is in regulation. If there is a persistent fault, IRQ pulls low again after reading FAULT, otherwise IRQ remains high until a fault occurs.  See the Output Voltage Monitor (PGOOD) and Interrupt Request Output (IRQ) sections for details. |  |  |  |  |  |  |

| 16  | FOSC      | Frequency Setting Input. Connect a resistor to FOSC to set the switching frequency of the DC-DC converters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 17  | SYNCOUT   | Synchronization Clock Output. SYNCOUT outputs a clock that is 90° out-of-phase with the internal oscillator or the external FSYNC input. For the quad-phase configuration, connect SYNCOUT of the master to FSYNC of the slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 18  | FSYNC     | External Clock Synchronization Input. To synchronize with an external clock, connect the clock to FSYNC. See the Oscillator Frequency/External Synchronization section. When not using external synchronization, connect FSYNC to BIAS for forced-PWM operation with the internal clock, or connect FSYNC to GND for skip-mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|     |           | connect FSYNC to GND for skip-mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 19  | SDA       | connect FSYNC to GND for skip-mode operation.  I <sup>2</sup> C Data Input/Output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

# **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                               |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | PWM  | PWM Positioning Control Input. Controls the output voltage, allowing it to track a digital duty cycle (PWM) signal. Connect PWM to GND when using an external resistor-divider to set the output voltage or if PWM is not used.                                                        |

| 22  | CS2P | Positive Current-Sense Input for Phase 2. Connect CS2P to the positive side of the current-sense element. See the <u>Current Limiting and Current-Sense Inputs (SUP and CS)</u> section.                                                                                               |

| 23  | CS2N | Negative Current-Sense Input for Phase 2. Connect CS2N to the negative side of the current-sense element. See the <u>Current Limiting and Current-Sense Inputs (SUP and CS)</u> section.                                                                                               |

| 24  | BST2 | Boost Flying Capacitor Connection for High-Side Gate Voltage. Connect a high-voltage diode between DRV and BST2. Connect a ceramic capacitor between BST2 and LX2. See the <u>High-Side Gate-Driver Supply (BST)</u> section.                                                          |

| 25  | DH2  | High-Side MOSFET Gate Driver Output. The DH2 output voltage swings from V <sub>LX2</sub> to V <sub>BST2</sub> .                                                                                                                                                                        |

| 26  | LX2  | Inductor Connection for Phase 2. Connect LX2 to the switched side of the inductor. LX2 serves as the lower supply rail for the DH2 high-side gate driver.                                                                                                                              |

| 27  | DL2  | Low-Side n-Channel MOSFET Gate Driver Output for Phase 2.                                                                                                                                                                                                                              |

| 28  | PGND | Power Ground.                                                                                                                                                                                                                                                                          |

| 29  | DRV  | 6.5V to 10V Preset Low-Dropout Voltage-Regulator Output. Bypass DRV to GND with a 4.7μF or greater ceramic capacitor. This voltage is used as the gate drive voltage for external MOSFETs. See the <u>Ordering Information</u> table for the factory-set DRV voltage.                  |

| 30  | DL1  | Low-Side n-Channel MOSFET Gate Driver Output for Phase 1.                                                                                                                                                                                                                              |

| 31  | LX1  | Inductor Connection for Phase 1. Connect LX1 to the switched side of the inductor. LX1 serves as the lower supply rail for the DH1 high-side gate driver.                                                                                                                              |

| 32  | DH1  | High-Side MOSFET Gate Driver Output. The DH1 output voltage swings from V <sub>LX1</sub> to V <sub>BST1</sub> .                                                                                                                                                                        |

| EP  | EP   | Exposed Pad. Connect the exposed pad to ground. Connecting the exposed pad to ground does not remove the requirement for proper ground connections to GND. The exposed pad is attached with epoxy to the substrate of the die, making it an excellent path to remove heat from the IC. |

## **Functional Diagram**

#### **Detailed Description**

The MAX25203 automotive dual-phase synchronous boost controller enables infotainment systems to stay in regulation during cold-crank or start-stop operation all the way down to a battery input of 1.8V. It can also be used to generate backlight voltage and Class D audio amplifier voltages. This device can start with an input voltage supply from 4.5V to 42V and can operate down to 1.8V after start-up, and has a low 5µA shutdown supply current.

The MAX25203 operates at up to 2.1MHz frequency to allow small external components and reduced output ripple, and to guarantee no AM band interference. The switching frequency is resistor adjustable (220kHz to 2100kHz) or it can be synchronized on-the-fly to an external clock.

The MAX25203 has a spread-spectrum option for frequency modulation to minimize EMI interference. A 90° out-of-phase clock output enables synchronizing a second MAX25203 for guad-phase operation.

Pass-through operation has over 98% efficiency when the supply voltage exceeds the output regulation voltage. Programmable current-limit blanking handles high peak loads without oversizing the inductor.

The MAX25203 features a power-OK monitor and undervoltage lockout. Protection features include cycle-by-cycle current limit and thermal shutdown. It operates over the -40°C to +125°C automotive temperature range.

#### **Current-Mode Control Loop**

Peak current-mode control operation provides excellent load step performance and simple compensation. The inherent feed-forward characteristic is useful especially in automotive applications where the input voltage changes quickly during cold-crank and load-dump conditions. To avoid premature turn-off at the beginning of the on-cycle, the current-limit and PWM comparator inputs have leading-edge blanking.

#### Fixed 5V Linear Regulator (BIAS)

An internal 5V linear regulator (BIAS) is used to power the controller's internal circuitry. Connect a  $1\mu F$  or greater ceramic capacitor from BIAS to GND as close to the IC pins as possible to guarantee stability under the full-load condition. If the BIAS voltage drops below the undervoltage (UVLO) threshold, the controller will shut down and all I<sup>2</sup>C register value reset to their default values.

#### **Gate Drive LDO (DRV)**

DRV is a low-dropout voltage regulator (LDO) used to supply the gate drive for external MOSFETs. The gate drive LDO output voltage is factory preset to 6.5V, 8V, or 10V; see the <u>Ordering Information</u> table for each part number's drive voltage. DRV can provide up to 150mA (typ) total. The gate drive current requirements can be estimated as follows:

$I_{DRV} = f_{SW} (Q_{G1DL} + Q_{G1DH} + Q_{G2DL} + Q_{G2DH})$