# Bottom Port PDM Digital Output Multi-Mode Microphone

#### **GENERAL DESCRIPTION**

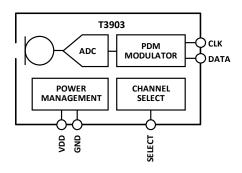

The T3903 is a multi-mode, low noise digital MEMS microphone in a small package. The T3903 consists of a MEMS microphone element and an impedance converter amplifier followed by a fourth-order  $\Sigma$ - $\Delta$  modulator. The digital interface allows the pulse density modulated (PDM) output of two microphones to be time multiplexed on a single data line using a single clock.

The T3903 has multiple modes of operation: High Quality, Low-Power (AlwaysOn), and Sleep. The T3903 has high SNR in all operational modes. It has 133 dB SPL AOP in High Quality Mode and 120 dB SPL AOP in Low-Power mode.

The T3903 is available in a standard  $3.5 \times 2.65 \times 0.98$  mm surface-mount package. It is reflow solder compatible with no sensitivity degradation.

#### **APPLICATIONS**

- Smartphones

- Microphone Arrays

- Tablet Computers

- Cameras

#### **FEATURES**

| SPEC        | HIGH QUALITY MODE  | LOW-POWER MODE     |

|-------------|--------------------|--------------------|

| Sensitivity | −37 dB FS ±1 dB    | −26 dB FS ±1 dB    |

| SNR         | 66 dBA             | 63 dBA             |

| Current     | 590 μΑ             | 220 μΑ             |

| AOP         | 133 dB SPL         | 120 dB SPL         |

| Clock       | 2.0 MHz to 3.3 MHz | 400 kHz to 800 kHz |

- 3.5 × 2.65 × 0.98 mm surface-mount package

- Extended frequency response from 40 Hz to >20 kHz

- Sleep Mode: 9 μA

- Fourth-order Σ-Δ modulator

- Digital pulse density modulation (PDM) output

- Compatible with Sn/Pb and Pb-free solder processes

- RoHS/WEEE compliant

#### **FUNCTIONAL BLOCK DIAGRAM**

#### ORDERING INFORMATION

| PART             | TEMP RANGE     | PACKAGING         |

|------------------|----------------|-------------------|

| MMICT3903-00-012 | -40°C to +85°C | 13" Tape and Reel |

| EV_T3903-FX      | _              |                   |

# **TABLE OF CONTENTS**

|     | General Description                                                | 1  |

|-----|--------------------------------------------------------------------|----|

|     | Functional Block Diagram                                           | 1  |

|     | Applications                                                       | 1  |

|     | Features                                                           | 1  |

|     | Ordering Information                                               | 1  |

| Tab | ole of Contents                                                    | 2  |

| Spe | ecifications                                                       | 4  |

|     | Table 1. Acoustical/Electrical Characteristics – General           | 4  |

|     | Table 2. Acoustical/Electrical Characteristics – High Quality Mode | 4  |

|     | Table 3. Acoustical/Electrical Characteristics – Low-Power Mode    | 5  |

|     | Table 4. Digital Input/Output Characteristics                      | 5  |

|     | Table 5. PDM Digital Input/Output                                  | 6  |

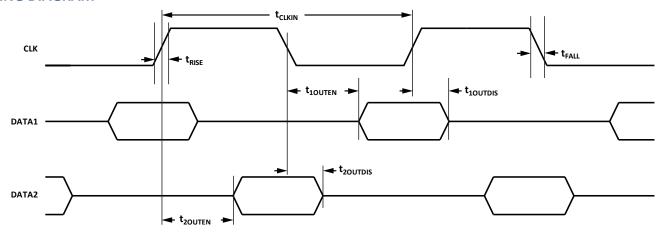

|     | Timing Diagram                                                     | 6  |

| Abs | solute Maximum Ratings                                             | 7  |

|     | Table 6. Absolute Maximum Ratings                                  | 7  |

|     | ESD Caution                                                        | 7  |

|     | Soldering Profile                                                  | 8  |

|     | Table 7. Recommended Soldering Profile*                            | 8  |

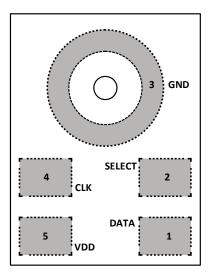

| Pin | Configurations And Function Descriptions                           | 9  |

|     | Table 8. Pin Function Descriptions                                 | 9  |

| Тур | oical Performance Characteristics                                  | 10 |

| The | eory Of Operation                                                  | 11 |

|     | PDM Data Format                                                    | 11 |

|     | Table 9. T3903 Channel Setting                                     | 11 |

|     | PDM Microphone Sensitivity                                         | 11 |

| App | plications Information                                             | 13 |

|     | Low-Power Mode                                                     | 13 |

|     | Dynamic Range Considerations                                       | 13 |

|     | Connecting PDM Microphones                                         | 13 |

|     | Sleep Mode                                                         | 15 |

|     | Start-Up Time                                                      | 15 |

| Sup | pporting Documents                                                 | 16 |

|     | Application Notes – General                                        | 16 |

| PCB | B Design And Land Pattern Layout                                   | 17 |

|     | PCB Material And Thickness                                         | 17 |

| Har | ndling Instructions                                                | 18 |

|     | Pick And Place Equipment                                           | 18 |

|     | Reflow Solder                                                      | 18 |

| Вс       | Soard Wash                 | 18 |

|----------|----------------------------|----|

|          | Dimensions                 |    |

| Oı       | Ordering Guide             | 19 |

| Re       | Revision History           | 20 |

| Compliar | nce Declaration Disclaimer | 21 |

# **SPECIFICATIONS**

# TABLE 1. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – GENERAL

$T_A = 25$ °C, VDD = 1.8 V to 3.3 V, SCK = 2.4 MHz,  $C_{LOAD} = 30$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                            | CONDITIONS                           | MIN             | TYP | MAX | UNITS | NOTES |

|--------------------------------------|--------------------------------------|-----------------|-----|-----|-------|-------|

| PERFORMANCE                          |                                      |                 |     |     |       |       |

| Directionality                       |                                      | Omni            |     |     |       |       |

| Output Polarity                      | Input acoustic pressure vs. output   | Non-Inverted    |     |     |       |       |

|                                      | data                                 | Non-inverted    |     |     |       |       |

| Supply Voltage (V <sub>DD</sub> )    |                                      | 1.65 1.8 3.63 V |     |     |       |       |

| Sleep Mode Current (I <sub>s</sub> ) | SCK < 200 kHz, V <sub>DD</sub> =1.8V |                 | 9   |     | μΑ    | 1     |

Note 1: Sleep Mode current is not specified at 3.3V

#### TABLE 2. ACOUSTICAL/ELECTRICAL CHARACTERISTICS – HIGH QUALITY MODE

$T_A = 25$ °C, VDD = 1.8 V to 3.3 V, SCK = 2.4 MHz,  $C_{LOAD} = 30$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                         | CONDITIONS                                                                    | MIN | TYP  | MAX | UNITS     | NOTES |

|-----------------------------------|-------------------------------------------------------------------------------|-----|------|-----|-----------|-------|

| Sensitivity                       | 1 kHz, 94 dB SPL                                                              | -38 | -37  | -36 | dB FS     | 2     |

| Signal-to-Noise Ratio (SNR)       | ise Ratio (SNR) 20 kHz bandwidth, A-weighted                                  |     | 66   |     | dBA       |       |

| Equivalent Input Noise (EIN)      | 20 kHz bandwidth, A-weighted                                                  |     | 28   |     | dBA SPL   |       |

| Acoustic Dynamic Range            | Derived from EIN and acoustic overload point                                  |     | 105  |     | dB        |       |

| Total Harmonic Distortion (THD)   | 94 dB SPL                                                                     |     | 0.1  |     | %         |       |

| Power Supply Rejection (PSR)      | 20 Hz, 100 mVpp applied to V <sub>DD</sub>                                    |     | -86  |     |           |       |

|                                   | 1 kHz, 100 mVpp applied to V <sub>DD</sub>                                    |     | -109 |     |           |       |

|                                   | 5 kHz, 100 mVpp applied to V <sub>DD</sub>                                    |     | -98  |     | dB FS(A)  |       |

|                                   | 10 kHz, 100 mVpp applied to V <sub>DD</sub>                                   |     | -96  |     |           |       |

|                                   | 20 kHz, 100 mVpp applied to V <sub>DD</sub>                                   |     | -81  |     |           |       |

| Power Supply Rejection (PSR)      | 217 Hz, 100 mV p-p square wave<br>superimposed on VDD = 1.8 V, A-<br>weighted |     | -105 |     | dB FS (A) |       |

| Power Supply Rejection—Swept Sine | 1 kHz sine wave                                                               |     | -109 |     | dB FS     |       |

| Acoustic Overload Point           | 10% THD                                                                       |     | 133  |     | dB SPL    |       |

| Supply Current (I <sub>S</sub> )  | V <sub>DD</sub> = 1.8 V, no load                                              |     | 590  |     | μΑ        |       |

Note 2: Sensitivity is relative to the RMS level of a sine wave with positive amplitude equal to 100% 1s density and negative amplitude equal to 0% 1s density.

# TABLE 3. ACOUSTICAL/ELECTRICAL CHARACTERISTICS - LOW-POWER MODE

$T_A = 25$ °C, VDD = 1.8 V to 3.3 V, SCK = 768 kHz,  $C_{LOAD} = 30$  pF unless otherwise noted. Typical specifications are not guaranteed.

| PARAMETER                         | CONDITIONS                                                             | MIN | TYP  | MAX | UNITS   | NOTES |

|-----------------------------------|------------------------------------------------------------------------|-----|------|-----|---------|-------|

| Sensitivity                       | 1 kHz, 94 dB SPL                                                       | -27 | -26  | -25 | dB FS   | 3     |

| Signal-to-Noise Ratio (SNR)       | 8 kHz bandwidth, A-weighted                                            |     | 63   |     | dBA     |       |

| Equivalent Input Noise (EIN)      | 8 kHz bandwidth, A-weighted                                            |     | 31   |     | dBA SPL |       |

| Acoustic Dynamic Range            | Derived from EIN and acoustic overload point                           |     | 89   |     | dB      |       |

| Total Harmonic Distortion (THD)   | 105 dB SPL                                                             |     | 0.15 |     | %       |       |

| Power Supply Rejection (PSR)      | 217 Hz, 100 mV p-p square wave superimposed on VDD = 1.8 V, A-weighted |     | -95  |     | dB FS   |       |

| Power Supply Rejection—Swept Sine | 1 kHz sine wave                                                        |     | -99  |     | dB FS   |       |

| Acoustic Overload Point           | 10% THD                                                                |     | 120  |     | dB SPL  |       |

| Supply Current (I <sub>S</sub> )  | V <sub>DD</sub> = 1.8 V, no load                                       |     | 220  |     | μΑ      |       |

Note 3: Sensitivity is relative to the RMS level of a sine wave with positive amplitude equal to 100% 1s density and negative amplitude equal to 0% 1s density.

# **TABLE 4. DIGITAL INPUT/OUTPUT CHARACTERISTICS**

$T_A = 25$ °C, 1.8 V < VDD < 3.3 V, unless otherwise noted.

| PARAMETER                              | CONDITIONS                 | MIN                    | TYP      | MAX                    | UNITS | NOTES |

|----------------------------------------|----------------------------|------------------------|----------|------------------------|-------|-------|

| Input Voltage High (V <sub>IH</sub> )  |                            | 0.65 × V <sub>DD</sub> |          |                        | V     |       |

| Input Voltage Low (V <sub>IL</sub> )   |                            |                        |          | 0.35 × V <sub>DD</sub> | V     |       |

| Output Voltage High (V <sub>OH</sub> ) | I <sub>LOAD</sub> = 0.5 mA | 0.7 × V <sub>DD</sub>  | $V_{DD}$ |                        | V     |       |

| Output Voltage Low (V <sub>OL</sub> )  | I <sub>LOAD</sub> = 0.5 mA |                        | 0        | 0.3 × V <sub>DD</sub>  | V     |       |

| Output DC Offset                       | Percent of full scale      |                        | 3        |                        | %     |       |

# **TABLE 5. PDM DIGITAL INPUT/OUTPUT**

$T_A$  = 25°C, 1.8 V < VDD < 3.3 V , unless otherwise noted.

| PARAMETER             | CONDITIONS                                                                                                                   | MIN | TYP   | MAX      | UNITS | NOTES |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------|-------|-------|

| MODE SWITCHING        |                                                                                                                              |     |       |          |       |       |

| Sleep Time            | Time from f <sub>CLK</sub> falling <200 kHz                                                                                  |     | 1     |          | ms    |       |

| Wake-Up Time          | /ake-Up Time High Quality mode, Sleep Mode to f <sub>CLK</sub> >1.2 MHz, output within 0.5 dB of final sensitivity, power on |     |       | ms       |       |       |

| Wake-Up Time          | Low-Power Mode, Sleep Mode to f <sub>CLK</sub> >400 kHz, output within 0.5 dB of final sensitivity, power on                 |     | 7     |          | ms    |       |

| Switching time        | Between Low-Power and High Quality Mode                                                                                      |     | 7     |          | ms    |       |

| INPUT                 |                                                                                                                              |     |       |          |       |       |

| t <sub>CLKIN</sub>    | Input clock period                                                                                                           | 303 |       | 2500     | ns    |       |

|                       | Sleep Mode                                                                                                                   |     |       | 200      | kHz   |       |

| Clock Frequency (CLK) | Low-Power Mode                                                                                                               | 400 |       | 800      | kHz   |       |

|                       | High Quality Mode                                                                                                            | 2.0 |       | 3.3      | MHz   |       |

| Clock Duty Cycle      | f <sub>CLK</sub> <3.3 MHz                                                                                                    | 45  |       | 55       | %     |       |

| t <sub>RISE</sub>     | CLK rise time (10% to 90% level)                                                                                             |     |       | 25       | ns    | 4     |

| t <sub>FALL</sub>     | CLK fall time (90% to 10% level)                                                                                             |     |       | 25       | ns    | 4     |

| OUTPUT                |                                                                                                                              |     | - II. | <u>'</u> | ч     |       |

| t <sub>1OUTEN</sub>   | DATA1 (right) driven after falling clock edge                                                                                | 30  |       |          | ns    |       |

| t <sub>10UTDIS</sub>  | DATA1 (right) disabled after rising clock edge                                                                               | 5   |       | 18       | ns    |       |

| t <sub>2OUTEN</sub>   | DATA2 (left) driven after rising clock edge                                                                                  | 30  |       |          | ns    |       |

| t <sub>2OUTDIS</sub>  | DATA2 (left) disabled after falling clock edge                                                                               | 5   |       | 18       | ns    |       |

Note 4: Guaranteed by design

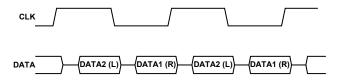

### **TIMING DIAGRAM**

Figure 1. Pulse Density Modulated Output Timing

# ABSOLUTE MAXIMUM RATINGS

Stress above those listed as Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to the absolute maximum ratings conditions for extended periods may affect device reliability.

#### **TABLE 6. ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                         | RATING                                                         |

|-----------------------------------|----------------------------------------------------------------|

| Supply Voltage (V <sub>DD</sub> ) | -0.3 V to +3.63 V                                              |

| Digital Pin Input Voltage         | -0.3 V to V <sub>DD</sub> + 0.3 V or 3.63 V, whichever is less |

| Mechanical Shock                  | 10,000 g                                                       |

| Vibration                         | Per MIL-STD-883 Method 2007, Test Condition B                  |

| Temperature Range                 |                                                                |

| Operating                         | -40°C to +85°C                                                 |

| Storage                           | −55°C to +150°C                                                |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

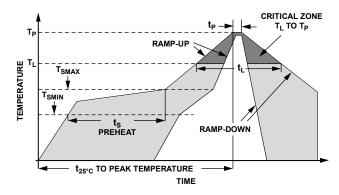

# **SOLDERING PROFILE**

**Figure 2. Recommended Soldering Profile Limits**

### **TABLE 7. RECOMMENDED SOLDERING PROFILE\***

| PROFILE FEATU                                                    | JRE                                      | Sn63/Pb37                      | Pb-Free          |

|------------------------------------------------------------------|------------------------------------------|--------------------------------|------------------|

| Average Ramp                                                     | Rate (T <sub>L</sub> to T <sub>P</sub> ) | 1.25°C/sec max                 | 1.25°C/sec max   |

|                                                                  | Minimum Temperature (T <sub>SMIN</sub> ) | 100°C                          | 100°C            |

| Preheat                                                          | Maximum Temperature (T <sub>SMAX</sub> ) | 150°C                          | 200°C            |

|                                                                  | Time ( $T_{SMIN}$ to $T_{SMAX}$ ), $t_S$ | 60 sec to 75 sec               | 60 sec to 75 sec |

| Ramp-Up Rate                                                     | (T <sub>SMAX</sub> to T <sub>L</sub> )   | 1.25°C/sec                     | 1.25°C/sec       |

| Time Maintaine                                                   | ed Above Liquidous (t <sub>L</sub> )     | 45 sec to 75 sec               | ~50 sec          |

| Liquidous Temp                                                   | perature (T <sub>L</sub> )               | 183°C                          | 217°C            |

| Peak Temperat                                                    | ure (T <sub>P</sub> )                    | 215°C +3°C/-3°C                | 260°C +0°C/-5°C  |

| Time Within +5°C of Actual Peak<br>Temperature (t <sub>P</sub> ) |                                          | 20 sec to 30 sec               | 20 sec to 30 sec |

| Ramp-Down Rate                                                   |                                          | n Rate 3°C/sec max 3°C/sec max |                  |

| Time +25°C (t <sub>25°C</sub> ) to Peak Temperature              |                                          | 5 min max                      | 5 min max        |

<sup>\*</sup>The reflow profile in Table 7 is recommended for board manufacturing with TDK MEMS microphones. All microphones are also compatible with the J-STD-020 profile

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration (Top View, Terminal Side Down)

### **TABLE 8. PIN FUNCTION DESCRIPTIONS**

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                       |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DATA   | Digital Output Signal (DATA1 or DATA2)                                                                                                                                                                                         |

| 2   | SELECT | Left Channel or Right Channel Select: DATA 1 (right): SELECT tied to GND DATA 2 (left): SELECT tied to VDD. In this setting, SELECT should be tied to the same voltage source as the VDD pin.                                  |

| 3   | GND    | Ground                                                                                                                                                                                                                         |

| 4   | CLK    | Clock Input to Microphone                                                                                                                                                                                                      |

| 5   | VDD    | Power Supply. For best performance and to avoid potential parasitic artifacts, place a $0.1\mu\text{F}$ (100 nF) ceramic type X7R capacitor between Pin 5 (VDD) and ground. Place the capacitor as close to Pin 5 as possible. |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

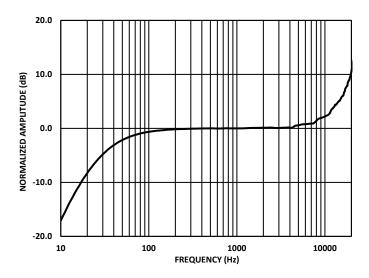

Figure 4. Typical Audio Frequency Response, High Quality Mode

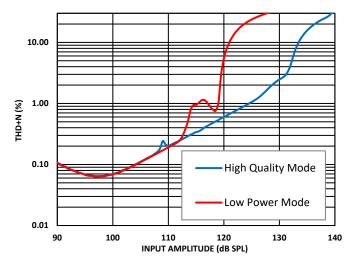

Figure 5. THD + N

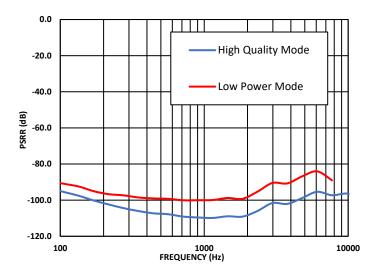

Figure 6. Power Supply Rejection (PSR) vs. Frequency

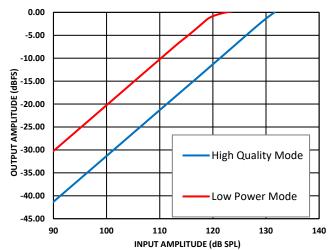

Figure 7. Linearity

## THEORY OF OPERATION

#### **PDM DATA FORMAT**

The output from the DATA pin of the T3903 is in pulse density modulated (PDM) format. This data is the 1-bit output of a fourth-order  $\Sigma$ - $\Delta$  modulator. The data is encoded so that the left channel is clocked on the falling edge of CLK, and the right channel is clocked on the rising edge of CLK. After driving the DATA signal high or low in the appropriate half frame of the CLK signal, the DATA driver of the microphone tristates. In this way, two microphones, one set to the left channel and the other to the right, can drive a single DATA line. See Figure 1 for a timing diagram of the PDM data format; the DATA1 and DATA2 lines shown in this figure are two halves of the single physical DATA signal. Figure 9 shows a diagram of the two stereo channels sharing a common DATA line.

Figure 9. Stereo PDM Format

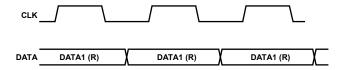

If only one microphone is connected to the DATA signal, the output is only clocked on a single edge (Figure 10). For example, a left channel microphone is never clocked on the rising edge of CLK. In a single microphone application, each bit of the DATA signal is typically held for the full CLK period until the next transition because the leakage of the DATA line is not enough to discharge the line while the driver is tristated.

Figure 10. Mono PDM Format

See Table 9 for the channel assignments according to the logic level on the SELECT pin. The setting on the SELECT pin is sampled at power-up and should not be changed during operation.

#### **TABLE 9. T3903 CHANNEL SETTING**

| SELECT Pin Setting | Channel       |

|--------------------|---------------|

| Low (tie to GND)   | Right (DATA1) |

| High (tie to VDD)  | Left (DATA2)  |

For PDM data, the density of the pulses indicates the signal amplitude. A high density of high pulses indicates a signal near positive full scale, and a high density of low pulses indicates a signal near negative full scale. A perfect zero (dc) audio signal shows an alternating pattern of high and low pulses.

The output PDM data signal has a small dc offset of about 3% of full scale. A high-pass filter in the codec that is connected to the digital microphone and does not affect the performance of the microphone typically removes this dc signal.

#### PDM MICROPHONE SENSITIVITY

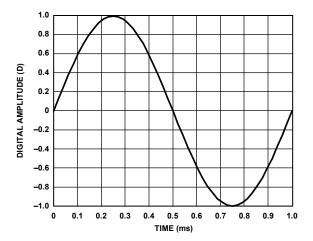

The sensitivity of a PDM output microphone is specified with the unit dB FS (decibels relative to digital full scale). A 0 dB FS sine wave is defined as a signal whose peak just touches the full-scale code of the digital word (see 10). This measurement convention also means that signals with a different crest factor may have an RMS level higher than 0 dB FS. For example, a full-scale square wave has an RMS level of 3 dB FS.

This definition of a 0 dB FS signal must be understood when measuring the sensitivity of the T3903. A 1 kHz sine wave at a 94 dB SPL acoustic input to the T3903 results in an output signal with a -26 dB FS level (low-power mode). The output digital word peaks at -26 dB below the digital full-scale level. A common misunderstanding is that the output has an RMS level of -29 dB FS; however, this is not true because of the definition of the 0 dB FS sine wave.

Figure 11. 1 kHz, 0 dB FS Sine Wave

There is not a commonly accepted unit of measurement to express the instantaneous level, as opposed to the RMS level of the signal, of a digital signal output from the microphone. Some measurement systems express the instantaneous level of an individual sample in units of D, where 1.0 D is digital full scale. In this case, a –26 dB FS sine wave has peaks at 0.05 D.

### APPLICATIONS INFORMATION

#### **LOW-POWER MODE**

Low-Power Mode (LPM) enables the T3903 to be used in an AlwaysOn listening mode for keyword spotting and ambient sound analysis. The T3903 will enter LPM when the frequency of SCK is 768 kHz. In this mode, the microphone consumes only 220  $\mu$ A while retaining high electro-acoustic performance.

When one microphone is in LPM for AlwaysOn listening, a second microphone sharing the same data line may be powered down. In this case, where one microphone is powered up and another is powered down by disabling the VDD supply or in sleep mode by reducing the frequency of a separate clock source, the disabled microphone does not present a load to the signal on the LPM microphone's DATA pin.

#### DYNAMIC RANGE CONSIDERATIONS

The microphone clips (THD = 10%) at 120 dB SPL in Low-Power Mode and at 133 dB SPL in High Quality Mode (see Figure 5); however, it continues to output an increasingly distorted signal above that point. The peak output level, which is controlled by the modulator, limits at 0 dB FS.

To fully use the 105 dB dynamic range of the output data of the T3903 in a design, the digital signal processor (DSP) or codec circuit following it must be chosen carefully. The decimation filter that inputs the PDM signal from the T3903 must have a dynamic range sufficiently better than the dynamic range of the microphone so that the overall noise performance of the system is not degraded. If the decimation filter has a dynamic range of 10 dB better than the microphone, the overall system noise only degrades by 0.4 dB. This 115 dB filter dynamic range requires the filter to have at least 20 bit resolution.

#### **CONNECTING PDM MICROPHONES**

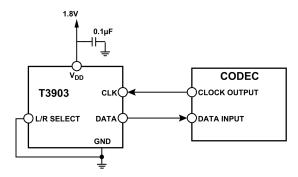

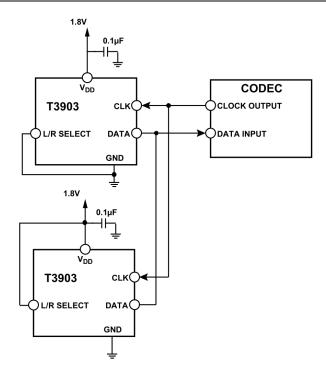

A PDM output microphone is typically connected to a codec with a dedicated PDM input. This codec separately decodes the left and right channels and filters the high sample rate modulated data back to the audio frequency band. This codec also generates the clock for the PDM microphones or is synchronous with the source that is generating the clock. Figure 12 and Figure 13 show mono and stereo connections of the T3903 to a codec. The mono connection shows an T3903 set to output data on the right channel. To output on the left channel, tie the SELECT pin to VDD instead of tying it to GND.

Figure 12. Mono PDM Microphone (Right Channel) Connection to Codec

Figure 13. Stereo PDM Microphone Connection to Codec

Decouple the VDD pin of the T3903 to GND with a 0.1  $\mu$ F capacitor. Place this capacitor as close to VDD as the printed circuit board (PCB) layout allows.

Do not use a pull-up or pull-down resistor on the PDM data signal line because it can pull the signal to an incorrect state during the period that the signal line is tristated.

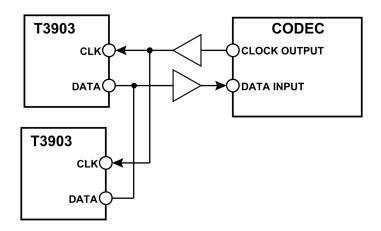

The DATA signal does not need to be buffered in normal use when the T3903 microphone(s) is placed close to the codec on the PCB. If the DATA signal must be driven over a long cable (>15 cm) or other large capacitive load, a digital buffer may be required. Only use a signal buffer on the DATA line when one microphone is in use or after the point where two microphones are connected (see Figure 14). The DATA output of each microphone in a stereo configuration cannot be individually buffered because the two buffer outputs cannot drive a single signal line. If a buffer is used, take care to select one with low propagation delay so that the timing of the data connected to the codec is not corrupted.

Figure 14. Buffered Connections Between Stereo T3903s and a Codec

When long wires are used to connect the codec to the T3903, a source termination resistor can be used on the clock output of the codec instead of a buffer to minimize signal overshoot or ringing. Match the value of this resistor to the characteristic impedance of

the CLK trace on the PCB. Depending on the drive capability of the codec clock output, a buffer may still be needed, as shown in Figure 14.

#### **SLEEP MODE**

The microphone enters sleep mode when the clock frequency falls below 200 kHz. In this mode, the microphone data output is in a high impedance state. The current consumption in sleep mode is  $9 \mu A$ .

The microphone wakes up from sleep mode and begins to output data 7 ms after the clock becomes active. The wake-up time indicates the time from when the clock is enabled to when the T3903 outputs data within 0.5 dB of its settled sensitivity.

#### **START-UP TIME**

The start-up time of the T3903 is typically 7 ms, measured by the time from when power and clock are enabled until sensitivity of the output signal is within 0.5 dB of its settled sensitivity.

# **SUPPORTING DOCUMENTS**

For additional information, see the following documents.

#### **APPLICATION NOTES – GENERAL**

AN-000048, PDM Digital Output MEMS Microphone Flex Evaluation Board User Guide

AN-100, MEMS Microphone Handling and Assembly Guide

AN-1003, Recommendations for Mounting and Connecting the TDK, Bottom-Ported MEMS Microphones

AN-1112, Microphone Specifications Explained

AN-1124, Recommendations for Sealing TDK Bottom-Port MEMS Microphones from Dust and Liquid Ingress

AN-1140, Microphone Array Beamforming

### PCB DESIGN AND LAND PATTERN LAYOUT

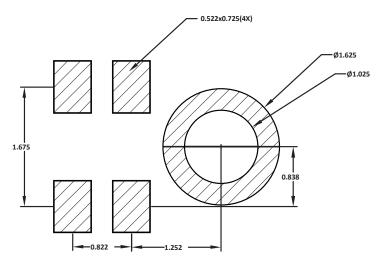

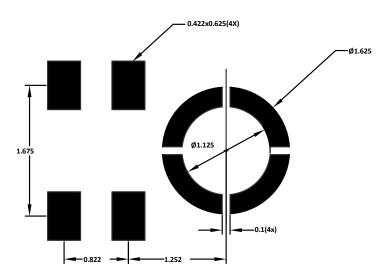

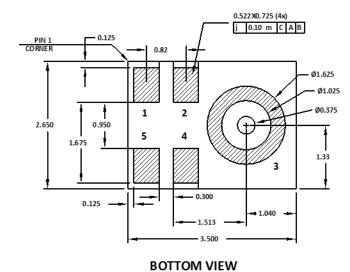

The recommended PCB land pattern for the T3903 is a 1:1 ratio of the solder pads on the microphone package, as shown in Figure 15. Avoid applying solder paste to the sound hole in the PCB. A suggested solder paste stencil pattern layout is shown in Figure 16.

The response of the T3903 is not affected by the PCB hole size as long as the hole is not smaller than the sound port of the microphone (0.375 mm in diameter). A 0.5 mm to 1 mm diameter for the hole is recommended. Take care to align the hole in the microphone package with the hole in the PCB. The exact degree of the alignment does not affect the microphone performance as long as the holes are not partially or completely blocked.

Figure 15. Recommended PCB Land Pattern Layout

Figure 16. Suggested Solder Paste Stencil Pattern Layout

#### **PCB MATERIAL AND THICKNESS**

The performance of the T3903 is not affected by PCB thickness. The T3903 can be mounted on either a rigid or flexible PCB. A flexible PCB with the microphone can be attached directly to the device housing with an adhesive layer. This mounting method offers a reliable seal around the sound port while providing the shortest acoustic path for good sound quality.

### HANDLING INSTRUCTIONS

#### **PICK AND PLACE EQUIPMENT**

The MEMS microphone can be handled using standard pick-and-place and chip shooting equipment. Take care to avoid damage to the MEMS microphone structure as follows:

- Use a standard pickup tool to handle the microphone. Because the microphone hole is on the bottom of the package, the pickup tool can make contact with any part of the lid surface.

- Do not pick up the microphone with a vacuum tool that makes contact with the bottom side of the microphone. Do not pull air out of or blow air into the microphone port.

- Do not use excessive force to place the microphone on the PCB.

#### **REFLOW SOLDER**

For best results, the soldering profile must be in accordance with the recommendations of the manufacturer of the solder paste used to attach the MEMS microphone to the PCB. It is recommended that the solder reflow profile not exceed the limit conditions specified in Figure 2 and Table 7.

#### **BOARD WASH**

When washing the PCB, ensure that water does not make contact with the microphone port. Do not use blow-off procedures or ultrasonic cleaning.

# **OUTLINE DIMENSIONS**

**TOP VIEW**

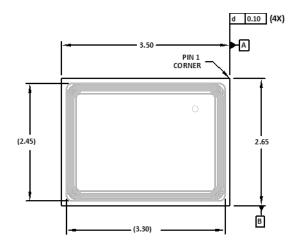

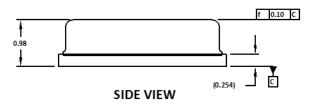

Figure 17. 5-Terminal Chip Array Small Outline No Lead Cavity [LGA\_CAV]  $3.5 \text{ mm} \times 2.65 \text{ mm} \times 0.98 \text{ mm} \text{ Body}$  Dimensions shown in millimeters  $\text{Dimension tolerance is } \pm 0.15 \text{ mm unless otherwise specified}$

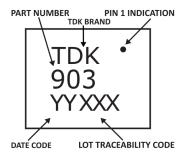

Figure 18. Package Marking Specification (Top View)

#### **ORDERING GUIDE**

| PART             | TEMP RANGE     | PACKAGE            | QUANTITY | PACKAGING         |

|------------------|----------------|--------------------|----------|-------------------|

| MMICT3903-00-012 | -40°C to +85°C | 5-Terminal LGA_CAV | 10,000   | 13" Tape and Reel |

| EV_T3903-FX      | _              | Evaluation Board   | _        |                   |

# **REVISION HISTORY**

| REVISION DATE | REVISION | DESCRIPTION                 |

|---------------|----------|-----------------------------|

| 1/15/20       | 0.1      | Initial preliminary version |

| 5/5/20        | 1.0      | Initial release             |

# COMPLIANCE DECLARATION DISCLAIMER

TDK believes the environmental and other compliance information given in this document to be correct but cannot guarantee accuracy or completeness. Conformity documents substantiating the specifications and component characteristics are on file. TDK subcontracts manufacturing, and the information contained herein is based on data received from vendors and suppliers, which has not been validated by TDK.

This information furnished by TDK, Inc. ("TDK") is believed to be accurate and reliable. However, no responsibility is assumed by TDK for its use, or for any infringements of patents or other rights of third parties that may result from its use. Specifications are subject to change without notice. TDK reserves the right to make changes to this product, including its circuits and software, in order to improve its design and/or performance, without prior notice. TDK makes no warranties, neither expressed nor implied, regarding the information and specifications contained in this document. TDK assumes no responsibility for any claims or damages arising from information contained in this document, or from the use of products and services detailed therein. This includes, but is not limited to, claims or damages based on the infringement of patents, copyrights, mask work and/or other intellectual property rights.

Certain intellectual property owned by TDK and described in this document is patent protected. No license is granted by implication or otherwise under any patent or patent rights of TDK. This publication supersedes and replaces all information previously supplied. Trademarks that are registered trademarks are the property of their respective companies. TDK sensors should not be used or sold in the development, storage, production or utilization of any conventional or mass-destructive weapons or for any other weapons or life threatening applications, as well as in any other life critical applications such as medical equipment, transportation, aerospace and nuclear instruments, undersea equipment, power plant equipment, disaster prevention and crime prevention equipment.

©2020 TDK. All rights reserved. TDK, MotionTracking, MotionProcessing, MotionProcessor, MotionFusion, MotionApps, DMP, AAR, and the TDK logo are trademarks of TDK, Inc. The TDK logo is a trademark of TDK Corporation. Other company and product names may be trademarks of the respective companies with which they are associated.