Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Rev. 5 — 5 May 2021

Product data sheet

### **1** General description

The MPXV7002 series piezoresistive transducers are monolithic silicon pressure sensors. The MPXV7002 is designed for a wide range of applications, particularly applications employing a microcontroller, or microprocessor with analog-to-digital inputs. This transducer combines advanced micromachining techniques, thin-film metallization, and bipolar processing to provide an accurate, high-level analog output signal that is proportional to the applied pressure.

### 2 Features and benefits

- · Ideally suited for microprocessor or microcontroller-based systems

- Thermoplastic (PPS) surface mount package

- Temperature compensated over +10 °C to +60 °C

- Patented silicon shear stress strain gauge

- Available in differential and gauge configurations

### **3** Applications

- Hospital beds

- HVAC

- Respiratory systems

- Process control

### 4 Ordering information

#### Table 1. Ordering information

| Type number | Package |                                                                                                 |           |  |  |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|             | Name    | Description                                                                                     | Version   |  |  |  |  |  |

| MPXV7002DP  | SO8     | Plastic, small outline package, 8 terminals, 2.54 mm pitch, 12.06 mm x 12.06 mm x 7.62 mm body  | SOT1693-1 |  |  |  |  |  |

| MPXV7002GC  | SO8     | Plastic, small outline package, 8 terminals, 2.54 mm pitch, 10.67 mm x 10.67 mm x 12.96 mm body | SOT1854-1 |  |  |  |  |  |

| MPXV7002GP  | SO8     | Plastic, small outline package, 8 terminals, 2.54 mm pitch, 12.06 mm x 12.06 mm x 8.38 mm body  | SOT1693-3 |  |  |  |  |  |

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### 4.1 Ordering options

#### Table 2. Ordering options

| Device name        | Package options                         | ckage SOT | # of Ports |        |      | Pressure type |              |          | Device     |

|--------------------|-----------------------------------------|-----------|------------|--------|------|---------------|--------------|----------|------------|

|                    |                                         | no.       | None       | Single | Dual | Gauge         | Differential | Absolute | marking    |

| Small Outline Pack | Small Outline Package (MPXV7002 Series) |           |            |        |      |               |              |          |            |

| MPXV7002DP         | Trays                                   | SOT1693-1 |            |        | •    |               | •            |          | MPXV7002DP |

| MPXV7002DPT1       | Tape & Reel                             | SOT1693-1 |            |        | •    |               | •            |          | MPXV7002DP |

| MPXV7002GC6U       | Rails                                   | SOT1854-1 |            | •      |      | •             |              |          | MPXV7002G  |

| MPXV7002GP         | Trays                                   | SOT1693-3 |            | •      |      | •             |              |          | MPXV7002G  |

Small outline packages

MPXV7002DP/DPT1 CASE 1351-01 SOT1693-1

### 5 Block diagram

MPXV7002GC6U/C6T1 CASE 482A-01 SOT1854-1

MPXV7002GP CASE 1369-01 SOT1693-3

### **NXP Semiconductors**

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

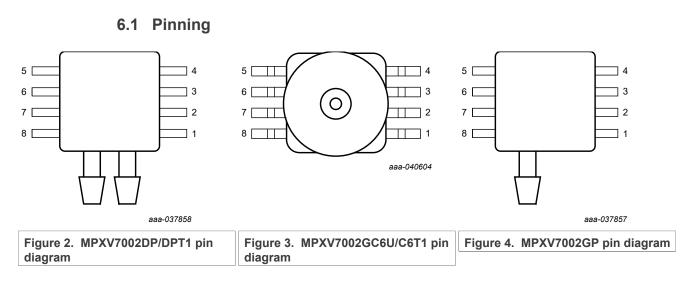

### 6 **Pinning information**

### 6.2 Pin description

This device family uses the style 2 pin configuration documented in <u>Table 3</u> and shown in <u>Figure 10</u>.

#### Table 3. Pin description

| Symbol           | Pin <sup>[1]</sup> | Description      |

|------------------|--------------------|------------------|

| n.c.             | 1                  | _[2]             |

| Vs               | 2                  | Supply voltage   |

| GND              | 3                  | Ground           |

| V <sub>out</sub> | 4                  | Voltage output   |

| n.c.             | 5                  | _[2]             |

| n.c.             | 6                  | _ <sup>[2]</sup> |

| n.c.             | 7                  | _[2]             |

| n.c.             | 8                  | _[2]             |

[1] The notch in the lead indicates pin 1.

[2] Internal device connection. Do not connect to external circuitry or ground

## 7 Maximum Ratings

#### Table 4. Maximum Ratings<sup>[1]</sup>

| Rating                     | Symbol           | Value       | Unit |

|----------------------------|------------------|-------------|------|

| Maximum pressure (P1 > P2) | P <sub>max</sub> | 75          | kPa  |

| Storage temperature        | T <sub>stg</sub> | -30 to +100 | °C   |

| Operating temperature      | T <sub>A</sub>   | 10 to 60    | °C   |

[1] Exposure beyond the specified limits may cause permanent damage or degradation to the device.

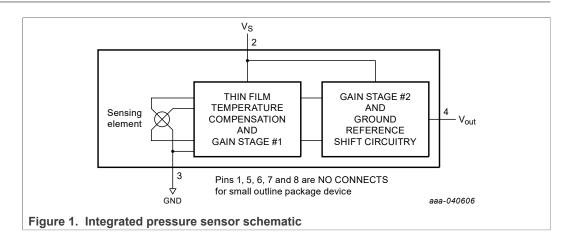

Figure 1 shows a block diagram of the internal circuitry integrated on a pressure sensor chip.

MPXV7002 Product data sheet Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

#### **Operating Characteristics** 8

#### **Table 5. Operating Characteristics**

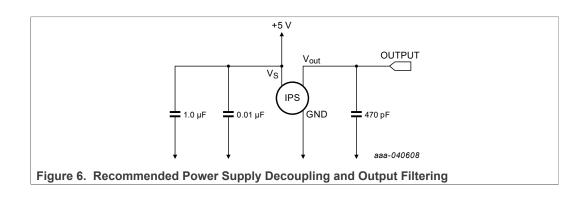

$(V_{\rm S} = 5.0 \text{ Vdc}, T_{\rm A} = 25 \text{ °C} unless otherwise noted. Decoupling circuit shown in Figure 6 required to meet specification.)$

| Characteristic                                                        | Symbol           | Min  | Тур                  | Max    | Unit              |

|-----------------------------------------------------------------------|------------------|------|----------------------|--------|-------------------|

| Pressure rRange <sup>[1]</sup>                                        | P <sub>OP</sub>  | -2.0 |                      | 2.0    | kPa               |

| Supply voltage <sup>[2]</sup>                                         | Vs               | 4.75 | 5.0                  | 5.25   | Vdc               |

| Supply current                                                        | I <sub>o</sub>   | —    | _                    | 10     | mAdc              |

| Pressure offset <sup>[3]</sup> (10 °C to 60 °C) @ $V_S$ = 5.0 Volts   | V <sub>off</sub> | 0.25 | 0.5                  | 0.75   | Vdc               |

| Full scale output <sup>[4]</sup> (10 °C to 60 °C) @ $V_S$ = 5.0 Volts | V <sub>FSO</sub> | 4.25 | 4.5                  | 4.75   | Vdc               |

| Full Scale Span <sup>[5]</sup> (10 °C to 60 °C) @ $V_S$ = 5.0 Volts   | V <sub>FSS</sub> | 3.5  | 4.0                  | 4.5 V  | Vdc               |

| Accuracy <sup>[6]</sup> (10 °C to 60 °C)                              | _                |      | ± 2.5 <sup>[7]</sup> | ± 6.25 | %V <sub>FSS</sub> |

| Sensitivity                                                           | V/P              |      | 1.0                  |        | V/kPa             |

| Response time <sup>[8]</sup>                                          | t <sub>R</sub>   |      | 1.0                  |        | ms                |

| Output source current at full scale output                            | I <sub>O+</sub>  | —    | 0.1                  |        | mAdc              |

| Warm-up time <sup>[9]</sup>                                           | _                | _    | 20                   |        | ms                |

1.0 kPa (kiloPascal) equals 0.145 psi. [1]

[2] [3] Device is ratiometric within this specified excitation range.

Offset (Voff) is defined as the output voltage at the minimum rated pressure.

Full scale output (V<sub>ESO</sub>) is defined as the output voltage at the maximum or full rated pressure.

[4] [5] Full scale span (V<sub>FSS</sub>) is defined as the algebraic difference between the output voltage at full rated pressure and the output voltage at the minimum rated pressure.

[6] Accuracy (error budget) consists of the following:

- · Linearity: Output deviation from a straight-line relationship with pressure over the specified pressure range.

- · Temperature hysteresis: Output deviation at any temperature within the operating temperature range, after the temperature is cycled to and from the minimum or maximum operating temperature points, with zero differential pressure applied.

- · Pressure hysteresis: Output deviation at any pressure within the specified range, when this pressure is cycled to and from the minimum or maximum rated pressure, at 25 °C.

- TcSpan: Output deviation over the temperature range of 10° to 60 °C, relative to 25 °C.

- TcOffset: Output deviation with minimum rated pressure applied, over the temperature range of 10° to 60 °C, relative to 25 °C.

- Variation from Nominal: The variation from nominal values, for offset or full scale span, as a percent of V<sub>FSS</sub>, at 25 °C.

Auto Zero at Factory Installation: Due to the sensitivity of the MPXV7002 Series, external mechanical stresses and mounting position can affect the zero [7] pressure output reading. Auto zero is defined as storing the zero pressure output reading and subtracting this from the device's output during normal operations. Reference AN1636<sup>[1]</sup> for specific information. The specified accuracy assumes a maximum temperature change of ± 5 °C between auto zero and measurement.

Response time is defined as the time for the incremental change in the output to go from 10% to 90% of its final value when subjected to a specified step [8] change in pressure.

[9] Warm-up time is defined as the time required for the product to meet the specified output voltage after the pressure has been stabilized. Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### 9 Characteristics

# 9.1 On-chip temperature compensation, calibration, and signal conditioning

The performance over temperature is achieved by integrating the shear-stress strain gauge, temperature compensation, calibration, and signal conditioning circuitry onto a single monolithic chip.

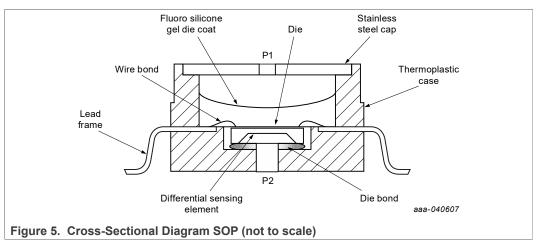

<u>Figure 5</u> illustrates the differential or gauge configuration in the basic chip carrier (Case 482). A fluorosilicone gel isolates the die surface and wire bonds from the environment, while allowing the pressure signal to be transmitted to the sensor diaphragm.

The MPXV7002 series pressure sensor operating characteristics, and internal reliability and qualification tests are based on use of dry air as the pressure media. Media, other than dry air, may have adverse effects on sensor performance and long-term reliability. Contact the factory for information regarding media compatibility in your application.

<u>Figure 6</u> shows the recommended decoupling circuit for interfacing the integrated sensor to the analog-to-digital input of a microprocessor or microcontroller. Proper decoupling of the power supply is recommended.

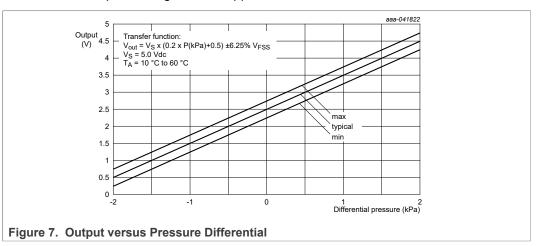

<u>Figure 7</u> shows the sensor output signal relative to pressure input. Typical, minimum, and maximum output curves are shown for operation over a temperature range of 10° to 60° C using the decoupling circuit shown in <u>Figure 6</u>. The output saturates outside the specified pressure range.

MPXV7002 Product data sheet

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

For additional output filtering, refer to Application Note AN1646<sup>[1]</sup>.

### 9.2 Pressure (P1)/Vacuum (P2) Side Identification Table

NXP designates the two sides of the pressure sensor as the Pressure (P1) side and the Vacuum (P2) side. The Pressure (P1) side is the side containing a gel die coat which protects the die from harsh media.

The Pressure (P1) side may be identified by using Table 6.

Table 6. Pressure side identification

| Part Number        | Case Type | Pressure (P1)<br>Side Identifier |

|--------------------|-----------|----------------------------------|

| MPXV7002GC6U/GC6T1 | 482A-01   | Side with Port Attached          |

| MPXV7002GP         | 1369-01   | Side with Port Attached          |

| MPXV7002DP         | 1351-01   | Side with Part Marking           |

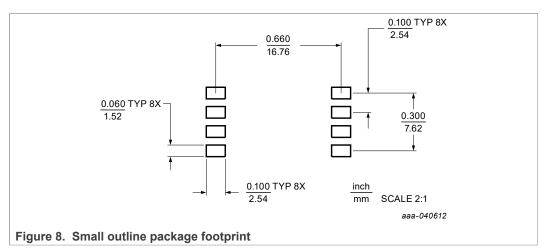

### 9.3 Minimum Recommended Footprint for Surface Mounted Applications

Surface mount board layout is a critical portion of the total design. The footprint for the surface mount packages must be the correct size to ensure proper solder connection interface between the board and the package. With the correct footprint, the packages self-align when subjected to a solder reflow process. NXP recommends designing boards with a solder mask layer to avoid bridging and shorting between solder pads.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

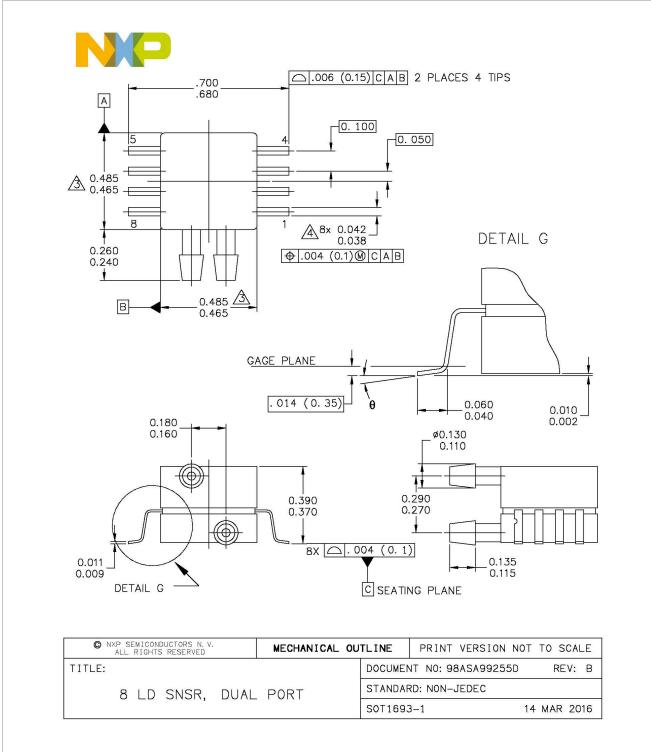

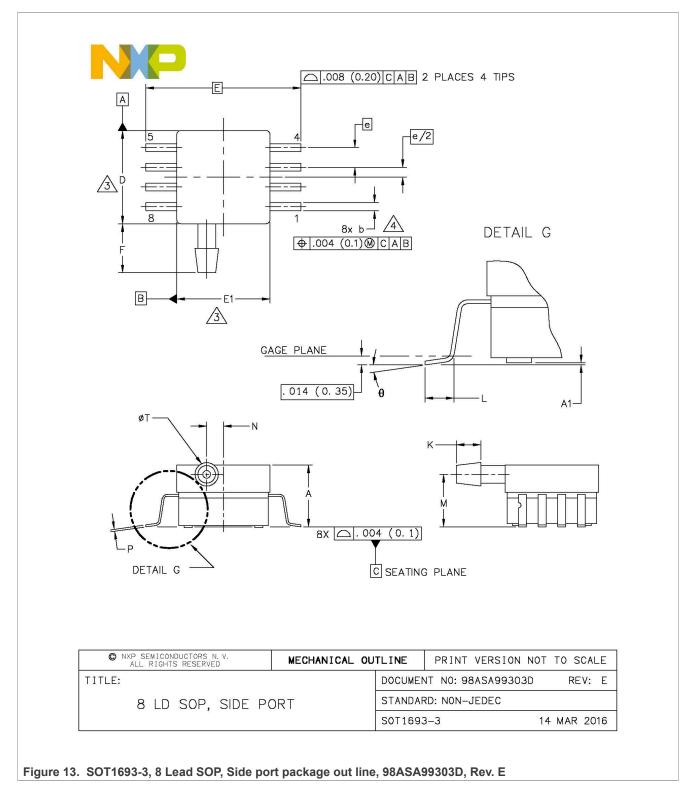

## 10 Package outline

Figure 9. SOT1693-1, 8 Lead sensor, dual port package outline, 98ASA99255D, Rev. B

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

| NP                                                                                       |                                                  |                                                                                      |                                        |

|------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|

| NOTES:                                                                                   |                                                  |                                                                                      |                                        |

| 1. CONTROLLING DIMENSION: INCH                                                           |                                                  |                                                                                      |                                        |

| 2. INTERPRET DIMENSIONS AND TOLI                                                         | ERANCES PER ASME                                 | Y14.5M-                                                                              | 1994.                                  |

| A dimensions do not include ma<br>mold flash and protrusions                             | DLD FLASH OR PPR                                 | TRUSIONS                                                                             | 5.                                     |

| DIMENSION DOES NOT INCLUDE D<br>PROTRUSION SHALL BE .008 MA                              | AMBAR PROTRUSION<br>XIMUM.                       | I. ALLOWA                                                                            | BLE DAMBAR                             |

| STYLE 1:<br>PIN 1:<br>PIN 2:<br>PIN 3:<br>PIN 4:<br>PIN 5:<br>PIN 6:<br>PIN 7:<br>PIN 8: | GND<br>+Vout<br>Vs<br>-Vout<br>N/C<br>N/C<br>N/C | E 2:<br>PIN 1:<br>PIN 2:<br>PIN 3:<br>PIN 4:<br>PIN 5:<br>PIN 6:<br>PIN 7:<br>PIN 8: | Vs<br>GND<br>Vout<br>N/C<br>N/C<br>N/C |

| NXP SEMICONDUCTORS N. V.<br>ALL RIGHTS RESERVED                                          | MECHANICAL OL                                    |                                                                                      | PRINT VERSION NOT TO SCALE             |

| TITLE:                                                                                   | DADT                                             | CONTRACT DESIGNATION                                                                 | NT NO: 98ASA99255D REV: E              |

| 8 LD SNSR, DUAL                                                                          | PORI                                             |                                                                                      | 3-1 14 MAR 2016                        |

Figure 10. SOT1693-1, 8 Lead sensor, dual port package outline notes, 98ASA99255D, Rev. B

Downloaded from Arrow.com.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

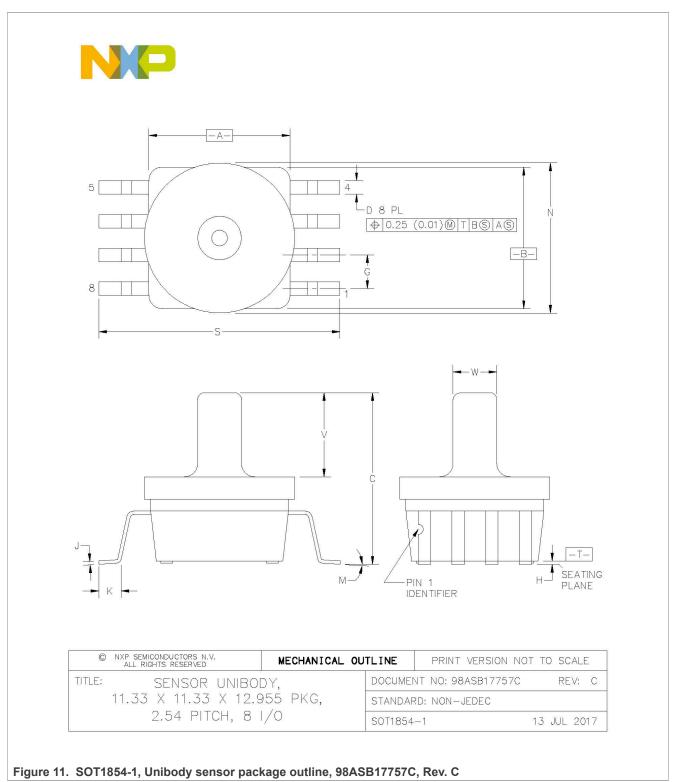

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M-1982.

- 2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION 'A' AND 'B' DO NOT INCLUDE MOLD PROTUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006).

- 5. ALL VERTICAL SURFACES 5' TYPICAL DRAFT.

|                   | INCHES                     |          | MILL    | IMETERS   |           |                    |             |

|-------------------|----------------------------|----------|---------|-----------|-----------|--------------------|-------------|

| DIM               | MIN                        | MAX      | MIN     | MAX       |           |                    |             |

| А                 | 0.415                      | 0.425    | 10.54   | 10.79     |           |                    |             |

| В                 | 0.415                      | 0.425    | 10.54   | 10.79     |           |                    |             |

| С                 | 0.500                      | 0.520    | 12.70   | 13.21     |           |                    |             |

| D                 | 0.038                      | 0.042    | 0.96    | 1.07      |           |                    |             |

| G                 | 0.100                      | BSC      | 2.5     | 4 BSC     |           |                    |             |

| Н                 | 0.002                      | 0.010    | 0.05    | 0.25      |           |                    |             |

| J                 | 0.009                      | 0.011    | 0.23    | 0.28      |           |                    |             |

| К                 | 0.061                      | 0.071    | 1.55    | 1.80      |           |                    |             |

| М                 | 0°                         | 7°       | 0°      | 7°        |           |                    |             |

| N                 | 0.444                      | 0.448    | 11.28   | 11.38     |           |                    |             |

| S                 | 0.709                      | 0.725    | 18.01   | 18.41     |           |                    |             |

| V                 | 0.245                      | 0.255    | 6.22    | 6.48      |           |                    |             |

| W                 | 0.115                      | 0.125    | 2.92    | 3.17      |           |                    |             |

|                   |                            |          |         |           |           |                    |             |

|                   |                            |          |         |           |           |                    |             |

|                   |                            |          |         |           |           | 1                  |             |

| O                 | NXP SEMICOND<br>ALL RIGHTS | RESERVED |         | MECHANICA | L OUTLINE | PRINT VERSION NO   | T TO SCALE  |

| TITLE:            | SE                         | NSOR U   | INIBOD' | Y,        | DOCUME    | NT NO: 98ASB17757C | REV: C      |

|                   | 11.33 X                    |          |         |           | STANDA    | RD: NON-JEDEC      |             |

| 2.54 PITCH, 8 I/O |                            |          |         |           | SOT1854   | L_1                | 13 JUL 2017 |

Figure 12. SOT1854-1, Unibody sensor package outline notes, 98ASB17757C, Rev. C

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

© NXP B.V. 2021. All rights reserved.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

A DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PPROTRUSIONS. MOLD FLASH AND PROTRUSIONS SHALL NOT EXCEED .006 (0.152) PER SIDE.

A DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .008 (0.203) MAXIMUM.

|      | INCHES MILLIMETERS |                                |        | LIMETERS  |     | INCHES MILL |              |          | METERS   |

|------|--------------------|--------------------------------|--------|-----------|-----|-------------|--------------|----------|----------|

| DIM  | MIN                | MAX                            | MIN    | MAX       | DIM | MIN         | MAX          | MIN      | MAX      |

| А    | .300               | .330                           | 7.62   | 8.38      | θ   | 0.          | 7.           | 0.       | 7.       |

| A1   | .002               | .010                           | 0.05   | 0.25      | =   |             |              |          |          |

| ь    | .038               | .042                           | 0.96   | 1.07      | _   |             |              |          |          |

| D    | .465               | .485                           | 11.81  | 12.32     | -   |             |              |          |          |

| E    | .717               | BSC                            | 18     | .21 BSC   | -   |             |              |          |          |

| E1   | .465               | .485                           | 11.81  | 12.32     | -   |             |              |          |          |

| е    | .100               | BSC                            | 2.     | 54 BSC    |     |             |              |          | <u></u>  |

| F    | .245               | .255                           | 6.22   | 6.47      | -   |             |              |          |          |

| К    | .120               | .130                           | 3.05   | 3.30      | -   |             |              |          |          |

| L.   | .061               | .071                           | 1.55   | 1.80      | -   |             |              |          |          |

| м    | .270               | .290                           | 6.86   | 7.36      | -   |             |              |          |          |

| Ν    | .080               | .090                           | 2.03   | 2.28      | -   |             |              |          |          |

| Ρ    | .009               | .011                           | 0.23   | 0.28      | -   |             |              |          |          |

| Т    | .115               | .125                           | 2.92   | 3.17      | -   |             |              |          |          |

|      |                    | ONDUCTORS N. V<br>ITS RESERVED |        | MECHANICA | LOU | TLINE       | PRINT VER    | SION NOT | TO SCALE |

| TITL | _E:                |                                |        |           |     | DOCUMEN     | NT NO: 98ASA | 99303D   | REV: E   |

|      | 8 LC               | ) SOP, S                       | IDE PO | DRT       |     | STANDAR     | RD: NON-JEDE | с        |          |

|      |                    |                                |        |           |     | S0T1693     | 3–3          | 14       | MAR 2016 |

Figure 14. SOT1693-3, 8 Lead SOP, Side port package out line notes, 98ASA99303D, Rev. E

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

## 11 References

[1] AN1646 – Noise considerations for integrated pressure sensors https://www.nxp.com/docs/en/application-note/AN1646.pdf

## **12 Revision History**

| Document ID       | Release Date                                                                                                                                                                                                                                                       | Data sheet status                           | Change notice             | Supercedes        |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|-------------------|--|--|--|--|

| MPXV7002 Rev. 5   | 20210505                                                                                                                                                                                                                                                           | Product                                     | —                         | MPXV7002 Rev. 4   |  |  |  |  |

| Modifications     | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP Semiconductors, N.V. Legal texts have been adapted to the new company name where appropriate.</li> <li>Global changes, revised as follows:</li> </ul> |                                             |                           |                   |  |  |  |  |

|                   | <ul> <li>Revised all images</li> <li>Semiconductor graph</li> </ul>                                                                                                                                                                                                | including the package ou<br>ohic standards. | Itline drawings to comply | with NXP          |  |  |  |  |

|                   | - Performed minor grammar, content, and typographical changes throughout.                                                                                                                                                                                          |                                             |                           |                   |  |  |  |  |

|                   | • <u>Section 1</u> , revised the first paragraph.                                                                                                                                                                                                                  |                                             |                           |                   |  |  |  |  |

|                   | • <u>Section 2</u> , removed two bullets starting with "2.5 % typical" and "6.25 % maximum" from the list of features.                                                                                                                                             |                                             |                           |                   |  |  |  |  |

|                   | • <u>Section 3</u> , added new section.                                                                                                                                                                                                                            |                                             |                           |                   |  |  |  |  |

|                   | <ul> <li><u>Section 4.1</u>, removed row for "MPXV7002GC6T1".</li> </ul>                                                                                                                                                                                           |                                             |                           |                   |  |  |  |  |

|                   | <ul> <li><u>Section 6.2</u>, added clarification stating this device family uses the style 2 pin configuration as<br/>shown in <u>Figure 10</u>.</li> </ul>                                                                                                        |                                             |                           |                   |  |  |  |  |

|                   | <u>Section 9.1</u> , revised "A gel die coat" to "A fluorosilicone gel"                                                                                                                                                                                            |                                             |                           |                   |  |  |  |  |

|                   | <u>Section 10</u> , updated the package information section.                                                                                                                                                                                                       |                                             |                           |                   |  |  |  |  |

|                   | <u>Section 11</u> , added new reference section.                                                                                                                                                                                                                   |                                             |                           |                   |  |  |  |  |

|                   | <ul> <li>Cover page and <u>Section 12</u>, revised data sheet status to use current terminology "Product"<br/>which replaces the term "Technical data" to describe the data sheet status. This change is a<br/>terminlogy update.</li> </ul>                       |                                             |                           |                   |  |  |  |  |

| MPXV7002 Rev. 4   | 2017 March                                                                                                                                                                                                                                                         | Technical data                              | —                         | MPXV7002 Rev. 3.0 |  |  |  |  |

| MPXV7002 Rev. 3.0 | 2015 January                                                                                                                                                                                                                                                       | Technical data                              | —                         | MPXV7002 Rev. 2.0 |  |  |  |  |

| MPXV7002 Rev. 2.0 | 2009 January                                                                                                                                                                                                                                                       | Technical data                              | —                         | MPXV7002 Rev. 1.0 |  |  |  |  |

| MPXV7002 Rev. 1.0 | 2008 September                                                                                                                                                                                                                                                     | Technical data                              | —                         | MPXV7002 Rev. 0   |  |  |  |  |

| MPXV7002 Rev. 0   | 2005 September                                                                                                                                                                                                                                                     | Technical data                              | -                         | —                 |  |  |  |  |

#### Table 7. Revision History

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### 13 Legal information

### 13.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

Please consult the most recently issued document before initiating or completing a design. [1]

[2] [3] The term 'short data sheet' is explained in section "Definitions".

The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### **13.2 Definitions**

Draft — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

### 13.3 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

$\ensuremath{\mathsf{Applications}}\xspace - \ensuremath{\mathsf{Applications}}\xspace - \ensuremath{\mathsf{Applications}}\xspace + \ensuremath{\mathsf{applications}}\x$ products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without

MPXV7002

Product data sheet

#### **NXP Semiconductors**

# **MPXV7002**

## Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 13.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

Tab. 5.

Tab. 6.

Tab. 7.

### **Tables**

| Tab. 1. | Ordering information1 |  |

|---------|-----------------------|--|

| Tab. 2. | Ordering options2     |  |

| Tab. 3. | Pin description3      |  |

|         | Maximum Ratings3      |  |

## **Figures**

| Fig. 1. | Integrated pressure sensor schematic | 2 |

|---------|--------------------------------------|---|

| Fig. 2. | MPXV7002DP/DPT1 pin diagram          | 3 |

| Fig. 3. | MPXV7002GC6U/C6T1 pin diagram        | 3 |

| Fig. 4. | MPXV7002GP pin diagram               | 3 |

| Fig. 5. | Cross-Sectional Diagram SOP (not to  |   |

|         | scale)                               | 5 |

| Fig. 6. | Recommended Power Supply Decoupling  |   |

|         | and Output Filtering                 | 5 |

| Fig. 7. | Output versus Pressure Differential  | 6 |

| Fig. 8. | Small outline package footprint      | 7 |

| Fig. 9. | SOT1693-1, 8 Lead sensor, dual port  |   |

|         | package outline, 98ASA99255D, Rev. B | 8 |

| Fig. 10. | SOT1693-1, 8 Lead sensor, dual port<br>package outline notes, 98ASA99255D, |

|----------|----------------------------------------------------------------------------|

|          | Rev. B9                                                                    |

| Fig. 11. | SOT1854-1, Unibody sensor package                                          |

| -        | outline, 98ASB17757C, Rev. C 10                                            |

| Fig. 12. | SOT1854-1, Unibody sensor package                                          |

|          | outline notes, 98ASB17757C, Rev. C11                                       |

| Fig. 13. | SOT1693-3, 8 Lead SOP, Side port                                           |

| •        | package out line, 98ASA99303D, Rev. E 12                                   |

| Fig. 14. | SOT1693-3, 8 Lead SOP, Side port                                           |

| U        | package out line notes, 98ASA99303D,                                       |

|          | Rev. E                                                                     |

Operating Characteristics ......4

Revision History ......14

Integrated silicon pressure sensor, on-chip signal conditioned, temperature compensated and calibrated

### Contents

| General description               | 1                    |

|-----------------------------------|----------------------|

| Features and benefits             | 1                    |

| Applications                      | 1                    |

| Ordering information              | 1                    |

| Ordering options                  | 2                    |

| Block diagram                     | 2                    |

|                                   |                      |

|                                   |                      |

|                                   |                      |

| Maximum Ratings                   | 3                    |

| -                                 |                      |

| Characteristics                   | 5                    |

| On-chip temperature compensation, |                      |

|                                   | 5                    |

| Pressure (P1)/Vacuum (P2) Side    |                      |

| Identification Table              | 6                    |

| Minimum Recommended Footprint for |                      |

| Surface Mounted Applications      | 6                    |

|                                   |                      |

| References                        | 14                   |

| Revision History                  | 14                   |

|                                   |                      |

|                                   | Identification Table |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 5 May 2021 Document identifier: MPXV7002