### **Features**

- 2 channel integrated analog input Class D audio amplifier in a small 7 x 7 mm PQFN44 package

- No mechanical heatsink required

- High peak music power output

- Split or single power supply

- Differential or single-ended input

- Over-current, over-temperature and under voltage protections with self-reset feature

- Start/stop click noise reduction

- Clip and Fault reporting outputs

- High noise immunity

- RoHS compliant

## **Typical Applications**

- Home theatre systems

- Docking station audio systems

- PC audio systems

- Musical instruments

- Karaoke amplifiers

- Game consoles

- Powered speaker systems

- · General purpose audio power amplifiers

## **Product Summary**

| Topology                                    | Half-Bridge,<br>Full-Bridge |

|---------------------------------------------|-----------------------------|

| IR4302 Output power                         | 130 W/ 4 Ω                  |

| (Typical, THD+N=10%)                        | 100 W/ 3 Ω                  |

| IR4322 Output power                         | 100 W/ 4 Ω                  |

| (Typical, THD+N=10%)                        | 100 W/ 2 Ω                  |

| IR4312 Output power                         | 35 W/ 4 Ω                   |

| (Typical, THD+N=10%)                        | 40 W/ 3 Ω                   |

| *Residual noise<br>(AES-17, IHF-A, typical) | 250 μVrms                   |

| *THD+N<br>(1kHz, 1W, 4 Ω, typical)          | 0.02 %                      |

<sup>\*</sup> In typical application example

## **Package**

7x7mm PQFN44L

## **Typical Connection**

www.irf.com

© 2013 International Rectifier

| Table of Contents                           | Page |

|---------------------------------------------|------|

| Typical Connection Diagram                  | 1    |

| Qualification Information                   | 4    |

| Absolute Maximum Ratings                    | 5    |

| Recommended Operating Conditions            | 7    |

| Electrical Characteristics                  | 8    |

| Functional Block Diagram                    | 11   |

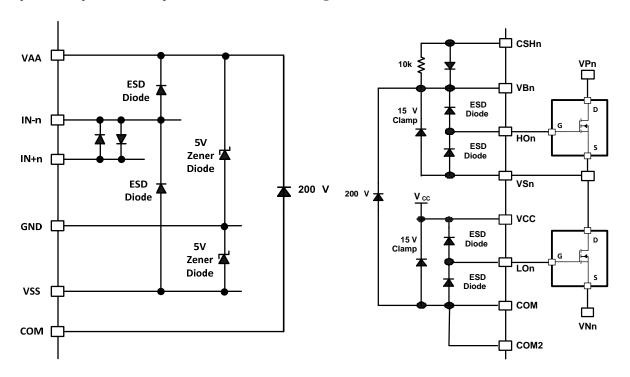

| Input/Output Pin Equivalent Circuit Diagram | 12   |

| Lead Definitions                            | 14   |

| Lead Assignments                            | 15   |

| Package Details                             | 16   |

| Part Marking Information                    | 17   |

| Ordering Information                        | 17   |

## **Description**

The IR43x2 integrates 2 channel PWM controller and digital audio MOSFETs forming a high performance Class D audio amplifier. As a result of fully optimized MOSFETs co-packed with a dedicated controller IC, the IR43X2 operates without mechanical heatsink attached in a typical music playback usage. High voltage ratings and noise immunity in the controller IC ensures reliable operation over various environmental conditions. A small 7x7 mm PQFN package enhances the benefit of smaller size of Class D topology. The IR43X2 series is a lead-free, ROHS compliant.

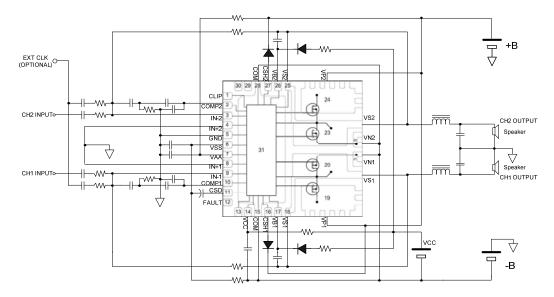

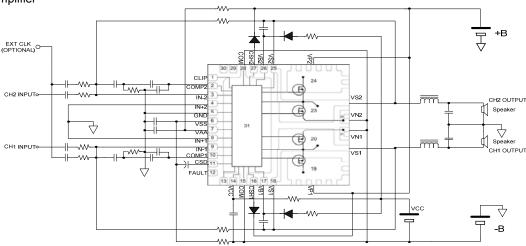

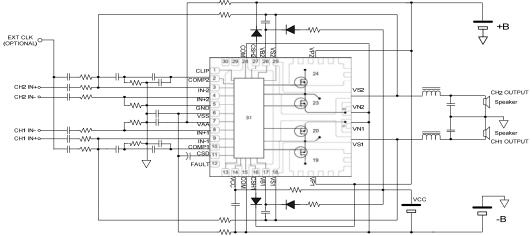

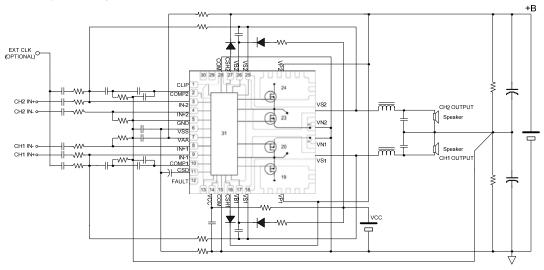

## **Typical Connection Diagram**

### 1. Inverting Amplifier

### 2. Differential Amplifier

www.irf.com

### 3. Single Power Supply (Inverting Amplifier)

## Qualification Information<sup>†</sup>

| <u> Quaiiiioati</u>        | on iniormation   |             |                                                            |  |  |  |

|----------------------------|------------------|-------------|------------------------------------------------------------|--|--|--|

|                            |                  |             | Industrial <sup>††</sup>                                   |  |  |  |

| Qualification              | a Lovel          | Comments: T | Comments: This family of ICs has passed JEDEC's Industrial |  |  |  |

| Qualification              | i Levei          |             | IR's Consumer qualification level is granted by            |  |  |  |

|                            |                  |             | e higher Industrial level.                                 |  |  |  |

| Moisture Sensitivity Level |                  |             | MSL2                                                       |  |  |  |

|                            |                  |             | (per IPC/JEDEC J-STD-020C)                                 |  |  |  |

|                            | Machine Model    |             | Class A                                                    |  |  |  |

|                            | Machine Model    | (           | (per JEDEC standard EIA/JESD22-A115)                       |  |  |  |

|                            |                  | IR4302M     | Class 1B                                                   |  |  |  |

| ESD                        | Human Body Model | IR4322M     | (per EIA/JEDEC standard JESD22-A114)                       |  |  |  |

| ESD                        | Human Body Model | IR4312M     | Class 1A                                                   |  |  |  |

|                            |                  |             | (per EIA/JEDEC standard JESD22-A114)                       |  |  |  |

| IC Latch-Up Test           |                  |             | Class I, Level A                                           |  |  |  |

| ic Laten-up                | 1621             |             | (per JESD78)                                               |  |  |  |

| RoHS Comp                  | liant            |             | Yes                                                        |  |  |  |

- † Qualification standards can be found at International Rectifier's web site http://www.irf.com/

- †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

- ††† Higher MSL ratings may be available for the specific package types listed here. Please contact your International Rectifier sales representative for further information.

www.irf.com

© 2013 International Rectifier

## **Absolute Maximum Ratings**

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM=VN1=VN2; all currents are defined positive into any lead. The Thermal Resistance and Power Dissipation ratings are measured under board mounted and still air conditions.

| Symbol                | Definition                                                                                                            |        | Min                           | Max                  | Units |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|--------|-------------------------------|----------------------|-------|--|

|                       |                                                                                                                       | IR4302 | -                             | 80                   |       |  |

| $V_{Pn}$              | Positive power supply rail voltage, n=1-2                                                                             | IR4322 | -                             | 60                   |       |  |

|                       |                                                                                                                       | IR4312 | -                             | 40                   |       |  |

|                       |                                                                                                                       | IR4302 | -0.3                          | 95                   | 1     |  |

| $V_{Bn}$              | High side floating supply voltage                                                                                     | IR4322 | -0.3                          | 75                   | 1     |  |

|                       |                                                                                                                       | IR4312 | -0.3                          | 55                   | ]     |  |

| $V_{Sn}$              | High side floating supply voltage <sup>††</sup> , n=1-2                                                               |        | $V_{Bn}$ -15                  | V <sub>Bn</sub> +0.3 |       |  |

| $V_{\text{CSHn}}$     | CSH pin input voltage, n=1-2                                                                                          |        | $V_{Sn}$ -0.3                 | V <sub>Bn</sub> +0.3 | V     |  |

| V <sub>CC</sub>       | Low side supply voltage <sup>††</sup>                                                                                 |        | -0.3                          | 15                   | \ \ \ |  |

|                       |                                                                                                                       | IR4302 | -0.3                          | 100                  |       |  |

| $V_{AA}$              | Floating input positive supply voltage <sup>††</sup>                                                                  | IR4322 | -0.3                          | 70                   | 1     |  |

|                       |                                                                                                                       |        | -0.3                          | 50                   |       |  |

| $V_{SS}$              | Floating input negative supply voltage <sup>††</sup>                                                                  |        | -1<br>(See I <sub>SSZ</sub> ) | GND +0.3             |       |  |

| V <sub>IN+n</sub>     | Floating input supply ground voltage , n=1-2                                                                          |        | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 |       |  |

| I <sub>INn</sub>      | Input current between IN- and IN+ pins <sup>†</sup> , n=1-2                                                           |        | -                             | ±3                   | mA    |  |

| $V_{CSD}$             | CSD pin input voltage                                                                                                 |        | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 |       |  |

| $V_{COMPn}$           | COMP pin input voltage, n=1-2                                                                                         |        | V <sub>SS</sub> -0.3          | V <sub>AA</sub> +0.3 | V     |  |

| V <sub>CLIP</sub>     | CLIP pin input voltage                                                                                                |        | GND -0.3                      | V <sub>AA</sub> +0.3 |       |  |

| I <sub>CLIP</sub>     | CLIP pin sinking current                                                                                              |        | -                             | 5                    | mA    |  |

| V <sub>FAULT</sub>    | FAULT pin input voltage                                                                                               |        | GND -0.3                      | V <sub>AA</sub> +0.3 | V     |  |

| I <sub>FAULT</sub>    | FAULT pin sinking current                                                                                             |        | -                             | 5                    |       |  |

| I <sub>AAZ</sub>      | Floating input supply zener clamp current <sup>††</sup>                                                               |        | -                             | 20                   | 1     |  |

| I <sub>SSZ</sub>      | Floating input negative supply zener clamp current                                                                    | †      | -                             | 20                   | mA    |  |

| I <sub>CCZ</sub>      | Low side supply zener clamp current ttt                                                                               |        | -                             | 20                   | 1     |  |

| I <sub>BSZn</sub>     | Floating supply zener clamp current <sup>†††</sup> , n=1-2                                                            |        | -                             | 20                   |       |  |

| dV <sub>Sn</sub> /dt  | Allowable Vs voltage slew rate, n=1-2                                                                                 |        | -                             | 50                   | V/ns  |  |

| dV <sub>SS</sub> /dt  | Allowable Vss voltage slew rate <sup>†††</sup>                                                                        |        | -                             | 50                   | V/ms  |  |

|                       |                                                                                                                       | IR4302 |                               | 6.5                  |       |  |

| Id <sub>@ 25°C</sub>  | Continuous output current, from VPn to VSn, VSn                                                                       | IR4322 | -                             | 7.0                  |       |  |

|                       | to VNn, $V_{CC}=10V$ , $V_{Bn}-V_{Sn}=10V$                                                                            | IR4312 |                               | 3.6                  | 1     |  |

|                       | Continuous output current from VPn to VSn VSn                                                                         | IR4302 |                               | 5.4                  |       |  |

| Id <sub>@ 100°C</sub> | $Id_{@ 100^{\circ}C}$ Continuous output current, from VPn to VSn, VSr to VNn, $V_{CC}$ =10V, $V_{Bn}$ - $V_{Sn}$ =10V |        | -                             | 5.8                  | A     |  |

|                       |                                                                                                                       | IR4312 |                               | 2.9                  | _ ^   |  |

|                       | Pulsed output current, from VPn to VSn, VSn to                                                                        | IR4302 |                               | 26                   |       |  |

| $I_{DM}$              | VNn, $V_{CC}$ =10V, $V_{Bn}$ - $V_{Sn}$ =10V <sup>†††††</sup>                                                         | IR4322 | -                             | 28                   | ]     |  |

|                       | , 50 , 5n on -                                                                                                        | IR4312 |                               | 15                   |       |  |

|                   |                                                                              |        |     | 25  |      |

|-------------------|------------------------------------------------------------------------------|--------|-----|-----|------|

| Pd                | Power dissipation <sup>††††</sup> @ T <sub>C</sub> = 25°C                    | IR4322 | -   | 25  | W    |

|                   |                                                                              | IR4312 |     | 8   | VV   |

|                   |                                                                              | IR4302 |     | 5   |      |

| $Rth_{JC}$        | Rth <sub>JC</sub> Thermal resistance, junction to ambient Thermal resistance |        | -   | 5   | °C/W |

|                   |                                                                              | IR4312 |     | 14  | C/VV |

| T <sub>JIC</sub>  | Control IC junction temperature                                              |        | -   | 150 |      |

| T <sub>JFET</sub> | FET junction temperature                                                     |        | -   | 150 | °C   |

| Ts                | Storage Temperature                                                          |        | -55 | 150 |      |

| TL                | Lead temperature (Soldering, 10 seconds)                                     |        | -   | 300 |      |

- † IN- and IN+ contain clamping diodes between the two pins.

- V<sub>AA</sub> -V<sub>SS</sub>, Vcc-COM and VBn-VSn contain internal shunt zener diodes. Note that the voltage †† ratings of these can be limited by the clamping current.

For the rising and falling edges of step signal of 10V. Vss=15V to 200V.

- †††

- †††† Per MOSFET

- Repetitive rating, pulse width limited by max. junction temperature **††††**†

## **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions below. The Vss and Vsn offset ratings are tested with supplies biased at COM=VN1=VN2,  $V_{AA}$ - $V_{SS}$ =9.6V,  $V_{CC}$ =12V and  $V_{Bn}$ - $V_{Sn}$ =12V. All voltage parameters are absolute voltages referenced to COM; all currents are defined positive into any lead.

| Symbol                                           | Definition                                                   |                 | Min                   | Max                   | Units |

|--------------------------------------------------|--------------------------------------------------------------|-----------------|-----------------------|-----------------------|-------|

|                                                  |                                                              | IR4302          | -                     | 46                    |       |

|                                                  | Positive power supply voltage, n=1-2, without heatsink       | IR4322          | -                     | 46                    |       |

|                                                  |                                                              |                 | -                     | 32                    |       |

| <b>v</b> <sub>Pn</sub>                           | D '''                                                        | IR4302          | -                     | 62                    |       |

| Positive power supply voltage, n=1-2, w heatsink |                                                              | IR4322          | -                     | 50                    |       |

| neat                                             | Todal IIII                                                   | IR4312          | -                     | 32                    |       |

| $V_{Bn}$                                         | High side floating supply absolute voltage, n=1-2            |                 | V <sub>Sn</sub> +10   | V <sub>Sn</sub> +14   |       |

|                                                  |                                                              | IR4302          | †                     | 80                    |       |

| $V_{Sn}$                                         | High side floating supply offset voltage, n=1-2              |                 | †                     | 60                    | V     |

|                                                  |                                                              |                 | †                     | 40                    |       |

| $V_{AA}$                                         | Floating input positive supply voltage <sup>††</sup>         |                 | V <sub>SS</sub> + 4.5 | V <sub>SS</sub> + 15  |       |

| V <sub>SS</sub>                                  | Floating input negative supply voltage <sup>††</sup>         | IR4302          | 0                     | 80                    | -     |

|                                                  |                                                              | IR4322          | 0                     | 60                    |       |

|                                                  |                                                              | IR4312          | 0                     | 40                    |       |

| $I_{AAZ}$                                        | Floating input supply zener clamp current <sup>††</sup>      |                 | 1                     | 15                    | mA    |

| I <sub>SSZ</sub>                                 | Floating input negative supply zener clamp curren            | t <sup>††</sup> | 1                     | 15                    | ША    |

| $V_{CC}$                                         | Low side fixed supply voltage                                |                 | 10                    | 15                    |       |

| $V_{\text{IC}}$                                  | IN- and IN+ pins common mode input voltage                   |                 | V <sub>SS</sub> + 2   | V <sub>AA</sub> - 2   |       |

| $V_{\text{IN-n}}$                                | Inverting input voltage, n=1-2                               |                 | V <sub>IN+</sub> -0.5 | V <sub>IN+</sub> +0.5 | V     |

| $V_{CSD}$                                        | CSD pin input voltage                                        |                 | $V_{SS}$              | $V_{AA}$              |       |

| $V_{\text{COMPn}}$                               | COMP pin input voltage, n=1-2                                |                 | $V_{SS}$              | $V_{AA}$              |       |

| $C_{\text{COMPn}}$                               | COMP pin phase compensation capacitor to GND                 | , n=1-2         | 1                     | -                     | nF    |

| $V_{\text{CSHn}}$                                | CSH pin input voltage, n=1-2                                 |                 | $V_{Sn}$              | $V_{Bn}$              | V     |

| dVss/dt                                          | Allowable Vss voltage slew rate upon power-up <sup>†††</sup> |                 | -                     | 50                    | V/ms  |

| f <sub>SW</sub>                                  | Switching Frequency                                          |                 | -                     | 500                   | kHz   |

| T <sub>A</sub>                                   | Ambient Temperature                                          |                 | -40                   | 100                   | °C    |

Logic operational for Vs equal to -5V to +80V. Logic state held for Vs equal to -5V to  $-V_{BS}$ .

*T* ††

† GND input voltage is limited by  $I_{AAZ}$  and  $I_{SSZ}$ .

††† Vss ramps up from 0V to 70V.

## **Electrical Characteristics**

$V_{CC}$ ,  $V_{BS}$ = 12 V,  $V_{SS}$ = $V_{S1}$ = $V_{S2}$ = $V_{N1}$ = $V_{N2}$ =COM=0V,  $V_{AA}$ =9.6V and  $V_{AB}$ =25°C unless otherwise specified.

| Symbol                | Definition                                                                               | Min  | Тур      | Max  | Units | Test Conditions                                                         |

|-----------------------|------------------------------------------------------------------------------------------|------|----------|------|-------|-------------------------------------------------------------------------|

| Low Side              |                                                                                          |      | 1 - 7  - | 1    |       |                                                                         |

| UV <sub>CC+</sub>     | Vcc supply UVLO positive threshold                                                       | 8.4  | 8.9      | 9.4  | V     |                                                                         |

| UV <sub>CC</sub> -    | Vcc supply UVLO negative threshold                                                       | 8.2  | 8.7      | 9.2  | V     |                                                                         |

| UV <sub>CCHYS</sub>   | UV <sub>CC</sub> hysteresis                                                              | -    | 0.2      | -    | V     |                                                                         |

| I <sub>QCC</sub>      | Low side quiescent current                                                               | _    | -        | 3    | mA    |                                                                         |

| I <sub>CC</sub>       | Low side supply current                                                                  | _    | 10       | -    | mA    | f=400kHz                                                                |

| $V_{CLAMPL}n$         | Low side zener diode clamp voltage, n=1-2                                                | 14.7 | 15.3     | 16.2 | V     | I <sub>CC</sub> =5mA                                                    |

| High Side             | e Floating Supply                                                                        |      |          |      |       |                                                                         |

| $UV_{BS+n}$           | High side well UVLO positive threshold, n=1-2                                            | 8.0  | 8.5      | 9.0  | V     |                                                                         |

| $UV_{BS-n}$           | High side well UVLO negative threshold, n=1-2                                            | 7.8  | 8.3      | 8.8  | V     |                                                                         |

| UV <sub>BSHYSn</sub>  | UV <sub>BS</sub> hysteresis, n=1-2                                                       | -    | 0.2      | -    | V     |                                                                         |

| $I_{QBSn}$            | High side quiescent current, n=1-2                                                       | -    | -        | 2.4  | mA    |                                                                         |

| $V_{\text{CLAMPHn}}$  | High side zener diode clamp voltage, n=1-2                                               | 14.7 | 15.3     | 16.2 | V     | I <sub>BS</sub> =5mA                                                    |

| Floating              | Input Supply                                                                             | •    |          |      | •     |                                                                         |

| $UV_{AA+}$            | VA+, VA- floating supply UVLO positive threshold from V <sub>SS</sub>                    | 8.2  | 8.7      | 9.2  | V     | V <sub>SS</sub> =0V, GND pin floating                                   |

| UV <sub>AA-</sub>     | VA+, VA- floating supply UVLO negative threshold from V <sub>SS</sub>                    | 7.7  | 8.2      | 8.7  | V     | V <sub>SS</sub> =0V, GND pin floating                                   |

| UV <sub>AAHYS</sub>   | UV <sub>AA</sub> hysteresis                                                              | -    | 0.5      | -    | V     | V <sub>SS</sub> =0V, GND pin floating                                   |

| I <sub>QAA0</sub>     | Floating Input positive quiescent supply current                                         | -    | 1.5      | 3    | mA    | V <sub>AA</sub> =9.6V, V <sub>SS</sub><br>=0V,<br>V <sub>CSD</sub> =VSS |

| I <sub>QAA1</sub>     | Floating Input positive quiescent supply current                                         | -    | 4        | 6    | mA    | V <sub>AA</sub> =9.6V, V <sub>SS</sub><br>=0V,<br>V <sub>CSD</sub> =VAA |

| I <sub>QAA2</sub>     | Floating Input positive quiescent supply current                                         | -    | 5        | 7.5  | mA    | V <sub>AA</sub> =9.6V, V <sub>SS</sub><br>=0V,<br>V <sub>CSD</sub> =GND |

| I <sub>LKM</sub>      | Floating input side to Low side leakage current                                          | -    | -        | 50   | μΑ    | V <sub>AA</sub> =V <sub>SS</sub> =V <sub>GND</sub> =<br>100V            |

| V <sub>CLAMPM+</sub>  | V <sub>AA</sub> floating supply zener diode clamp voltage, positive, with respect to GND | 4.9  | 5.1      | 5.4  | V     | $I_{AA}=5mA,$ $I_{SS}=5mA,$ $V_{GND}=0V,$ $V_{CSD}=VSS$                 |

| V <sub>CLAMPM</sub> - | V <sub>SS</sub> floating supply zener diode clamp voltage, negative, with respect to GND | -5.4 | -5.1     | -4.9 | V     | $I_{AA}=5mA,$ $I_{SS}=5mA,$ $V_{GND}=0V,$ $V_{CSD}=VSS$                 |

| Cumbal               | D 6 13                                                                                                                             |             | 9.0 V and 1                            |     |       |                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------|-----|-------|-------------------------------------------------|

| Symbol               | <b>Definition</b>                                                                                                                  | Min         | Тур                                    | Max | Units | Test Conditions                                 |

|                      | out (V <sub>GND</sub> =0, V <sub>AA</sub> =4.8V, V <sub>SS</sub> =-4.8                                                             |             |                                        | 10  |       |                                                 |

| V <sub>OSn</sub>     | Input offset voltage, n=1-2                                                                                                        | -18         | 0                                      | 18  | mV    |                                                 |

| I <sub>BINn</sub>    | Input bias current, n=1-2                                                                                                          | -           | -                                      | 40  | nA    | C =4 n F                                        |

| GBWn                 | Small signal bandwidth in OTA, n=1-2                                                                                               | -           | 9                                      | -   | MHz   | C <sub>COMP</sub> =1nF,<br>Rf=0                 |

| g <sub>mn</sub>      | OTA transconductance, n=1-2                                                                                                        | -           | 10                                     | -   | mS    | V <sub>IN+</sub> =0V, V <sub>IN-</sub><br>=10mV |

| $G_{Vn}$             | OTA gain, n=1-2                                                                                                                    | 50          | -                                      | -   | dB    |                                                 |

| PWM                  |                                                                                                                                    |             |                                        |     |       |                                                 |

| $Vth_{\text{PWM}}$   | PWM comparator threshold in COMP                                                                                                   | -           | (V <sub>AA</sub> - V <sub>SS</sub> )/2 | -   | V     |                                                 |

| f <sub>OTAn</sub>    | COMP pin star-up local oscillation frequency, n=1-2                                                                                | 0.7         | 1.0                                    | 1.5 | MHz   | V <sub>CSD</sub> =GND                           |

| Ton_n                | COMP to VS rising edge propagation delay, n=1-2                                                                                    | -           | 370                                    | -   | ns    |                                                 |

| Toff_n               | COMP to VS trailing edge propagation delay, n=1-2                                                                                  | -           | 320                                    | -   | ns    |                                                 |

| DTn                  | Deadtime: Low-side turn-off to High-side turn-on ( $DT_{LO-HO}$ ) & High-side turn-off to Low-side turn-on ( $DT_{HO-LO}$ ), n=1-2 | -           | 50                                     | -   | ns    | VP=30V,<br>VN=-30V,                             |

| Power MO             | SFET (FET1, FET2, FET3, FET                                                                                                        | 4) (IR4302) |                                        |     |       |                                                 |

| $V_{(BR)DSS}$        | Drain-to-Source breakdown voltage                                                                                                  | 80          | -                                      | -   | V     | V <sub>GS</sub> =0V,<br>I <sub>D</sub> =250uA   |

| R <sub>DS(ON)</sub>  | FET on resistance                                                                                                                  | -           | 39                                     | 50  | mΩ    | V <sub>GS</sub> =10V,<br>I <sub>D</sub> =3.3A   |

| Qg                   | Total gate charge                                                                                                                  | -           | 7.3                                    | -   | nC    |                                                 |

| I <sub>LK0</sub>     | VP leakage current, VS=VN                                                                                                          | -           | -                                      | 20  | μA    | V <sub>P</sub> =80V, V <sub>CSD</sub>           |

| I <sub>LK1</sub>     | VP leakage current, VS=VP                                                                                                          | -           | -                                      | 50  | μA    | =VSS                                            |

|                      | SFET (FET1, FET2, FET3, FET                                                                                                        | 4) (IR4322) |                                        |     |       |                                                 |

| V <sub>(BR)DSS</sub> | Drain-to-Source breakdown voltage                                                                                                  | 60          | _                                      | -   | V     | V <sub>GS</sub> =0V,<br>I <sub>D</sub> =250uA   |

| R <sub>DS(ON)</sub>  | FET on resistance                                                                                                                  | -           | 30                                     | 40  | mΩ    | V <sub>GS</sub> =10V,<br>I <sub>D</sub> =3.3A   |

| Qg                   | Total gate charge                                                                                                                  | -           | 8.3                                    | -   | nC    | _                                               |

| I <sub>LK0</sub>     | VP leakage current, VS=VN                                                                                                          | -           | -                                      | 20  | μΑ    | V <sub>P</sub> =60V, V <sub>CSD</sub>           |

| I <sub>LK1</sub>     | VP leakage current, VS=VP                                                                                                          | -           | -                                      | 50  | μA    | =VSS                                            |

| Power MO             | SFET (FET1, FET2, FET3, FET                                                                                                        | 4) (IR4312) |                                        |     |       |                                                 |

| $V_{(BR)DSS}$        | Drain-to-Source breakdown voltage                                                                                                  | 40          | _                                      | -   | V     | V <sub>GS</sub> =0V,<br>I <sub>D</sub> =250uA   |

| R <sub>DS(ON)</sub>  | FET on resistance                                                                                                                  | -           | 44                                     | 56  | mΩ    | I <sub>D</sub> =3.6A                            |

| Qg                   | Total gate charge                                                                                                                  | -           | 4.5                                    | -   | nC    | V <sub>GS</sub> =10V                            |

| I <sub>LK0</sub>     | VP leakage current, VS=VN                                                                                                          | -           | -                                      | 20  | μA    | V <sub>P</sub> =40V, V <sub>CSD</sub><br>=VSS   |

| I <sub>LK1</sub>     | VP leakage current, VS=VP                                                                                                          | -           | -                                      | 50  | μA    |                                                 |

## **Electrical Characteristics (cont'd)**

$V_{CC}$ ,  $V_{BS}$ = 12 V,  $V_{SS}$ = $V_{S1}$ = $V_{S2}$ = $V_{N1}$ = $V_{N2}$ = $V_{N2}$ = $V_{N2}$ = $V_{N2}$ = $V_{N3}$ = $V_{N2}$ = $V_{N3}$ = $V_{N2}$ = $V_{N3}$ = $V_$

| Symbol               | Definition                                                                             | Min                  | Тур                  | Max                  | Units      | Test Conditions             |

|----------------------|----------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------------|-----------------------------|

| Protection           |                                                                                        |                      | . , , ,              |                      | <b>C</b> c |                             |

| I <sub>OCPn</sub>    | Over current detection Positive threshold, n=1-2                                       | -                    | 16                   | -                    | А          |                             |

| I <sub>OCNn</sub>    | Over current detection Negatitive threshold, n=1-2                                     | -                    | -16                  | -                    | А          |                             |

| Vth1                 | CSD pin shutdown release threshold                                                     | 0.62xV <sub>AA</sub> | 0.70xV <sub>AA</sub> | 0.78xV <sub>AA</sub> | V          |                             |

| Vth2                 | CSD pin self reset threshold                                                           | $0.26xV_{AA}$        | $0.30xV_{AA}$        | $0.34xV_{AA}$        | V          |                             |

| I <sub>CSD+</sub>    | CSD pin discharge current                                                              | 70                   | 100                  | 130                  | μA         | $V_{CSD} = V_{SS} + 4.8V$   |

| I <sub>CSD-</sub>    | CSD pin charge current                                                                 | 70                   | 100                  | 130                  | μA         | $V_{CSD} = V_{SS}$<br>+4.8V |

| t <sub>SDn</sub>     | Shutdown propagation delay from $V_S$ < Vth1 to Shutdown, n=1-2                        | -                    | -                    | 250                  | ns         | COMP = V <sub>SS</sub>      |

| t <sub>OCPn</sub>    | CHn propagation delay time from I <sub>On</sub> > I <sub>OCPn</sub> to Shutdown, n=1-2 | -                    | -                    | 500                  | ns         | COMP = V <sub>SS</sub>      |

| t <sub>OCNn</sub>    | CHn propagation delay time from I <sub>On</sub> < I <sub>OCNn</sub> to Shutdown, n=1-2 | -                    | -                    | 500                  | ns         | COMP = V <sub>SS</sub>      |

| Vth+ <sub>CLIP</sub> | Clip detection positive threshold in COMP                                              | 0.85xV <sub>AA</sub> | 0.90xV <sub>AA</sub> | 0.95xV <sub>AA</sub> | V          |                             |

| Vth- <sub>CLIP</sub> | Clip detection negative threshold in COMP                                              | 0.05xV <sub>AA</sub> | 0.10xV <sub>AA</sub> | 0.15xV <sub>AA</sub> | V          |                             |

| t <sub>CLIP</sub>    | Clipping detection propagation delay                                                   | -                    | 40                   | -                    | ns         |                             |

| t <sub>CLIPmin</sub> | Clipping detection minimum output duration                                             | -                    | 3                    | -                    | us         |                             |

| $T_{SD}$             | Over temperature shutdown threshold in controller IC                                   | -                    | 105                  | -                    | °C         |                             |

| T <sub>SDHYS</sub>   | Over temperature shutdown threshold hysteresis                                         | -                    | 7                    | -                    | °C         |                             |

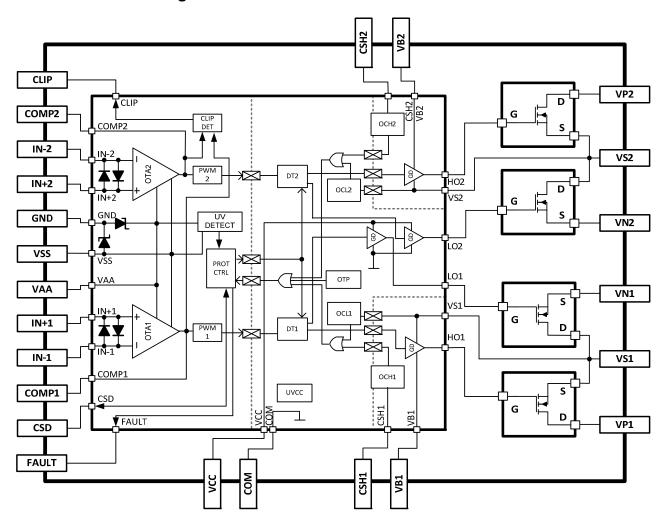

## **Functional Bock Diagram**

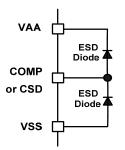

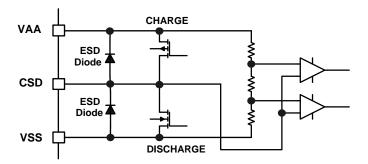

## **Input/Output Pin Equivalent Circuit Diagrams**

# Input/Output Pin Equivalent Circuit Diagrams (Cont'd)

## **Lead Definitions**

| Pin # | Symbol | Description                                                 |

|-------|--------|-------------------------------------------------------------|

| 1     | CLIP   | Clipping detection output, open drain, referenced to GND    |

| 2     | COMP2  | CH2 PWM comparator input                                    |

| 3     | IN-2   | CH2 Analog inverting input                                  |

| 4     | IN+2   | CH2 Analog non-inverting input                              |

| 5     | GND    | GND for internal shunt zener diodes to VAA and VSS          |

| 6     | VSS    | Floating input negative supply                              |

| 7     | VAA    | Floating input positive supply                              |

| 8     | IN+1   | CH1 Analog non-inverting input                              |

| 9     | IN-1   | CH1 Analog inverting input                                  |

| 10    | COMP1  | CH1 PWM comparator input                                    |

| 11    | CSD    | Shutdown timing capacitor / shutdown input                  |

| 12    | FAULT  | Fault reporting output, open drain, referenced to GND       |

| 13    | NC     |                                                             |

| 14    | VCC    | Low side supply                                             |

| 15    | COM    | Low side supply return, internally connected to pin 31      |

| 16    | CSH1   | CH1 High side over current sensing input, referenced to VS1 |

| 17    | VB1    | CH1 High side floating supply                               |

| 18    | VS1    | CH1 PWM output, internally connected to pin 20              |

| 19    | VP1    | CH1 Positive power supply                                   |

| 20    | VS1    | CH1 PWM output                                              |

| 21    | VN1    | CH1 Negative power supply, connect to COM externally        |

| 22    | VN2    | CH2 Negative power supply, connect to COM externally        |

| 23    | VS2    | CH2 PWM output, internally connected to pin 25              |

| 24    | VP2    | CH2 Positive power supply                                   |

| 25    | VS2    | CH2 PWM output                                              |

| 26    | VB2    | CH2 High side floating supply                               |

| 27    | CSH2   | CH2 High side over current sensing input, referenced to VS2 |

| 28    | COM    | Low side supply return, internally connected to pin 31      |

| 29    | NC     |                                                             |

| 30    | NC     |                                                             |

|       |        |                                                             |

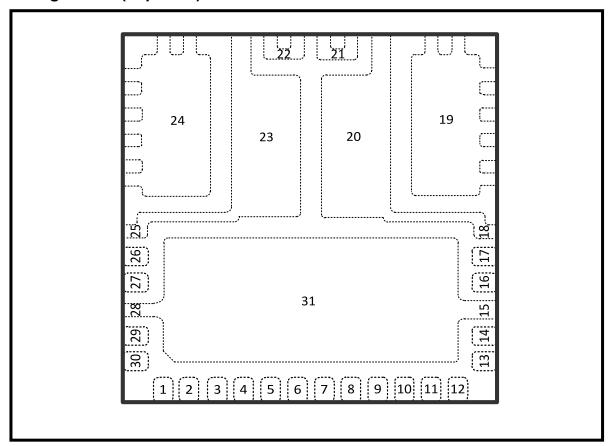

# **Lead Assignments (Top View)**

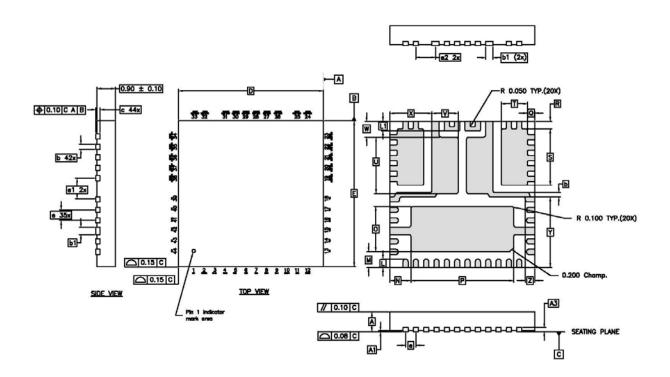

# **Package Details**

| 200 | MILLIM | ETERS      | INCH  | IES   |

|-----|--------|------------|-------|-------|

| DIM | MIN    | MAX        | MIN   | MAX   |

| A   | 0.80   | 1.00       | .032  | .039  |

| -A1 | 0.00   | 0.05       | .0000 | .0020 |

| A3  | 0.20   | REF        | 0.00  | REF   |

| ь   | 0.18   | 0.30       | .0071 | .0118 |

| ь1  | 0.30   | 0.40       | .0118 | .0157 |

| D   | 7.00 E | BASIC      | .276  | BASIC |

| E   | 7.00 E | 7.00 BASIC |       | BASIC |

| L   | 0.30   | 0.50       | .0118 | .0197 |

| L1  | 0.35   | 0.55       | .0138 | .0217 |

| •   | 0.50 E | BASIC      | .0197 | BASIC |

| e1  | 1.00 E | 1.00 BASIC |       | BASIC |

| e2  | 0.95 E | BASIC      | .0374 | BASIC |

| M   | 0.65   | 0.85       | .0256 | .0335 |

| N   | 0.91   | 1.11       | .0358 | .0437 |

| 0   | 2.06   | 2.26       | .0811 | .0890 |

| Р   | 4.88   | 5.08       | .1921 | .2000 |

| Q | 0.25 | 0.45 | .0098 | .0177 |

|---|------|------|-------|-------|

| R | 0.25 | 0.45 | .0098 | .0177 |

| s | 2.62 | 2.82 | .1031 | .1110 |

| T | 1.17 | 1.37 | .0461 | .0539 |

| U | 2.62 | 2.82 | .1031 | .1110 |

| ٧ | 1.17 | 1.37 | .0461 | .0539 |

| w | 0.65 | 0.85 | .0256 | .0335 |

| x | 1.92 | 2.12 | .0756 | .0835 |

| Y | 3.27 | 3.47 | .1287 | .1366 |

| z | 0.35 | 0.55 | .0138 | .0217 |

### **Board Mounting Information**

Refer to Application Note AN-1170 Audio Power Quad Flat No-Lead (PQFN) Board Mounting Application Note.

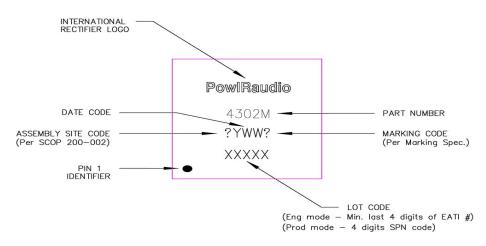

## **Part Marking Information**

## **Ordering Information**

| Base Part Number | Package Type    | Standard Pack |          | Complete Bort Number |

|------------------|-----------------|---------------|----------|----------------------|

|                  |                 | Form          | Quantity | Complete Part Number |

| IR4302M          | PQFN44<br>7x7mm | Tape and Reel | 3000     | IR4302MTRPBF         |

| IR4322M          | PQFN44<br>7x7mm | Tape and Reel | 3000     | IR4322MTRPBF         |

| IR4312M          | PQFN44<br>7x7mm | Tape and Reel | 3000     | IR4312MTRPBF         |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

### **WORLD HEADQUARTERS:**

101 N. Sepulveda Blvd., El Segundo, California 90245 Tel: (310) 252-7105

17 www.irf.com

© 2013 International Rectifier