**Data Sheet**

### FEATURES

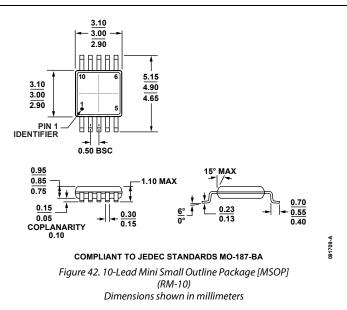

Typical 0.1 µV/°C offset drift Maximum ±200 µV voltage offset over full temperature range 2.7 V to 5.5 V power supply operating range **Electromagnetic interference (EMI) filters included** High common-mode input voltage range -2 V to +70 V, continuous operation -3 V to +80 V, continuous survival Minimum DC common-mode rejection ratio (CMRR): 90 dB Initial gain = 20 V/V Wide operating temperature range AD8418AWB and AD8418AB: -40°C to +125°C AD8418AWH: -40°C to +150°C **Bidirectional operation** Available in 8-lead SOIC\_N, 8-lead MSOP, and FMEA tolerant **10-lead MSOP pinout** AEC-Q100 gualified for automotive applications

### APPLICATIONS

High-side current sensing in Motor controls Solenoid controls Power management Low-side current sensing Diagnostic protection

# Bidirectional, Zero Drift, Current Sense Amplifier

# AD8418A

### **GENERAL DESCRIPTION**

The AD8418A is a high voltage, high resolution current shunt amplifier. It features an initial gain of 20 V/V, with a maximum  $\pm 0.15\%$  gain error over the entire temperature range. The buffered output voltage directly interfaces with any typical converter. The AD8418A offers excellent input common-mode rejection from -2 V to +70 V. The AD8418A performs bidirectional current measurements across a shunt resistor in a variety of automotive and industrial applications, including motor control, power management, and solenoid control.

The AD8418A offers breakthrough performance throughout the –40°C to +150°C temperature range. It features a zero drift core, which leads to a typical offset drift of 0.1  $\mu$ V/°C throughout the operating temperature range and the common-mode voltage range. The AD8418A is qualified for automotive applications. The device includes EMI filters and patented circuitry to enable output accuracy with pulse-width modulation (PWM) type input common-mode voltages. The typical input offset voltage is ±100  $\mu$ V. The AD8418A is offered in an 8-lead MSOP and an 8-lead SOIC\_N package with a 10-lead MSOP pinout option engineered for failure mode and effects analysis (FMEA).

### Table 1. Related Devices

| Part No. | Description                                      |  |

|----------|--------------------------------------------------|--|

| AD8205   | Current sense amplifier, gain = 50               |  |

| AD8206   | Current sense amplifier, gain = 20               |  |

| AD8207   | High accuracy current sense amplifier, gain = 20 |  |

| AD8210   | High speed current sense amplifier, gain = 20    |  |

| AD8417   | High accuracy current sense amplifier, gain = 60 |  |

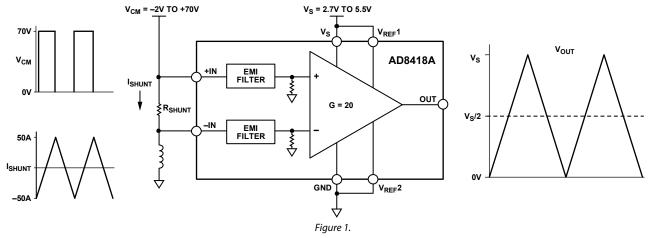

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. E

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013-2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

1883-001

# **TABLE OF CONTENTS**

| Features                                    |

|---------------------------------------------|

| Applications 1                              |

| General Description                         |

| Functional Block Diagram1                   |

| Revision History                            |

| Specifications                              |

| Absolute Maximum Ratings 4                  |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation                         |

| Output Offset Adjustment                    |

| Unidirectional Operation12                  |

### **REVISION HISTORY**

| 6/2020—Rev. D to Rev. E                                   |   |

|-----------------------------------------------------------|---|

| Changes to Features Section and                           |   |

| General Description Section 1                             | L |

| Changes to Figure 2 Caption and Table 4 Title             | 5 |

| Added Figure 3 and Table 5; Renumbered Sequentially       | 5 |

| Added Pinout Option Engineered for FMEA Section, Table 6, |   |

| and Table 7 17                                            | 7 |

| Updated Outline Dimensions                                | ) |

| Changes to Ordering Guide                                 | ) |

### 12/2018-Rev. C to Rev. D

| Changes to Features Section |

|-----------------------------|

| Changes to Table 3 4        |

### 5/2018-Rev. B to Rev. C

| Changes to Input Bias Current Parameter, Table 2 | 3 |

|--------------------------------------------------|---|

| Changes to Figure 20                             | 3 |

|   | Bidirectional Operation           | 12 |

|---|-----------------------------------|----|

|   | External Referenced Output        | 13 |

|   | Splitting the Supply              | 13 |

|   | Splitting an External Reference   | 13 |

| A | pplications Information           | 14 |

|   | Motor Control                     | 14 |

|   | Solenoid Control                  | 15 |

|   | Pinout Option Engineered for FMEA | 16 |

| 0 | utline Dimensions                 | 17 |

|   | Ordering Guide                    | 18 |

|   | Automotive Products               | 18 |

|   |                                   |    |

### 4/2017—Rev. A to Rev. B

| Changes to Features Section and General Description Section | 1 |

|-------------------------------------------------------------|---|

| Changes to Table 2                                          | 3 |

| Changes to Table 3                                          | 4 |

| Change to Figure 18                                         | 8 |

| Added Figure 19 and Figure 20; Renumbered Sequentially      |   |

### 12/2014-Rev. 0 to Rev. A

| Added AD8418AWH                                     | Universal |

|-----------------------------------------------------|-----------|

| Changes to Features Section and General Description | Section1  |

| Changes to Specifications Section and Table 2       | 3         |

| Changes to Table 3                                  | 4         |

| Changes to Ordering Guide                           |           |

11/2013—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A = -40^{\circ}$ C to  $+125^{\circ}$ C (operating temperature range) for the AD8418AWB,  $T_A = -40^{\circ}$ C to  $+150^{\circ}$ C for the AD8418AWH,  $V_S = 5$  V, unless otherwise noted.

| Table 2.                                   | Test Conditions/Comments                                      | Min    | Turn | Max             | Unit   |

|--------------------------------------------|---------------------------------------------------------------|--------|------|-----------------|--------|

| Parameter                                  | Test Conditions/Comments                                      | Min    | Тур  | Max             | Unit   |

| GAIN                                       |                                                               |        | ~~   |                 |        |

| Initial                                    |                                                               |        | 20   | .0.15           | V/V    |

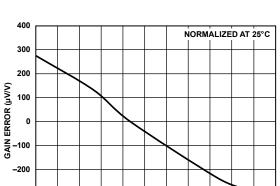

| Error Over Temperature                     | Specified temperature range                                   | _      |      | ±0.15           | %      |

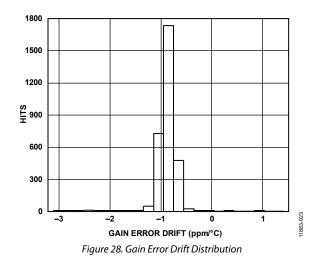

| Gain vs. Temperature                       |                                                               | -5     |      | +5              | ppm/°C |

| VOLTAGE OFFSET                             |                                                               |        |      |                 |        |

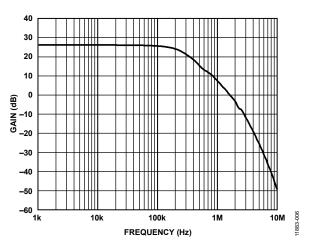

| Offset Voltage, Referred to the Input, RTI | 25°C                                                          |        | ±100 |                 | μV     |

| Over Temperature, RTI                      | Specified temperature range                                   |        |      | ±200            | μV     |

| Offset Drift                               |                                                               | -0.4   | +0.1 | +0.4            | μV/°C  |

| INPUT                                      |                                                               |        |      |                 |        |

| Input Bias Current                         |                                                               |        | 130  |                 | μΑ     |

|                                            | $+IN = -IN = 12 V, V_{REF}1 = V_{REF}2 = 2.5 V,$<br>AD8418AWB |        |      | 260             | μA     |

| Input Voltage Range                        | Common mode, continuous                                       | -2     |      | +70             | V      |

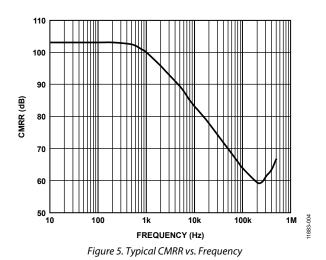

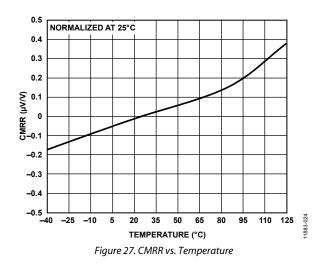

| Common-Mode Rejection Ratio (CMRR)         | Specified temperature range, f = dc                           | 90     | 100  |                 | dB     |

|                                            | f = dc to 10 kHz                                              |        | 86   |                 | dB     |

| OUTPUT                                     |                                                               |        |      |                 |        |

| Output Voltage Range                       | $R_L = 25 \ k\Omega$                                          | 0.032  |      | $V_{s} - 0.032$ | V      |

| Output Resistance                          |                                                               |        | 2    |                 | Ω      |

| Maximum Capacitive Load                    | No continuous oscillation                                     | 0      |      | 500             | pF     |

| DYNAMIC RESPONSE                           |                                                               |        |      |                 |        |

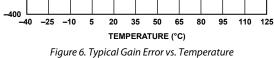

| Small Signal –3 dB Bandwidth               |                                                               |        | 250  |                 | kHz    |

| Slew Rate                                  |                                                               |        | 1    |                 | V/µs   |

| NOISE                                      |                                                               |        |      |                 |        |

| 0.1 Hz to 10 Hz (RTI)                      |                                                               |        | 2.3  |                 | μV p-p |

| Spectral Density, 1 kHz, RTI               |                                                               |        | 110  |                 | nV/√Hz |

| OFFSET ADJUSTMENT                          |                                                               |        |      |                 |        |

| Ratiometric Accuracy <sup>1</sup>          | Divider to supplies                                           | 0.4985 |      | 0.5015          | V/V    |

| Accuracy, Referred to the Output (RTO)     | Voltage applied to $V_{REF}1$ and $V_{REF}2$ in parallel      |        |      | ±1              | mV/V   |

| Output Offset Adjustment Range             | $V_s = 5 V$                                                   | 0.032  |      | $V_{s} - 0.032$ | V      |

| POWER SUPPLY                               |                                                               |        |      |                 |        |

| Operating Range                            |                                                               | 2.7    |      | 5.5             | v      |

| Quiescent Current Over Temperature         | $V_{OUT} = 0.1 V dc$                                          |        |      |                 |        |

| •                                          | AD8418AWB and AD8418AB                                        |        |      | 4.1             | mA     |

|                                            | AD8418AWH                                                     |        |      | 4.2             | mA     |

| Power Supply Rejection Ratio               |                                                               | 80     |      |                 | dB     |

| TEMPERATURE RANGE                          |                                                               |        |      |                 |        |

| For Specified Performance                  | Operating temperature range                                   |        |      |                 |        |

|                                            | AD8418AWB and AD8418AB                                        | -40    |      | +125            | °C     |

|                                            | AD8418AWH                                                     | -40    |      | +150            | °C     |

$^{1}$  The offset adjustment is ratiometric to the power supply when V<sub>REF</sub>1 and V<sub>REF</sub>2 are used as a divider between the supplies.

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                          | Rating            |

|------------------------------------|-------------------|

| Supply Voltage                     | 6 V               |

| Input Voltage Range                |                   |

| Common-Mode                        | −3 V to +80 V     |

| Differential                       | 5.5 V (magnitude) |

| Reverse Supply Voltage             | 0.3 V             |

| ESD Human Body Model (HBM)         | ±2000 V           |

| Operating Temperature Range        |                   |

| AD8418AWB and AD8418AB             | -40°C to +125°C   |

| AD8418AWH                          | -40°C to +150°C   |

| Storage Temperature Range          | –65°C to +150°C   |

| Output Short-Circuit Duration      | Indefinite        |

| SOIC Package                       |                   |

| $\theta_{JA}$ Thermal Resistance   | 127.4°C/W         |

| MSOP Package                       |                   |

| θ <sub>JA</sub> Thermal Resistance | 134.5°C/W         |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

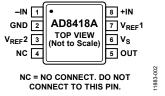

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. 8-lead MSOP and 8-lead SOIC Pin Configuration

### Table 4. 8-lead MSOP and 8-lead SOIC Pin Function Descriptions

| Pin No. | Mnemonic           | Description                             |

|---------|--------------------|-----------------------------------------|

| 1       | -IN                | Negative Input.                         |

| 2       | GND                | Ground.                                 |

| 3       | V <sub>REF</sub> 2 | Reference Input 2.                      |

| 4       | NC                 | No Connect. Do not connect to this pin. |

| 5       | OUT                | Output.                                 |

| 6       | Vs                 | Supply.                                 |

| 7       | V <sub>REF</sub> 1 | Reference Input 1.                      |

| 8       | +IN                | Positive Input.                         |

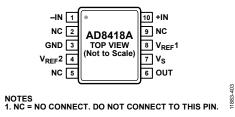

Figure 3. 10-lead MSOP Pin Configuration

### Table 5. 10-lead MSOP Pin Function Descriptions

| Pin No. | Mnemonic           | Description                             |

|---------|--------------------|-----------------------------------------|

| 1       | -IN                | Negative Input.                         |

| 2, 5, 9 | NC                 | No Connect. Do not connect to this pin. |

| 3       | GND                | Ground.                                 |

| 4       | V <sub>REF</sub> 2 | Reference Input 2.                      |

| 6       | OUT                | Output.                                 |

| 7       | Vs                 | Supply.                                 |

| 8       | V <sub>REF</sub> 1 | Reference Input 1.                      |

| 10      | +IN                | Positive Input.                         |

### AD8418A

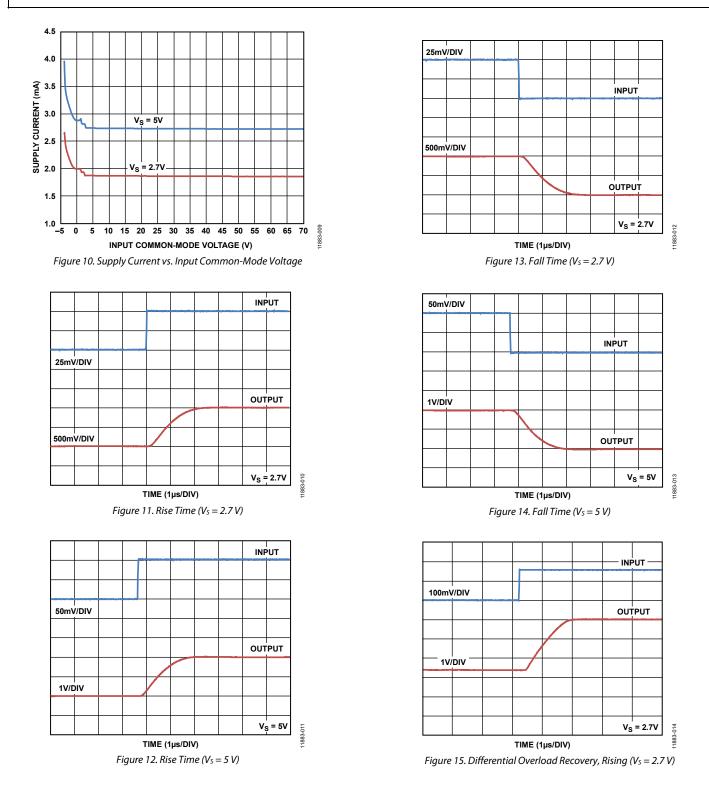

## **TYPICAL PERFORMANCE CHARACTERISTICS**

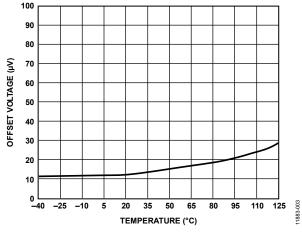

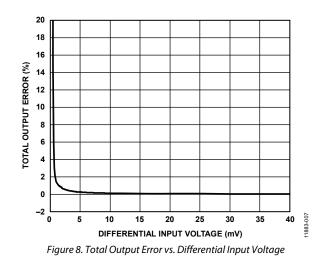

Figure 4. Typical Offset Drift vs. Temperature

Figure 7. Typical Small Signal Bandwidth (Vout = 200 mV p-p)

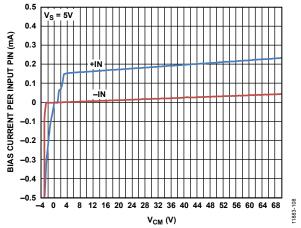

Figure 9. Bias Current per Input Pin vs. Common-Mode Voltage (V<sub>CM</sub>)

1883-005

-300

### **Data Sheet**

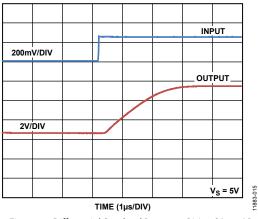

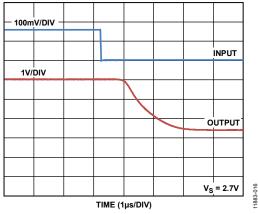

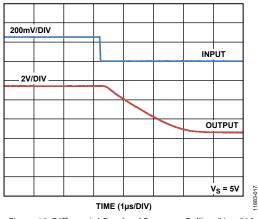

Figure 16. Differential Overload Recovery, Rising ( $V_5 = 5 V$ )

Figure 17. Differential Overload Recovery, Falling ( $V_S = 2.7 V$ )

Figure 18. Differential Overload Recovery, Falling ( $V_S = 5 V$ )

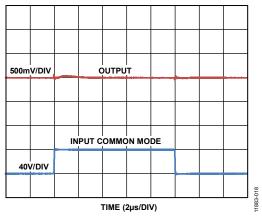

Figure 19. Input Common-Mode Step Response Large Scale (V<sub>S</sub> = 5 V, Inputs Shorted)

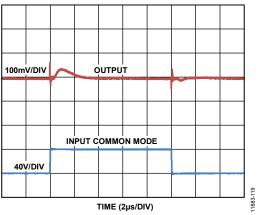

Figure 20. Input Common-Mode Step Response Small Scale (V<sub>S</sub> = 5 V, Inputs Shorted)

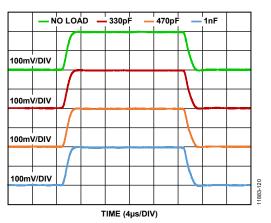

Figure 21. Small Signal Response for Various Capacitive Loads

### **Data Sheet**

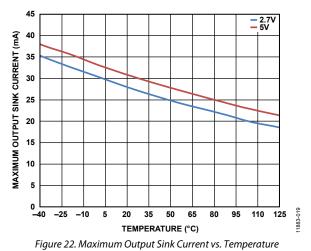

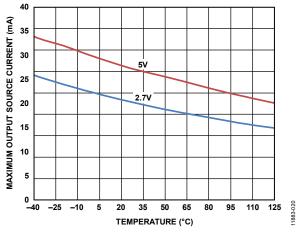

Figure 23. Maximum Output Source Current vs. Temperature

AD8418A

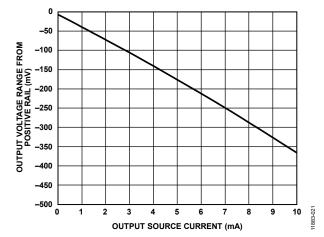

Figure 24. Output Voltage Range from Positive Rail vs. Output Source Current

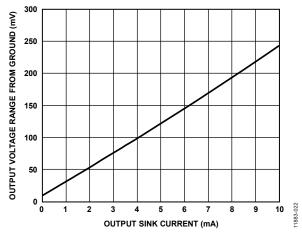

Figure 25. Output Voltage Range from Ground vs. Output Sink Current

# AD8418A

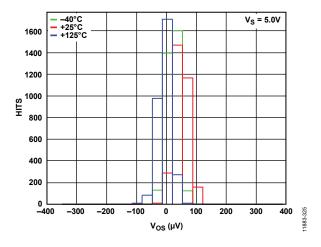

Figure 26. Offset Voltage Distribution

### **THEORY OF OPERATION**

The AD8418A is a single-supply, zero drift, difference amplifier that uses a unique architecture to accurately amplify small differential current shunt voltages in the presence of rapidly changing common-mode voltages.

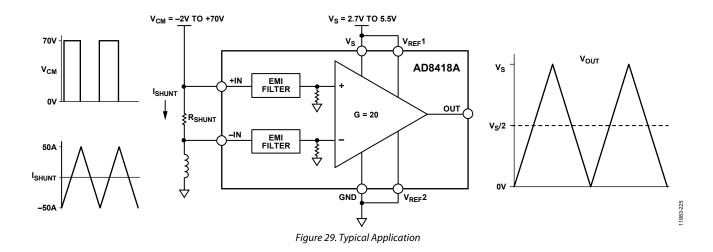

In typical applications, the AD8418A measures current by amplifying the voltage across a shunt resistor connected to its inputs by a gain of 20 V/V (see Figure 29).

The AD8418A design provides excellent common-mode rejection, even with PWM common-mode inputs that can change at very fast rates, for example, 1 V/ns. The AD8418A contains proprietary technology to eliminate the negative effects of such fast changing external common-mode variations.

The AD8418A features an input offset drift of less than 400 nV/°C. This performance is achieved through a novel zero drift architecture that does not compromise bandwidth, which is typically rated at 250 kHz.

The reference inputs,  $V_{REF}1$  and  $V_{REF}2$ , are tied through 100 k $\Omega$  resistors to the positive input of the main amplifier, which allows the output offset to be adjusted anywhere in the output operating range. The gain is 1 V/V from the reference pins to the output when the reference pins are used in parallel. When the pins are used to divide the supply, the gain is 0.5 V/V.

The AD8418A offers breakthrough performance without compromising any of the robust application needs typical of solenoid or motor control. The ability to reject PWM input common-mode voltages and the zero drift architecture providing low offset and offset drift allows the AD8418A to deliver total accuracy for these demanding applications.

### **OUTPUT OFFSET ADJUSTMENT**

The output of the AD8418A can be adjusted for unidirectional or bidirectional operation.

### UNIDIRECTIONAL OPERATION

Unidirectional operation allows the AD8418A to measure currents through a resistive shunt in one direction. The basic modes for unidirectional operation are ground referenced output mode and  $V_S$  referenced output mode.

For unidirectional operation, the output can be set at the negative rail (near ground) or at the positive rail (near VS) when the differential input is 0 V. The output moves to the opposite rail when a correct polarity differential input voltage is applied. The required polarity of the differential input depends on the output voltage setting. If the output is set at the positive rail, the input polarity needs to be negative to decrease the output. If the output is set at ground, the polarity must be positive to increase the output.

### Ground Referenced Output Mode

When using the AD8418A in ground referenced output mode, both referenced inputs are tied to ground, which causes the output to sit at the negative rail when there are zero differential volts at the input (see Figure 30).

Figure 30. Ground Referenced Output

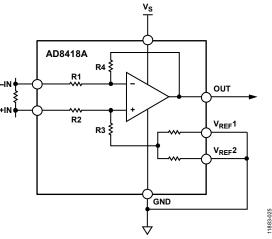

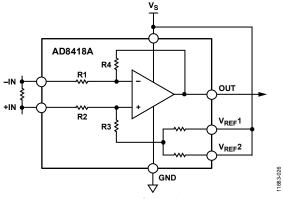

### Vs Referenced Output Mode

$V_s$  referenced output mode is set when both reference pins are tied to the positive supply. It is typically used when the diagnostic scheme requires detection of the amplifier and the wiring before power is applied to the load (see Figure 31).

### **BIDIRECTIONAL OPERATION**

Bidirectional operation allows the AD8418A to measure currents through a resistive shunt in two directions.

In this case, the output is set anywhere within the output range. Typically, it is set at half-scale for equal range in both directions. In some cases, however, it is set at a voltage other than half-scale when the bidirectional current is nonsymmetrical.

Adjusting the output is accomplished by applying voltage(s) to the referenced inputs.  $V_{REF}1$  and  $V_{REF}2$  are tied to internal resistors that connect to an internal offset node. There is no operational difference between the pins.

# AD8418A

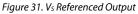

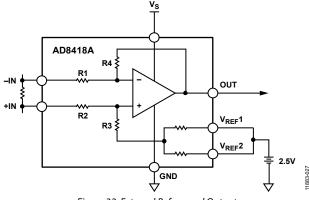

### **EXTERNAL REFERENCED OUTPUT**

Tying  $V_{REF}1$  and  $V_{REF}2$  together and to a reference produces an output equal to the reference voltage when there is no differential input (see Figure 32). The output decreases with respect to the reference voltage when the input is negative, relative to the -IN pin, and increases when the input is positive, relative to the -IN pin.

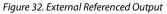

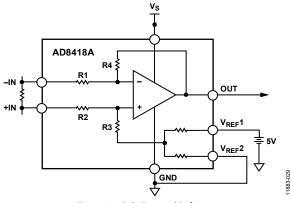

### SPLITTING THE SUPPLY

By tying one reference pin to  $V_s$  and the other to the ground pin, the output is set at half of the supply when there is no differential input (see Figure 33). The benefit of this configuration is that an external reference is not required to offset the output for bidirectional current measurement. Tying one reference pin to  $V_s$ and the other to the ground pin creates a midscale offset that is ratiometric to the supply, which means that if the supply increases or decreases, the output remains at half the supply. For example, if the supply is 5.0 V, the output is at half scale or 2.5 V. If the supply increases by 10% (to 5.5 V), the output increases to 2.75 V.

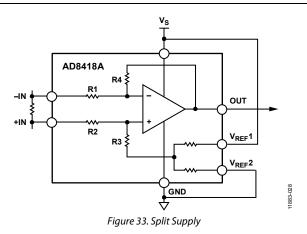

### **SPLITTING AN EXTERNAL REFERENCE**

Use the internal reference resistors to divide an external reference by 2 with an accuracy of approximately 0.5%. Split an external reference by connecting one  $V_{REFX}$  pin to ground and the other  $V_{REFX}$  pin to the reference (see Figure 34).

Figure 34. Split External Reference

### APPLICATIONS INFORMATION motor control

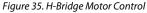

### 3-Phase Motor Control

The AD8418A is ideally suited for monitoring current in 3-phase motor applications.

The 250 kHz typical bandwidth of the AD8418A provides instantaneous current monitoring. Additionally, the typical low offset drift of 0.1  $\mu$ V/°C means that the measurement error between the two motor phases is at a minimum over temperature. The AD8418A rejects PWM input common-mode voltages in the -2 V to +70 V (with a 5 V supply) range. Monitoring the current on the motor phase allows sampling of the current at any point and provides diagnostic information, such as a short to GND and battery. Refer to Figure 36 for the typical phase current measurement setup with the AD8418A.

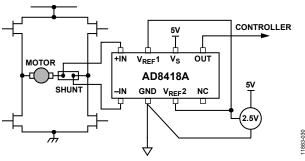

### H-Bridge Motor Control

Another typical application for the AD8418A is to form part of the control loop in H-bridge motor control. In this case, place the shunt resistor in the middle of the H-bridge to accurately measure current in both directions by using the shunt available at the motor (see Figure 35). Using an amplifier and shunt in this location is a better solution than a ground referenced op amp because ground is not typically a stable reference voltage in this type of application. The instability of the ground reference causes inaccuracies in the measurements that can be made with a simple ground referenced op amp. The AD8418A measures current in both directions as the H-bridge switches and the motor changes direction. The output of the AD8418A is configured in an external referenced bidirectional mode (see the Bidirectional Operation section).

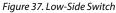

### SOLENOID CONTROL

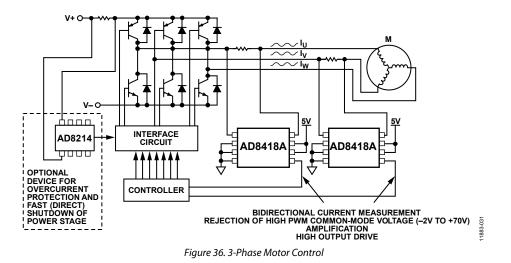

#### High-Side Current Sense with a Low-Side Switch

In the case of a high-side current sense with a low-side switch, the PWM control switch is ground referenced. Tie an inductive load (solenoid) to a power supply and place a resistive shunt between the switch and the load (see Figure 37). An advantage of placing the shunt on the high side is that the entire current, including the recirculation current, is measurable because the shunt remains in the loop when the switch is off. In addition, diagnostics are enhanced because shorts to ground are detected with the shunt on the high side.

In this circuit configuration, when the switch is closed, the common-mode voltage decreases to near the negative rail. When the switch is open, the voltage reversal across the inductive load causes the common-mode voltage to be held one diode drop above the battery by the clamp diode.

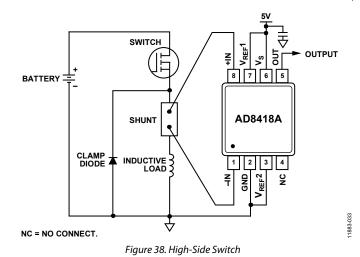

### High-Side Current Sense with a High-Side Switch

The high-side current sense with a high-side switch configuration minimizes the possibility of unexpected solenoid activation and excessive corrosion (see Figure 38). In this case, both the switch and the shunt are on the high side. When the switch is off, the battery is removed from the load, which prevents damage from potential shorts to ground while still allowing the recirculating current to be measured and to provide diagnostics. Removing the power supply from the load for the majority of the time that the switch is open minimizes the corrosive effects that can be caused by the differential voltage between the load and ground.

When using a high-side switch, the battery voltage is connected to the load when the switch is closed, causing the common-mode voltage to increase to the battery voltage. In this case, when the switch is open, the voltage reversal across the inductive load causes the common-mode voltage to be held one diode drop below ground by the clamp diode.

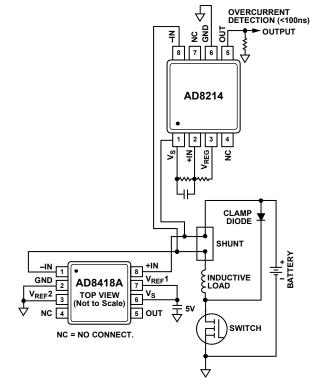

#### High Rail Current Sensing

In the high rail, current sensing configuration, the shunt resistor is referenced to the battery. High voltage is present at the inputs of the current sense amplifier. When the shunt is battery referenced, the AD8418A produces a linear ground referenced analog output. Additionally, the AD8214 provides an overcurrent detection signal in as little as 100 ns (see Figure 39). This feature is useful in high current systems where fast shutdown in overcurrent conditions is essential.

Figure 39. High Rail Current Sensing

1883-034

AD8418A

1883-032

### **PINOUT OPTION ENGINEERED FOR FMEA**

The AD8418A is available in a 10-lead MSOP pinout option engineered for FMEA. This FMEA tolerant pinout is designed to meet stringent automotive requirements and to conditionally survive single faults that are a result of common printed circuit board (PCB) defects, as described in Table 6 and Table 7. NC pins are inserted between -IN and GND, as well as between +IN and  $V_{REF}1$ . These NC pins effectively isolate the voltages at the input pins, which may range from -2 V to +70 V, from adjacent pins that prevent the occurrence of unrecoverable faults.

| Pin Number | Adjacent Pins Shorted      | Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 2       | –IN and NC                 | The circuit behaves normally.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 2, 3       | NC and GND                 | The circuit behaves normally.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 3, 4       | GND and V <sub>REF</sub> 2 | The operating range of $V_{REF}2$ is from GND to $V_s$ . Therefore, shorting $V_{REF}2$ to GND does not<br>represent a fault. For example, if the AD8418A references are configured to split the supply with<br>$V_{REF}2$ tied to GND, the circuit behaves normally. A system error occurs, however, if $V_{REF}2$ is tied<br>either to $V_s$ or to a different external reference because GND is shorted to $V_s$ or to the external<br>reference voltage on the PCB.    |  |

| 4, 5       | V <sub>REF</sub> 2 and NC  | The circuit behaves normally.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 6, 7       | OUT and Vs                 | OUT approaches V <sub>S</sub> voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 7, 8       | Vs and V <sub>REF</sub> 1  | The operating range of $V_{REF}1$ is from GND to $V_s$ . Therefore, shorting $V_{REF}1$ to $V_s$ does not represent<br>a fault. For example, if the AD8418A references are configured to split the supply with $V_{REF}1$ tied<br>to $V_s$ , the circuit behaves normally. A system error occurs, however, if $V_{REF}1$ is tied either to GND<br>or to a different external reference because $V_s$ is shorted to GND or to the external reference<br>voltage on the PCB. |  |

| 8, 9       | V <sub>REF</sub> 1 and NC  | The circuit behaves normally.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 9, 10      | NC and +IN                 | The circuit behaves normally.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

### Table 6. Behavior as a Result of Adjacent Pin to Pin Shorts

#### Table 7. Behavior as a Result of Open Pin, Split Supply Setup (V<sub>REF</sub>1 to V<sub>S</sub> and V<sub>REF</sub>2 to GND), V<sub>S</sub> - 5 V, -IN = +IN = 12 V

| Pin Number | Pin Opened         | Behavior                                                                                                                                          |

|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | -IN                | OUT is undetermined but is limited between GND and Vs.                                                                                            |

| 2          | NC                 | The circuit behaves normally.                                                                                                                     |

| 3          | GND                | The output voltage range is limited to 0.7 V to VS and the device receives the ground through an ESD diode on $V_{REF}2$ .                        |

| 4          | V <sub>REF</sub> 2 | OUT approaches V <sub>s</sub> .                                                                                                                   |

| 5          | NC                 | The circuit behaves normally.                                                                                                                     |

| 6          | OUT                | No OUT signal.                                                                                                                                    |

| 7          | Vs                 | The device is powered through an ESD diode between the $V_{REF}1$ pin and $V_S$ pin. The output voltage range is limited to GND to $V_S - 0.7$ V. |

| 8          | V <sub>REF</sub> 1 | OUT approaches GND.                                                                                                                               |

| 9          | NC                 | The circuit behaves normally.                                                                                                                     |

| 10         | +IN                | OUT is undetermined but is limited between GND and Vs.                                                                                            |

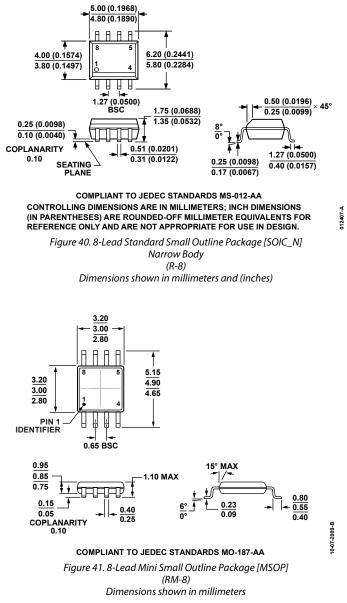

### **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Package Description              | Package Option | Marking Code |

|-----------------------|-------------------|----------------------------------|----------------|--------------|

| AD8418ABRMZ           | -40°C to +125°C   | 8-Lead MSOP                      | RM-8           | Y5J          |

| AD8418ABRMZ-RL        | -40°C to +125°C   | 8-Lead MSOP, 13" Tape and Reel   | RM-8           | Y5J          |

| AD8418AWBRMZ          | -40°C to +125°C   | 8-Lead MSOP                      | RM-8           | Y5G          |

| AD8418AWBRMZ-RL       | -40°C to +125°C   | 8-Lead MSOP, 13" Tape and Reel   | RM-8           | Y5G          |

| AD8418AWBRZ           | -40°C to +125°C   | 8-Lead SOIC_N                    | R-8            |              |

| AD8418AWBRZ-RL        | -40°C to +125°C   | 8-Lead SOIC_N, 13" Tape and Reel | R-8            |              |

| AD8418AWHRZ           | -40°C to +150°C   | 8-Lead SOIC_N                    | R-8            |              |

| AD8418AWHRZ-RL        | -40°C to +150°C   | 8-Lead SOIC_N, 13" Tape and Reel | R-8            |              |

| AD8418AWHRMZ          | -40°C to +150°C   | 8-Lead MSOP                      | RM-8           | Y5H          |

| AD8418AWHRMZ-RL       | -40°C to +150°C   | 8-Lead MSOP, 13" Tape and Reel   | RM-8           | Y5H          |

| AD8418AWBRMZ-10       | -40°C to +125°C   | 10-lead MSOP                     | RM-10          | A3Z          |

| AD8418AWBRMZ-10RL     | -40°C to +125°C   | 10-lead MSOP, 13" Tape and Reel  | RM-10          | A3Z          |

| AD8418AR-EVALZ        |                   | 8-Lead SOIC_N Evaluation Board   |                |              |

| AD8418ARM-EVALZ       |                   | 8-Lead MSOP Evaluation Board     |                |              |

<sup>1</sup> Z = RoHS Compliant Part.

$^{2}$  W = Qualified for Automotive Applications.

### **AUTOMOTIVE PRODUCTS**

The AD8418AW models are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. Note that these automotive models may have specifications that differ from the commercial models; therefore, designers should review the Specifications section of this data sheet carefully. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

©2013–2020 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D11883-6/20(E)

Rev. E | Page 18 of 18

www.analog.com