# 2-Wire Serial I/O Expander and Fan Controller

### **Features**

- Provides Eight Bits of General Purpose I/O

- · Built-In Fan Speed Control Logic (Optional)

- 2-Wire SMBus™/I<sup>2</sup>C™-Compatible Serial Interface plus Interrupt Output

- · 2.7V to 3.6V Operating Voltage Range

- 5V-Tolerant I/O

- Low Quiescent Current: 2 μA (Typical)

- Bit-Programmable I/O Options:

- Input or Output

- Push-Pull or Open-Drain Output

- Interrupt on Input Changes

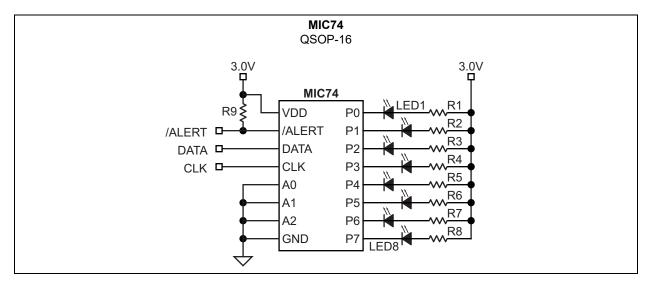

- Outputs can Directly Drive LEDs (10 mA I<sub>OL</sub>)

- · Up to 8 Devices per Bus

#### **Applications**

- · General Purpose I/O Expansion via Serial Bus

- Personal Computer System Management

- · Distributed Sensing and Control

- Microcontroller I/O Expansion

- Fan Control

- · Garage Door Opener and Remote

- · Dip Switch Decoder

### **General Description**

The MIC74 is a fully programmable serial-to-parallel I/O expander compatible with the SMBus™ (system management bus) protocol. It acts as a client on the bus, providing eight independent I/O lines.

Each I/O bit can be individually programmed as an input or output. If programmed as an output; each I/O bit can be programmed as an open-drain or complementary push-pull output. If desired, the four most significant I/O bits can be programmed to implement fan speed control. An internal clock generator and state machine eliminate the overhead generally associated with "bit-banging" fan speed control.

Programming the device and reading/writing the I/O bits is accomplished using seven internal registers. All registers can be read by the host. Output bits are capable of directly driving high-current loads, such as LEDs. A separate interrupt output can notify the host of state changes on the input bits without requiring the MIC74 to perform a transaction on the serial bus or be polled by the host. Three address selection inputs are provided, allowing up to eight devices to share the same bus and provide a total of 64 bits of I/O.

The MIC74 is available in an ultra-small-footprint 16-pin QSOP. Low quiescent current, small footprint, and low package height make the MIC74 ideal for portable and desktop applications.

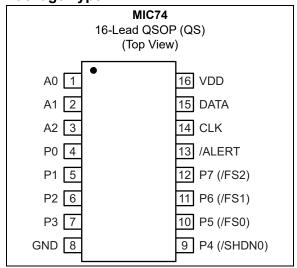

## **Package Type**

# **Typical Application Circuit**

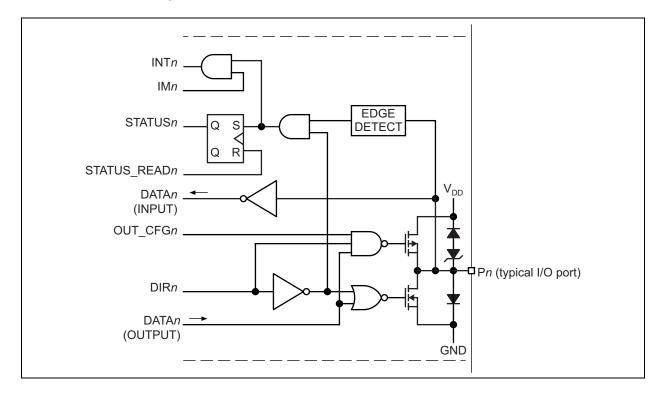

# **Functional Block Diagram**

## 1.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings †**

| Supply Voltage (V <sub>DD</sub> )                              | +4.6V               |

|----------------------------------------------------------------|---------------------|

| Input Voltage (All pins except VDD and GND) (V <sub>IN</sub> ) | GND – 0.3V to +5.5V |

| ESD Rating (VDD, Note 1)                                       | 1.5 kV              |

| ESD Rating (A0, A1, A2, Note 1)                                | 500V                |

| ESD Rating (Others, Note 1)                                    | 200V                |

| Operating Ratings ‡                                            |                     |

| Supply Voltage (V <sub>DD</sub> )                              | +2.7V to +3.6V      |

**<sup>†</sup> Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

**‡ Notice:** The device is not guaranteed to function outside its operating ratings.

Note 1: Devices are ESD sensitive. Handling precautions are recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

# **MIC74**

TABLE 1-1: ELECTRICAL CHARACTERISTICS

**Electrical Characteristics:**  $2.7V \le V_{DD} \le 3.6V$ ;  $T_A = +25^{\circ}C$ . **Bold** values indicate  $-40^{\circ}C < T_A < +85^{\circ}C$ , unless noted. Note 1

| Parameters                                       | Symbol             | Min.               | Тур. | Max.                  | Units | Conditions                                                                                                     |

|--------------------------------------------------|--------------------|--------------------|------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------|

| Input Voltage (any pin except VDD and GND)       | V <sub>IN</sub>    | GND - 0.3          | _    | 5.5                   | V     | _                                                                                                              |

| Operating Supply<br>Current                      | I <sub>DD</sub>    | _                  | 2    | 6                     | μΑ    | P[7:0] inputs; P[7:0] = V <sub>DD</sub> or<br>GND; /ALERT open; f <sub>CLK</sub> =<br>100 kHz                  |

| Fan Startup Supply<br>Current (Fan Mode<br>Only) | I <sub>START</sub> |                    | l    | 1.75                  | mA    | During $t_{START}$ ; /ALERT, /SHDN,<br>/FS2[2:0] = open;<br>$V_{CLK} = V_{DATA} = V_{DD}$ ;<br>P[3:0] = inputs |

| Standby Supply<br>Current                        | I <sub>STBY</sub>  | _                  | 1    | 3                     | μΑ    | /ALERT = open,<br>V <sub>CLK</sub> = V <sub>DATA</sub> = V <sub>DD</sub> ;<br>P[3:0] = inputs                  |

| Serial I/O (DATA, CLK)                           |                    |                    |      |                       |       |                                                                                                                |

| Input Low Voltage                                | $V_{IL}$           | -0.3               | _    | 0.8                   | V     | _                                                                                                              |

| Input High Voltage                               | V <sub>IH</sub>    | 2                  | _    | 5.5                   | V     | _                                                                                                              |

| Output Low Voltage                               | V <sub>OL</sub>    | _                  | 1    | 0.4                   | V     | I <sub>OL</sub> = 3 mA                                                                                         |

| Leakage Current                                  | I <sub>LEAK</sub>  | -1                 |      | 1                     | μΑ    | V <sub>IN</sub> = 5.5V or GND                                                                                  |

| Input Capacitance                                | C <sub>IN</sub>    |                    | 10   | _                     | pF    | _                                                                                                              |

| Parallel I/O [P0-P3, P4                          | (/SHDN), P5(       | /FS0)-P7(/FS       | 2)]  |                       |       |                                                                                                                |

| Input Low Voltage                                | $V_{IL}$           | -0.5               |      | 0.8                   | V     | _                                                                                                              |

| Input High Voltage                               | V <sub>IH</sub>    | 2                  | _    | 5.5                   | V     | _                                                                                                              |

| Outrout Law Commant                              | 1                  | 7                  | 1    | _                     | A     | $V_{OL} = 0.4V, V_{DD} = 2.7V$                                                                                 |

| Output Low Current                               | l <sub>OL</sub>    | 10                 |      | _                     | mA    | $V_{OL} = 1.0V, V_{DD} = 3.3V$                                                                                 |

| Output High Current                              | I <sub>OH</sub>    | 7                  |      | _                     | mA    | V <sub>OH</sub> = 2.4V                                                                                         |

| Leakage Current                                  | I <sub>LEAK</sub>  | <b>–</b> 1         | 1    | 1                     | μΑ    | V <sub>IN</sub> = 5.5V or GND                                                                                  |

| Input Capacitance                                | C <sub>IN</sub>    |                    | 10   | _                     | pF    | _                                                                                                              |

| Output Capacitance                               | C <sub>OUT</sub>   | _                  | 10   | _                     | pF    | _                                                                                                              |

| Address Input (A0-A2)                            | )                  |                    |      |                       |       |                                                                                                                |

| Input Low Voltage                                | $V_{IL}$           | -0.3               |      | 0.3V <sub>DD</sub>    | V     | _                                                                                                              |

| Input High Voltage                               | V <sub>IH</sub>    | 0.7V <sub>DD</sub> | _    | V <sub>DD</sub> + 0.3 | V     | _                                                                                                              |

| Leakage Current                                  | I <sub>LEAK</sub>  | -250               | 1    | 250                   | nA    | V <sub>IN</sub> = V <sub>DD</sub> or GND                                                                       |

| /ALERT                                           |                    |                    |      |                       |       |                                                                                                                |

| Output Low Voltage                               | V <sub>OL</sub>    |                    |      | 0.4                   | V     | I <sub>OL</sub> = 1 mA                                                                                         |

| Leakage Current                                  | I <sub>LEAK</sub>  | -1                 | ±250 | 1                     | μΑ    | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub>                                                           |

| AC Characteristics                               |                    |                    |      |                       |       |                                                                                                                |

| Fan Startup Interval                             | t <sub>START</sub> | 0.5                | 1    | 3.3                   | sec.  | Normal operation                                                                                               |

| Minimum Pulse Width                              | t <sub>PULSE</sub> | 10                 | _    | _                     | ns    | Minimum pulse width on Pn to generate an interrupt, Note 5                                                     |

TABLE 1-1: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Characteristics:**  $2.7V \le V_{DD} \le 3.6V$ ;  $T_A = +25^{\circ}C$ . **Bold** values indicate  $-40^{\circ}C < T_A < +85^{\circ}C$ , unless noted. Note 1

| Parameters                                                                  | Symbol               | Min. | Тур. | Max. | Units | Conditions                                                                                 |

|-----------------------------------------------------------------------------|----------------------|------|------|------|-------|--------------------------------------------------------------------------------------------|

| Interrupt Delay                                                             | t/int                | _    | _    | 4    | μs    | Interrupt delay from state change on Pn to /ALERT ≤ V <sub>OL</sub> , Note 5               |

| Delay from Status<br>Read or ARA<br>Response to /ALERT ≥<br>V <sub>OH</sub> | t <sub>/IR</sub>     | _    | _    | 4    | μs    | _                                                                                          |

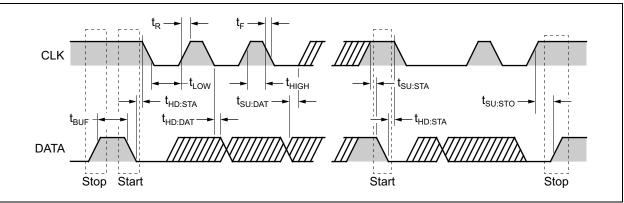

| Hold Time, Note 5                                                           | t <sub>HD:STA</sub>  | 4    | _    | _    | μs    | Hold time after repeated start condition; after this period, the first clock is generated. |

| Setup Time, Note 5                                                          | t <sub>SU:STA</sub>  | 4.7  | _    | _    | μs    | Repeated start condition setup time                                                        |

| Stop Condition Setup<br>Time                                                | t <sub>SU:STO</sub>  | 4    | _    | _    | μs    | Note 5                                                                                     |

| Data Hold Time                                                              | t <sub>HD:DAT</sub>  | 500  | _    | _    | ns    | Note 5                                                                                     |

| Data Setup Time                                                             | t <sub>SU:DAT</sub>  | 0    | _    | _    | ns    | Note 5                                                                                     |

| Clock Low Timeout                                                           | t <sub>TIMEOUT</sub> | 25   | 35   | _    | ms    | Note 2, Note 5                                                                             |

| Clock Low Period                                                            | t <sub>LOW</sub>     | 4.7  | _    | _    | μs    | Note 3, Note 5                                                                             |

| Clock High Period                                                           | t <sub>HIGH</sub>    | 4    | 50   | _    | μs    | Note 3, Note 5                                                                             |

| Clock/Data Fall Time                                                        | t <sub>F</sub>       | _    | 300  | _    | ns    | Note 4, Note 5                                                                             |

| Clock/Data Rise Time                                                        | t <sub>R</sub>       | _    | 1000 | _    | ns    | Note 4, Note 5                                                                             |

| Bus Free Time<br>between Stop and Start<br>Condition                        | t <sub>BUF</sub>     | 4.7  | _    | _    | μs    | Note 5                                                                                     |

- Note 1: Specification for packaged product only.

- 2: Devices participating in a transfer will timeout when any clock low exceeds the value of t<sub>TIMEOUT(min)</sub> of 25 ms. Devices that have detected a timeout condition must reset the communication no later than t<sub>TIMEOUT(max)</sub> of 35 ms. The maximum value specified must be adhered to by both a host and a client as it incorporates the cumulative stretch limit for both a host (10 ms) and a client (25 ms).

- **3:** t<sub>HIGH(max)</sub> provides a simple guaranteed method for devices to detect bus idle conditions.

- 4: Rise and fall time is defined as follows:  $t_R = V_{IL(max)} 0.15V$  to  $V_{IH(min)} + 0.15V$ ;  $t_F = 0.9V_{DD}$  to  $V_{IL(max)} 0.15V$ .

- 5: Guaranteed by design.

# MIC74

# **TEMPERATURE SPECIFICATIONS (Note 1)**

| Parameters                   | Sym.                        | Min. | Тур. | Max. | Units | Conditions         |  |  |

|------------------------------|-----------------------------|------|------|------|-------|--------------------|--|--|

| Temperature Ranges           |                             |      |      |      |       |                    |  |  |

| Maximum Junction Temperature | TJ                          | _    | _    | +150 | °C    | _                  |  |  |

| Ambient Temperature Range    | T <sub>A</sub>              | -40  | _    | +85  | °C    | _                  |  |  |

| Lead Temperature Soldering   | _                           | _    | _    | +260 | °C    | Soldering, 10 sec. |  |  |

| Package Thermal Resistances  | Package Thermal Resistances |      |      |      |       |                    |  |  |

| QSOP-16                      | $\theta_{JA}$               | _    | 163  | _    | °C/W  | _                  |  |  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +150°C rating. Sustained junction temperatures above +150°C can impact the device reliability.

# 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

| Pin Number    | Symbol                                           | Description                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|---------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1, 2, 3       | A0, A1, A2                                       | Address (input): Client address selection inputs; sets the three least significant bits of the MIC74's client address.                                                                                                                                                                                                      |  |  |  |  |

| 4, 5, 6, 7    | P0, P1,<br>P2, P3                                | Parallel I/O (input/output): General-purpose I/O pin. Direction and output type are user-programmable.                                                                                                                                                                                                                      |  |  |  |  |

| 8             | GND                                              | Ground                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 9, 10, 11, 12 | P4, P5,<br>P6, P7<br>(/SHDN, /FS0<br>/FS1, /FS2) | Parallel I/O (input/output): P4 – P7 are general-purpose I/O pins. Direction and output type are user-programmable.  Shutdown (output): When the FAN bit is set, pin 9 becomes SHDN. Fan speed (output): When the FAN bit is set, pins 10 through 12 become /FS0 – /FS2 respectively, controlled by the FAN_SPEED register. |  |  |  |  |

| 13            | /ALERT                                           | Interrupt (output): Active-low, open-drain output signals input-change-interrupts to the host on this pin. Signal is cleared when the bus host polls the ARA (alert response address = 0001 100) or reads status.                                                                                                           |  |  |  |  |

| 14            | CLK                                              | Serial bus clock (input): The host provides the serial bit clock in this input.                                                                                                                                                                                                                                             |  |  |  |  |

| 15            | DATA                                             | Serial data (input/output): Serial data input and open-drain serial data output.                                                                                                                                                                                                                                            |  |  |  |  |

| 16            | VDD                                              | Power supply (input).                                                                                                                                                                                                                                                                                                       |  |  |  |  |

# **Timing Definitions**

FIGURE 2-1: Timing Measurement.

## 3.0 REGISTER DESCRIPTIONS

# TABLE 3-1: DEVICE CONFIGURATION REGISTER (DEV\_CFG)

| D[7] | D[6]                  | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |  |  |

|------|-----------------------|------|------|------|------|------|------|--|--|

|      | Always write as zero. |      |      |      |      |      |      |  |  |

Device configuration register parameters:

Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

- Interrupts disabled

Not in fan mode

Command\_byte address: 0000 0000<sub>b</sub>, 00<sub>h</sub>

Type: 8-bits, read/write

Bit name: IE

Function: Global Interrupt Enable

· Operation: 1 = enabled, 0 = disabled

· Bit name: FAN

• Function: Selects fan mode (P[7:4] vs. /FS[2:0],

/SHDN)

Note:

• Operation: 1 = fan mode; 0 = I/O mode

• Bit Name: D[2] through D[6]

· Function: Reserved

· Operation: Reserved; always write as zero

#### TABLE 3-2: DATA DIRECTION REGISTER (DIR)

| D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|------|------|------|------|------|------|------|------|

| DIR7 | DIR6 | DIR5 | DIR4 | DIR3 | DIR2 | DIR1 | DIR0 |

Data direction register parameters:

Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

- All Pn's configured as inputs

Command\_byte address: 0000 0001<sub>b</sub>, 01<sub>h</sub>

· Type: 8-bits, read/write

• Bit name: DIRn

Function: Selects data direction, input or output,

of Pn

• Operation: 1 = output; 0 = input

If the FAN bit of the DEV\_CFG register is set to '1' (i.e., if fan mode is selected), P[7:4] are automatically configured as open-drain outputs. They are then referred to as /FS[2:0] and /SHDN. The DIR register

has no effect on these I/O bits while in fan

mode.

TABLE 3-3: OUTPUT CONFIGURATION REGISTER (OUT\_CFG)

| D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|------|------|------|------|------|------|------|------|

| OUT7 | OUT6 | OUT5 | OUT4 | OUT3 | OUT2 | OUT1 | OUT0 |

Output configuration register parameters:

Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

- All outputs open-drain

Command byte address: 0000 0010<sub>h</sub>, 02<sub>h</sub>

· Type: 8-bits, read/write

• Bit name: OUTn

• Function: Selects output driver configuration of Pn when Pn is configured as an output.

• Operation: 1 = push-pull; 0 = open-drain

Note: If the FAN bit of the DEV\_CFG register is set to '1' (i.e., if fan mode is selected), P[7:4] are automatically configured as open-drain outputs. They are then referred to as /FS[2:0] and /SHDN. The OUT\_CFG register has no effect on these I/O bits

while in fan mode.

TABLE 3-4: STATUS REGISTER (STATUS)

| D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|------|------|------|------|------|------|------|------|

| S7   | S6   | S5   | S4   | S3   | S2   | S1   | S0   |

Status register parameters:

Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

- No interrupts pending

Command\_byte address: 0000 0011<sub>b</sub>, 03<sub>h</sub>

· Type: 8-bits, read/write

• Bit name: Sn

Function: Flag for Pn input-change event when Pn is configured as an input. Sn is set when the corresponding input changes state.

Operation: 1 = change occurred; 0 = no change occurred

Note:

If the FAN bit of the DEV\_CFG register is set to '1' (i.e., if fan mode is selected), P[7:4] are automatically configured as open-drain outputs. They are then referred to as /FS[2:0] and /SHDN. No interrupts of any kind are generated by these pins while in fan mode. All status bits are cleared after any read operation is performed on STATUS.

TABLE 3-5: INTERRUPT MASK REGISTER (INT\_MASK)

| D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|------|------|------|------|------|------|------|------|

| IM7  | IM6  | IM5  | IM4  | IM3  | IM2  | IM1  | IM0  |

Interrupt mask register parameters:

Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

• Command\_byte address: 0000 0100<sub>b</sub>, 04<sub>h</sub>

• Type: 8-bits, read/write

• Bit name: IMn

Function: Interrupt enable bit for Pn when Pn is configured as an input.

• Operation: 1 = enabled; 0 = disabled

Note:

If the FAN bit of the DEV\_CFG register is set to '1' (i.e., if fan mode is selected), P[7:4] are automatically configured as open-drain outputs. They are then referred to as /FS[2:0] and /SHDN. No interrupts of any kind are generated by these pins while in fan mode.

TABLE 3-6: DATA REGISTER (DATA)

|   | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|---|------|------|------|------|------|------|------|------|

| ľ | P7   | P6   | P5   | P4   | P3   | P2   | P1   | P0   |

Data register parameters:

• Power-on default value: 1111 1111<sub>b</sub>, FF<sub>h</sub>

Command\_byte address: 0000 0101<sub>b</sub>, 05<sub>h</sub>

· Type: 8-bits, read/write

• Bit name: Pn

Function: Returns the current state of any Pn configured as an input and the last value written to Pn's configured as outputs. Writing the DATA register sets the output state of any Pn's configured as outputs; writes to I/O bits configured as inputs are ignored.

- Read operation: 1 = Pn is high; 0 = Pn is low

- Write operation: 1 = Pn is set to '1'; 0 = Pn is cleared

Note:

If the FAN bit of the DEV\_CFG register is set to '1' (i.e., if fan mode is selected), P[7:4] are automatically configured as open-drain outputs. They are then referred to as /FS[2:0] and /SHDN. The state of these pins is determined by the FAN\_SPEED register. While in fan mode, D[7:4] of the DATA registers have no effect.

### TABLE 3-7: FAN SPEED REGISTER (FAN\_SPEED)

| D[7] | D[6] | D[5]            | D[4]      | D[3] | D[2] | D[1] | D[0] |

|------|------|-----------------|-----------|------|------|------|------|

|      | Alv  | vays write as z | Fan Speed |      |      |      |      |

Fan speed register parameters:

• Power-on default value: 0000 0000<sub>b</sub>, 00<sub>h</sub>

- Fan off

• Command\_byte address: 0000 0110<sub>b</sub>, 06<sub>h</sub>

Type: 8-bits, read/writeBit name: D[0] through D[2]

Function: Determines bit-pattern on FS[2:0]

Operation: Fan speed settings (see Table 3-8)

Note:

Any time the fan speed register contains zero, meaning the fan is shut down, and a non-zero value is written into the fan speed register, the /FS[2:0] and /SHDN outputs will assume the highest fan speed state for approximately one second ( $t_{START}$ ). Following this interval, the state of the fan speed control outputs will assume the value indicated by the contents of FAN\_SPEED. This ensures that the fan will start reliably when low speed operation is desired.

• Bit Name: D[3] through D[7]

· Function: Reserved

· Operation: Always write as zero

TABLE 3-8: FAN SPEED SETTINGS

| 17 (DLL 0 0. | 1741 OF EED GETTINGS |           |                      |  |  |

|--------------|----------------------|-----------|----------------------|--|--|

| D[2:0]       | Outpu                | Fan Speed |                      |  |  |

| Value        | /FS[2:0] /SHDN       |           |                      |  |  |

| 000          | 111                  | 0         | Off                  |  |  |

| 001          | 110                  | 1         | Speed 1 (slowest)    |  |  |

| 010          | 101                  | 1         | Speed 2              |  |  |

| 011          | 100                  | 1         | Speed 3              |  |  |

| 100          | 011                  | 1         | Speed 4              |  |  |

| 101          | 010                  | 1         | Speed 5              |  |  |

| 110          | 001                  | 1         | Speed 6              |  |  |

| 111          | 000                  | 1         | Speed 7<br>(fastest) |  |  |

### 4.0 FUNCTIONAL DESCRIPTION

# 4.1 Pin Descriptions

#### 4.1.1 VDD

Power supply input connection. See Operating Ratings

‡ section for additional information.

#### 4.1.2 GND

Ground or return connection for all MIC74 functions.

#### 4.1.3 CLK

A CLK signal is provided by the host and is common to all devices on the bus. The CLK signal controls all transactions in both directions on the bus and is applied to each MIC74 at the CLK pin.

#### 4.1.4 DATA

Serial data is bidirectional and is common to all devices on the bus. The MIC74's DATA output is open-drain.

The DATA line requires one external pull-up resistor or current source per system that can be located anywhere along the line.

#### 4.1.5 A2, A1, A0

The MIC74 responds to its own unique address which is assigned using the A0–A2 pins. A0–A2 set the three LSBs (least significant bits) of the MIC74's 7-bit client address. The three address pins allow eight unique MIC74 addresses in a system. When the MIC74's address matches an address received in the serial bit stream, communication is initiated.

A2, A1 and A0 should be connected to GND or VDD. The state of these pins is sampled only once at device power-on. New client addresses are not accepted unless the MIC74 is powered off then on.

TABLE 4-1: MIC74 ADDRESS CONFIGURATION

| A2<br>Inputs | A1<br>Inputs | A0<br>Inputs | Binary<br>Address     | Hex<br>Address  |  |

|--------------|--------------|--------------|-----------------------|-----------------|--|

| 0            | 0            | 0            | 010 0000 <sub>b</sub> | 20 <sub>h</sub> |  |

| 0            | 0            | 1            | 010 0001 <sub>b</sub> | 21 <sub>h</sub> |  |

| 0            | 1            | 0            | 010 0010 <sub>b</sub> | 22 <sub>h</sub> |  |

| 0            | 1            | 1            | 010 0011 <sub>b</sub> | 23 <sub>h</sub> |  |

| 1            | 0            | 0            | 010 0100 <sub>b</sub> | 24 <sub>h</sub> |  |

| 1            | 0            | 1            | 010 0101 <sub>b</sub> | 25 <sub>h</sub> |  |

| 1            | 1            | 0            | 010 0110 <sub>b</sub> | 26 <sub>h</sub> |  |

| 1            | 1            | 1            | 010 0111 <sub>b</sub> | 27 <sub>h</sub> |  |

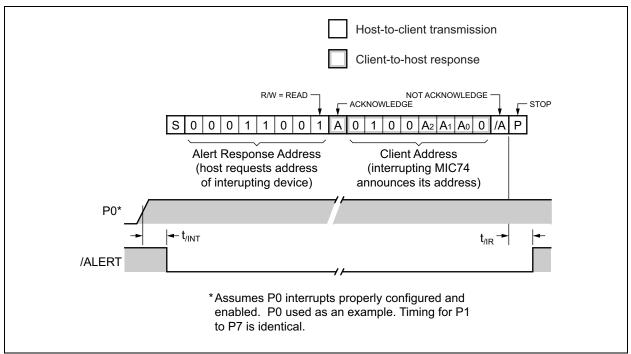

#### 4.1.6 ALERT RESPONSE ADDRESS

The MIC74 also responds to the Alert Response Address (ARA). The ARA is used by the host to request the address of a client that has provided an interrupt to the host via the /ALERT line.

The ARA is a single address (0001 100) common to all clients and is described in more detail under Interrupt Generation with related information under /ALERT. Also see Figure 5-5.

#### 4.1.7 PN, /SHDN, AND /FS0 - /FS2

P0 through P7 are general purpose input/output bits. Each bit is independently programmable as an input or an output. If programmed as an output, each bit is further programmable as either a complementary push-pull or open-drain output.

If properly enabled, any Pn programmed as an input will generate an interrupt to the host using the /ALERT output when the input changes state. In this way, the MIC74 can notify the host of an input change without requiring periodic polling by the host or a message transaction on the bus.

Regardless of whether interrupts are enabled or disabled, each input-change event also sets the corresponding bit in the status register. I/O configuration is performed using the output configuration (OUT\_CFG), I/O direction (DIR), and interrupt mask (INT\_MASK) registers.

If the FAN bit in the device configuration register is set, the states of P[7:4] are controlled by the FAN\_SPEED register. The bits in the OUT\_CFG, DIR, and INT\_MASK registers corresponding to P[7:4] are ignored. When in fan mode, P[7:4] are referred to as /FS2, /FS1, /FS0, and /SHDN. While in this mode, no interrupts of any kind will be generated by these pins.

#### 4.1.8 /ALERT

The alert signal is an open-drain, active-low output. The operation of the /ALERT output is controlled by the IM*n* bits in the INT\_MASK register and the global interrupt enable bit (IE) in the DEV\_CFG register.

If the IE bit is set to zero, or if the corresponding interrupt enable bit, IMn, is set to zero, no input-change interrupts will be generated. Regardless of the IE bit setting, the change will be reflected in the status register.

If the IE bit is set to one, IMn is set to one, and Pn is an input, then /ALERT is driven active whenever Pn changes state, (goes from a high-to-low or low-to-high state). Once triggered, /ALERT is unconditionally reset to its inactive state once the MIC74 successfully responds to the alert response addressor STATUS is read.

#### 4.2 Serial Port Operation

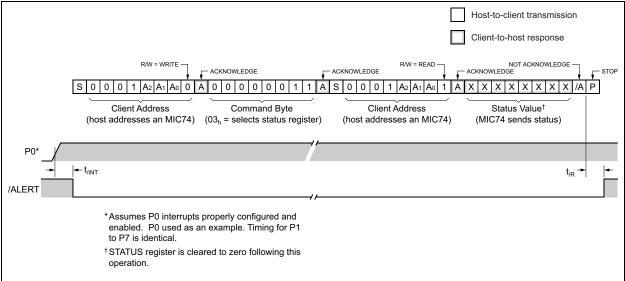

The MIC74 uses standard SMBus Read\_Byte and Write\_Byte operations to communicate with its host.

The Read\_Byte operation is a composite read-write operation consisting of first sending the MIC74's client address followed by a command byte (a write) and then resending the client address and clocking out the data byte (a read). The command byte is the address of the target register. See Table 4-2. An example of a Read\_Byte operation is shown in Figure 5-6.

Similarly, the write-byte operation consists of sending the device's client address followed by a command byte and the byte to be written to the target register. Again, in the case of the MIC74, the command byte is the address of the target register. See Table 4-2.

In addition, to the read byte and write byte protocols, the MIC74 adheres to the SMBus protocol for response to the ARA (alert response address). An MIC74 expects to be interrogated using the ARA when it has asserted its /ALERT output. /ALERT interrupts can be enabled or disabled using the IE bit in the DEV\_CFG register.

#### 4.3 Power On

When power is initially applied, the MIC74's internal registers will assume their power-up default state and the state of the address inputs, A2, A1, and A0, will be read to establish the device's client address. See the individual register descriptions for each registers default state. Also see Table 4-2.

#### 4.4 I/O Ports

Each I/O bit, P0 through P7, may be individually programmed as an input or output using the corresponding bit in the I/O direction register, DIR. If programmed as an output, each is further programmable as either a complementary push-pull or open-drain output using the output configuration register, OUT CFG.

If enabled by the corresponding bit, IMn, in the interrupt mask register INT\_MASK, each Pn programmed as an input will generate an interrupt to the host on /ALERT if the input changes state. In this way, the MIC74 can notify the host of an input change without requiring periodic polling by the host or a transaction on the bus.

Each input-change event also sets the corresponding bit in the status register, STATUS. See the Functional Block Diagram for the logic arrangement of atypical MIC74 I/O port.

## 4.5 Fan Speed Control

If the FAN bit in the device configuration register is set, the state of P[7:4] is controlled by the FAN\_SPEED register. The bits in the OUT\_CFG, DIR, and INT\_MASK registers corresponding to P[7:4] are ignored. When in Fan Control Mode, P[7:4] are referred to as /FS2, /FS1, /FS0, and /SHDN. While in this mode, no interrupts of any kind will be generated by these pins. See the Application Information section for typical fan speed control applications.

TABLE 4-2: REGISTER SUMMARY

| Register<br>Name | Register<br>Description | Binary<br>Address      | Hex<br>Address  | Available<br>Options | Binary<br>Power-On<br>Default | Hex<br>Power-On<br>Default |

|------------------|-------------------------|------------------------|-----------------|----------------------|-------------------------------|----------------------------|

| DEV_CFG          | Device configuration    | 0000 0000 <sub>b</sub> | 00 <sub>h</sub> | 8-bit read/write     | 0000 0000b                    | 00 <sub>h</sub>            |

| DIR              | I/O direction           | 0000 0001 <sub>b</sub> | 01 <sub>h</sub> | 8-bit read/write     | 0000 0000b                    | 00 <sub>h</sub>            |

| OUT_CFG          | Output configuration    | 0000 0010 <sub>b</sub> | 02 <sub>h</sub> | 8-bit read/write     | 0000 0000b                    | 00 <sub>h</sub>            |

| STATUS           | Interrupt status        | 0000 0011 <sub>b</sub> | 03 <sub>h</sub> | 8-bit read           | 0000 0000b                    | 00 <sub>h</sub>            |

| INT_MASK         | Interrupt mask          | 0000 0100 <sub>b</sub> | 04 <sub>h</sub> | 8-bit read/write     | 0000 0000b                    | 00 <sub>h</sub>            |

| DATA             | General<br>purpose I/O  | 0000 0101 <sub>b</sub> | 05 <sub>h</sub> | 8-bit read/write     | 1111 1111 <sub>b</sub>        | FF <sub>h</sub>            |

| FAN_SPEED        | Fan speed               | 0000 0110 <sub>b</sub> | 06 <sub>h</sub> | 8-bit read/write     | 0000 0000b                    | 00 <sub>h</sub>            |

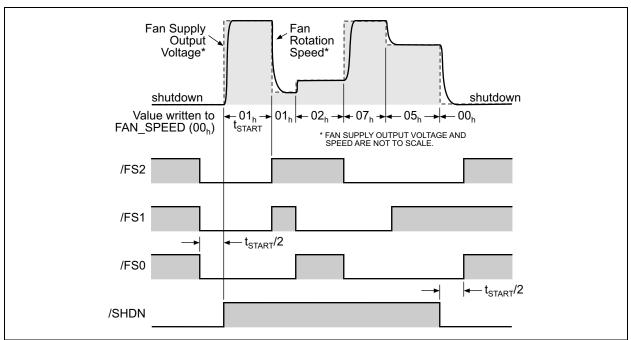

## 4.6 Fan Start-Up

Any time the fan speed register contains zero (fan is off) and then a nonzero value is written to FAN\_SPEED, the /FS[2:0] and /SHDN outputs will assume the highest fan speed state for approximately one second ( $t_{START}$ ). Following this interval, the state of the fan speed control outputs will assume the value indicated by the contents of FAN\_SPEED. This ensures that the fan will start reliably when low speed operation is desired. The  $t_{START}$  interval is generated by an internal oscillator and counters. At the end of  $t_{START}$ , this oscillator is powered down to reduce overall power consumption.

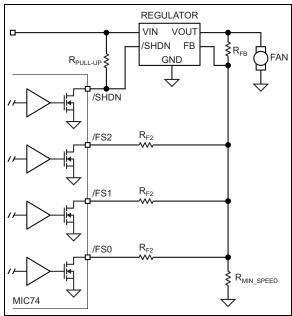

FIGURE 4-1: Fan Speed Control Application.

Proper sequencing of the /FS[2:0] and /SHDN signals is performed by the MIC74's internal logic state machine. When activating the fan from the off state, the /FS[2:0] lines change state first, then, after a delay equal to t<sub>START</sub>/2, the /SHDN pin is deasserted. Conversely, when the fan is shutdown (zero is written to FAN\_SPEED), the /SHDN pin is deasserted first. The /FS[2:0] lines are subsequently deasserted after a delay of t<sub>START</sub>/2. The internal oscillator is also powered down following the t<sub>START</sub>/2 interval at fan shut-down. These timing relationships are illustrated in Figure 4-2.

#### 4.7 Interrupt Generation

Assuming that any or all of the I/Os are configured as inputs, the MIC74 will reflect the occurrence of an input change in the corresponding bit in the status register, STATUS. This action cannot be masked. An input change will only generate an interrupt to the host if interrupts are properly configured and enabled.

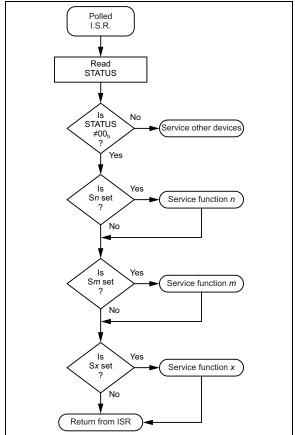

The MIC74 can operate in either polled mode or interrupt mode. In the case of polled operation, the host periodically reads the contents of STATUS to determine the device state. The act of reading STATUS clears its contents. Repeating events which have occurred since the last read from STATUS will not be discernable to the host.

Interrupts are only generated if the global interrupt enable bit, IE, in the DEV\_CFG register is set. The /ALERT signal will be asserted (driven low) when an interrupt is generated. The MIC74 expects to be interrogated using the ARA when it has generated an interrupt output. Once it has successfully responded to the ARA (Alert Response Address), the /ALERT output will be deasserted. The contents of the status register will not be cleared until it is read using a read byte operation.

If a given system does not wish to use the SMBus ARA protocol for reporting interrupts, the system may simply poll the contents of the status register after detecting an interrupt on /ALERT. This action will clear the contents of STATUS and cause /ALERT to be deasserted. Reading the status register is an acceptable substitute for using the ARA protocol. Presumably, however, it will involve higher system overhead since all the devices on the bus must be polled to determine which one generated the interrupt.

FIGURE 4-2: Typical MIC74 Fan Mode Timing and System Behavior.

## 5.0 APPLICATION INFORMATION

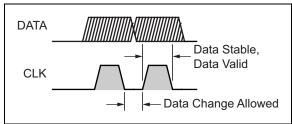

#### 5.1 Bit Transfer

The data received on the DATA pin must be stable during the high period of the clock.

Data can change state only when the CLK line is low. Refer to Figure 5-1.

FIGURE 5-1: Acceptable Bit Transfer Conditions.

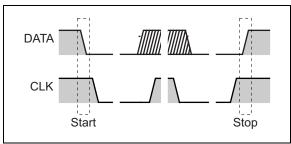

## 5.2 Start and Stop Conditions

Two unique bus situations define start and stop conditions. A high-to-low transition of the DATA line while CLK is high indicates a start condition. A low-to-high transition of the DATA line while CLK is high defines a stop condition. See Figure 5-2.

FIGURE 5-2: Start and Stop Definitions.

Start (leading edge of start) and stop (trailing edge of stop) conditions are always generated by the bus host. After a start condition, the bus is considered to be busy. The bus becomes free again after a certain time following a stop condition or after both CLK and DATA lines remain high for more than  $50~\mu s$ .

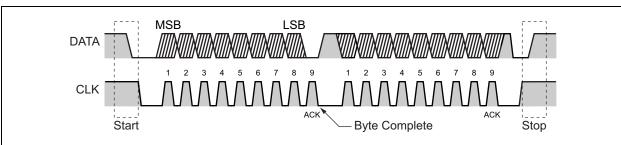

## 5.3 Serial Byte Format

Every byte consists of 8 bits. Each byte transferred on the bus must be followed by an acknowledge bit. Bytes are transferred with the MSB (most significant bit) first. See Figure 5-3.

FIGURE 5-3: Serial Byte Format.

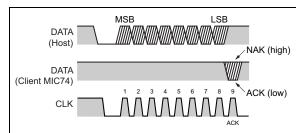

# 5.4 Acknowledge and Not Acknowledge

The acknowledge related clock pulse is generated by the host. The transmitter releases the DATA line (high) during the acknowledge clock cycle.

In order to acknowledge (ACK) a byte, the receiver must pull the DATA line low during the high period of the clock pulse according the bus timing specifications. A client device that wishes to not acknowledge a byte must let the DATA line remain high during the acknowledge clock pulse. See Figure 5-4.

**FIGURE 5-4:** Acknowledge and Not Acknowledge.

FIGURE 5-5: Interrupt Handling Using the Alert Response Address.

FIGURE 5-6: Interrupt Handling Without the Alert Response Address.

# 5.5 Initializing the MIC74

The MIC74's internal registers are reset to their default state at power-on. The MIC74's default state can be summarized as follows:

- All I/Os configured as inputs (DIR = 00h)

- Output configuration set to open-drain (OUT CFG = 00h)

- All outputs high/floating (DATA = FFh)

- Fan functions disabled (FAN\_SPEED = 00h; FAN bit of DEV\_CFG = 0)

- All interrupts masked (IE bit of DEV CFG = 0)

The result of this configuration is that all I/O pins will essentially float unless driven by external circuitry. Any system using the MIC74 will need to initialize the internal registers to the state required for proper system operation. The recommended order for initializing the MIC74's registers is as follows:

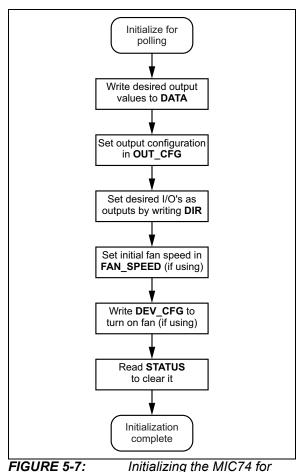

FIGURE 5-7:

Polled Operation.

- 1. Write DATA

- 2. Write OUT CFG

- 3. Write DIR

- 4. Write FAN\_SPEED (if using fan mode)

- 5. Write INT\_MASK (if using interrupts)

- 6. Read STATUS to clear it

- Write DEV\_CFG to enable fan mode and/or interrupts, if using.

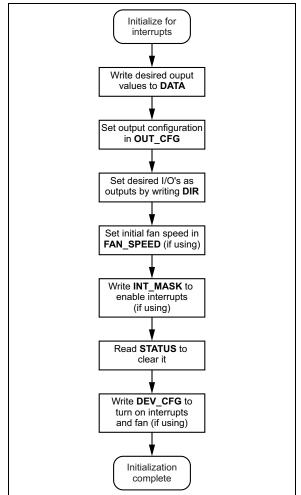

At the conclusion of step three, any I/Os configured as outputs in step two will be driven to the levels programmed into the data register in step one. The order of step one through step three is important to ensure that spurious data does not appear at the I/Os configuration. Following durina step programming the device configuration register, the MIC74 will begin generating interrupts if they are enabled, and the fan will be started if FAN SPEED contains a non-zero value. The corresponding interrupt service routines (if any) must be initialized and enabled prior to step seven. STATUS should be cleared (step six) in both polled and interrupt-driven systems.

FIGURE 5-8: Interrupts.

Initializing the MIC74 for

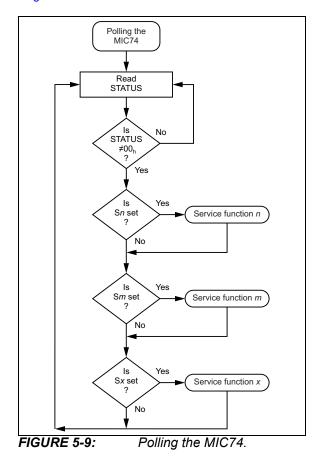

#### 5.6 Polled Mode

Input state changes on I/Os configured as inputs will be reflected in the status register regardless of the state of the global interrupt enable bit (IE) and the individual interrupt mask bits in INT\_MASK. In a system utilizing polling to monitor for input changes, the status register is periodically read to check for input events. The act of reading STATUS clears it in preparation for detecting future events. The status bits corresponding to I/Os configured as outputs or corresponding to P[7:4] when in fan mode will not be set by state changes on these pins. It is always good practice, however, to mask the value obtained when reading STATUS to eliminate any bits, output or otherwise, that are not of immediate concern. This will help avoid problems if software changes are made in the future.

The flowchart shown in Figure 5-7 illustrates the steps involved in initializing the MIC74 for polled operation. The flowchart in Figure 5-9 illustrates the corresponding polling routine. The process for writing output data is straight-forward: simply write the desired bit pattern to DATA. Special precautions may be required when changing output data in an interrupt driven system, however. See the Writing to the Data Register section.

# 5.7 Interrupt Mode

Input state changes on I/Os configured as inputs will be reflected in the status register regardless of the state of the global interrupt enable bit (IE) and the individual interrupt mask bits in INT\_MASK. In a system utilizing interrupts to detect input changes, one or more of the bits in the interrupt mask register, INT\_MASK, are set to allow interrupts on /ALERT to be generated by input events. The global interrupt enable bit, IE, in the device configuration register must also be set to enable interrupts.

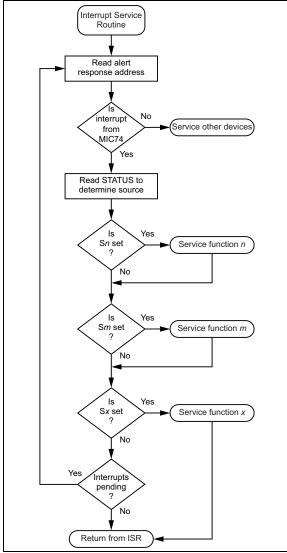

The flowchart shown in Figure 5-8 illustrates the steps involved in initializing the MIC74 for interrupt-driven operation. The flowchart in Figure 5-10 illustrates the corresponding interrupt service routine using the SMBus ARA. The corresponding timing diagram is shown in Figure 5-5. The flowchart in Figure 5-11 illustrates the corresponding interrupt service routine using polling to determine the interrupt source. Figure 5-6 illustrates the timing. Utilizing the ARA greatly speeds identification of the interrupting client device and lowers latency, as only a single transaction on the bus is necessary to identify the interrupt source.

Using either method, STATUS must be read to determine the exact source of the interrupt within the MIC74.

The act of reading STATUS clears it in preparation for detecting future events. The status bits corresponding to I/Os configured as outputs or corresponding to P[7:4] when in fan mode will not be set by state changes on these pins. It is always good practice, however, for the interrupt service routine to mask the value obtained when reading STATUS to eliminate any bits, output or otherwise, that are not of immediate concern. This will help avoid problems if software changes are made in the future.

The process for writing output data is straight-forward—simply write the desired bit pattern to DATA. Special precautions may be required, however, when changing output data in an interrupt driven system. See the Writing to the Data Register section.

FIGURE 5-10: Interrupt Service Routine Using the ARA.

## 5.8 Writing to the Data Register

Multiple software routines may use the various output bits available on the MIC74 to control individual functions such as power switches, LEDs, etc. These various functions may be handled by independent software routines that must manipulate individual output bits without regard for other bits. Care must be taken to ensure that these various software routines do not interfere with each other when modifying output data. The recommended procedure for changing isolated output bits is as follows:

- 1. Read DATA

- 2. Set desired bits by ORing the value read from DATA with an appropriate mask value

- Clear desired bits by ANDing the value read from DATA with an appropriate mask value

#### 4. Write the result back to DATA

A functionally equivalent alternative to this procedure is to keep an image of the data register in software. Any independent routines would make changes to this image using the procedure above and then call a routine that actually writes the new image to DATA. Interrupts would be disabled briefly while DATA is being modified.

FIGURE 5-11: Interrupt Service Routine Without ARA.

Regardless of which procedure is used, it is important that only one software routine at a time attempts to make changes to the output data. In a system where polling is the exclusive method for servicing inputs, this is usually not a problem. If interrupts are employed to any degree in dealing with MIC74 inputs, care must be taken to ensure that a software routine in the midst of making changes to outputs is not interrupted by another routine that proceeds to make its own changes. The risk is that the value in DATA will be changed by an interrupting routine after it is read by a different routine in the process of making its own changes. If this occurs, the value written to DATA by the first routine may be incorrect. The most straightforward solution to this potential problem is to disable system interrupts while the data register is actually being modified.

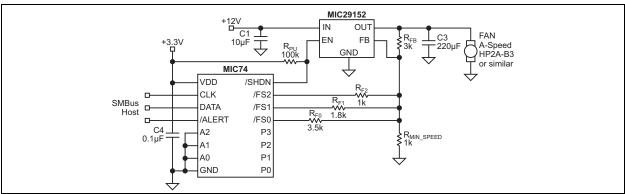

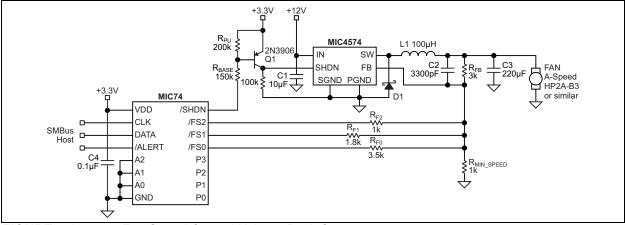

## 5.9 Application Circuits

The MIC74, in conjunction with a linear low-dropout or switching regulator, can be configured as a fan speed controller. Most adjustable regulators have a feedback pin and use an external resistor divider to adjust the output voltage. The MIC74 is designed to take advantage of this configuration with its ability to manipulate multiple feedback resistors connected to the P4–P7 outputs. Individual open-drain output bits are selectively grounded or allowed to float under the control of the internal state machine. This action raises or lowers the equivalent resistance seen in the regulator's feedback path, thus changing the output voltage.

Any conventional adjustable regulator is usually suitable for use with the MIC74. The output voltage corresponding to each value to be programmed into the fan speed register can be determined by selecting the resistors in the circuit. The regulator itself can be chosen to meet the needs of the application, such as input voltage, output voltage, current handling capability, maximum power dissipation, and physical space constraints.

The circuit of Figure 5-12 illustrates use of a typical LDO linear regulator such as the MIC29152. A switching regulator-based fan control circuit using the

MIC4574 200 kHz simple 0.5A buck regulator is shown in Figure 5-13. Both circuits assume a 12V fan power supply, but will accommodate much higher input voltages if required (MIC4574: 24V, MIC29152: 26V). Care must be taken, however, to ensure that the maximum power dissipation of the regulator is not exceeded. If the regulator overheats, its internal thermal shutdown circuitry will deactivate it. (See MIC29152 or MIC4574 data sheet.)

Because the MIC74 powers up with all its I/Os inputs (floating), both circuits will power-up with the fan running at a minimum speed determined by the value of  $R_{\text{MIN\_SPEED}}$ . Once the MIC74's fan mode is activated by setting the appropriate bit in the configuration register, the fan will be shutdown by the assertion of the /SHDN output if FAN\_SPEED is zero. If FAN\_SPEED is programmed with any nonzero value, the fan will be driven to its maximum speed for the duration of  $t_{\text{START}}$  (about 1 second) and then assume the programmed speed. Note that the circuit in Figure 5-13 contains an additional transistor, Q1, as an inverter because the regulator in this example has an active-high shutdown input rather than an enable input. Otherwise the circuits function identically.

FIGURE 5-12: Fan Speed Control Using an Adjustable Low-Dropout Regulator.

FIGURE 5-13: Fan Speed Control Using a Buck Converter.

Table 5-1 lists the output voltages corresponding to all the fan speeds and system states possible with these circuits. The following equations are used to calculate the resistor values used in MIC74 fan speed control circuits. It is assumed here that the regulator's internal reference voltage is 1.24V. If the regulator uses a different reference voltage, that value should be used instead.

The following equation shows how to calculate the resistor values for the fan controllers. For example, when the fan speed register contains 011b, which is the third lowest speed,  $R_{\text{F1}}$  and  $R_{\text{F0}}$  are parallel to  $R_{\text{MIN}}$  to give the equivalence resistor  $(R_{\text{EO}})$  value of  $545\Omega$ .

### **EQUATION 5-1:**

$$R_{EQ} = R_{F1} \parallel R_{F0} \parallel R_{MIN}$$

$$R_{EQ} = 1.8k\Omega \parallel 3.6k\Omega \parallel 1k\Omega$$

$$R_{EQ} = 545\Omega$$

The output voltage is calculated using Equation 5-2.

#### **EQUATION 5-2:**

$$V_{OUT} = 1.24V \left(1 + \frac{R_{FB}}{R_{EQ}}\right)$$

$$V_{OUT} = 1.24V \left(1 + \frac{3k\Omega}{545\Omega}\right)$$

$$V_{OUT} = 8.06V$$

TABLE 5-1: FAN SPEED SELECTION

| FAN_SPEED<br>Value     | Fan Speed<br>Selected | R <sub>FB</sub> | R <sub>MIN</sub> | R <sub>F2</sub> | R <sub>F1</sub> | R <sub>F0</sub> | R <sub>EQ</sub> | V <sub>OUT</sub> |

|------------------------|-----------------------|-----------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|

| 0000 0000 <sub>b</sub> | Power-up              | 3 kΩ            | 1 kΩ             | Open            | Open            | Open            | 1 kΩ            | 4.96V            |

| 0000 0000 <sub>b</sub> | Fan off               | 3 kΩ            | 1 kΩ             | Open            | Open            | Open            | 1 kΩ            | 0V               |

| 0000 0001 <sub>b</sub> | Lowest                | 3 kΩ            | 1 kΩ             | Open            | Open            | 3.6 kΩ          | 783Ω            | 5.99V            |

| 0000 0010 <sub>b</sub> | 2nd lowest            | 3 kΩ            | 1 kΩ             | Open            | 1.8 kΩ          | Open            | 643Ω            | 7.03V            |

| 0000 0011 <sub>b</sub> | 3rd lowest            | 3 kΩ            | 1 kΩ             | Open            | 1.8 kΩ          | 3.6 kΩ          | 545Ω            | 8.06V            |

| 0000 0100 <sub>b</sub> | Medium                | 3 kΩ            | 1 kΩ             | 1 kΩ            | Open            | Open            | 500Ω            | 8.68V            |

| 0000 0101 <sub>b</sub> | 3rd highest           | 3 kΩ            | 1 kΩ             | 1 kΩ            | Open            | 3.6 kΩ          | 439Ω            | 9.71V            |

| 0000 0110 <sub>b</sub> | 2nd highest           | 3 kΩ            | 1 kΩ             | 1 kΩ            | 1.8 kΩ          | Open            | 391Ω            | 10.75V           |

| 0000 0111 <sub>b</sub> | Highest               | 3 kΩ            | 1 kΩ             | 1 kΩ            | 1.8 kΩ          | 3.6 kΩ          | 353Ω            | 11.78V           |

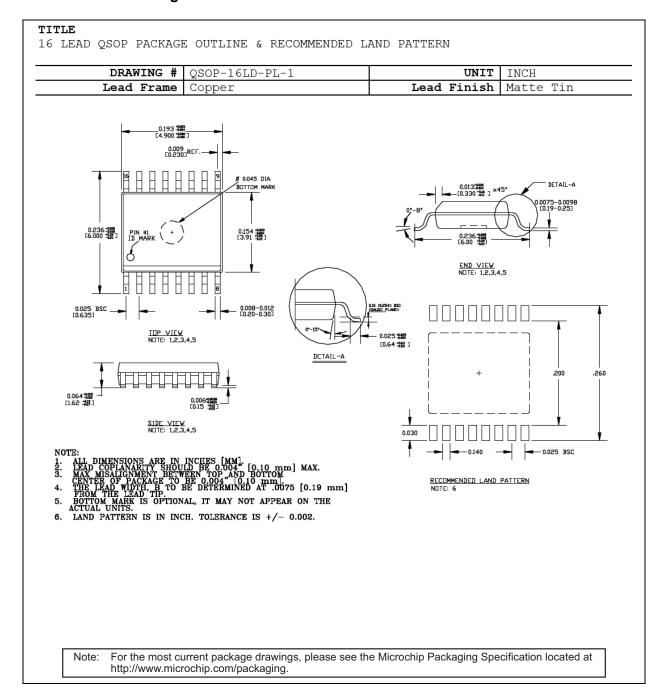

## 6.0 PACKAGING INFORMATION

# 6.1 Package Marking Information

16-Lead QSOP\*

Example

MIC 74YQS 8564

**Legend:** XX...X Product code or customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

•, ▲, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar (\_) and/or Overbar (¯) symbol may not be to scale.

# 16-Lead QSOP Package Outline and Recommended Land Pattern

NOTES:

# APPENDIX A: REVISION HISTORY

# Revision A (November 2020)

- Converted Micrel data sheet MIC74 to Microchip data sheet DS20005969A.

- Minor grammatical corrections throughout.

NOTES:

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

PART NO. X XX -XX

Device Junction Package Media Temp. Range Type

Device: MIC74:

2-Wire Serial I/O Expander and Fan Con-

troller

Junction

Temperature Range:

$Y = -40^{\circ}C \text{ to } +85^{\circ}C$

Package:

QS = 16-Lead QSOP

Examples:

a) MIC74YQS: MIC74, -40°C to +85°C Junction

Temperature Range, 16-Lead

QSOP, 98/Tube

b) MIC74YQS-TR: MIC74, -40°C to +85°C Junction

Temperature Range, 16-Lead

QSOP, 2,500/Reel

Note 1:

Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the

Tape and Reel option.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-7131-8

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423

Fax: 972-818-2924 **Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Fax: 317-773-5323 Fax: 317-773-5453 Tel: 317-536-2380 **Los Angeles**

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820