TLV320DAC3203

SLOS756B-MAY 2012-REVISED DECEMBER 2018

# TLV320DAC3203 Ultra Low Power Stereo Audio Codec With Integrated Headphone Amplifiers

### 1 Features

- Stereo Audio DAC with 100dB SNR

- 4.1mW Stereo 48ksps Playback

- PowerTune™

- Extensive Signal Processing Options

- Stereo Headphone Outputs

- · Low Power Analog Bypass Mode

- Programmable PLL

- Integrated LDO

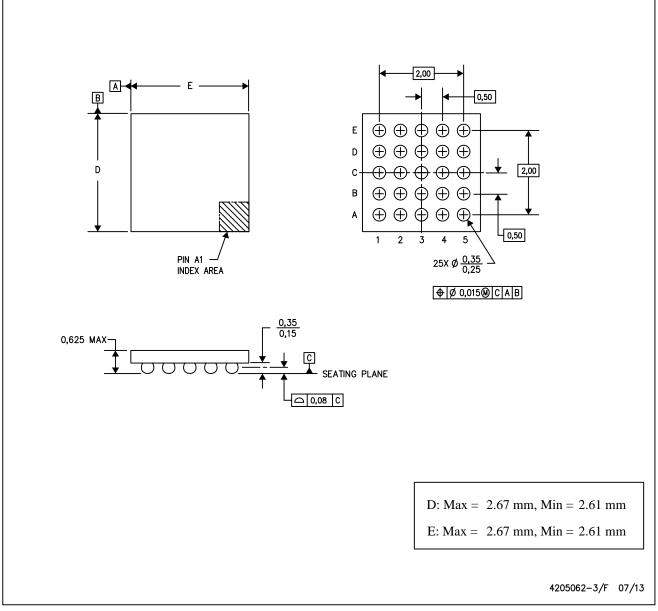

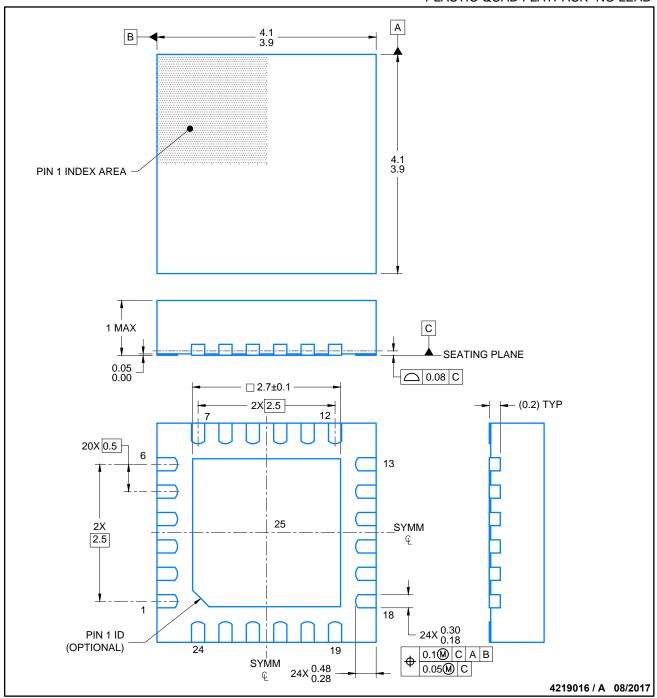

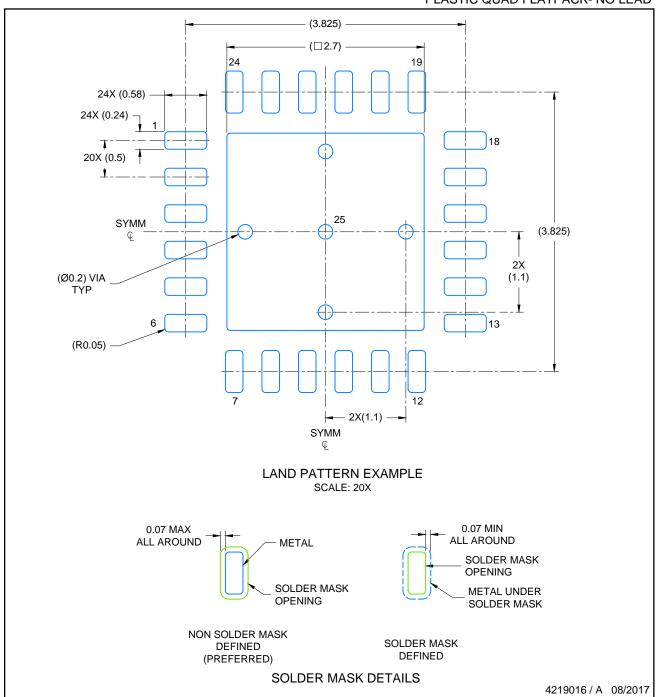

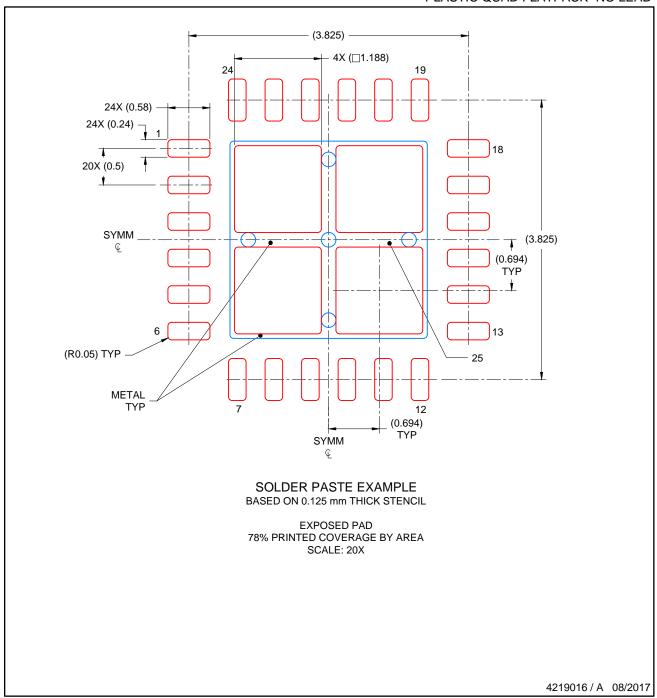

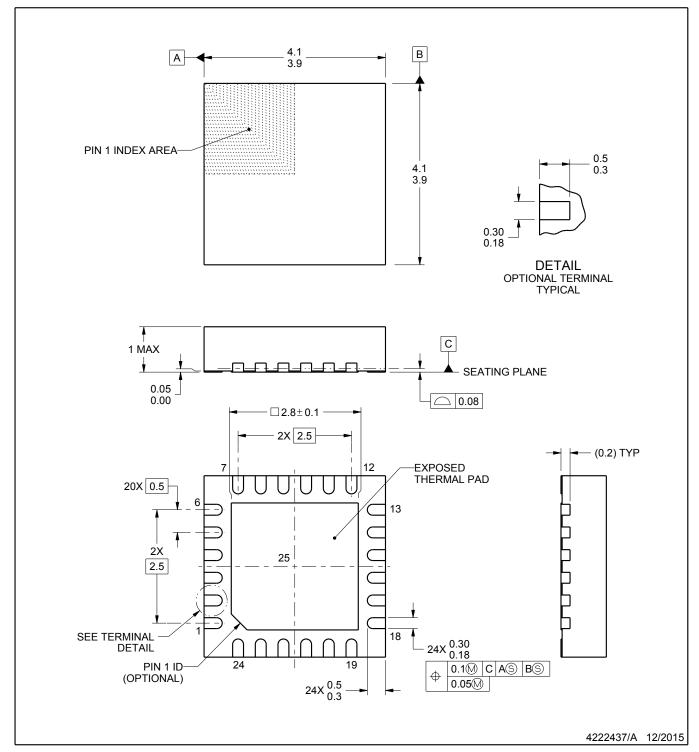

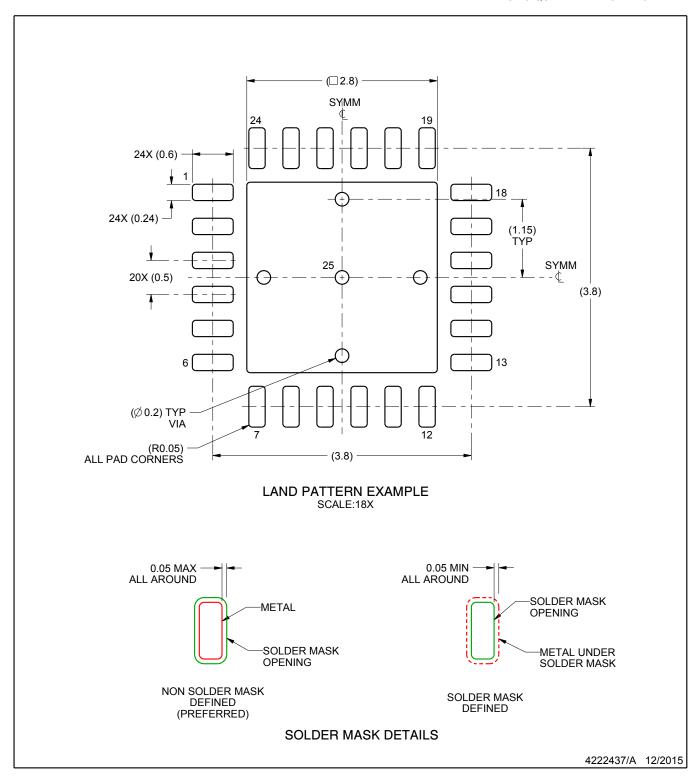

- 4 mm x 4 mm VQFN and 2.7 mm x 2.7 mm DSGBA Package

# 2 Applications

- Mobile Handsets

- Communication

- Portable Computing

# 3 Description

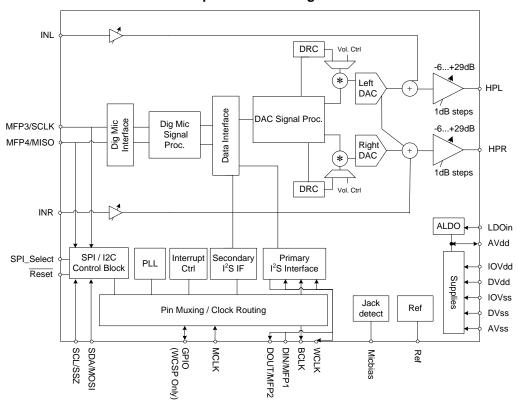

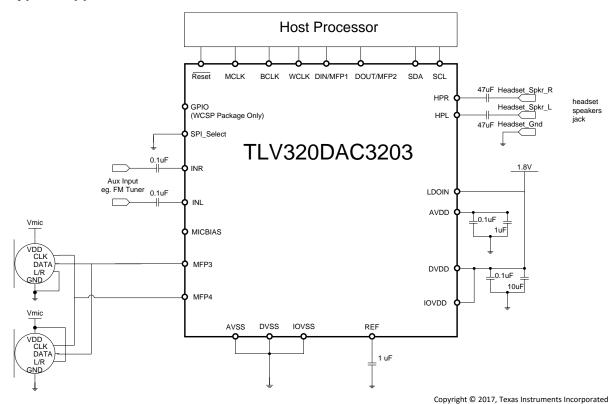

The TLV320DAC3203 (sometimes referred to as the DAC3203) is a flexible, low-power, low-voltage stereo audio codec with programmable outputs, PowerTune capabilities, fixed predefined and parameterizable signal processing blocks, integrated PLL, integrated LDO and flexible digital interfaces. Extensive register-based control of power, input/output channel configuration, gains, effects, pin-multiplexing and clocks is included, allowing the device to be precisely targeted to its application.

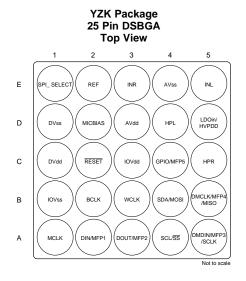

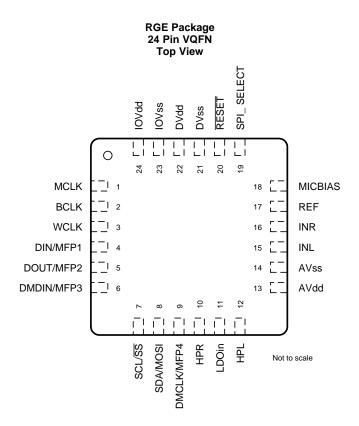

The device is available in the 4 mm  $\times$  4 mm VQFN and 2.7 mm  $\times$  2.7 mm DSGBA package.

#### Device Information<sup>(1)</sup>

| PART NUMBER   | PACKAGE    | BODY SIZE (NOM)   |  |  |

|---------------|------------|-------------------|--|--|

| TLV320DAC3203 | VQFN (24)  | 4.00 mm x 4.00 mm |  |  |

|               | DSBGA (25) | 2.70 mm x 2.70 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

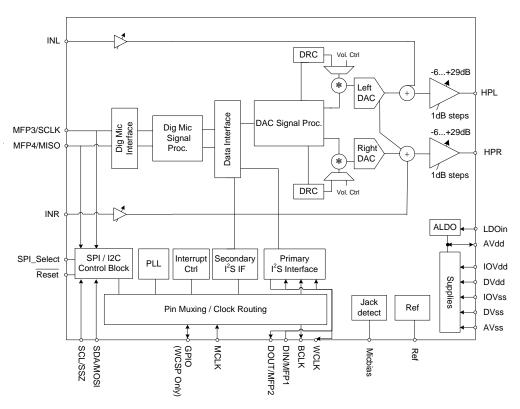

# **Simplified Block Diagram**

Copyright © 2017, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                                              | 7 Detailed Description 16                               |

|---|---------------------------------------------------------|---------------------------------------------------------|

| 2 | Applications 1                                          | 7.1 Overview 16                                         |

| 3 | Description 1                                           | 7.2 Functional Block Diagram 16                         |

| 4 | Revision History2                                       | 7.3 Feature Description                                 |

| 5 | Pin Configuration and Functions                         | 7.4 Device Functional Modes22                           |

| 6 | Specifications5                                         | 7.5 Register Maps23                                     |

| ٠ | 6.1 Absolute Maximum Ratings                            | 8 Application and Implementation 26                     |

|   | 6.2 ESD Ratings                                         | 8.1 Application Information26                           |

|   | 6.3 Recommended Operating Conditions                    | 8.2 Typical Application26                               |

|   | 6.4 Thermal Information                                 | 9 Power Supply Recommendations27                        |

|   | 6.5 Electrical Characteristics, Bypass Outputs 6        | 10 Layout 28                                            |

|   | 6.6 Electrical Characteristics, Microphone Interface 6  | 10.1 Layout Guidelines28                                |

|   | 6.7 Electrical Characteristics, Audio Outputs           | 10.2 Layout Example28                                   |

|   | 6.8 Electrical Characteristics, LDO9                    | 11 Device and Documentation Support 29                  |

|   | 6.9 Electrical Characteristics, Misc9                   | 11.1 Documentation Support29                            |

|   | 6.10 Electrical Characteristics, Logic Levels9          | 11.2 Receiving Notification of Documentation Updates 29 |

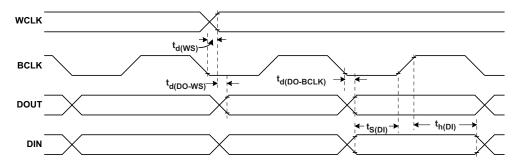

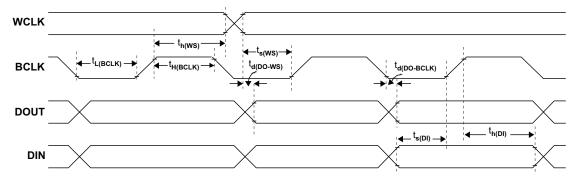

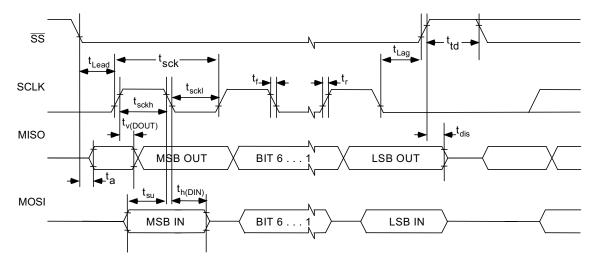

|   | 6.11 Typical Timing Characteristics — Audio Data Serial | 11.3 Community Resources29                              |

|   | Interface Timing (I <sup>2</sup> S)10                   | 11.4 Trademarks                                         |

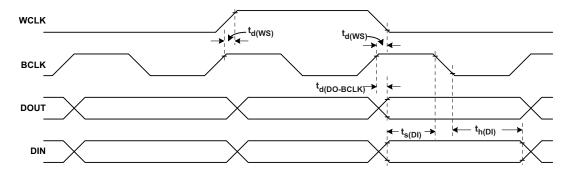

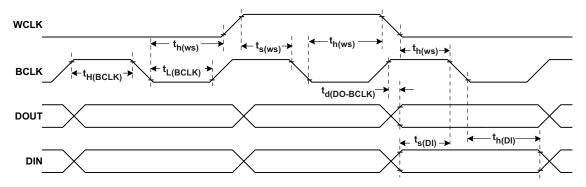

|   | 6.12 Typical DSP Timing Characteristics 11              | 11.5 Electrostatic Discharge Caution                    |

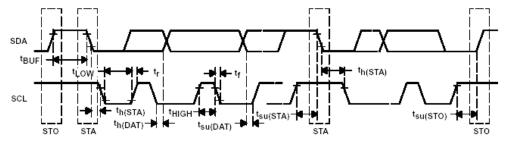

|   | 6.13 I <sup>2</sup> C Interface Timing 12               | 11.6 Glossary 29                                        |

|   | 6.14 SPI Interface Timing (See Figure 6)                | 12 Mechanical, Packaging, and Orderable                 |

|   | 6.15 Typical Characteristics14                          | Information 29                                          |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | hanges from Revision A (March 2017) to Revision B                              | Page |

|----|--------------------------------------------------------------------------------|------|

| •  | Changed Description of pin 7 in the Pin Functions table                        | 4    |

| •  | Changed TYPE and Description of pin 8 in the Pin Functions table               | 4    |

| •  | Changed pin 14 (ball E4) TYPE From: AVdd To: AVss in the Pin Functions table   | 4    |

| •  | Changed pin 21 (ball D1) TYPE From: DVdd To: DVss in the Pin Functions table   | 4    |

| •  | Changed pin 23 (ball B1) TYPE From: IOVdd To: IOVss in the Pin Functions table | 4    |

| •  | Changed ball C4 TYPE From: I To: I/O in the Pin Functions table                | 4    |

# Changes from Original (May 2012) to Revision A

Page

1

| mm × 2.7 mm DSGBA Package                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Added the Device Information table, Pin Configuration and Functions section, ESD Ratings table, Thermal Information table, Detailed Description section, Application and Implementation section, Device and Documentation |

| Support, and Mechanical, Packaging, and Orderable Information sections                                                                                                                                                    |

Submit Documentation Feedback

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN     |              |           |      |                                                     |

|---------|--------------|-----------|------|-----------------------------------------------------|

| QFN PIN | WCSP<br>BALL | NAME      | TYPE | DESCRIPTION                                         |

| 1       | A1           | MCLK      | I    | Master Clock Input                                  |

| 2       | B2           | BCLK      | Ю    | Audio serial data bus (primary) bit clock           |

| 3       | В3           | WCLK      | Ю    | Audio serial data bus (primary) word clock          |

| 4       | A2           | DIN/MFP1  | I    | Primary function                                    |

|         |              |           |      | Audio serial data bus data input                    |

|         |              |           |      | Secondary function                                  |

|         |              |           |      | Digital Microphone Input                            |

|         |              |           |      | General Purpose Input                               |

| 5       | A3           | DOUT/MFP2 | 0    | Primary                                             |

|         |              |           |      | Audio serial data bus data output                   |

|         |              |           |      | Secondary                                           |

|         |              |           |      | General Purpose Output                              |

|         |              |           |      | Clock Output                                        |

|         |              |           |      | INT1 Output INT2 Output                             |

|         |              |           |      | Audio serial data bus (secondary) bit clock output  |

|         |              |           |      | Audio serial data bus (secondary) word clock output |

# Pin Functions (continued)

| PIN     |              |                 |        | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN PIN | WCSP<br>BALL | NAME            | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6       | A5           | DMDIN/<br>MFP3/ | I      | Primary (SPI_Select = 1)     SPI serial clock  Secondary: (SPI_Select = 0)     Digital microphone input     Headset detect input     Audio serial data bus (secondary) bit clock input     Audio serial data bus (secondary) DAC/common word clock input     Audio serial data bus (secondary) ADC word clock input     Audio serial data bus (secondary) data input     General Purpose Input                                                                                                                     |

| 7       | A4           | SCL/<br>SS      | I      | Multi-function digital input.  For (SPI_SELECT=0): Clock Pin for I2C control bus.  For (SPI_SELECT = 1): SPI chip selection pin.                                                                                                                                                                                                                                                                                                                                                                                   |

| 8       | B4           | SDA/ MOSI       | I/O    | Multi-function digital pin.  For (SPI_SELECT=0): Data Pin for I2C control bus.  For (SPI_SELECT = 1): SPI data input.                                                                                                                                                                                                                                                                                                                                                                                              |

| 9       | B5           | DMCLK/<br>MFP4  | 0      | Primary (SPI_Select = 1) Serial data output  Secondary (SPI_Select = 0) Multifunction pin #4 (MFP4) options are only available using I <sup>2</sup> C  Digital microphone clock output General purpose output CLKOUT output INT1 output INT2 output Audio serial data bus (primary) ADC word clock output Audio serial data bus (secondary) data output Audio serial data bus (secondary) bit clock output Audio serial data bus (secondary) word clock output Audio serial data bus (secondary) word clock output |

| 10      | C5           | HPR             | 0      | Right high-power output driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11      | D5           | LDOin           | Power  | LDO Input supply and Headphone Power supply 1.9V- 3.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12      | D4           | HPL             | 0      | Left high power output driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13      | D3           | AVdd            | Power  | Analog voltage supply 1.5V–1.95V Input when A-LDO disabled, Filtering output when A-LDO enabled                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14      | E4           | AVss            | Ground | Analog ground supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15      | E5           | INL             | _      | Left Analog Bypass Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16      | E3           | INR             | 1      | Right Analog Bypass Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17      | E2           | REF             | 0      | Reference voltage output for filtering                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18      | D2           | MICBIAS         | 0      | Microphone bias voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19      | E1           | SPI_ SELECT     | I      | Control mode select pin (1 = SPI, 0 = I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20      | C2           | RESET           | I      | Reset (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 21      | D1           | DVss            | Ground | Digital Ground and Chip-substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22      | C1           | DVdd            | Power  | Digital voltage supply 1.26V–1.95V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 23      | B1           | IOVss           | Ground | I/O ground supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 24      | C3           | IOVdd           | Power  | I/O voltage supply 1.1V – 3.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| n/a     | C4           | GPIO/MFP5       | I/O    | Primary General Purpose digital IO Secondary CLKOUT Output INT1 Output INT2 Output Audio serial data bus ADC word clock output Audio serial data bus (secondary) bit clock output Audio serial data bus (secondary) word clock output Digital microphone clock output                                                                                                                                                                                                                                              |

Submit Documentation Feedback

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                           | MIN  | MAX         | UNIT |

|-------------------------------------------|------|-------------|------|

| AVdd to AVss                              | -0.3 | 2.2         | V    |

| DVdd to DVss                              | -0.3 | 2.2         | V    |

| IOVDD to IOVSS                            | -0.3 | 3.9         | ٧    |

| LDOIN to AVss                             | -0.3 | 3.9         | V    |

| Digital Input voltage                     | -0.3 | IOVDD + 0.3 | V    |

| Analog input voltage                      | -0.3 | AVdd + 0.3  | V    |

| Operating temperature range               | -40  | 85          | ô    |

| Storage temperature range                 | -58  | 125         | ô    |

| Junction temperature (T <sub>J</sub> Max) |      | 105         | °C   |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                              |                                                                                     |                                                             | VALUE      | UNIT |

|------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------|------------|------|

|                              |                                                                                     | Human-body model (HBM), YZK, per ANSI/ESDA/JEDEC JS-001 (1) | ±2000      | V    |

| V <sub>(ESD)</sub> discharge | Human-body model (HBM), RGE, per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2500                                                       | V          |      |

|                              | Charged-device model (CDM), YZK, per JEDEC specification JESD22-C101 (2)            | ±1000                                                       | \ <i>\</i> |      |

|                              | Charged-device model (CDM), RGE, per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500                                                       | V          |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. .

### 6.3 Recommended Operating Conditions

|                      |                                                                                                                                                                                                                                             |                                                                                                                                                     | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NOM | MAX  | UNIT |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| LDOIN <sup>(1)</sup> | Power Supply Voltage Range  DVdd  DVdd  DVdd  PLL Input Frequency  MCLK Master Clock Frequency  SCL SCL Clock Frequency  HPL, HPR  Stereo headphone output load resistance Headphone output load resistance Digital output load capacitance | Deferenced to AVac(2)                                                                                                                               | 1.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 3.6  |      |

| AVdd                 |                                                                                                                                                                                                                                             | Referenced to AVSS                                                                                                                                  | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.8 | 1.95 |      |

| IOVDD                |                                                                                                                                                                                                                                             | Referenced to IOVSS <sup>(2)</sup>                                                                                                                  | 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 3.6  | V    |

| DVdd                 |                                                                                                                                                                                                                                             | D-f                                                                                                                                                 | 1.65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.8 | 1.95 |      |

| DVdd <sup>(3)</sup>  |                                                                                                                                                                                                                                             | Referenced to DVSS(-)                                                                                                                               | 1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.8 | 1.95 |      |

|                      | DLI Input Fraguency                                                                                                                                                                                                                         | Clock divider uses fractional divide (D > 0), P=1, D <sub>Vdd</sub> ≥ 1.65V (See table in SLAU434, <i>Maximum TLV320DAC3203 Clock Frequencies</i> ) | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 20   | MHz  |

| PLL Input Frequency  | Clock divider uses integer divide<br>(D = 0), P=1, D <sub>Vdd</sub> ≥ 1.65V (Refer to table in SLAU434,<br><i>Maximum TLV320DAC3203 Clock Frequencies</i> )                                                                                 | 0.512                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20  | MHz  |      |

| MCLK                 | Master Clock Frequency                                                                                                                                                                                                                      | MCLK; Master Clock Frequency; D <sub>Vdd</sub> ≥ 1.65V                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 50   | MHz  |

| SCL                  | SCL Clock Frequency                                                                                                                                                                                                                         |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 400  | kHz  |

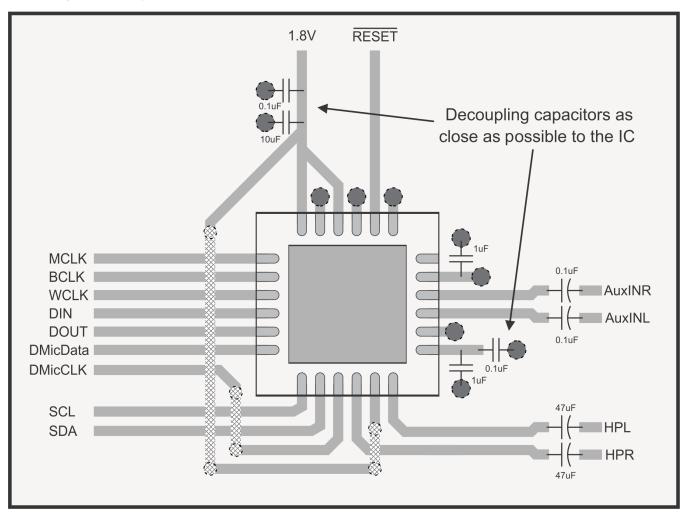

| LIDI LIDD            | Stereo headphone output load resistance                                                                                                                                                                                                     | Single-ended configuration                                                                                                                          | 14.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16  |      | Ω    |