19-5706; Rev 0; 12/10 EVALUATION KIT

AVAILABLE

**Up to 8.0Gbps Dual Passive Switches**

**Rates**

Signals

PART

MAX4888BETI+

MAX4888CETI+

\*EP = Exposed pad.

Single +3.3V Power-Supply Voltage

Superior Bandwidth Return Loss

Supports PCIe Gen I, Gen II, and Gen III Data

Small, 3.5mm x 5.5mm, 28-Pin TQFN Package

**TEMP RANGE**

-40°C to +85°C

-40°C to +85°C

+Denotes a lead(Pb)-free/RoHS-compliant package.

PIN-PACKAGE

28 TQFN-EP\*

28 TQFN-EP\*

### **General Description**

The MAX4888B/MAX4888C dual double-pole/doublethrow (2 x DPDT), high-speed passive switches are ideal for switching two half-lanes of PCI Express<sup>®</sup> (PCIe) data between two possible destinations. These devices feature a dual digital control input to switch signal paths. The MAX4888C is intended for use in systems where both the input and output are capacitively coupled (e.g., SAS, SATA, XAUI, and PCIe) and provides a 10µA (typ) source current and a  $60k\Omega$  (typ) internal biasing resistor to GND at the AOUT\_ and BOUT\_ pins.

The devices are fully specified to operate from a single +3.3V (typ) power supply. Both devices are available in an industry-standard 3.5mm x 5.5mm, 28-pin TQFN package. They operate over the -40°C to +85°C extended temperature range.

## **Applications**

**Desktop PCs** Notebook PCs Servers

PCI Express is a registered trademark of PCI-SIG Corp.

### **MIXI/N**

Maxim Integrated Products 1

Features **MAX48888B/MAX4888C** Supports Up To and Including 6.0Gbps SAS/SATA Supports Other High-Speed Interfaces (e.g., XAUI) **Ordering Information**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.)<br>Vcc0.3V to +4V   | Continuous Current (SEL, SELB)±10mA<br>Peak Current (SEL, SELB)                         |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| SEL, SELB, AIN+, AIN-, BIN+, BIN-, AOUTA+,<br>AOUTA-, AOUTB+, AOUTB-, BOUTA+, | (pulsed at 1ms, 10% duty cycle) $\pm$ 10mA<br>Continuous Power Dissipation (TA = +70°C) |

| BOUTA-, BOUTB+, BOUTB- (Note 1)0.3V to (VCC + 0.3V)                           | TQFN (derate 28.6mW/°C above +70°C)2286mW                                               |

| Continuous Current (AIN_ to AOUTA_/AOUTB_,                                    | Operating Temperature Range40°C to +85°C                                                |

| BIN_ to BOUTA_/BOUTB_) ±15mA                                                  | Junction Temperature+150°C                                                              |

| Peak Current (AIN_ to AOUTA_/AOUTB_,                                          | Storage Temperature Range65°C to +150°C                                                 |

| BIN_ to BOUTA_/BOUTB_)                                                        | Lead Temperature (soldering, 10s)+300°C                                                 |

| (pulsed at 1ms, 10% duty cycle) ±70mA                                         | Soldering Temperature (reflow)+260°C                                                    |

Note 1: Signals on SEL, SELB, AIN\_, BIN\_, AOUTA\_, AOUTB\_, BOUTA\_, and BOUTB\_ exceeding V<sub>CC</sub> or GND are clamped by internal diodes. Limit forward-diode current to maximum current rating.

### PACKAGE THERMAL CHARACTERISTICS (Note 2)

#### TQFN

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> =  $3.3V \pm 10\%$ , T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.) (Note 3)

| PARAMETER                               | SYMBOL                                                                                           | CONDITIONS                                                                                                                       | MIN  | TYP | MAX                      | UNITS |

|-----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------------|-------|

| DC PERFORMANCE                          |                                                                                                  |                                                                                                                                  |      |     |                          |       |

| Analog-Signal Range                     | Vinput                                                                                           | AIN_, BIN_, AOUTA_, BOUTA_, AOUTB_,<br>BOUTB_                                                                                    | -0.3 |     | V <sub>CC</sub> -<br>1.8 | V     |

| On-Resistance                           | n-Resistance $R_{ON}$ $V_{CC} = +3.0V, I_{AIN} = I_{BIN} = 15mA, V_{OUTA} = V_{OUTB} = 0V, 1.2V$ |                                                                                                                                  |      | 6.4 | 8.4                      | Ω     |

| On-Resistance Match<br>Between Channels | ΔR <sub>ON</sub>                                                                                 | $V_{CC} = +3.0V$ , $I_{AIN} = I_{BIN} = 15mA$ ,<br>$V_{OUTA} = V_{OUTB} = 0V$ (Note 4)                                           |      | 0.2 | 1.5                      | Ω     |

| On-Resistance Flatness                  | RFLAT(ON)                                                                                        | $V_{CC} = +3.0V, I_{AIN} = I_{BIN} = 15mA, V_OUTA_ = V_OUTB_ = 0V, 1.2V (Note 5)$                                                |      | 0.3 | 1                        | Ω     |

| _OUTA_ or _OUTB_<br>Off-Leakage Current | I_OUTA_(OFF),<br>I_OUTB_(OFF)                                                                    | V <sub>CC</sub> = +3.6V, V <sub>AIN</sub> = V <sub>BIN</sub> = 0V, 1.2V;<br>V_OUTA_ or V_OUTB_ = 1.2V, 0V<br>(MAX4888B)          | -1   |     | +1                       | μA    |

| AIN_, BIN_ On-Leakage Current           | Iain_(on),<br>Ibin_(on)                                                                          | $V_{CC} = +3.6V$ , $V_{AIN} = V_{BIN} = 0V$ , 1.2V;<br>$V_{OUTA}$ or $V_{OUTB} = V_{AIN} = V_{BIN}$ or<br>unconnected (MAX4888B) | -1   |     | +1                       | μA    |

| Output Short-Circuit Current            |                                                                                                  | All other ports are unconnected (MAX4888C)                                                                                       | 5    |     | 15                       | μA    |

| Output Open-Circuit Voltage             |                                                                                                  | All other ports are unconnected (MAX4888C)                                                                                       | 0.2  | 0.6 | 0.9                      | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> =  $3.3V \pm 10\%$ , T<sub>A</sub> =  $-40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 3.3V, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.) (Note 3)

| PARAMETER                           | SYMBOL      | CONDITIONS                                                             | MIN | ТҮР | MAX | UNITS |  |

|-------------------------------------|-------------|------------------------------------------------------------------------|-----|-----|-----|-------|--|

| AC PERFORMANCE                      |             |                                                                        |     |     |     |       |  |

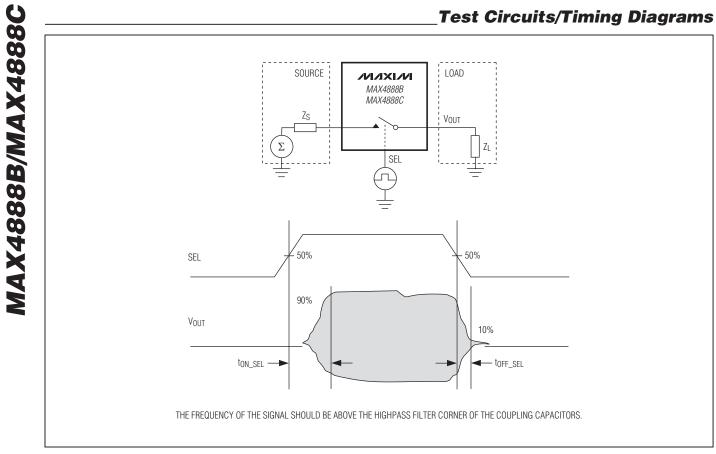

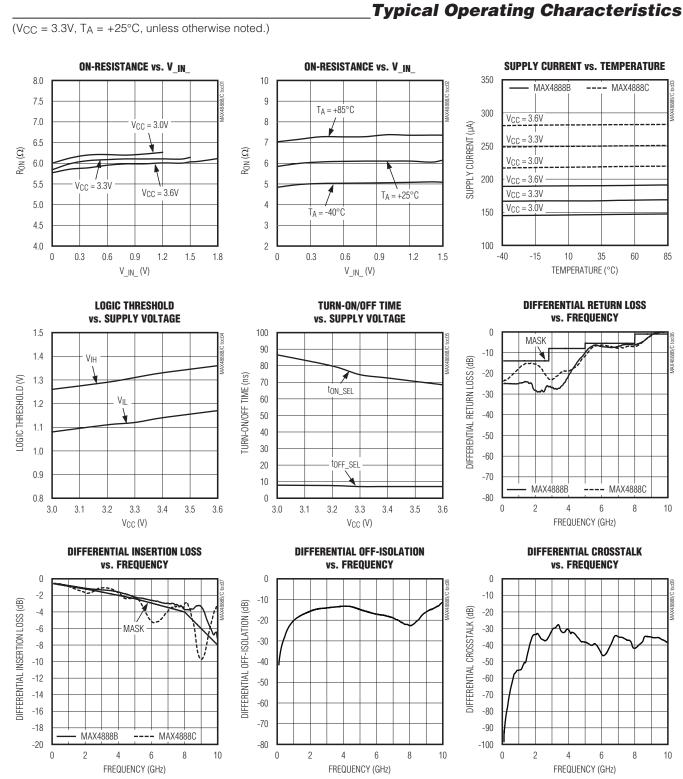

| Switch Turn-On Time                 | ton_sel     | $Z_{\rm S} = Z_{\rm L} = 50\Omega$                                     |     | 65  |     | ns    |  |

| Switch Turn-Off Time                | tOFF_SEL    | $Z_{\rm S}$ = $Z_{\rm L}$ = 50 $\Omega$ , Figure 1, measured at 500MHz |     | 7   |     | ns    |  |

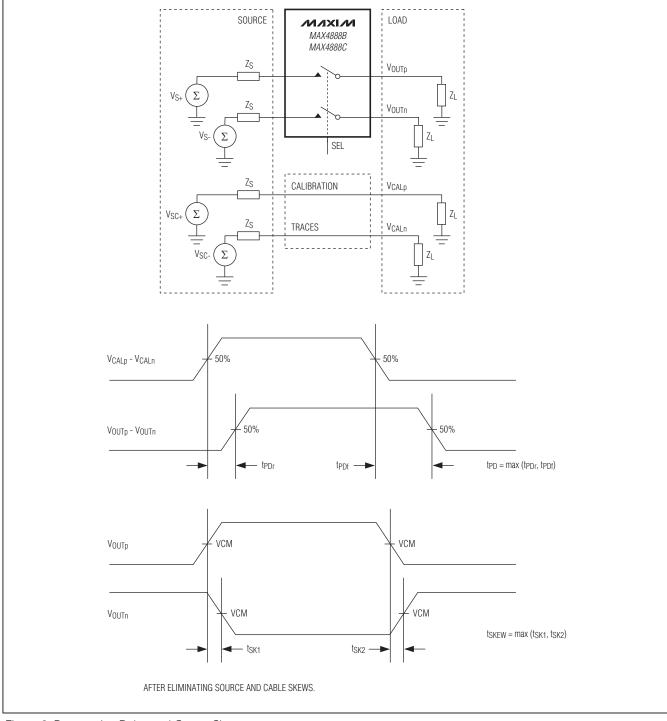

| Propagation Delay                   | tPD         | $Z_{\rm S}$ = $Z_{\rm L}$ = 50 $\Omega$ , Figure 2, measured at 500MHz |     | 43  |     | ps    |  |

| Output Skew Between Pairs           | tSK1        | $Z_{\rm S}$ = $Z_{\rm L}$ = 50 $\Omega$ , Figure 2, measured at 500MHz |     | 8   |     | ps    |  |

| Output Skew Between Same<br>Pair    | tSK2        | $Z_{S} = Z_{L} = 50\Omega$ , Figure2                                   |     | 10  |     | ps    |  |

|                                     |             | 0Hz < f ≤ 2.8GHz                                                       | -14 |     |     |       |  |

| Differential Daturn Loss (Note 6)   | S           | 2.8GHz < f ≤ 5.0GHz                                                    | -8  |     |     | dB    |  |

| Differential Return Loss (Note 6)   | SDD11       | 5.0GHz < f ≤ 8.0GHz                                                    | -5  |     |     |       |  |

|                                     |             | f > 8.0GHz                                                             | -1  |     |     |       |  |

| Differential Insertion Loss         | SDD21       | Table 1                                                                |     |     |     | dB    |  |

| Bandwidth                           | SDD12/SDD21 |                                                                        |     | 8   |     | GHz   |  |

|                                     | Sddctk      | $OHz < f \le 2.5GHz$                                                   |     | -30 |     | - dB  |  |

| Differential Crosstalk (Note 6)     |             | $2.5GHz < f \le 5.0GHz$                                                |     | -25 |     |       |  |

| Differential Crosstark (Note 0)     |             | $5.0GHz < f \le 8.0GHz$                                                |     | -35 |     |       |  |

|                                     |             | f > 8.0GHz                                                             |     | -35 |     |       |  |

|                                     | SDD21_OFF   | $OHz < f \le 2.5GHz$                                                   |     | -15 |     | - dB  |  |

| Differential Off-Isolation (Note 6) |             | $2.5GHz < f \le 5.0GHz$                                                |     | -12 |     |       |  |

| Differential Off-Isolation (Note 0) |             | $5.0GHz < f \le 8.0GHz$                                                |     | -12 |     | UD    |  |

|                                     |             | f > 8.0GHz                                                             |     | -12 |     |       |  |

| CONTROL INPUT                       |             |                                                                        |     |     |     |       |  |

| Input Logic-High                    | Vih         |                                                                        | 1.4 |     |     | V     |  |

| Input Logic-Low                     | VIL         |                                                                        |     |     | 0.6 | V     |  |

| Input Logic Hysteresis              | VHYST       |                                                                        |     | 130 |     | mV    |  |

| POWER SUPPLY                        |             |                                                                        |     |     |     |       |  |

| Power-Supply Range                  | Vcc         |                                                                        | 3.0 |     | 3.6 | V     |  |

| V <sub>CC</sub> Supply Current      | Icc         |                                                                        |     |     | 1   | mA    |  |

**Note 3:** All units are 100% production tested at  $T_A = +85^{\circ}$ C. Limits over the operating temperature range are guaranteed by design and characterization and are not production tested.

**Note 4:**  $\Delta RON = RON(MAX) - RON(MIN)$ .

Note 5: Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over the specified analog-signal range.

Note 6: Guaranteed by design; not production tested.

Figure 1. Switching Time

## **Table 1. Insertion Loss Mask**

| FREQUENCY RANGE (GHz) | MAXIMUM INSERTION LOSS (dB)    |

|-----------------------|--------------------------------|

| 0 to 2.5              | 1/3 × f <sub>GHZ</sub> + 17/30 |

| 2.5 to 5              | 2/5 x fGHZ - 2/5               |

| 5 to 8                | 18/5 x f <sub>GHZ</sub> - 4/15 |

| Greater than 8        | 2 x fgHz - 12                  |

## Test Circuits/Timing Diagrams (continued)

Figure 2. Propagation Delay and Output Skew

**MAX4888B/MAX4888C**

MAX4888B/MAX4888C

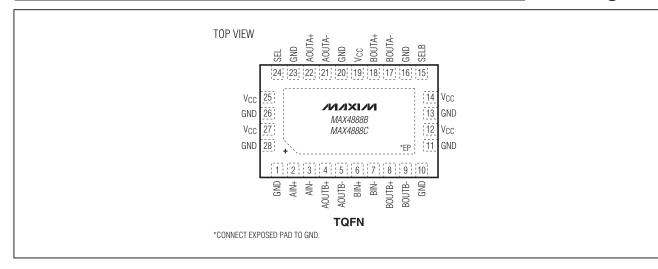

### **Pin Configuration**

### \_Pin Description

| PIN                                        | NAME   | FUNCTION                                                                                                                                                                                                                |

|--------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 10, 11,<br>13, 16,<br>20, 23,<br>26, 28 | GND    | Ground                                                                                                                                                                                                                  |

| 2                                          | AIN+   | Analog Switch 1, Common Positive Terminal                                                                                                                                                                               |

| 3                                          | AIN-   | Analog Switch 1, Common Negative Terminal                                                                                                                                                                               |

| 4                                          | AOUTB+ | Analog Switch 1, Normally Open Positive Terminal                                                                                                                                                                        |

| 5                                          | AOUTB- | Analog Switch 1, Normally Open Negative Terminal                                                                                                                                                                        |

| 6                                          | BIN+   | Analog Switch 2, Common Positive Terminal                                                                                                                                                                               |

| 7                                          | BIN-   | Analog Switch 2, Common Negative Terminal                                                                                                                                                                               |

| 8                                          | BOUTB+ | Analog Switch 2, Normally Open Positive Terminal                                                                                                                                                                        |

| 9                                          | BOUTB- | Analog Switch 2, Normally Open Negative Terminal                                                                                                                                                                        |

| 12, 14,<br>19, 25,<br>27                   | Vcc    | Positive Supply-Voltage Input. Connect $V_{CC}$ to a 3.0V to 3.6V supply voltage. Bypass $V_{CC}$ to GND with a 0.1µF ceramic capacitor placed as close as possible to the device. See the <i>Board Layout</i> section. |

| 15                                         | SELB   | Control Signal Input. SELB has a 70k $\Omega$ (typ) pullup resistor to V <sub>CC</sub> . If SELB is not in use, leave unconnected.                                                                                      |

| 17                                         | BOUTA- | Analog Switch 2, Normally Closed Negative Terminal                                                                                                                                                                      |

| 18                                         | BOUTA+ | Analog Switch 2, Normally Closed Positive Terminal                                                                                                                                                                      |

| 21                                         | AOUTA- | Analog Switch 1, Normally Closed Negative Terminal                                                                                                                                                                      |

| 22                                         | AOUTA+ | Analog Switch 1, Normally Closed Positive Terminal                                                                                                                                                                      |

| 24                                         | SEL    | Control Signal Input. SEL has a 70k $\Omega$ (typ) pulldown resistor to GND.                                                                                                                                            |

|                                            | EP     | Exposed Pad. Connect EP to GND.                                                                                                                                                                                         |

**MAX4888B/MAX4888C**

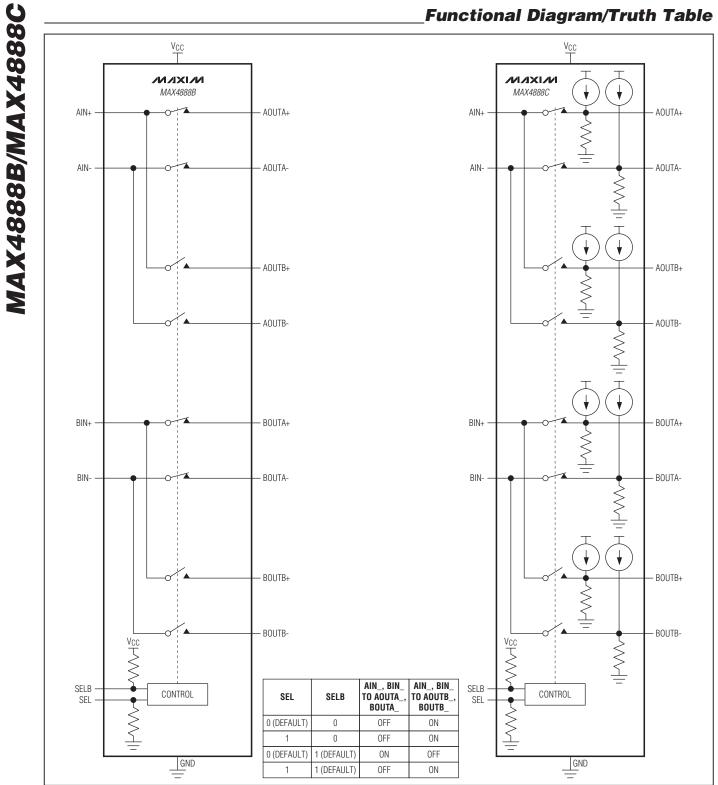

Functional Diagram/Truth Table

M/IXI/M

### **Detailed Description**

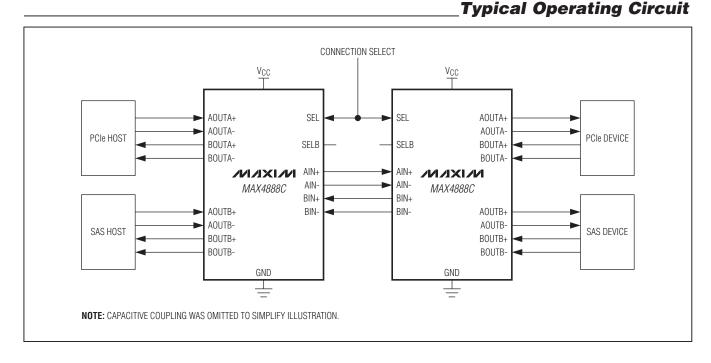

The MAX4888B high-speed passive switch routes highspeed differential signals such as PCIe, SAS, SATA, and XAUI from one source to two possible destinations or vice versa. The MAX4888B is ideal for routing PCIe signals to change the system configuration. The MAX4888C features a 10µA (typ) source current and a 60k $\Omega$  (typ) internal biasing resistor to GND at the AOUTA\_, BOUTA\_, AOUTB\_, and BOUTB\_ terminals. The MAX4888C is ideal for circuits that are capacitively coupled at both the output and input. These devices are protocol independent and can be used to switch two different protocol signals over the same physical lane. They feature dual digital control inputs (SEL, SELB) to switch signal paths. SEL has a 70k $\Omega$  (typ) pulldown resistor to GND and SELB has a 70k $\Omega$  (typ) pullup resistor to V<sub>CC</sub>.

These devices are fully specified to operate from a single 3.0V to 3.6V power supply.

#### **Digital Control Input (SEL, SELB)**

The devices provide dual digital control inputs (SEL, SELB) to select the signal path between the AIN\_, BIN\_ and AOUTA\_, BOUTA\_ or AOUTB\_, BOUTB\_ channels. In most cases SEL is chosen and SELB is unconnected. The truth table for the devices is depicted in the *Functional Diagram/Truth Table*. SEL has a 70k $\Omega$  (typ) pulldown resistor to GND and SELB has a 70k $\Omega$  (typ) pullup resistor to V<sub>CC</sub>.

#### **Analog-Signal Levels**

The devices accept signals from -0.3V to (VCC - 1.8V). Signals on the AIN+ and BIN+ channels are routed to either the AOUTA+, BOUTA+ or AOUTB+, BOUTB+ channels. Signals on the AIN- and BIN- channels are routed to either the AOUTA-, BOUTA- or AOUTB-, BOUTBchannels. The devices are bidirectional switches, allowing AIN\_, BIN\_ and AOUTA\_, BOUTA\_, AOUTB\_, and BOUTB\_ to be used as either inputs or outputs.

### **Applications Information**

#### **High-Speed Switching**

The devices' primary applications are aimed at sharing resources. For example, a single lane of PCIe or SAS can be shared between a single host and two devices. This could be used for redundancy or to share resources such as a physical lane or route a lane between one host and two devices or two hosts and one device.

#### **Board Layout**

High-speed switches require proper layout and design procedures for optimum performance. Keep controlled impedance PCB traces as short as possible or follow impedance layouts per the PCIe specification. Ensure that power-supply bypass capacitors are placed as close as possible to the device. Multiple bypass capacitors are recommended. Connect all grounds and the exposed pad to a large ground plane.

#### **Chip Information**

PROCESS: CMOS

### Package Information

For the latest package outline information and land patterns, go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE   | OUTLINE        | LAND           |

|------------|-----------|----------------|----------------|

| TYPE       | CODE      | NO.            | PATTERN NO.    |

| 28 TQFN-EP | T283555+1 | <u>21-0184</u> | <u>90-0123</u> |

### \_Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 12/10            | Initial release | —                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

$\_$  Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2010 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated: MAX4888BETI+ MAX4888CETI+ MAX4888BETI+T MAX4888CETI+T