## Low Voltage Quad Buffer with 5 V Tolerant Inputs and Outputs

#### 74LCX125

#### Description

The LCX125 contains four independent non-inverting buffers with 3-STATE outputs. The inputs tolerate Voltages up to 7 V Allowing the interface of 5 V Systems to 3 V Systems.

The 74LCX125 is fabricated with an advanced CMOS technology to achieve high Speed operation while Maintaining CMOS Low Power Dissipation.

#### **Features**

- 5 V Tolerant Inputs and Outputs

- 2.3 V–3.6 V V<sub>CC</sub> Specifications Provided

- 6.0 ns  $t_{PD}$  max. ( $V_{CC} = 3.3 \text{ V}$ ), 10  $\mu$ A  $I_{CC}$  max.

- Power Down High Impedance Inputs and Outputs

- Supports Live Insertion/Withdrawal\*

- $\pm 24$  mA Output Drive ( $V_{CC} = 3.0 \text{ V}$ )

- Latch-up Performance Exceeds JEDEC 78 Conditions

- ESD Performance:

- ♦ Human body model > 2000 V

- ♦ Machine model > 100 V

- Leadless DQFN Package

SOIC14, CASE 751EF

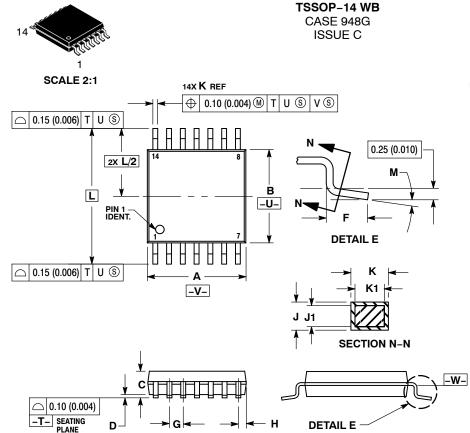

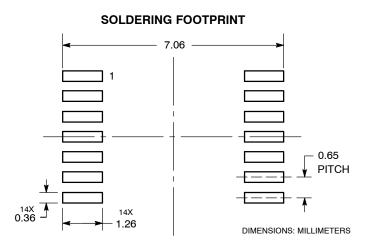

TSSOP-14, WB CASE 948G

QFN14, 3.0X2.5, 0.5P CASE 510CB

#### **MARKING DIAGRAM**

ZXYKK LCX125

Z = Assembly Plan Code XY = Date Code (Year & Week) KK = Lot Run Traceability Code LCX125 = Specific Device Code

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet.

<sup>\*</sup>To ensure the High–Impedance State During Power up or down,  $\overline{\text{OE}}$  Should be tied to  $V_{CC}$  through a pull–up resistor: the minimum value of the resistor is determined by the current–sourcing capability of the driver.

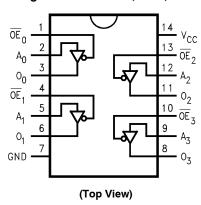

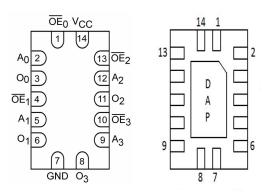

#### **Connection Diagrams**

#### Pin Assignments for SOIC, SOP, and TSSOP

#### **Pad Assignments for DQFN**

(Bottom View)

Pin Description

(Top Through View)

| Pin Names      | Description          |

|----------------|----------------------|

| A <sub>n</sub> | Inputs               |

| ŌĒn            | Output Enable Inputs |

| On             | Outputs              |

| DAP            | No Connect           |

Note: DAP (Die Attach Pad)

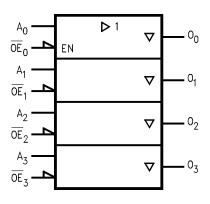

#### **Logic Symbol**

#### IEEE/IEC

#### **Truth Table**

| Inp | Output         |                |

|-----|----------------|----------------|

| ŌΕn | A <sub>n</sub> | O <sub>n</sub> |

| L   | L              | L              |

| L   | Н              | Н              |

| Н   | Х              | Z              |

H = HIGH Voltage Level

L = HIGH Voltage Level

Z = HIGH Impedance

X = Immaterial

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                                                       | Ratings                                           | Unit     |

|------------------|---------------------------------------------------------------------------------|---------------------------------------------------|----------|

| V <sub>CC</sub>  | Supply Voltage                                                                  | -0.5 to +7.0                                      | V        |

| VI               | DC Input Voltage                                                                | -0.5 to +7.0                                      | V        |

| Vo               | DC Output Voltage,  - Output in 3-STATE  - Output in HIGH or LOW State (Note 1) | −0.5 V to +7.0<br>−0.5 V to V <sub>CC</sub> + 0.5 | V V      |

| I <sub>IK</sub>  | DC Input Diode Current, V <sub>I</sub> < GND                                    | -50                                               | mA       |

| I <sub>OK</sub>  | DC Input Diode Current - VO < GND - VO > VCC                                    | -50<br>+50                                        | mA<br>mA |

| I <sub>O</sub>   | DC Output Source/Sink Current                                                   | ±50                                               | mA       |

| I <sub>CC</sub>  | DC Supply Current per Supply Pin                                                | ±50                                               | mA       |

| I <sub>GND</sub> | DC Ground Current per Ground Pin                                                | ±100                                              | mA       |

| T <sub>STG</sub> | Storage Temperature                                                             | -65 to +150                                       | °C       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **RECOMMENDED OPERATING CONDITIONS** (Note 4)

| Symbol                            | Parameter                                                                                                                       | Min.       | Max.                   | Unit |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------|------------------------|------|

| V <sub>CC</sub>                   | Supply Voltage  - Operating  - Data Retention                                                                                   | 2.0<br>1.5 | 3.6<br>3.6             | V    |

| VI                                | Input Voltage                                                                                                                   | 0          | 5.5                    | V    |

| Vo                                | Output Voltage - HIGH or LOW State - 3-STATE                                                                                    | 0          | V <sub>CC</sub><br>5.5 | V    |

| I <sub>OH</sub> / I <sub>OL</sub> | Common-mode Input Voltage - V <sub>CC</sub> = 3.0 V - 3.6 V - V <sub>CC</sub> = 2.7 V - 3.0 V - V <sub>CC</sub> = 2.3 V - 2.7 V |            | ±24<br>±12<br>±8       | mA   |

| T <sub>A</sub>                    | Free-Air Operating Temperature                                                                                                  | -40        | 85                     | °C   |

| Δt / ΔV                           | Input Edge Rate, V <sub>IN</sub> = 0.8 V – 2.0 V, V <sub>CC</sub> = 3.0 V                                                       | 0          | 10                     | ns/V |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

2. Unused inputs must be held HIGH or LOW. They may not float..

#### DC ELECTRICAL CHARACTERISTICS

|                 |                           |                     |                          | T <sub>A</sub> = -40°C | to +85°C |      |

|-----------------|---------------------------|---------------------|--------------------------|------------------------|----------|------|

| Symbol          | Parameter                 | V <sub>CC</sub> (V) | Test Conditions          | Min.                   | Max.     | Unit |

| V <sub>IH</sub> | HIGH Level Input Voltage  | 2.3–2.7             |                          | 1.7                    |          | V    |

|                 |                           | 2.7–3.6             |                          | 2.0                    |          |      |

| V <sub>IL</sub> | LOW Level Input Voltage   | 2.3–2.7             |                          | -                      | 0.7      | V    |

|                 |                           | 2.7–3.6             |                          | -                      | 0.8      |      |

| V <sub>OH</sub> | HIGH Level Output Voltage | 2.3–3.6             | $I_{OH} = -100 \mu A$    | V <sub>CC</sub> - 0.2  | _        | V    |

|                 |                           | 2.3                 | I <sub>OH</sub> = -8 mA  | 1.8                    | -        |      |

|                 |                           | 2.7                 | I <sub>OH</sub> = -12 mA | 2.2                    | -        |      |

|                 |                           | 3.0                 | I <sub>OH</sub> = -18mA  | 2.4                    | -        |      |

|                 |                           |                     | I <sub>OH</sub> = -24 mA | 2.2                    | _        |      |

<sup>1.</sup> I<sub>O</sub> Absolute Maximum Rating must be observed.

#### DC ELECTRICAL CHARACTERISTICS (continued)

|                  |                                       |                     |                                                                                         | T <sub>A</sub> = -40°0 | C to +85°C |      |

|------------------|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------|------------------------|------------|------|

| Symbol           | Parameter                             | V <sub>CC</sub> (V) | Test Conditions                                                                         | Min.                   | Max.       | Unit |

| V <sub>OL</sub>  | LOW Level Output Voltage              | 2.3–3.6             | I <sub>OL</sub> = 100 μA                                                                | -                      | 0.2        | V    |

|                  |                                       | 2.3                 | I <sub>OL</sub> = 8 mA                                                                  | -                      | 0.6        |      |

|                  |                                       | 2.7                 | I <sub>OL</sub> = 12 mA                                                                 | -                      | 0.4        |      |

|                  |                                       | 3.0                 | I <sub>OL</sub> = 16 mA                                                                 | -                      | 0.4        |      |

|                  |                                       |                     | I <sub>OL</sub> = 24 mA                                                                 | -                      | 0.55       |      |

| I <sub>I</sub>   | Input Leakage Current                 | 2.3–3.6             | $0 \le V_I \le 5.5 \text{ V}$                                                           | -                      | ±5.0       | μА   |

| I <sub>OZ</sub>  | 3-STATE Output Leakage                | 2.3–3.6             | $0 \le V_O \le 5.5 \text{ V},$<br>$V_I = V_{IH} \text{ or VIL}$                         | _                      | ±5.0       | μА   |

| IO <sub>FF</sub> | Power-Off Leakage Current             | 0                   | $V_I$ or $V_O = 5.5 \text{ V}$                                                          | -                      | 10         | μА   |

| I <sub>CC</sub>  | Quiescent Supply Current              | 2.3–3.6             | VI = V <sub>CC</sub> or GND                                                             | -                      | 10         | μΑ   |

|                  |                                       |                     | $3.6 \text{ V} \le \text{V}_{\text{I}}, \text{V}_{\text{O}} \le 5.5 \text{ V}$ (Note 3) | _                      | ±10        |      |

| $\Delta I_{CC}$  | Increase in I <sub>CC</sub> per Input | 2.3–3.6             | $V_{IH} = V_{CC} - 0.6 V$                                                               | _                      | 500        | μΑ   |

<sup>3.</sup> Outputs disabled or 3-STATE only.

#### **AC ELECTRICAL CHARACTERISTICS**

|                                       |                                |                                             | TA = -40°C to +85°C, $R_L$ = 500 $\Omega$ |                                       |      |                                             |      |      |

|---------------------------------------|--------------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------|------|---------------------------------------------|------|------|

|                                       |                                | $V_{CC}$ = 3.3 V $\pm$ 0.3 V, $C_L$ = 50 pF |                                           | V <sub>CC</sub> = C <sub>L</sub> = \$ |      | V <sub>CC</sub> = 2.5<br>C <sub>L</sub> = 3 |      |      |

| Symbol                                | Parameter                      | Min.                                        | Max.                                      | Min.                                  | Max. | Min.                                        | Max. | Unit |

| t <sub>PHL</sub> , t <sub>PLH</sub>   | Propagation Delay              | 1.5                                         | 6.0                                       | 1.5                                   | 6.5  | 1.5                                         | 7.2  | ns   |

| t <sub>PZL</sub> , t <sub>PZH</sub>   | Output Enable Time             | 1.5                                         | 7.0                                       | 1.5                                   | 8.0  | 1.5                                         | 9.1  | ns   |

| t <sub>PLZ</sub> , t <sub>PHZ</sub>   | Output Disable Time            | 1.5                                         | 6.0                                       | 1.5                                   | 7.0  | 1.5                                         | 7.2  | ns   |

| t <sub>OSHL</sub> , t <sub>OSLH</sub> | Output to Output Skew (Note 4) | -                                           | 1.0                                       | _                                     | -    | _                                           | -    | ns   |

<sup>4.</sup> Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (toshl) or LOW-to-HIGH (toslh).

#### **DYNAMIC SWITCHING CHARACTERISTICS**

|                  |                                           |                     |                                                                     | T <sub>A</sub> = 25°C |      |

|------------------|-------------------------------------------|---------------------|---------------------------------------------------------------------|-----------------------|------|

| Symbol           | Parameter                                 | V <sub>CC</sub> (V) | Test Conditions                                                     | Typical               | Unit |

| V <sub>OLP</sub> | Quiet Output Dynamic Peak V <sub>OL</sub> | 3.3                 | $C_L = 50 \text{ pF}, V_{IH} = 3.3 \text{ V}, V_{IL} = 0 \text{ V}$ | 0.8                   | V    |

|                  |                                           | 2.5                 | $C_L = 30 \text{ pF}, V_{IH} = 2.5 \text{ V}, V_{IL} = 0 \text{ V}$ | 0.6                   |      |

| V <sub>OLV</sub> | Quiet Output Dynamic Peak V <sub>OL</sub> | 3.3                 | $C_L = 50 \text{ pF}, V_{IH} = 3.3 \text{ V}, V_{IL} = 0 \text{ V}$ | -0.8                  | V    |

|                  |                                           | 2.5                 | $C_L = 30 \text{ pF}, V_{IH} = 2.5 \text{ V}, V_{IL} = 0 \text{ V}$ | -0.6                  |      |

#### **CAPACITANCE**

| Symbol           | Parameter                     | Test Conditions                                                            | Typical | Unit |

|------------------|-------------------------------|----------------------------------------------------------------------------|---------|------|

| C <sub>IN</sub>  | Input Capacitance             | V <sub>CC</sub> = Open, V <sub>I</sub> = 0 V or V <sub>CC</sub>            | 7.0     | pF   |

| C <sub>OUT</sub> | Output Capacitance            | $V_{CC} = 3.3 \text{ V}, V_I = 0 \text{ V or } V_{CC}$                     | 8.0     | pF   |

| C <sub>PD</sub>  | Power Dissipation Capacitance | $V_{CC} = 3.3 \text{ V}, V_I = 0 \text{ V or } V_{CC}, f = 10 \text{ MHz}$ | 25.0    | pF   |

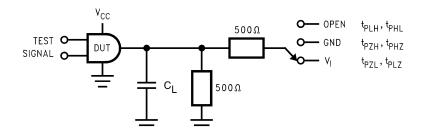

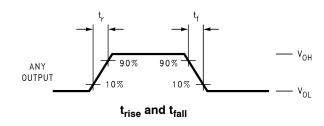

#### AC LOADING AND WAVEFORMS (GENERIC FOR LCX FAMILY)

| Test                                | Switch                                                              |  |

|-------------------------------------|---------------------------------------------------------------------|--|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Open                                                                |  |

| t <sub>PZL</sub> , t <sub>PLZ</sub> | 6V at $V_{CC}$ = 3.3 ± 0.3 V $V_{CC}$ x 2 at $V_{CC}$ = 2.5 ± 0.2 V |  |

| t <sub>PZH</sub> , t <sub>PHZ</sub> | GND                                                                 |  |

Figure 1. AC Test Circuit (C<sub>L</sub> includes probe and jig capacitance)

#### **Waveform for Inverting and Non-Inverting Functions**

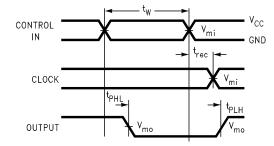

#### Propagation Delay. Pulse Width and t<sub>rec</sub> Waveforms

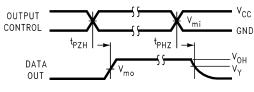

3-STATE Output Low Enable and Disable Times for Logic

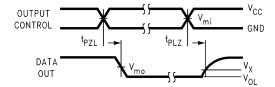

### 3-STATE Output High Enable and Disable Times for Logic

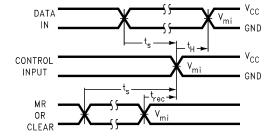

Setup Time, Hold Time and Recovery Time for Logic

|                 | V <sub>CC</sub>         |                         |                          |

|-----------------|-------------------------|-------------------------|--------------------------|

| Symbol          | 3.3 V + 0.3 V           | 2.7 V                   | 2.5 V + 0.2 V            |

| V <sub>mi</sub> | 1.5 V                   | 1.5 V                   | V <sub>CC</sub> /2       |

| V <sub>mo</sub> | 1.5 V                   | 1.5 V                   | V <sub>CC</sub> /2       |

| V <sub>x</sub>  | V <sub>OL</sub> + 0.3 V | V <sub>OL</sub> + 0.3 V | V <sub>OL</sub> + 0.15 V |

| V <sub>y</sub>  | V <sub>OH</sub> – 0.3 V | V <sub>OH</sub> – 0.3 V | V <sub>OH</sub> – 0.15 V |

Figure 2. Waveforms (Input Characteristics; f = 1 MHz,  $t_r = t_f = 3$  ns)

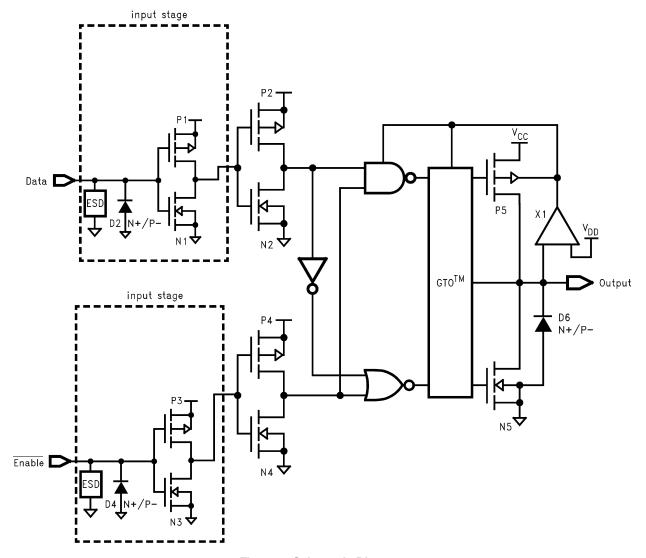

#### SCHEMATIC DIAGRAM (GENERIC FOR LCX FAMILY)

Figure 3. Schematic Diagram

#### **ORDERING INFORMATION**

| Product Number       | Package                              | Shipping <sup>†</sup> |

|----------------------|--------------------------------------|-----------------------|

| 74LCX125M            | SOIC-14<br>(Pb-Free/Halide Free)     | 1150 Units / Tube     |

| 74LCX125MX           | SOIC-14<br>(Pb-Free/Halide Free)     | 2500 / Tape and Reel  |

| 74LCX125MTCX         | TSSOP-14 WB<br>(Pb-Free/Halide Free) | 2500 / Tape and Reel  |

| 74LCX125BQX (Note 5) | QFN-14<br>(Pb-Free/Halide Free)      | 3000 / Tape and Reel  |

| 74LCX125MTC          | TSSOP-14 WB<br>(Pb-Free/Halide Free) | 2350 Units / Tube     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

<sup>5.</sup> DQFN package available in Tape and Reel only.

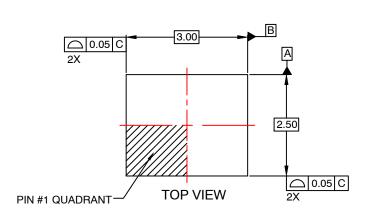

#### QFN14 3.0x2.5, 0.5P CASE 510CB **ISSUE O**

**DATE 31 AUG 2016**

RECOMMENDED LAND PATTERN

0.80±0.05-// 0.10 C 0.08 C C 0.025±0.025 SIDE VIEW SEATING **PLANE**

# -0.20±0.05

#### 3.00±0.05 1.65±0.05 -0.370±0.05 2 (14X) PIN #1 IDENT 0.50 5±0.05 2.50±0.05 13 -0.25±0.05 0.50 (14X) 0.10M C A B 2.00 Φ 0.05(M) C **BOTTOM VIEW**

#### NOTES:

- A. CONFORMS TO JEDEC REGISTRATION MO-241, VARIATION AA

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009.

- D. LAND PATTERN RECOMMENDATION IS EXISTING INDUSTRY LAND PATTERN.

| DOCUMENT NUMBER: | 98AON13643G         | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | QFN14 3.0X2.5, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

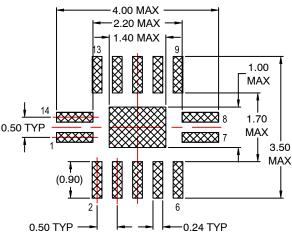

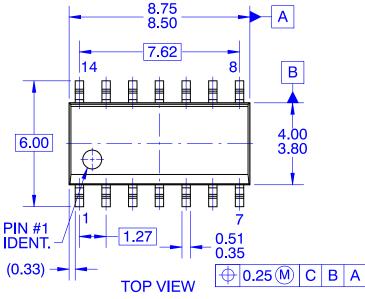

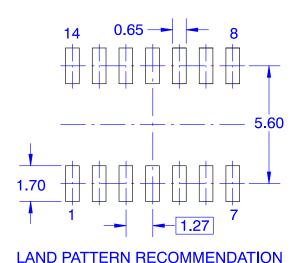

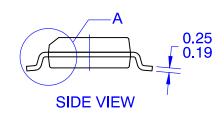

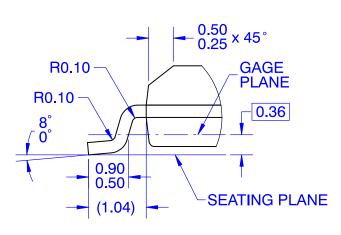

SOIC14 CASE 751EF ISSUE O

**DATE 30 SEP 2016**

1.75 MAX 0.10 1.50 0.25 0.10 **FRONT VIEW**

#### **NOTES:**

- A. CONFORMS TO JEDEC MS-012, VARIATION AB, ISSUE C

B. ALL DIMENSIONS ARE IN MILLIMETERS

- C. DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS

- LAND PATTERN STANDARD: SOIC127P600X145-14M

- E. CONFORMS TO ASME Y14.5M, 2009

DETAIL A SCALE 16:1

| DOCUMENT NUMBER: | 98AON13739G | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC14      |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**DATE 17 FEB 2016**

- NOTES.

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD

- FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

DIMENSION B DOES NOT INCLUDE

- INTERLEAD FLASH OR PROTRUSION.

INTERLEAD FLASH OR PROTRUSION SHALL

- INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. TERMINAL NUMBERS ARE SHOWN FOR DEFERENCE ONLY

- REFERENCE ONLY.

DIMENSION A AND B ARE TO BE

- DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.90        | 5.10 | 0.193     | 0.200 |

| В   | 4.30        | 4.50 | 0.169     | 0.177 |

| С   |             | 1.20 |           | 0.047 |

| D   | 0.05        | 0.15 | 0.002     | 0.006 |

| F   | 0.50        | 0.75 | 0.020     | 0.030 |

| G   | 0.65 BSC    |      | 0.026 BSC |       |

| Н   | 0.50        | 0.60 | 0.020     | 0.024 |

| J   | 0.09        | 0.20 | 0.004     | 0.008 |

| J1  | 0.09        | 0.16 | 0.004     | 0.006 |

| K   | 0.19        | 0.30 | 0.007     | 0.012 |

| K1  | 0.19        | 0.25 | 0.007     | 0.010 |

| L   | 6.40        | BSC  | 0.252     | BSC   |

| М   | o °         | 8 °  | o °       | a °   |

#### **GENERIC MARKING DIAGRAM\***

= Assembly Location

= Wafer Lot V - Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location) \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASH70246A | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSSOP-14 WB |                                                                                                                                                                                     | PAGE 1 OF 1 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.org/www.onsemi.or

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales