# O Hz/DC to 13 GHz, 2.5 kV HBM ESD, **SP4T, MEMS Switch with Integrated Driver**

**ADGM1004 Data Sheet**

#### **FEATURES**

Fully operational down to 0 Hz/dc On resistance: 2.9 Ω (maximum) Off leakage: 0.5 nA (maximum)

-3 dB bandwidth

10.8 GHz (typical) for RF1, RF4 13 GHz (typical) for RF2, RF3 RF performance characteristics

Insertion loss: 0.45 dB (typical) at 2.5 GHz Isolation: 24 dB (typical) at 2.5 GHz

IP3: 67 dBm (typical)

RF input power: 32 dBm (maximum) Actuation lifetime: 1 billion cycles (minimum) Hermetically sealed switch contacts On switching time: 75 µs (maximum)

**ESD HBM rating**

5 kV for RF1 to RF4 and RFC pins

2.5 kV for all other pins

Integrated driver removes the need for an external driver

Supply voltage: 3.0 V to 3.6 V CMOS/LVTTL compatible Parallel and SPI Interface

Independently controllable switches

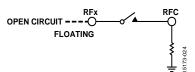

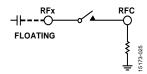

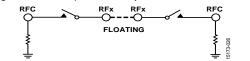

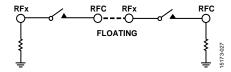

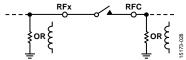

Switch is in an open state with no power supply present Requirement to avoid floating nodes on all RFx pins (see the Floating Node section)

5 mm × 4 mm × 1.45 mm, 24-lead LFCSP Operating temperature range: 0°C to +85°C

#### **APPLICATIONS**

**Relay replacements**

Automatic test equipment (ATE): RF, digital, and mixed signals Load and probe boards: RF, digital, and mixed signals

RF test instrumentation

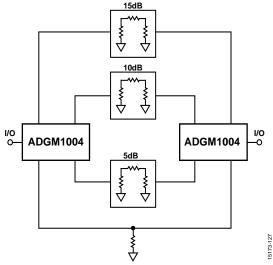

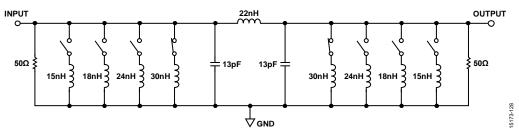

**Reconfigurable filters and attenuators High performance RF switching**

#### **COMPANION PRODUCTS**

Quad PMU: AD5522

SP4T MEMS Switch: ADGM1304

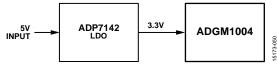

Low Noise, LDO: ADP7142, LT1962, LT3045-1

#### **GENERAL DESCRIPTION**

The ADGM1004 is a wideband, single-pole, four-throw (SP4T) switch fabricated using Analog Devices, Inc., microelectromechanical system (MEMS) switch technology. This technology enables a small form factor, wide RF bandwidth, highly linear, low insertion loss switch that is operational from 0 Hz/dc to 13 GHz, making it an ideal solution for a wide range of RF and precision equipment switching needs.

An integrated driver chip generates a high voltage to electrostatically actuate switch that can be controlled by a parallel interface and a serial peripheral interface (SPI). All four switches are independently controllable.

The device is packaged in a 24-lead,  $5 \text{ mm} \times 4 \text{ mm} \times 1.45 \text{ mm}$ , lead frame chip-scale package (LFCSP).

To ensure optimum operation of the ADGM1004, follow the Critical Operational Requirements section exactly.

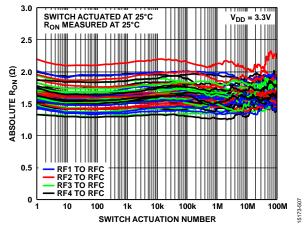

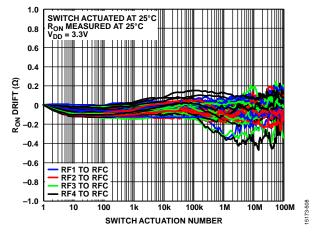

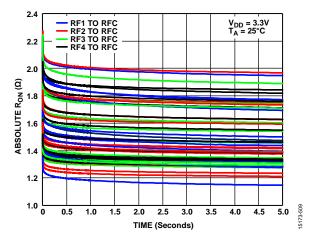

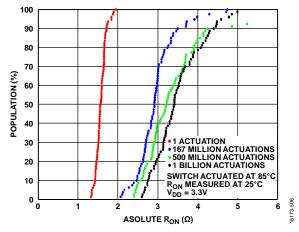

The on resistance ( $R_{\text{ON}}$ ) performance of the ADGM1004 is affected by part to part variation, channel to channel variation, cycle actuations, settling time post turn on, bias voltage, and temperature changes.

Note that throughout this data sheet, multifunction pins, such as IN1/SDI, are referred to either by the entire pin name or by a single function of the pin, for example, SDI, when only that function is relevant.

# **TABLE OF CONTENTS**

| Features1                                                   | Low Power Mode                                            |

|-------------------------------------------------------------|-----------------------------------------------------------|

| Applications 1                                              | Typical Operating Circuit                                 |

| Companion Products1                                         | Applications Information                                  |

| General Description1                                        | Power Supply Rails                                        |

| Revision History2                                           | Power Supply Recommendations                              |

| Functional Block Diagram4                                   | Switchable RF Attenuator                                  |

| Specifications                                              | Reconfigurable RF Filter                                  |

| Timing Characteristics                                      | Critical Operational Requirements                         |

| Absolute Maximum Ratings                                    | System Error Considerations Due to On-Resistance Drift 2  |

| Thermal Resistance                                          | On Resistance Shift Due to Temperature Shock Post         |

| ESD Caution                                                 | Actuations                                                |

|                                                             | Floating Node                                             |

| Pin Configuration and Function Descriptions                 | Cumulative On Switch Lifetime                             |

| Typical Performance Characteristics                         | Handling Precautions                                      |

| Test Circuits                                               |                                                           |

| Terminology20                                               | Register Details                                          |

| Theory of Operation22                                       | Switch Data Register                                      |

| Parallel Digital Interface22                                | Outline Dimensions                                        |

| SPI Digital Interface23                                     | Ordering Guide                                            |

| Internal Oscillator Feedthrough25                           |                                                           |

| Internal Oscillator Feedthrough Mitigation25                |                                                           |

| REVISION HISTORY                                            |                                                           |

| 11/2020—Rev. D to Rev. E                                    | Added Timing Diagrams Section, Figure 2, Figure 3, and    |

| Added Companions Products Section                           | Figure 4; Renumbered Sequentially                         |

| Added Endnote 3, Table 1; Renumbered Sequentially 5         | Changes to Absolute Maximum Rating Section                |

| Changes to Figure 11                                        | and Table 3                                               |

| Changes to Figure 4319                                      | Changes to Figure 5 and Table 5                           |

| Changes to Addressable Mode Section and Figure 45 Caption23 | Changes to Typical Performance Characteristics Section    |

| Added Figure 46; Renumbered Sequentially23                  | Changes to Terminology Section                            |

| Changes to Typical Operating Circuit Section26              | Changes to Parallel Digital Interface Section and         |

| Added Power Supply Rails Section, Power Supply              | Table 6 Title                                             |

| Recommendations Section, Figure 51, and Table 7;            |                                                           |

| Renumbered Sequentially27                                   | Added SPI Digital Interface Section, Addressable Mode     |

| Changes to System Error Considerations Due to On Resistance | Section, and Figure 45                                    |

| Drift Section                                               | Added Daisy-Chain Mode Section, Figure 46, Figure 47, and |

| Added On Resistance Shift Due to Temperature Shock Post     | Figure 48                                                 |

| Actuations Section                                          | Added Hardware Reset Section and Internal Error Status    |

| Moved Figure 6; Renumbered Sequentially29                   | Section                                                   |

| 27                                                          | Changes to Internal Oscillator Feedthrough Section and    |

| 11/2019—Rev. C to Rev. D                                    | Internal Oscillator Feedthrough Mitigation Section        |

| Change to Features Section and General                      | Changes to Typical Operating Circuit Section and          |

| Applications Section                                        | Figure 49                                                 |

| Moved Functional Block Diagram Section                      | Deleted Handling Guidelines Section, DC Voltage Range     |

| Changes to Figure 1                                         | Section, and Voltage Standoff Limit Section               |

| Changes to Figure 1                                         | Added Critical Operational Requirements Section, System   |

| Added Timing Characteristics Section and Table 2;           | Error Considerations Due to On-Resistance Drift Section,  |

| Renumbered Sequentially 7                                   |                                                           |

| Figure 52, Table 7, Floating Node Section, Figure 53, Figure | e 54, |

|--------------------------------------------------------------|-------|

| Figure 55, Figure 56, and Figure 57                          | 28    |

| Added Figure 58, Figure 59, Cumulative On Switch Lifetim     |       |

| Section, Handling Precautions Section, and Figure 61         | 29    |

| Moved Figure 60 and Electrical Overstress (EOS)              |       |

| Precautions Section                                          | 29    |

| Added Mechanical Shock Precautions Section and Table 8.      | 30    |

| Changes to Figure 62                                         | 30    |

| Added Register Details Section, Switch Data Register Section | n,    |

| and Table 9                                                  | 31    |

| Change to Ordering Guide                                     | 32    |

|                                                              |       |

| 3/2019—Rev. B to Rev. C                                      |       |

| Change to Features Section and Figure 1                      |       |

| Changes to Specifications Section and Table 1                | 3     |

| Deleted Endnote 1, Endnote 3, and Endnote 6 in Table 1;      |       |

| Renumbered Sequentially                                      | 4     |

| Changes to Table 2                                           | 5     |

| Changes to Table 4                                           | 6     |

| Updated Typical Performance Characteristics Section          |       |

| Format                                                       | 7     |

| Changes to Figure 6 to Figure 8 Captions                     | 7     |

| Added Figure 9 to Figure 12; Renumbered Sequentially         | 8     |

| Deleted Figure 15                                            | 9     |

| Added Figure 19 and Figure 20                                | 9     |

| Added Figure 24 to Figure 26                                 | 10    |

| Added Figure 27 to Figure 30                                 | 11    |

| Changes to Figure 32 Caption                                 | 12    |

| Added Figure 33                                              | 12    |

| Deleted Figure 27 to Figure 29                               | 12    |

| Changes to Figure 35                                         | 13    |

| Changes to Figure 37 Caption                                 | 13    |

| Added Figure 39, Figure 40, and Figure 42                 | 14 |

|-----------------------------------------------------------|----|

| Changes to Terminology Section                            | 15 |

| Changes to Theory of Operation Section                    | 17 |

| Changed Internal Oscillator/EXTD_EN Section to Internal   |    |

| Oscillator Section                                        | 18 |

| Changes to Internal Oscillator Section, Typical Operating |    |

| Circuit Section                                           | 18 |

| Replaced Figure 44                                        | 18 |

| Added Oscillator Feedthrough Mitigation Section and Low   |    |

| Power Mode Section                                        | 18 |

| Changes to Figure 50 and Figure 51                        | 19 |

| Added Voltage Standoff Limit Section                      | 22 |

|                                                           |    |

| 3/2018—Rev. A to Rev. B                                   |    |

| Changes to Features Section                               | 1  |

| Changes to Table 1                                        | 3  |

| Added Endnote 5 to Table 1; Renumbered Sequentially       | 3  |

| Changes to Table 2                                        | 5  |

| Added Figure 27, Figure 28, and Figure 29; Renumbered     |    |

| Sequentially                                              | 12 |

| Changes to Floating Node Avoidance Section and Figure 36  | 17 |

| Updated Outline Dimensions                                | 21 |

|                                                           |    |

| 2/2017—Rev. 0 to Rev. A                                   |    |

| Changes to Features Section                               | 1  |

| Changes to On Resistance Parameter, Table 1               |    |

| Change to Table 2                                         | 5  |

| Changes to Figure 13 and Figure 14                        | 8  |

| Updated Outline Dimensions                                | 20 |

1/2017—Revision 0: Initial Version

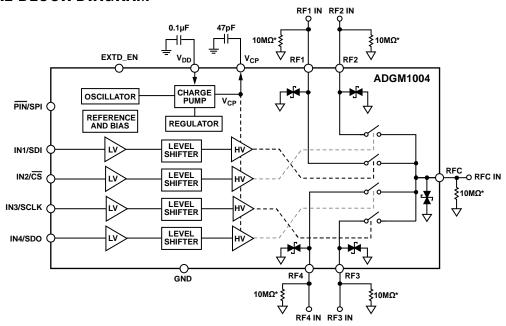

# **FUNCTIONAL BLOCK DIAGRAM**

\*10M $\Omega$  RESISTORS ARE REQUIRED TO AVOID ANY FLOATING NODES. FOR MORE INFORMATION, REFER TO THE CRITICAL OPERATIONAL REQUIREMENTS SECTION NOTES 1. LV = LOW VOLTAGE. HV = HIGH VOLTAGE.

Figure 1.

# **SPECIFICATIONS**

Supply voltage  $(V_{DD}) = 3.0 \text{ V}$  to 3.6 V, GND = 0 V, and all specifications at  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted. Typical specifications tested at  $T_A = 25^{\circ}\text{C}$  with  $V_{DD} = 3.3 \text{ V}$ .

Table 1.

| Parameter                                 | Symbol                | Min             | Тур                    | Max   | Unit       | Test Conditions/Comments <sup>1</sup>                                                                                                                                 |

|-------------------------------------------|-----------------------|-----------------|------------------------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON-RESISTANCE PROPERTIES                  |                       |                 |                        |       |            | See Figure 54 to Figure 12 for more details                                                                                                                           |

| Initial On-Resistance<br>Properties       |                       |                 |                        |       |            |                                                                                                                                                                       |

| On Resistance                             | Ron                   |                 |                        | 2.9   | Ω          | Drain source current (I <sub>Ds</sub> ) = 50 mA, 0 V input bias, at 1 ms after first actuation, maximum specification from 0°C to 85°C                                |

| On-Resistance Match<br>Between Channels   | $\Delta R$ on ch_ch   |                 |                        | 1     | Ω          | Maximum value tested from 0°C to 85°C                                                                                                                                 |

| On-Resistance Drift                       |                       |                 |                        |       |            |                                                                                                                                                                       |

| Over Time <sup>2, 3</sup>                 | ΔR <sub>ON</sub> TIME |                 |                        | -0.25 | Ω          | R <sub>ON</sub> changed from 1 ms to 100 ms after first actuation, maximum value tested from 0°C to 85°C                                                              |

| Over Actuations <sup>4</sup>              | $\Delta R_{ON}$       |                 | 0.5                    |       | Ω          | $10^9$ actuations, switch is actuated at 25°C and $R_{\text{ON}}$ is measured at 25°C                                                                                 |

|                                           |                       |                 |                        | 5     | Ω          | 10° actuations, switch is actuated at 85°C and R <sub>ON</sub> is<br>measured at 25°C, 1 kHz actuating frequency,<br>220 mA load applied between toggles <sup>5</sup> |

| RELIABILITY PROPERTIES                    |                       |                 |                        |       |            |                                                                                                                                                                       |

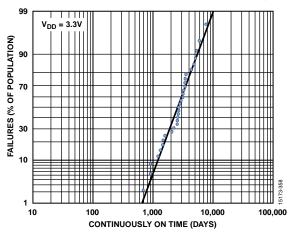

| Continuously On Lifetime                  |                       |                 | 7.2                    |       | Years      | Median time before failure at 50°C <sup>6</sup> , see Figure 60 for more details                                                                                      |

| Actuation Lifetime                        |                       |                 |                        |       |            |                                                                                                                                                                       |

| Cold Switched                             |                       | 10 <sup>9</sup> |                        |       | Actuations | Load between toggling is 220 mA, tested at 85°C                                                                                                                       |

| Hot Switched                              |                       |                 |                        |       |            | RF power = continuous wave (CW), terminated into $50 \Omega$ , see Figure 13 for details                                                                              |

| 10 dBm                                    |                       |                 | 5.16 × 10 <sup>9</sup> |       | Actuations | 50% of test population failure point (T50)                                                                                                                            |

| 15 dBm                                    |                       |                 | 3.21 × 10 <sup>6</sup> |       | Actuations | 50% of test population failure point (T50)                                                                                                                            |

| 20 dBm                                    |                       |                 | 390 × 10 <sup>3</sup>  |       | Actuations | 50% of test population failure point (T50)                                                                                                                            |

| DYNAMIC CHARACTERISTICS                   |                       |                 |                        |       |            |                                                                                                                                                                       |

| Operating Frequency                       |                       | 0/dc            |                        | 13    | GHz        |                                                                                                                                                                       |

| –3 dB Bandwidth                           | BW                    |                 |                        |       |            |                                                                                                                                                                       |

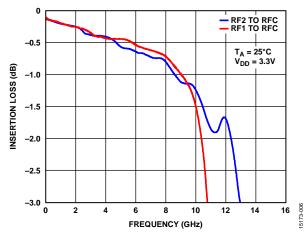

| RF1, RF4                                  |                       | 9.5             | 10.8                   |       | GHz        | RF1 to RFC and RF4 to RFC channels                                                                                                                                    |

| RF2, RF3                                  |                       | 11.5            | 13                     |       | GHz        | RF2 to RFC and RF3 to RFC channels                                                                                                                                    |

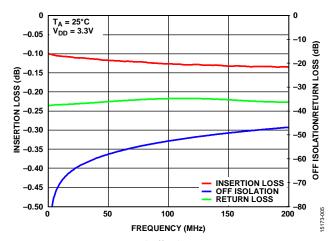

| Insertion Loss                            | IL                    |                 | 0.45                   | 0.6   | dB         | At 2.5 GHz, RFC to RFx                                                                                                                                                |

|                                           |                       |                 | 0.63                   | 0.95  | dB         | At 6.0 GHz, RFC to RFx                                                                                                                                                |

| Isolation                                 |                       |                 |                        |       |            |                                                                                                                                                                       |

| RFx to RFC                                |                       | 22              | 24                     |       | dB         | At 2.5 GHz, RFx to RFC (all channels off)                                                                                                                             |

|                                           |                       | 16              | 19                     |       | dB         | At 6.0 GHz, RFx to RFC (all channels off)                                                                                                                             |

| RF1 to RFC                                |                       |                 | 27                     |       |            | At 6 GHz, RF2 to RFC is on, RF1 to RFC is off                                                                                                                         |

| RF2 to RFC                                |                       |                 | 26                     |       |            | At 6 GHz, RF1 to RFC is on, RF2 to RFC is off                                                                                                                         |

| Crosstalk                                 |                       | 27              | 30                     |       | dB         | At 2.5 GHz, RFx to RFx                                                                                                                                                |

|                                           |                       | 22              | 24                     |       | dB         | At 6.0 GHz, RFx to RFx                                                                                                                                                |

| Return Loss                               | RL                    | 14              | 17                     |       | dB         | DC to 6.0 GHz                                                                                                                                                         |

| Third-Order Intermodulation<br>Intercept  | IP3                   |                 | 67                     |       | dBm        | Input: 900 MHz and 901 MHz, input power = 27 dBm                                                                                                                      |

| Second-Order Intermodulation<br>Intercept | IP2                   |                 | 95                     |       | dBm        | Input: 900 MHz and 901 MHz, input power = 27 dBm                                                                                                                      |

| Second Harmonic Distortion                | HD2                   |                 | -90                    |       | dBc        | Input: 5.4 MHz, input power = 0 dBm                                                                                                                                   |

|                                           |                       |                 | -74                    |       | dBc        | Input: 150 MHz and 800 MHz, input power = 27 dBm                                                                                                                      |

| Parameter                                       | Symbol                              | Min                   | Тур   | Max  | Unit             | Test Conditions/Comments <sup>1</sup>                                                                                                                   |

|-------------------------------------------------|-------------------------------------|-----------------------|-------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Third Harmonic Distortion                       | HD3                                 |                       | -80   |      | dBc              | Input: 150 MHz and 800 MHz, input power = 27 dBm                                                                                                        |

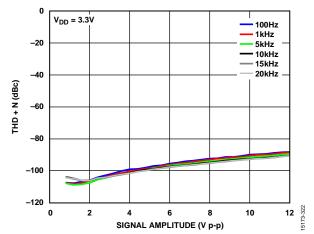

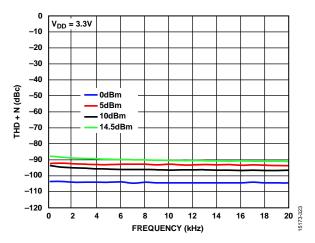

| Total Harmonic Distortion plus Noise            | THD + N                             |                       | -102  |      | dBc              | Load resistance (R <sub>L</sub> ) = 300 $\Omega$ , f = 1 kHz, RFx = 2.5 V p-p                                                                           |

| RF Input Power                                  |                                     |                       |       | 32   | dBm              | Switch in the on state and terminated into 50 $\Omega$ , maximum specification tested at 25°C                                                           |

| DC Voltage Range                                |                                     | -6                    |       | +6   | V                | On switch dc voltage operation range, 0°C to 85°C                                                                                                       |

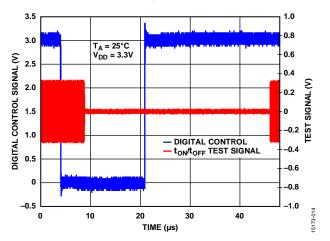

| On Switching Time <sup>7</sup>                  | ton                                 | 0                     |       | 75   | μs               | 50% INx to 90% (0.05 dB of final IL value) RFx, 50 $\Omega$ termination, 0°C to 85°C                                                                    |

| Off Switching Time <sup>7</sup>                 | toff                                | 0                     |       | 75   | μs               | 50% INx to 10% (0.05 dB of final IL value) RFx, 50 $\Omega$ termination, 0°C to 85°C                                                                    |

| Actuation Frequency                             |                                     |                       |       | 5    | kHz              | All switches toggled simultaneously, 0°C to 85°C                                                                                                        |

| Power-Up Time                                   |                                     |                       | 0.75  |      | ms               | $C_{CP} = 47 \text{ pF}, 95\% \text{ V}_{DD} \text{ to } 90\% \text{ RFx}, 0^{\circ}\text{C to } 85^{\circ}\text{C}$                                    |

| Video Feedthrough                               |                                     |                       | 16    |      | mV peak          | 1 MΩ termination at RFx pin                                                                                                                             |

| Internal Oscillator Frequency                   |                                     | 8                     | 10    | 12   | MHz              | 0°C to 85°C                                                                                                                                             |

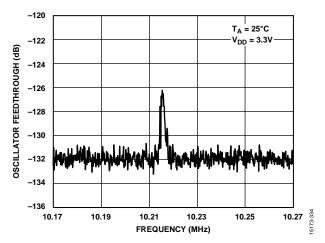

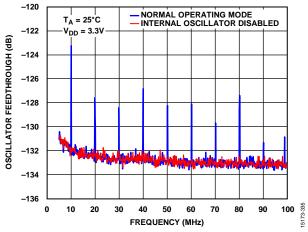

| Internal Oscillator<br>Feedthrough <sup>8</sup> |                                     |                       | -123  |      | dBm              | Spectrum analyzer resolution bandwidth ( $R_{BW}$ ) = 200 Hz, one switch in on state, all other switches off with 50 $\Omega$ terminations <sup>9</sup> |

|                                                 |                                     |                       | -146  |      | dBm/Hz           | on with 50 12 terminations.                                                                                                                             |

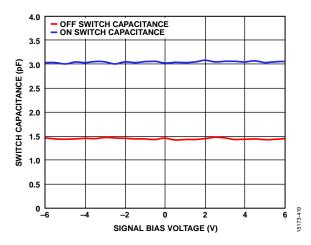

| CAPACITANCE PROPERTIES                          |                                     | -                     | -140  |      | UBITI/FIZ        | At 1 Mile in deal CCCD and be as a second to the                                                                                                        |

| On Switch Channel Capacitance                   | C <sub>RF ON</sub>                  |                       | 3     |      | pF               | At 1 MHz, includes LFCSP package capacitance                                                                                                            |

| Off Switch Channel Capacitance                  | C <sub>RF</sub> OFF                 |                       | 1.5   |      | pF               |                                                                                                                                                         |

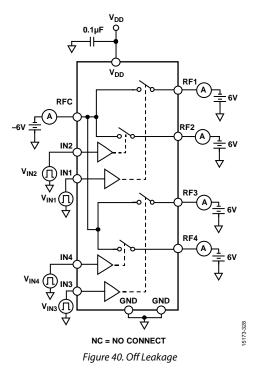

| LEAKAGE PROPERTIES                              |                                     |                       |       |      |                  | Maximum specification from 0°C to 85°C                                                                                                                  |

| On Leakage                                      |                                     |                       |       | 5    | nA               | RFx (off channels) = $-6$ V, RFC to RFx (on channel) = $-6$ V                                                                                           |

| Off Leakage                                     |                                     |                       |       | 0.5  | nA               | RFx = 6  V, RFC = -6  V                                                                                                                                 |

| DIGITAL INPUTS                                  |                                     |                       |       |      |                  | Minimum and maximum over 0°C to 85°C                                                                                                                    |

| Input High Voltage                              | V <sub>INH</sub>                    | 2                     |       |      | V                |                                                                                                                                                         |

| Input Low Voltage                               | V <sub>INL</sub>                    |                       |       | 0.8  | V                |                                                                                                                                                         |

| Input Current                                   | I <sub>INL</sub> , I <sub>INH</sub> |                       | 0.025 | 1    | μA               | Input voltage $(V_{IN}) = V_{INL}$ or $V_{INH}$                                                                                                         |

| DIGITAL OUTPUTS                                 |                                     |                       |       |      | '                | Minimum and maximum over 0°C to 85°C                                                                                                                    |

| Output Low Voltage                              | VoL                                 |                       |       | 0.4  | V <sub>MAX</sub> | Sink current (I <sub>SINK</sub> ) = 1 mA                                                                                                                |

| Output High Voltage                             | Voh                                 | V <sub>DD</sub> - 0.4 |       |      | V <sub>MIN</sub> | Source current (I <sub>SOURCE</sub> ) = 1 mA                                                                                                            |

| POWER REQUIREMENTS                              |                                     |                       |       |      |                  | Minimum and maximum over 0°C to 85°C                                                                                                                    |

| Supply Voltage                                  | $V_{DD}$                            | 3.0                   |       | 3.6  | V                |                                                                                                                                                         |

| Supply Current                                  | I <sub>DD</sub>                     |                       |       | 2.5  | mA               | Digital inputs = 0 V or $V_{DD}$ , SDO is floating in SPI mode                                                                                          |

| Low Power Mode Current <sup>10</sup>            | I <sub>DD EXT VCP</sub>             |                       |       | 50   | μΑ               | This value is IDD in low power mode                                                                                                                     |

| External Drive Voltage <sup>11</sup>            | VCP <sub>EXT</sub>                  | 79.2                  | 80    | 80.8 | V                | pone                                                                                                                                                    |

| External Drive Current                          | I <sub>CP EXT VCP</sub>             |                       |       | 20   | μΑ               |                                                                                                                                                         |

$<sup>^{\</sup>rm 1}$  RFx is RF1, RF2, RF3, and RF4. INx is IN1, IN2, IN3, and IN4.

$<sup>^2</sup>$  Maximum  $R_{ON}$  over time is  $R_{ON}$  (max) +  $\Delta R_{ON\,TIME}$  (max) = 2.65  $\Omega.$

$<sup>^3</sup>$  Typically, the on-resistance over time drifts by  $-0.05\,\Omega$  per decade.

<sup>&</sup>lt;sup>4</sup> Maximum R<sub>ON</sub> after 1 billion actuations is R<sub>ON</sub> (max) +  $\Delta$ R<sub>ON</sub> (max) = 7.9  $\Omega$ .

S Actuating the switch at 85°C and measuring R<sub>ON</sub> at 25°C is the most severe condition for ADGM1004 R<sub>ON</sub> drift over actuations.

Failure occurs when 50% of a sample lot fails. For more details, see the Cumulative On Switch Lifetime section.

Switch is settled after 75 μs. Do not apply RF power between 0 μs and 75 μs.

<sup>&</sup>lt;sup>8</sup> Disable the internal oscillator to eliminate feedthrough. When the internal oscillator and charge pump circuitry is disabled, the V<sub>CP</sub> pin (Pin 24) must be driven with 80 V dc (VCP<sub>EXT</sub>) from an external voltage supply required for MEMS switch actuation, as outlined in Table 3.

The spectrum analyzer setup is as follows:  $R_{BW} = 200$  Hz, video bandwidth ( $V_{BW}$ ) = 2 Hz, span = 100 kHz, input attenuator = 0 dB, the detector type is peak, and the maximum hold is off. The fundamental feedthrough noise or harmonic (whichever is higher) is tested.

<sup>&</sup>lt;sup>10</sup> For more details, see the Low Power Mode section.

<sup>&</sup>lt;sup>11</sup> For more details, see the Internal Oscillator Feedthrough Mitigation section.

#### **TIMING CHARACTERISTICS**

$V_{DD}$  = 3.0 V to 3.6 V, GND = 0 V, and all specifications  $T_{MIN}$  to  $T_{MAX}$  = 0°C to +85°C, unless otherwise noted.

Table 2.

| Parameter             | Description                                     | Limit at T <sub>MIN</sub> | Limit at T <sub>MAX</sub> | Unit |

|-----------------------|-------------------------------------------------|---------------------------|---------------------------|------|

| t <sub>1</sub>        | SCLK period                                     | 100                       |                           | ns   |

| $t_2$                 | SCLK high pulse width                           | 45                        |                           | ns   |

| t <sub>3</sub>        | SCLK low pulse width                            | 45                        |                           | ns   |

| <b>t</b> 4            | CS falling edge to SCLK active edge             | 25                        |                           | ns   |

| <b>t</b> <sub>5</sub> | Data setup time                                 | 20                        |                           | ns   |

| t <sub>6</sub>        | Data hold time                                  | 20                        |                           | ns   |

| t <sub>7</sub>        | SCLK active edge to CS rising edge              | 25                        |                           | ns   |

| t <sub>8</sub>        | CS falling edge to SDO data available           |                           | 20                        | ns   |

| $t_9$ <sup>1</sup>    | SCLK falling edge to SDO data available         |                           | 40                        | ns   |

| t <sub>10</sub>       | CS rising edge to SDO returns to high impedance |                           | 25                        | ns   |

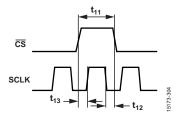

| t <sub>11</sub>       | CS high time between SPI commands               | 100                       |                           | ns   |

| t <sub>12</sub>       | SCLK edge rejection to CS falling edge          | 25                        |                           | ns   |

| t <sub>13</sub>       | CS rising edge to SCLK edge rejection           | 25                        |                           | ns   |

$<sup>^{1}</sup>$  Measured with a 20 pF load, to determines the maximum SCLK frequency when the SDO pin is used.

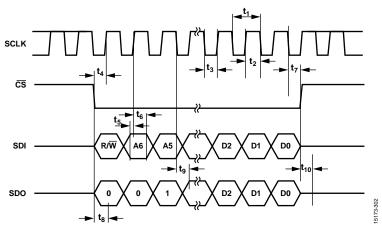

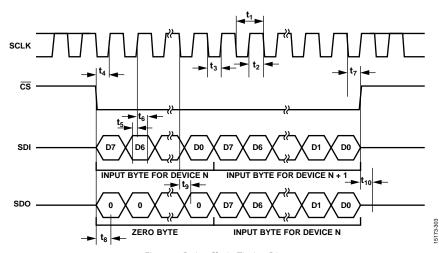

#### **Timing Diagrams**

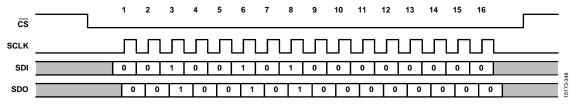

Figure 2. Addressable Mode Timing Diagram

Figure 3. Daisy-Chain Timing Diagram

Figure 4. SCLK/CS Timing Relationship

#### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Table 3.                                             |                                               |  |

|------------------------------------------------------|-----------------------------------------------|--|

| Parameter                                            | Rating                                        |  |

| V <sub>DD</sub> to GND                               | −0.3 V to +6 V                                |  |

| Digital Inputs <sup>1</sup>                          | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V or}$ |  |

|                                                      | +30 mA (whichever occurs                      |  |

|                                                      | first)                                        |  |

| DC Voltage Rating <sup>2</sup>                       | ±7 V                                          |  |

| Standoff Voltage <sup>3</sup>                        | 20 V                                          |  |

| RFx to AGND                                          | ±10 V                                         |  |

| RFC to AGND                                          | ±10 V                                         |  |

| RFx to RFC                                           | 20 V                                          |  |

| Current Rating <sup>2</sup>                          | 250 mA                                        |  |

| RF Power Rating <sup>4</sup>                         | 33 dBm                                        |  |

| Temperature                                          |                                               |  |

| Operating Range                                      | 0°C to +85°C                                  |  |

| Storage Range                                        | −65°C to +150°C                               |  |

| Reflow Soldering (Pb-Free)                           |                                               |  |

| Peak                                                 | 260 (+0/-5)°C                                 |  |

| Time at Peak                                         | 10 sec to 30 sec                              |  |

| Electrostatic Discharge (ESD)                        |                                               |  |

| Human Body Model (HBM)                               |                                               |  |

| RF1 to RF4 and RFC                                   | 5 kV                                          |  |

| All Other Pins                                       | 2.5 kV                                        |  |

| Field Induced Charged Device<br>Model <sup>5</sup>   |                                               |  |

| All Pins                                             | 1.25 kV                                       |  |

| Group D                                              |                                               |  |

| Mechanical Shock (with 0.5 ms<br>Pulse) <sup>6</sup> | 1500 <i>g</i>                                 |  |

| Vibration (Acceleration at 50 g)                     | 20 Hz to 2000 Hz                              |  |

| Constant Acceleration                                | 30,000 <i>g</i>                               |  |

|                                                      |                                               |  |

<sup>&</sup>lt;sup>1</sup> Clamp overvoltages at INx by internal diodes. Limit the current to the maximum ratings given.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

**Table 4. Thermal Resistance**

| Package Type         | θ <sub>JA</sub> | θις | Unit |

|----------------------|-----------------|-----|------|

| CP-24-4 <sup>1</sup> | 60              | 75  | °C/W |

$<sup>^1</sup>$  A simulated  $\theta_{JA}$  number is evaluated using the maximum junction temperature in the package and the total power being dissipated in the package under operating conditions. For thermal performance calculation purposes at 25°C, a power dissipation of 113 mW per switch can be used. This value is calculated from a typical  $R_{\text{ON}}$  of 1.8  $\Omega$  and an absolute maximum current rating of 250 mA.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> This rating is with respect to the switch in the on position with no radio frequency signal applied.

<sup>&</sup>lt;sup>3</sup> This rating is with respect to the switch in the off position.

$<sup>^4</sup>$  This rating is with respect to the switch in the on position and terminated into 50  $\Omega$ . The rating is 27 dBm when the switch is unterminated.

<sup>&</sup>lt;sup>5</sup> A safe automated handling and assembly process is achieved at this rating level by implementing industry standard ESD controls.

<sup>&</sup>lt;sup>6</sup> If the device is dropped during handling, do not use the device.

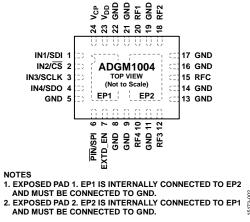

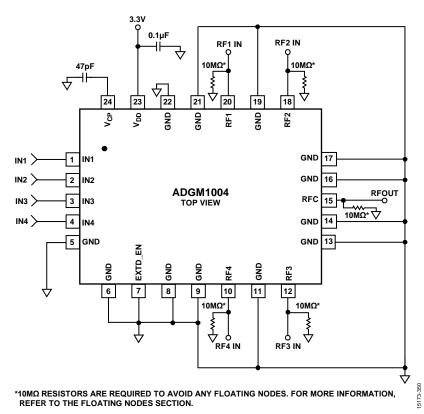

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.                                       | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                             | IN1/SDI  | Parallel Logic Digital Control Input 1. The voltage applied to this pin controls the gate of the RF1 to RFC MEMS switch. In SPI mode, this pin is the serial data input pin. In parallel mode, if the IN1 pin is low, the RF1 to RFC switch is open (off). If the IN1 pin is high, the RF1 to RFC switch is closed (on). In SPI mode, this pin functions as the serial data input (SDI) pin.                                                                                                                                                                                                                                                                    |

| 2                                             | IN2/CS   | Parallel Logic Digital Control Input 2. The voltage applied to this pin controls the gate of the RF2 to RFC MEMS switch. In parallel mode, if IN2 is low, the RF2 to RFC switch is open (off). If IN2 is high, the RF2 to RFC switch is closed (on). In SPI mode, this pin is the chip select (CS) pin. CS is an active low signal that selects the slave device with which the master device intends to communicate. Typically, there is a dedicated CS signal between the master device and each slave device. The CS pin also functions to synchronize and frame the communications to and from the slave device.                                            |

| 3                                             | IN3/SCLK | Parallel Logic Digital Control Input 3. The voltage applied to this pin controls the gate of the RF3 to RFC MEMS switch. In parallel mode, if IN3 is low, the RF3 to RFC switch is open (off). If IN3 is high, the RF3 to RFC switch is closed (on). In SPI mode, this pin functions as the serial clock (SCLK) pin that synchronizes the slave device(s) to the master device. Typically, the SCLK signal is shared for all slave devices on the serial bus. The SCLK signal is always driven by the master device.                                                                                                                                            |

| 4                                             | IN4/SDO  | Parallel Logic Digital Control Input 4. The voltage applied to this pin controls the gate of the RF4 to RFC MEMS switch. In parallel mode, if IN4 is low, the RF4 to RFC switch is open (off). If IN4 is high, the RF4 to RFC switch is closed (on). In SPI mode, this pin functions as the serial data output (SDO) pin. Typically, the SDO pin is shared for all slave devices on the serial bus. The SDO pin is driven by only one slave device at a time, otherwise it is high impedance. The SDO pin is always high impedance when the $\overline{\text{CS}}$ pin is deasserted high.                                                                      |

| 5, 8, 9, 11, 13,<br>14, 16, 17,<br>19, 21, 22 | GND      | Ground Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                                             | PIN/SPI  | Parallel or Serial Logic Control Enable Pin. The SPI interface is enabled when this pin is high. When this pin is low the parallel digital interface is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7                                             | EXTD_EN  | External Voltage Drive Enable. In normal operation, set EXTD_EN low to enable the built in 10 MHz oscillator, which enables the internal driver IC voltage boost circuitry. Setting EXTD_EN high disables the internal 10 MHz oscillator and driver boost circuitry. With the oscillator disabled, the switch can still be controlled via the logic interface pins (IN1 to IN4) or via SPI interface, but the VcP pin must be driven with 80 V dc from an external voltage supply. In this mode, the ADGM1004 only consumes 50 µA maximum supply current. Disabling the internal oscillator eliminates the associated 10 MHz noise feedthrough from the switch. |

| 10                                            | RF4      | RF4 Port. This pin can be an input or an output. If unused, connect the pin to GND or terminate the pin with a 50 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12                                            | RF3      | RF3 Port. This pin can be an input or an output. If unused, connect the pin to GND or terminate the pin with a 50 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15                                            | RFC      | Common RF Port. This pin can be an input or an output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18                                            | RF2      | RF2 Port. This pin can be an input or an output. If unused, connect the pin to GND or terminate the pin with a 50 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20                                            | RF1      | RF1 Port. This pin can be an input or an output. If unused, connect the pin to GND or terminate the pin with a 50 $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin No. | Mnemonic | Description                                                                                                                                                                                                    |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23      | $V_{DD}$ | Positive Power Supply Input. The recommended decoupling capacitor to ground value is 0.1 $\mu$ F. For the recommended input voltage for this chip, see the Specifications section.                             |

| 24      | $V_{CP}$ | Charge Pump Capacitor Terminal. The recommended shunt capacitor to ground value is 47 pF (100 V rated). If the EXTD_EN pin is high, input an 80 V dc drive voltage into V <sub>CP</sub> to drive the switches. |

|         | EP1      | Exposed Pad 1. EP1 is internally connected to EP2 and must be connected to GND.                                                                                                                                |

|         | EP2      | Exposed Pad 2. EP2 is internally connected to EP1 and must be connected to GND.                                                                                                                                |

### TYPICAL PERFORMANCE CHARACTERISTICS

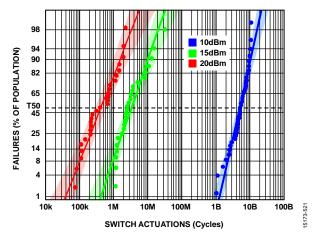

In Figure 13, T50 refers to the number of cycles required for 50% of the population to fail.

Figure 6. Absolute R<sub>ON</sub> vs. Switch Actuation Number, Switch Actuated at 25°C and R<sub>ON</sub> Measured at 25°C

Figure 7. R<sub>ON</sub> Drift vs. Switch Actuation Number, Normalized at Zero, Switch Actuated at 25°C and R<sub>ON</sub> Measured at 25°C

Figure 8. Absolute R<sub>ON</sub> vs. Time (1 ms to 5 sec) on Linear Scale

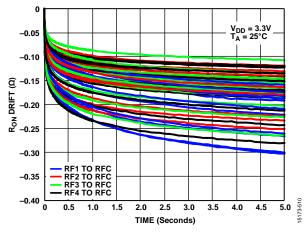

Figure 9.  $R_{\rm ON}$  Drift vs. Time (1 ms to 5 sec) on Linear Scale, Normalized at Zero

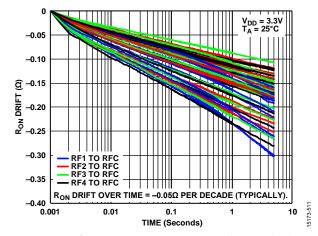

Figure 10.  $R_{ON}$  Drift vs. Time (1 ms to 5 sec) on Log Scale, Normalized at Zero

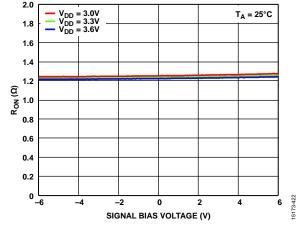

Figure 11. R<sub>ON</sub> vs. Signal Bias Voltage over Supply Voltages (Measured 5 sec Post Switch Turn On Time, RF1 to RFC on)

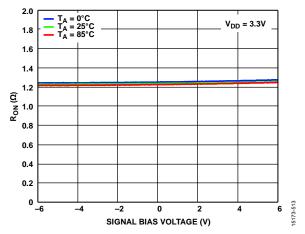

Figure 12. R<sub>ON</sub> vs. Signal Bias Voltage over Temperature (Measured 5 sec Post Switch Turn On Time, RF1 to RFC on)

Figure 13. Hot Switching Probability Distribution on Log Normal with 95% Confidence Interval (CI) (RF Power = CW, Terminated into 50  $\Omega$ ,  $T_A$  = 25°C,  $V_{DD}$  = 3.3 V)

Figure 14. Insertion Loss vs. Frequency, Linear Scale ( $V_{DD} = 3.3 V$ )

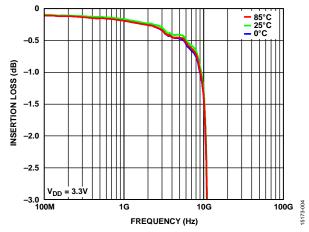

Figure 15. Insertion Loss vs. Frequency over Temperature ( $V_{DD} = 3.3 V$ , RF1 to RFC)

Figure 16. Insertion Loss and Off Isolation/Return Loss vs. Frequency  $(V_{DD} = 3.3 \text{ V}, RF1 \text{ to RFC})$

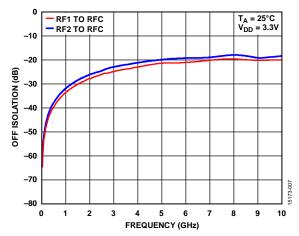

Figure 17. Off Isolation vs. Frequency, All Channels Off ( $V_{DD} = 3.3 \text{ V}$ )

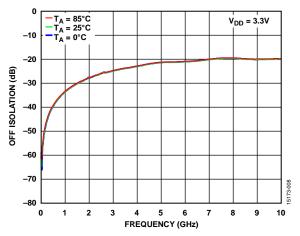

Figure 18. Off Isolation vs. Frequency over Temperature, All Channels Off  $(V_{DD} = 3.3 V, RF1 \text{ to } RFC)$

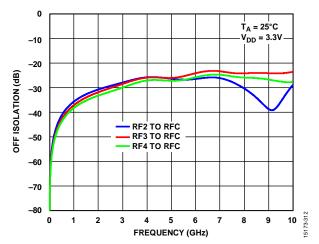

Figure 19. Off Isolation vs. Frequency, RF1 to RFC On  $(V_{DD} = 3.3 \text{ V})$

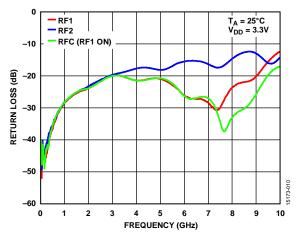

Figure 20. Return Loss vs. Frequency ( $V_{DD} = 3.3 \text{ V}$ )

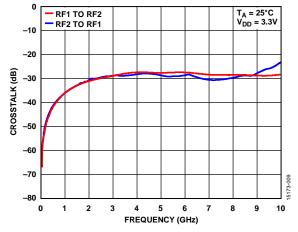

Figure 21. Crosstalk vs. Frequency ( $V_{DD} = 3.3 \text{ V}$ )

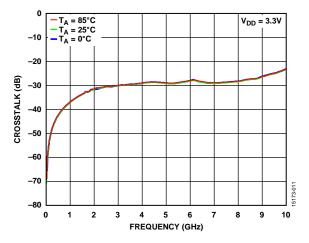

Figure 22. Crosstalk vs. Frequency over Temperature ( $V_{DD} = 3.3 \text{ V}$ , RF2 to RF1)

Figure 23. THD + N vs. Signal Amplitude ( $V_{DD}$  = 3.3 V,  $R_{LOAD}$  = 300  $\Omega$ ,  $T_A$  = 25 °C, Signal Source Impedance = 20  $\Omega$ )

Figure 24. THD + N vs. Frequency ( $V_{DD}$  = 3.3 V,  $R_{LOAD}$  = 300  $\Omega$ ,  $T_A$  = 25°C, Signal Source Impedance = 20  $\Omega$

Figure 25. Digital Control Signal and Test Signal vs. Time ( $V_{DD} = 3.3 V$ )

Figure 26. Switch Capacitance vs. Signal Bias Voltage

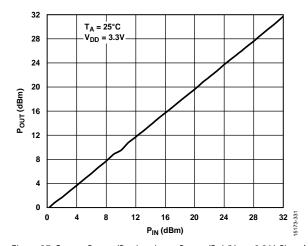

Figure 27. Output Power ( $P_{OUT}$ ) vs. Input Power ( $P_{IN}$ ) ( $V_{DD} = 3.3 \text{ V}$ , Signal Frequency = 4 GHz)

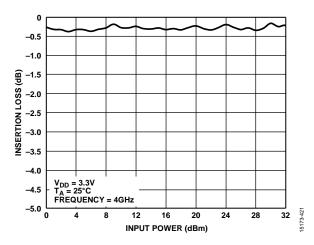

Figure 28. Insertion Loss vs. Input Power

Figure 29. Oscillator Feedthrough vs. Frequency, Zoomed in at 10.2 MHz  $(V_{DD}=3.3\ V)$

Figure 30. Oscillator Feedthrough vs. Frequency, Wide Bandwidth  $(V_{DD} = 3.3 \text{ V})$

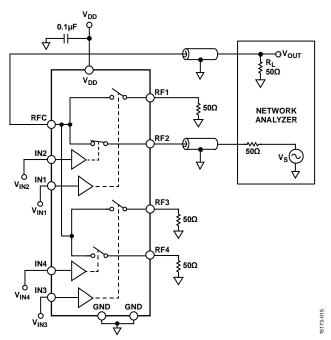

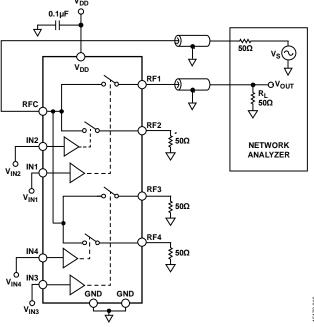

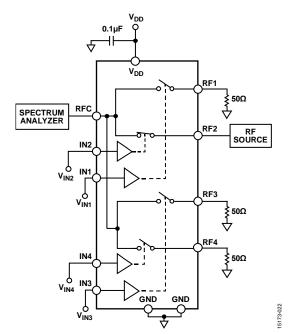

# **TEST CIRCUITS**

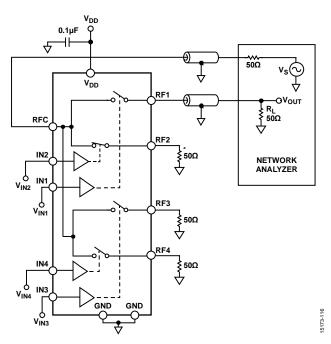

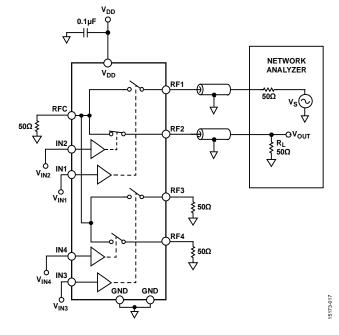

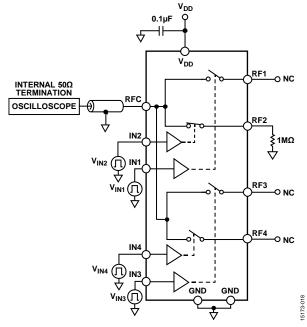

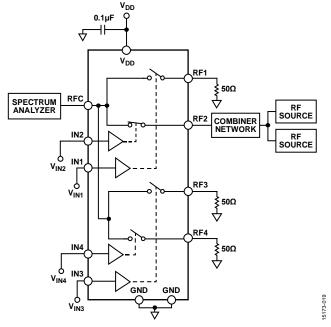

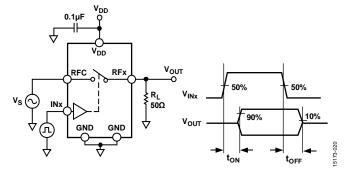

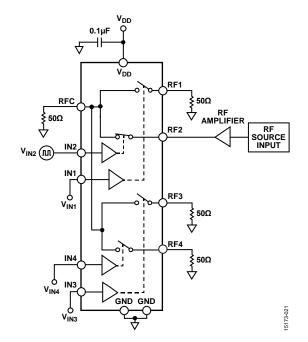

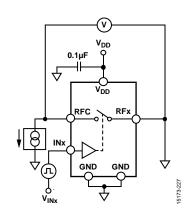

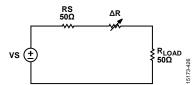

The test circuits shown in Figure 31 to Figure 42 are applicable to all channels. Additional pins are omitted for clarity and  $V_S$  is the source voltage.

Figure 31. Insertion Loss and Return Loss

Figure 32. Isolation (All Switches Off)

Figure 33. Isolation (RF2 to RFC On, RF1 to RFC Off)

Figure 34. Crosstalk

Figure 35. Video Feedthrough

Figure 36. IP2 and IP3

Figure 37. Switch Timing,  $t_{\text{ON}}$  and  $t_{\text{OFF}}$  (All RFx Terminals Connected to 50  $\Omega$  Termination)

Figure 38. Hot Switching Evaluation Setup, 2 GHz RF Source, 50% Duty Cycle, 5 kHz Switching Actuation Speed

Figure 39. On Resistance

Figure 41. Second and Third Harmonics, RF Power

Figure 42. On Leakage

#### **TERMINOLOGY**

#### **Insertion Loss**

Insertion loss is the amount of signal attenuation between the input and output ports of the switch when the switch is in the on state. Expressed in decibels, ensure that insertion loss is as small as possible for maximum power transfer.

An example calculation of insertion loss based on the setup in Figure 31 is as follows:

Insertion Loss (dB) =

$$-20\log_{10}|S_{RF2RFC}|$$

where  $S_{RF2RFC}$  is the transmission coefficient measured from RF2 to RFC with RF2 in the on position. All unused switches are in the off position and terminated in a purely resistive load of 50  $\Omega$ .

#### **Isolation**

Isolation is the amount of signal attenuation between the input and output ports of the switch when the switch is in the off state. Expressed in decibels, ensure that isolation is as large as possible.

An example calculation of isolation based on the setup in Figure 32 is as follows:

Isolation (dB) =

$$-20\log_{10}|S_{RFCRFI}|$$

where  $S_{RFCRF1}$  is the transmission coefficient measured from RFC to RF1 with RF1 in the off position. All unused switches are in the off position and terminated in a purely resistive load of 50  $\Omega$ .

#### Crosstalk

Crosstalk is a measure of unwanted signals coupled through from one channel to another because of parasitic capacitance.

An example calculation of crosstalk based on the setup in Figure 34 is as follows:

$$Crosstalk$$

(dB) =  $-20log_{10}|S_{RF1RF2}|$

where  $S_{RFIRF2}$  is the transmission coefficient measured from RF1 to RF2 with RF1 in the off position and RF2 in the on position. All unused switches are in the off position and terminated in a purely resistive load of 50  $\Omega$ .

#### **Return Loss**

Return Loss is the magnitude of the reflection coefficient expressed in decibels, and the amount of reflected signal relative to the incident signal.

An example calculation of return loss based on the setup in Figure 31 is as follows:

Return Loss (dB) =

$$-20\log_{10}|S_{11}|$$

where  $S_{II}$  is the reflection coefficient of the port under test.

#### Third-Order Intermodulation Intercept (IP3)

IP3 is the intersection point of the fundamental  $P_{\rm OUT}$  vs.  $P_{\rm IN}$  extrapolated line and the third-order intermodulation products extrapolated line of a two-tone test. IP3 is a figure of merit that characterizes the switch linearity.

#### Second-Order Intermodulation Intercept (IP2)

IP2 is the intersection point of the fundamental  $P_{OUT}$  vs.  $P_{IN}$  extrapolated line and the second-order intermodulation products extrapolated line of a two-tone test. IP2 is a figure of merit that characterizes the switch linearity.

#### Second Distortion Harmonic (HD2)

HD2 is the amplitude of the second distortion harmonic, where, for a signal whose fundamental frequency is f, the second distortion harmonic has a frequency of 2 f. This measurement is a single-tone test expressed with reference to the carrier signal (dBc).

#### Third Distortion Harmonic (HD3)

HD3 is the amplitude of the third distortion harmonic, where, for a signal whose fundamental frequency is f, the third distortion harmonic has a frequency of 3 f. This measurement is a single tone test expressed with reference to the carrier signal (dBc).

#### On Switching Time (ton)

$t_{\rm ON}$  is the time it takes for the switch to turn on.  $t_{\rm ON}$  is measured from 50% of the control signal (INx) to 90% of the on level. No power was applied through the switch during this test (cold switched). The switch was terminated into a 50  $\Omega$  load.

#### Off Switching Time (toff)

$t_{\text{OFF}}$  is the time it takes for the switch to turn off.  $t_{\text{OFF}}$  is measured from 50% of the control signal (INx) to 10% of the on level. No power was applied through the switch during this test (cold switched). The switch was terminated into a 50  $\Omega$  load.

#### **Actuation Frequency**

The actuation frequency refers to the speed at which the ADGM1004 can be switched on and off. The actuation frequency is dependent on both the settling times and the on and off switching times.

#### Power-Up Time

The power-up time is a measure of the time required for the device to power up and start to pass 90% of an RF input signal after the  $V_{\rm DD}$  pin reaches 95%.

#### Video Feedthrough

Video feedthrough is a measure of the spurious signals present at the RFx ports of the switch when the control voltage is switched from high to low or from low to high without an RF signal present.

#### **Internal Oscillator Frequency**

The internal oscillator frequency is the value of the on-board oscillator that drives the gate control chip of the ADGM1004.

#### **Internal Oscillator Feedthrough**

The internal oscillator feedthrough is the amount of internal oscillator signal that feeds through to the RFx and RFC pins of the switch. This signal appears as a noise spur on the RFx and RFC pins of the switch at the frequency the oscillator is operating at and the harmonics thereof.

#### On Resistance (Ron)

R<sub>ON</sub> is the resistance of a switch in the closed/on state measured between the RFx and RFC package pins. Measure resistance in 4-wire mode to null out any cabling or PCB series resistances.

#### On Resistance Drift

On resistance drift is the change in the  $R_{\text{ON}}$  of the switch over the specified criteria in Table 1.

#### **Continuously On Lifetime**

The continuously on lifetime parameter measures how long the switch is left in a continuously on state. If the switch is left in the on position for an extended period, this parameter affects the turn off mechanism of the device.

#### **Actuation Lifetime**

Actuation lifetime is the number of consecutive open, close, and open cycles that the device can complete without the  $R_{\rm ON}$  exceeding a specified limit and no occurrence of failures to open (FTO) or failures to close (FTC).

#### **Cold Switching**

Cold switching operates the switch in a mode so that no voltage differential exists between the source and the drain when the switch is closed and/or no current is flowing from the source to the drain when the switch opens. All switches have longer lives when cold switched.

#### **Hot Switching**

Hot switching is operating the switch in a mode where a voltage differential exists between the source and the drain when the switch is closed and/or current is flowing from RFx to RFC when the switch opens. Hot switching results in a reduced switch life, depending on the magnitude of the open circuit voltage between the source and the drain.

#### Input High Voltage (VINH)

$V_{\text{INH}}$  is the minimum input voltage for Logic 1.

#### Input Low Voltage (V<sub>INL</sub>)

$V_{\text{INL}}$  is the maximum input voltage for Logic 0.

#### Input Current (IINL, IINH)

$I_{\text{INL}}$  and  $I_{\text{INH}}$  are the low and high input currents of the digital inputs.

#### Low Power Mode Current (IDD EXT VCP)

$I_{DD\;EXT\;VCP}$  is the amount of supply current used by the gate driver circuity when the internal oscillator and the charge pump circuitry are disabled by setting the EXTD\_EN pin high.

#### External Drive Current (I<sub>CP EXT VCP</sub>)

$I_{\text{CP EXT VCP}}$  is the amount of current used by the ADGM1004 from the external 80 V power supply when the internal oscillator and the charge pump circuitry are turned off by setting EXTD\_EN pin high.

#### THEORY OF OPERATION

The ADGM1004 is a wideband SP4T switch fabricated using Analog Devices MEMS switch technology. This technology enables high power, low loss, low distortion GHz switches for use in demanding RF applications.

The MEMS switch simultaneously brings together high frequency RF performance and 0 Hz/dc precision performance. This combination, coupled with superior reliability and a tiny surface-mountable form factor, makes the MEMS switch an ideal switching solution for all RF and precision signal instrumentation needs.

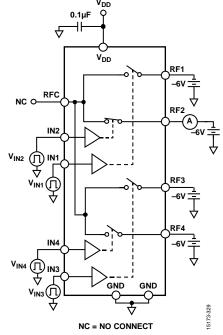

Figure 43 shows a cross section of the switch with dimensions. The switch is an electrostatically actuated cantilever beam connected in a 3-terminal configuration. Functionally, the switch is analogous to a field effect transistor (FET). The terminals can be used as a source, gate, or drain.

Figure 43. Cross Section of the MEMS Switch Design Showing the Cantilever Switch Beam (Not to Scale)

When a dc actuation voltage is applied between the gate electrode and the source (the switch beam), an electrostatic force is generated, resulting in attracting the beam toward the substrate. A separate on-board driver IC generates the 80 V bias voltage used for actuation.

When the bias voltage between the gate and the source exceeds the threshold voltage of the switch ( $V_{TH}$ ) the contacts on the beam touch the drain, which completes the circuit between the source and the drain and turns the switch on. When the bias voltage is removed, that is, the 0 V on the gate electrode, the beam acts as a spring generating a sufficient restoring force to open the connection between the source and the drain, thus breaking the circuit and turning the switch off.

The silicon cap covering the switch die is shown in Figure 43. This cap hermetically seals the switch, which improves reliability. The switch contacts do not suffer from dry switching or low power switching lifetime degradation.

#### **PARALLEL DIGITAL INTERFACE**

The ADGM1004 is controlled via a parallel digital interface. Standard complimentary metal-oxide semiconductor (CMOS)/ low voltage transistor to transistor logic (LVTTL) signals applied through this interface control the actuation or release of all ADGM1004 switch channels. Gate signals applied are boosted to provide the required voltages required to actuate the MEMS switch.

Setting the PIN/SPI pin low enables the parallel digital interface in 4-wire SP4T mode. In parallel mode, Pin 1 to Pin 4 (IN1 to IN4) control the switching functions of the ADGM1004. When a Logic 1 is applied to one of these pins, the gate of the corresponding switch is activated and the switch turns on. Conversely, when a Logic 0 is applied to one of these pins, the switch turns off. Note that it is possible to connect more than one RFx input to RFC at a time. See Table 6 for the ADGM1004 truth table.

Table 6. Truth Table When in Parallel Digital Interface Mode

|     |     |     |     | Igital Iliteriace Wiode | T          | T          | Г          |

|-----|-----|-----|-----|-------------------------|------------|------------|------------|

| IN1 | IN2 | IN3 | IN4 | RF1 to RFC              | RF2 to RFC | RF3 to RFC | RF4 to RFC |

| 0   | 0   | 0   | 0   | Off                     | Off        | Off        | Off        |

| 0   | 0   | 0   | 1   | Off                     | Off        | Off        | On         |

| 0   | 0   | 1   | 0   | Off                     | Off        | On         | Off        |

| 0   | 0   | 1   | 1   | Off                     | Off        | On         | On         |

| 0   | 1   | 0   | 0   | Off                     | On         | Off        | Off        |

| 0   | 1   | 0   | 1   | Off                     | On         | Off        | On         |

| 0   | 1   | 1   | 0   | Off                     | On         | On         | Off        |

| 0   | 1   | 1   | 1   | Off                     | On         | On         | On         |

| 1   | 0   | 0   | 0   | On                      | Off        | Off        | Off        |

| 1   | 0   | 0   | 1   | On                      | Off        | Off        | On         |

| 1   | 0   | 1   | 0   | On                      | Off        | On         | Off        |

| 1   | 0   | 1   | 1   | On                      | Off        | On         | On         |

| 1   | 1   | 0   | 0   | On                      | On         | Off        | Off        |

| 1   | 1   | 0   | 1   | On                      | On         | Off        | On         |

| 1   | 1   | 1   | 0   | On                      | On         | On         | Off        |

| 1   | 1   | 1   | 1   | On                      | On         | On         | On         |

#### **SPI DIGITAL INTERFACE**

The ADGM1004 can be controlled via a digital SPI when the  $\overline{\text{PIN}}/\text{SPI}$  pin is high. The SPI is compatible with SPI Mode 0 (clock polarity (CPOL) = 0, clock phase (CPHA) = 0) and Mode 3 (CPOL = 1, CPHA = 1) and it operates with SCLK frequencies up to 10 MHz. When the SPI is active, the default mode is addressable, in which, the device registers are accessed by a 16-bit SPI command that is bound by the state of the  $\overline{\text{CS}}$  pin. The ADGM1004 can also operate in daisy-chain mode.

The SPI interface pins of the ADGM1004 are  $\overline{\text{CS}}$ , SCLK, SDI, and SDO. Hold the  $\overline{\text{CS}}$  pin low when using the SPI. The data on the SDI pin is captured on the rising edge of SCLK, and data is propagated out on the SDO pin on the falling edge of SCLK. The SDO pin has a push pull output driver architecture. Therefore, the ADGM1004 does not require pull-up resistors. The two modes of SPI operation are: addressable and daisy-chain.

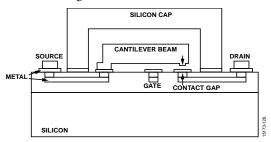

#### Addressable Mode

Addressable mode is the default mode for the ADGM1004 upon power-up. A single SPI frame in addressable mode is bound by a  $\overline{\text{CS}}$  falling edge and the succeeding  $\overline{\text{CS}}$  rising edge. The frame is comprised of 16 SCLK cycles. The timing diagram for addressable mode is shown in Figure 44 for SPI mode 0.

The first SDI signal bit indicates if the SPI command is a read or write command. The next seven bits determine the target register address. The remaining eight bits provide the data to the addressed register. The last eight bits are ignored during a read command because the SDO pin propagates out the data contained in the addressed register during these clock cycles.

In Mode 0, during any SPI command, SDO sends out eight alignment bits on the  $\overline{\text{CS}}$  falling edge and the first seven SCLK falling edges (in Mode 3, the first SCLK falling edge is ignored as shown in Figure 45). The alignment bits observed at SDO are 0x25.

The target register address of an SPI command is determined on the eighth SCLK rising edge. Data from this register propagates out on the SDO pin from the 8<sup>th</sup> to the 15<sup>th</sup> SCLK falling edge during SPI reads. A register write occurs on the 16<sup>th</sup> SCLK rising edge during SPI writes.

Figure 45. Addressable Mode Timing Diagram (Mode 3)

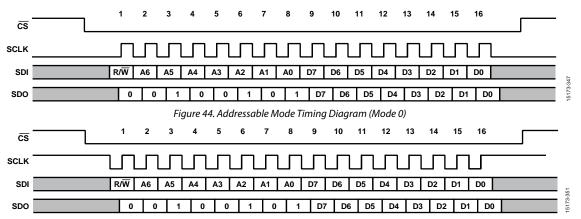

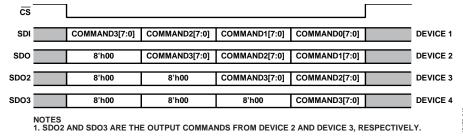

#### **Daisy-Chain Mode**

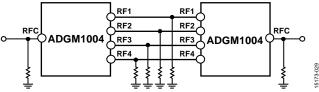

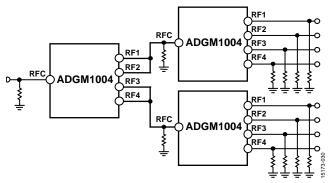

The connection of several ADGM1004 devices in a daisy-chain configuration is possible. All devices share the same CS and SCLK lines while the SDO pin of one device forms a connection to the SDI pin of the next device, creating a shift register. In daisy-chain mode, the SDO signal is an 8-cycle delayed version of the SDI signal (see Figure 47).

The ADGM1004 can only enter daisy-chain mode from addressable mode by sending the 16-bit SPI command, 0x2500. See Figure 47 for an example of this command. When the ADGM1004 receives this command, the SDO pin of the devices sends out the same command because the alignment bits at the SDO pin are 0x25. This command allows multiple daisychained devices to enter daisy-chain mode in a single SPI frame. A hardware reset is required to exit daisy-chain mode.

For the timing diagram of a typical daisy-chain SPI frame, see Figure 48. When the  $\overline{\text{CS}}$  pin goes high, Device 1 writes Command 0, Bits[7:0], to the SWITCH\_DATA register, Device 2 writes Command 1, Bits[7:0], to the switches, and so on. The SPI block uses the last eight bits received through the SDI pin to update the switches. After entering daisy-chain mode, the first eight bits sent out by the SDO pin are 0x00. When  $\overline{CS}$  goes high, the internal shift register value does not reset back to 0.

An SCLK rising edge reads in data on the SDI pin while data is propagated out of the SDO pin on an SCLK falling edge. The expected number of SCLK cycles are a multiple of eight before the  $\overline{\text{CS}}$  pin goes high. When this is not the case, the SPI interface sends the last eight bits received to the SWITCH\_DATA register.

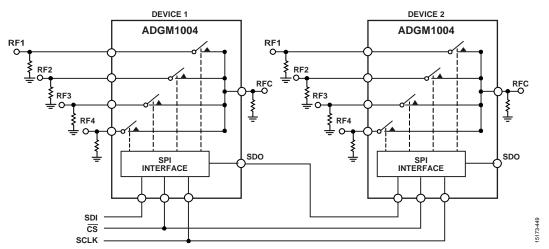

Figure 46. Two SPI Controlled ADGM1004 Switches Connected in Daisy-Chain Configuration

Figure 47. SPI Command to Enter Daisy-Chain Mode

Figure 48. Example of SPI Frame with Three ADGM1004 Switches Connected in Daisy-Chain Mode

#### **Hardware Reset**

The digital section of the ADGM1004 goes through an initialization phase during  $V_{\rm DD}$  power-up. To hardware reset the device, power cycle the  $V_{\rm DD}$  input. After power-up or a hardware reset, ensure that there is a minimum of 10  $\mu s$  from the time of power-up or reset before any SPI command is issued. Ensure that  $V_{\rm DD}$  does not drop out during the 10  $\mu s$  initialization phase because  $V_{\rm DD}$  dropout can result in incorrect operation of the ADGM1004.

#### Internal Error Status

When an internal error is detected in the device, the internal error is flagged by the INTERNAL\_ERROR bits (Bits[7:6]) of the SWITCH\_DATA register (Register 0x20), as shown in Table 9. An internal error results from an error in the configuration of the device at power up.

#### INTERNAL OSCILLATOR FEEDTHROUGH