# 49.6.41 Contrast And Brightness Control Register

| Name:<br>Address: | ISC_CBC_CTRL<br>0xF00083B4 |    |    |         |         |    |        |  |  |  |

|-------------------|----------------------------|----|----|---------|---------|----|--------|--|--|--|

| Access:           | Read/Write                 |    |    |         |         |    |        |  |  |  |

| 31                | 30                         | 29 | 28 | 27      | 26      | 25 | 24     |  |  |  |

| -                 | -                          | _  | _  | —       | —       | _  | _      |  |  |  |

| 23                | 22                         | 21 | 20 | 19<br>— | 18<br>— | 17 | 16     |  |  |  |

| 15                | 14                         | 13 | 12 | 11      | 10      | 9  | 8      |  |  |  |

| _                 | -                          | -  | -  | -       | _       | _  | -      |  |  |  |

| 7                 | 6                          | 5  | 4  | 3       | 2       | 1  | 0      |  |  |  |

| -                 | -                          | _  | _  | _       | _       | _  | ENABLE |  |  |  |

# • ENABLE: Contrast and Brightness Control Enable

0: Contrast and brightness control is disabled.

1: Contrast and brightness control is enabled.

# 49.6.42 Contrast And Brightness Configuration Register

| Name:    | ISC_CBC_CFG |    |    |    |       |      |      |

|----------|-------------|----|----|----|-------|------|------|

| Address: | 0xF00083B8  |    |    |    |       |      |      |

| Access:  | Read/Write  |    |    |    |       |      |      |

| 31       | 30          | 29 | 28 | 27 | 26    | 25   | 24   |

| -        | -           | -  | -  | -  | -     | -    | -    |

|          |             |    |    |    |       |      |      |

| 23       | 22          | 21 | 20 | 19 | 18    | 17   | 16   |

| —        | -           | -  | -  | -  | -     | -    | -    |

| 15       | 14          | 13 | 12 | 11 | 10    | 9    | 8    |

| -        | -           | -  | -  | -  | -     | -    | -    |

| 7        | 6           | 5  | 4  | 3  | 2     | 1    | 0    |

| -        | -           | _  | _  | -  | CCIRI | MODE | CCIR |

# CCIR: CCIR656 Stream Enable

- 0: Raw mode

- 1: CCIR656 stream

## CCIRMODE: CCIR656 Byte Ordering

| Value | Name | Description                    |

|-------|------|--------------------------------|

| 0     | СВҮ  | Byte ordering Cb0, Y0, Cr0, Y1 |

| 1     | CRY  | Byte ordering Cr0, Y0, Cb0, Y1 |

| 2     | ҮСВ  | Byte ordering Y0, Cb0, Y1, Cr0 |

| 3     | YCR  | Byte ordering Y0, Cr0, Y1, Cb0 |

| 49.6.43 Contrast And Brightness, Brightness Register |                      |            |     |     |    |        |    |  |  |  |  |

|------------------------------------------------------|----------------------|------------|-----|-----|----|--------|----|--|--|--|--|

| Name:                                                | Name: ISC_CBC_BRIGHT |            |     |     |    |        |    |  |  |  |  |

| Address:                                             | 0xF00083BC           | 0xF00083BC |     |     |    |        |    |  |  |  |  |

| Access:                                              | Read/Write           |            |     |     |    |        |    |  |  |  |  |

| 31                                                   | 30                   | 29         | 28  | 27  | 26 | 25     | 24 |  |  |  |  |

| _                                                    | -                    | _          | -   | -   | _  | _      | -  |  |  |  |  |

| 23                                                   | 22                   | 21         | 20  | 19  | 18 | 17     | 16 |  |  |  |  |

| -                                                    | -                    | -          | -   | -   | -  | -      | -  |  |  |  |  |

| 15                                                   | 14                   | 13         | 12  | 11  | 10 | 9      | 8  |  |  |  |  |

| -                                                    | -                    | -          | -   | -   |    | BRIGHT |    |  |  |  |  |

| 7                                                    | 6                    | 5          | 4   | 3   | 2  | 1      | 0  |  |  |  |  |

|                                                      |                      |            | BRI | GHT |    |        |    |  |  |  |  |

• BRIGHT: Brightness Control (signed 11 bits 1:10:0)

#### 49.6.44 Contrast And Brightness, Contrast Register ISC\_CBC\_CONTRAST Name: Address: 0xF00083C0 Access: Read/Write 31 30 29 28 27 26 25 24 \_ \_ \_ \_ \_ \_ \_ -23 22 21 20 19 18 17 16 \_ -\_ \_ \_ \_ \_ \_ 15 14 13 12 11 10 9 8 CONTRAST -\_ \_ \_ 7 6 5 4 3 2 1 0 CONTRAST

• CONTRAST: Contrast (signed 12 bits 1:3:8)

#### 49.6.45 Subsampling 4:4:4 to 4:2:2 Control Register ISC\_SUB422\_CTRL Name: Address: 0xF00083C4 Access: Read/Write 31 30 29 28 27 26 25 24 \_ \_ \_ \_ \_ \_ --23 22 21 20 19 18 17 16 \_ \_ \_ \_ \_ \_ \_ \_ 15 13 12 10 9 8 14 11 -\_ \_ \_ \_ \_ \_ \_ 7 6 5 4 3 2 1 0 \_ \_ \_ \_ \_ \_ \_ ENABLE

# • ENABLE: 4:4:4 to 4:2:2 Chrominance Horizontal Subsampling Filter Enable

0: Subsampler is disabled.

1: Subsampler is enabled.

# 49.6.46 Subsampling 4:4:4 to 4:2:2 Configuration Register

| Name:<br>Address: | ISC_SUB422_CFG<br>0xF00083C8 |     |     |    |       |      |      |  |  |

|-------------------|------------------------------|-----|-----|----|-------|------|------|--|--|

| Access:           | Read/Write                   |     |     |    |       |      |      |  |  |

| 31                | 30                           | 29  | 28  | 27 | 26    | 25   | 24   |  |  |

| _                 | -                            | -   | -   | -  | _     | _    | -    |  |  |

| 23                | 22                           | 21  | 20  | 19 | 18    | 17   | 16   |  |  |

| -                 | -                            | -   | -   | -  | -     | -    | -    |  |  |

| 15                | 14                           | 13  | 12  | 11 | 10    | 9    | 8    |  |  |

| -                 | -                            | -   | -   | _  | _     | _    | -    |  |  |

| 7                 | 6                            | 5   | 4   | 3  | 2     | 1    | 0    |  |  |

| -                 | -                            | FIL | TER | —  | CCIRI | MODE | CCIR |  |  |

#### CCIR: CCIR656 Input Stream

- 0: Raw mode

- 1: CCIR mode

# CCIRMODE: CCIR656 Byte Ordering

| Value | Name | Description                    |

|-------|------|--------------------------------|

| 0     | СВҮ  | Byte ordering Cb0, Y0, Cr0, Y1 |

| 1     | CRY  | Byte ordering Cr0, Y0, Cb0, Y1 |

| 2     | ҮСВ  | Byte ordering Y0, Cb0, Y1, Cr0 |

| 3     | YCR  | Byte ordering Y0, Cr0, Y1, Cb0 |

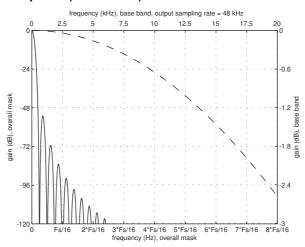

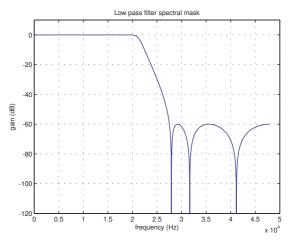

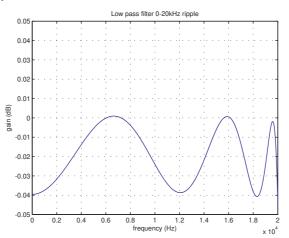

### • FILTER: Low Pass Filter Selection

| Value | Name    | Description           |

|-------|---------|-----------------------|

| 0     | FILT0CO | Cosited, {1}          |

| 1     | FILT1CE | Centered {1, 1}       |

| 2     | FILT2CO | Cosited {1,2,1}       |

| 3     | FILT3CE | Centered {1, 3, 3, 1} |

Atmel

# 49.6.47 Subsampling 4:2:2 to 4:2:0 Control Register

| Name:<br>Address: | ISC_SUB420_CTRL<br>0xF00083CC |    |        |    |    |    |        |  |  |  |

|-------------------|-------------------------------|----|--------|----|----|----|--------|--|--|--|

| Access:           | Read/Write                    |    |        |    |    |    |        |  |  |  |

| 31                | 30                            | 29 | 28     | 27 | 26 | 25 | 24     |  |  |  |

| -                 | -                             | _  | —      | _  | —  | _  | –      |  |  |  |

| 23                | 22                            | 21 | 20     | 19 | 18 | 17 | 16     |  |  |  |

| _                 | -                             | _  | -      | _  | _  | _  | _      |  |  |  |

| 15                | 14                            | 13 | 12     | 11 | 10 | 9  | 8      |  |  |  |

| _                 | -                             | -  | -      | -  | -  | -  | -      |  |  |  |

| 7                 | 6                             | 5  | 4      | 3  | 2  | 1  | 0      |  |  |  |

| -                 | -                             | —  | FILTER | —  | —  | —  | ENABLE |  |  |  |

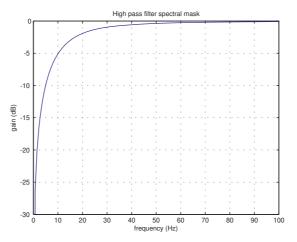

### • ENABLE: 4:2:2 to 4:2:0 Vertical Subsampling Filter Enable (Center Aligned)

0: Subsampler disabled

1: Subsampler enabled

# • FILTER: Interlaced or Progressive Chrominance Filter

0: Progressive filter {0.5, 0.5}

1: Field-dependent filter, top field filter is {0.75, 0.25}, bottom field filter is {0.25, 0.75}

# 49.6.48 Rounding, Limiting and Packing Configuration Register

| Name:<br>Address: | ISC_RLP_CFG<br>0xF00083D0 |    |     |     |    |    |    |

|-------------------|---------------------------|----|-----|-----|----|----|----|

|                   | Read/Write                |    |     |     |    |    |    |

| Access:           | Read/write                |    |     |     |    |    |    |

| 31                | 30                        | 29 | 28  | 27  | 26 | 25 | 24 |

| -                 | -                         | -  | -   | -   | -  | -  | -  |

|                   |                           |    |     |     |    |    | •  |

| 23                | 22                        | 21 | 20  | 19  | 18 | 17 | 16 |

| -                 | -                         | -  | -   | -   | -  | _  | -  |

|                   |                           |    |     |     |    |    |    |

| 15                | 14                        | 13 | 12  | 11  | 10 | 9  | 8  |

|                   |                           |    | ALF | РНА |    |    |    |

| -                 | 0                         | _  | 4   | 0   | 0  |    | 0  |

| 7                 | 6                         | 5  | 4   | 3   | 2  | 1  | 0  |

| —                 | -                         | _  | -   |     | MO | DE |    |

### MODE: Rounding, Limiting and Packing Mode

| Value | Name         | Description                      |

|-------|--------------|----------------------------------|

| 0     | DAT8         | 8-bit data                       |

| 1     | DAT9         | 9-bit data                       |

| 2     | DAT10        | 10-bit data                      |

| 3     | DAT11        | 11-bit data                      |

| 4     | DAT12        | 12-bit data                      |

| 5     | DATY8        | 8-bit luminance only             |

| 6     | DATY10       | 10-bit luminance only            |

| 7     | ARGB444      | 12-bit RGB+4-bit Alpha (MSB)     |

| 8     | ARGB555      | 15-bit RGB+1-bit Alpha (MSB)     |

| 9     | RGB565       | 16-bit RGB                       |

| 10    | ARGB32       | 24-bits RGB mode+8-bit Alpha     |

| 11    | YYCC         | YCbCr mode (full range, [0–255]) |

| 12    | YYCC_LIMITED | YCbCr mode (limited range)       |

# • ALPHA: Alpha Value for Alpha-enabled RGB Mode

# 49.6.49 Histogram Control Register

| Name:<br>Address: | ISC_HIS_CTRL<br>0xF00083D4<br>Read/Write |    |    |         |         |    |        |

|-------------------|------------------------------------------|----|----|---------|---------|----|--------|

| Access:           | Read/write                               |    |    |         |         |    |        |

| 31                | 30                                       | 29 | 28 | 27      | 26      | 25 | 24     |

| -                 | -                                        | -  | -  | -       | -       | -  | -      |

| 23                | 22                                       | 21 | 20 | 19<br>- | 18<br>- | 17 | 16     |

| 15                | 14                                       | 13 | 12 | 11      | 10      | 9  | 8      |

| _                 | -                                        | -  | -  | _       | _       | -  | -      |

| 7                 | 6                                        | 5  | 4  | 3       | 2       | 1  | 0      |

| -                 | -                                        | -  | -  | -       | -       | -  | ENABLE |

# • ENABLE: Histogram Sub Module Enable

0: Histogram disabled.

1: Histogram enabled.

## 49.6.50 Histogram Configuration Register

| Name:<br>Address:<br>Access: | ISC_HIS_CFG<br>0xF00083D8<br>Read/Write |     |      |    |    |      |     |

|------------------------------|-----------------------------------------|-----|------|----|----|------|-----|

| ALLESS.                      | Reau/white                              |     |      |    |    |      |     |

| 31                           | 30                                      | 29  | 28   | 27 | 26 | 25   | 24  |

| -                            | -                                       | -   | -    | -  | -  | -    | -   |

| 23                           | 22                                      | 21  | 20   | 19 | 18 | 17   |     |

| -                            | -                                       | _   | -    | -  | -  | -    | -   |

| 15                           | 14                                      | 13  | 12   | 11 | 10 | 9    | 8   |

| -                            | -                                       | —   | -    | -  | _  | -    | RAR |

| 7                            | 6                                       | 5   | 4    | 3  | 2  | 1    | 0   |

| -                            | -                                       | BAY | 'SEL | -  |    | MODE |     |

#### MODE: Histogram Operating Mode

| Value | Name     | Description                                      |

|-------|----------|--------------------------------------------------|

| 0     | Gr       | Gr sampling                                      |

| 1     | R        | R sampling                                       |

| 2     | Gb       | Gb sampling                                      |

| 3     | В        | B sampling                                       |

| 4     | Y        | Luminance-only mode                              |

| 5     | RAW      | Raw sampling                                     |

| 6     | YCCIR656 | Luminance only with CCIR656 10-bit or 8-bit mode |

#### BAYSEL: Bayer Color Component Selection

| Value | Name | escription                                       |  |  |  |  |

|-------|------|--------------------------------------------------|--|--|--|--|

| 0     | GRGR | Starting row configuration is G R G R (red row)  |  |  |  |  |

| 1     | RGRG | Starting row configuration is R G R G (red row)  |  |  |  |  |

| 2     | GBGB | Starting row configuration is G B G B (blue row  |  |  |  |  |

| 3     | BGBG | Starting row configuration is B G B G (blue row) |  |  |  |  |

### • RAR: Histogram Reset After Read

0: Reset after read mode is disabled

1: Reset after read mode is enabled

# 49.6.51 DMA Configuration Register

|          | -          | -   |      |    |       |     |       |

|----------|------------|-----|------|----|-------|-----|-------|

| Name:    | ISC_DCFG   |     |      |    |       |     |       |

| Address: | 0xF00083E0 |     |      |    |       |     |       |

| Access:  | Read/Write |     |      |    |       |     |       |

| 31       | 30         | 29  | 28   | 27 | 26    | 25  | 24    |

| _        | -          | -   | —    | _  | —     | _   | -     |

| 23       | 22         | 21  | 20   | 19 | 18    | 17  | 16    |

| —        | -          | -   | -    | -  | -     | -   | -     |

| 15       | 14         | 13  | 12   | 11 | 10    | 9   | 8     |

| _        | -          | _   | _    | _  | _     | CME | BSIZE |

|          |            |     |      |    |       |     |       |

| 7        | 6          | 5   | 4    | 3  | 2     | 1   | 0     |

| -        | -          | YMB | SIZE | _  | IMODE |     |       |

#### IMODE: DMA Input Mode Selection

| Value | Name     | scription                      |  |  |  |  |  |

|-------|----------|--------------------------------|--|--|--|--|--|

| 0     | PACKED8  | 8 bits, single channel packed  |  |  |  |  |  |

| 1     | PACKED16 | ts, single channel packed      |  |  |  |  |  |

| 2     | PACKED32 | 32 bits, single channel packed |  |  |  |  |  |

| 3     | YC422SP  | 32 bits, dual channel          |  |  |  |  |  |

| 4     | YC422P   | 32 bits, triple channel        |  |  |  |  |  |

| 5     | YC420SP  | 32 bits, dual channel          |  |  |  |  |  |

| 6     | YC420P   | 32 bits, triple channel        |  |  |  |  |  |

# YMBSIZE: DMA Memory Burst Size Y channel

| Value | Name    | Description          |

|-------|---------|----------------------|

| 0     | SINGLE  | DMA single access    |

| 1     | BEATS4  | 4-beat burst access  |

| 2     | BEATS8  | 8-beat burst access  |

| 3     | BEATS16 | 16-beat burst access |

### CMBSIZE: DMA Memory Burst Size C channel

| Value | Name    | Description          |

|-------|---------|----------------------|

| 0     | SINGLE  | DMA single access    |

| 1     | BEATS4  | 4-beat burst access  |

| 2     | BEATS8  | 8-beat burst access  |

| 3     | BEATS16 | 16-beat burst access |

#### 49.6.52 DMA Control Register

| Name:<br>Address: | ISC_DCTRL<br>0xF00083E4 |    |    |    |     |    |    |

|-------------------|-------------------------|----|----|----|-----|----|----|

| Access:           | Read/Write              |    |    |    |     |    |    |

| 31                | 30                      | 29 | 28 | 27 | 26  | 25 | 24 |

| -                 | -                       | _  | _  | _  | _   | _  | -  |

| 23                | 22                      | 21 | 20 | 19 | 18  | 17 | 16 |

| 15                | 14                      | 13 | 12 | 11 | 10  | 9  | 8  |

|                   |                         |    |    |    |     |    |    |

| 7                 | 6                       | 5  | 4  | 3  | 2   | 1  | 0  |

| DONE              | FIELD                   | WB | IE | _  | DVI | EW | DE |

#### • DE: Descriptor Enable

0: Descriptor disabled

1: Descriptor enabled

#### • DVIEW: Descriptor View

| Value | Name       | escription                                       |  |  |  |

|-------|------------|--------------------------------------------------|--|--|--|

| 0     | PACKED     | Address {0} Stride {0} are updated               |  |  |  |

| 1     | SEMIPLANAR | EMIPLANAR Address {0,1} Stride {0,1} are updated |  |  |  |

| 2     | PLANAR     | Address {0,1,2} Stride {0,1,2} are updated       |  |  |  |

#### • IE: Interrupt Enable

0: DMA Done interrupt is generated.

1: DMA Done interrupt is not set.

#### • WB: Write Back Operation Enable

0: Write Back operation is skipped.

1: Write Back operation is performed.

### • FIELD: Value of Captured Frame Field Signal<sup>(1)(2)</sup>

- 0: Field value is 0.

- 1: Field value is 1.

#### • DONE: Descriptor Processing Status<sup>(2)</sup>

- 0: Descriptor not processed yet

- 1: Descriptor processed

- Notes: 1. Only relevant for interlaced content.

- 2. Appears only in descriptor located in memory. Can be used only if WB (Write Back) is set.

| 49.6.53 DMA Descriptor Address Register |            |    |    |    |    |    |    |  |  |

|-----------------------------------------|------------|----|----|----|----|----|----|--|--|

| Name:                                   | ISC_DNDA   |    |    |    |    |    |    |  |  |

| Address:                                | 0xF00083E8 |    |    |    |    |    |    |  |  |

| Access:                                 | Read/Write |    |    |    |    |    |    |  |  |

| 31                                      | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|                                         |            |    | N  | AC |    |    |    |  |  |

| 23                                      | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|                                         |            |    | N  | AC |    |    |    |  |  |

| 15                                      | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

| NDA                                     |            |    |    |    |    |    |    |  |  |

| 7                                       | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|                                         |            | N  | DA |    |    | _  | -  |  |  |

NDA: Next Descriptor Address Register

| 49.6.54 DMA Address 0 Register |            |    |    |    |    |    |    |  |  |

|--------------------------------|------------|----|----|----|----|----|----|--|--|

| Name:                          | ISC_DAD0   |    |    |    |    |    |    |  |  |

| Address:                       | 0xF00083EC |    |    |    |    |    |    |  |  |

| Access:                        | Read/Write |    |    |    |    |    |    |  |  |

| 31                             | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|                                |            |    | AE | 00 |    |    |    |  |  |

| 23                             | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|                                |            |    | AE | 00 |    |    |    |  |  |

| 15                             | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

| AD0                            |            |    |    |    |    |    |    |  |  |

| 7                              | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|                                |            |    | A  | 00 |    |    |    |  |  |

• AD0: Channel 0 Address

| 49.6.55 DMA Stride 0 Register |            |    |    |    |    |    |    |  |  |

|-------------------------------|------------|----|----|----|----|----|----|--|--|

| Name:                         | ISC_DST0   |    |    |    |    |    |    |  |  |

| Address:                      | 0xF00083F0 |    |    |    |    |    |    |  |  |

| Access:                       | Read/Write |    |    |    |    |    |    |  |  |

| 31                            | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|                               |            |    | ST | 0  |    |    |    |  |  |

| 23                            | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|                               |            |    | ST | 0  |    |    |    |  |  |

| 15                            | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

|                               | STO        |    |    |    |    |    |    |  |  |

| 7                             | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|                               |            |    | ST | 0  |    |    |    |  |  |

• ST0: Channel 0 Stride

| 49.6.56 DMA Address 1 Register |            |    |    |    |    |    |    |  |  |

|--------------------------------|------------|----|----|----|----|----|----|--|--|

| Name:                          | ISC_DAD1   |    |    |    |    |    |    |  |  |

| Address:                       | 0xF00083F4 |    |    |    |    |    |    |  |  |

| Access:                        | Read/Write |    |    |    |    |    |    |  |  |

| 31                             | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |

|                                |            |    | AD | 01 |    |    |    |  |  |

| 23                             | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |

|                                |            |    | A  | )1 |    |    |    |  |  |

| 15                             | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |

| AD1                            |            |    |    |    |    |    |    |  |  |

| 7                              | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |

|                                |            |    | A  | D1 |    |    |    |  |  |

• AD1: Channel 1 Address

| 49.6.57 DN | IA Stride 1 Register |    |    |    |    |    |    |

|------------|----------------------|----|----|----|----|----|----|

| Name:      | ISC_DST1             |    |    |    |    |    |    |

| Address:   | 0xF00083F8           |    |    |    |    |    |    |

| Access:    | Read/Write           |    |    |    |    |    |    |

| 31         | 30                   | 29 | 28 | 27 | 26 | 25 | 24 |

|            |                      |    | ST | 1  |    |    |    |

| 23         | 22                   | 21 | 20 | 19 | 18 | 17 | 16 |

|            |                      |    | ST | 1  |    |    |    |

| 15         | 14                   | 13 | 12 | 11 | 10 | 9  | 8  |

|            |                      |    | ST | 1  |    |    |    |

| 7          | 6                    | 5  | 4  | 3  | 2  | 1  | 0  |

|            |                      |    | ST | 1  |    |    |    |

• ST1: Channel 1 Stride

| 49.6.58 DN | IA Address 2 Regis | ster |    |    |    |    |    |

|------------|--------------------|------|----|----|----|----|----|

| Name:      | ISC_DAD2           |      |    |    |    |    |    |

| Address:   | 0xF00083FC         |      |    |    |    |    |    |

| Access:    | Read/Write         |      |    |    |    |    |    |

| 31         | 30                 | 29   | 28 | 27 | 26 | 25 | 24 |

|            |                    |      | A  | 02 |    |    |    |

| 23         | 22                 | 21   | 20 | 19 | 18 | 17 | 16 |

|            |                    |      | A  | )2 |    |    |    |

| 15         | 14                 | 13   | 12 | 11 | 10 | 9  | 8  |

|            | AD2                |      |    |    |    |    |    |

| 7          | 6                  | 5    | 4  | 3  | 2  | 1  | 0  |

|            |                    |      | A  | 02 |    |    |    |

• AD2: Channel 2 Address

| 49.6.59 DN | MA Stride 2 Register |    |    |    |    |    |    |

|------------|----------------------|----|----|----|----|----|----|

| Name:      | ISC_DST2             |    |    |    |    |    |    |

| Address:   | 0xF0008400           |    |    |    |    |    |    |

| Access:    | Read/Write           |    |    |    |    |    |    |

| 31         | 30                   | 29 | 28 | 27 | 26 | 25 | 24 |

|            |                      |    | ST | 2  |    |    |    |

| 23         | 22                   | 21 | 20 | 19 | 18 | 17 | 16 |

|            |                      |    | ST | 2  |    |    |    |

| 15         | 14                   | 13 | 12 | 11 | 10 | 9  | 8  |

|            | ST2                  |    |    |    |    |    |    |

| 7          | 6                    | 5  | 4  | 3  | 2  | 1  | 0  |

|            |                      |    | ST | 2  |    |    |    |

• ST2: Channel 2 Stride

| 49.6.60 His | 49.6.60 Histogram Entry       |    |    |     |     |     |    |  |

|-------------|-------------------------------|----|----|-----|-----|-----|----|--|

| Name:       | Name: ISC_HIS_ENTRYx [x=0511] |    |    |     |     |     |    |  |

| Address:    | 0xF0008410                    |    |    |     |     |     |    |  |

| Access:     | Read/Write                    |    |    |     |     |     |    |  |

| 31          | 30                            | 29 | 28 | 27  | 26  | 25  | 24 |  |

| -           | -                             | _  | -  | -   | -   | -   | -  |  |

| 23          | 22                            | 21 | 20 | 19  | 18  | 17  | 16 |  |

| -           | -                             | —  | _  |     | COL | JNT |    |  |

| 15          | 14                            | 13 | 12 | 11  | 10  | 9   | 8  |  |

|             | COUNT                         |    |    |     |     |     |    |  |

| 7           | 6                             | 5  | 4  | 3   | 2   | 1   | 0  |  |

|             |                               |    | CO | UNT |     |     |    |  |

• COUNT: Entry Counter

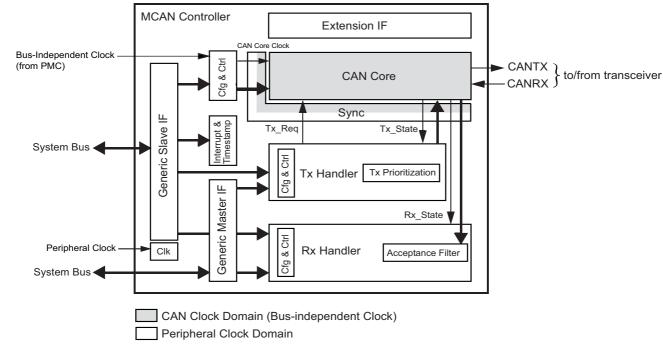

# 50. Controller Area Network (MCAN)

# 50.1 Description

The Controller Area Network (MCAN) performs communication according to ISO11898-1 (Bosch CAN specification 2.0 part A,B) and to Bosch CAN FD specification V1.0. Additional transceiver hardware is required for connection to the physical layer.

All functions concerning the handling of messages are implemented by the Rx Handler and the Tx Handler. The Rx Handler manages message acceptance filtering, the transfer of received messages from the CAN core to the Message RAM, as well as providing receive message status information. The Tx Handler is responsible for the transfer of transmit messages from the Message RAM to the CAN core, as well as providing transmit status information.

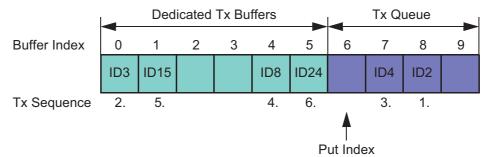

Acceptance filtering is implemented by a combination of up to 128 filter elements, where each element can be configured as a range, as a bit mask, or as a dedicated ID filter.

# 50.2 Embedded Characteristics

- Compliant with CAN Protocol Version 2.0 Part A, B and ISO 11898-1

- CAN FD with up to 64 Data Bytes Supported

- CAN Error Logging

- AUTOSAR Optimized

- SAE J1939 Optimized

- Improved Acceptance Filtering

- Two Configurable Receive FIFOs

- Separate Signalling on Reception of High Priority Messages

- Up to 64 Dedicated Receive Buffers

- Up to 32 Dedicated Transmit Buffers

- Configurable Transmit FIFO

- Configurable Transmit Queue

- Configurable Transmit Event FIFO

- Direct Message RAM Access for Processor

- Multiple MCANs May Share the Same Message RAM

- Programmable Loop-back Test Mode

- Maskable Module Interrupts

- Support for Asynchronous CAN and System Bus Clocks

- Power-down Support

- Debug on CAN Support

1977

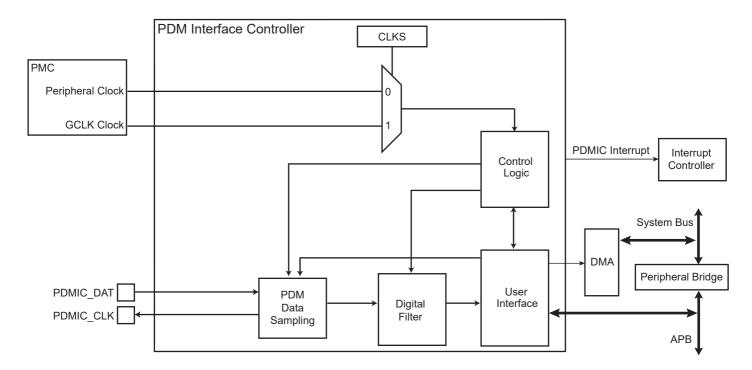

# 50.3 Block Diagram

Figure 50-1. MCAN Block Diagram

Note: Refer to section "Power Management Controller (PMC)" for details about the bus-independent clock (GCLK).

# 50.4 Product Dependencies

#### 50.4.1 I/O Lines

The pins used to interface to the compliant external devices can be multiplexed with PIO lines. The programmer must first program the PIO controllers to assign the CAN pins to their peripheral functions.

| Instance | Signal | I/O Line | Peripheral |

|----------|--------|----------|------------|

| MCAN0    | CANRX0 | PC2      | С          |

| MCAN0    | CANRX0 | PC11     | E          |

| MCAN0    | CANTX0 | PC1      | С          |

| MCAN0    | CANTX0 | PC10     | E          |

| MCAN1    | CANRX1 | PC27     | D          |

| MCAN1    | CANTX1 | PC26     | D          |

| Table 50-1. | I/O Lines |

|-------------|-----------|

|-------------|-----------|

#### 50.4.2 Power Management

The MCAN can be clocked through the Power Management Controller (PMC), thus the programmer must first configure the PMC to enable the MCAN clock.

In order to achieve a stable function of the MCAN, the system bus clock must always be faster than or equal to the CAN clock.

It is recommended to use the CAN clock at frequencies of 20, 40 or 80 MHz. To achieve these frequencies, PMC GCLK must select the UPLLCK (480 MHz) as source clock and divide by 24,12, or 6. GCLK allows the system bus and processor clock to be modified without affecting the bit rate communication.

#### 50.4.3 Interrupt Sources

The two MCAN interrupt lines (MCAN\_INT0, MCAN\_INT1) are connected on internal sources of the Interrupt Controller.

Using the MCAN interrupts requires the Interrupt Controller to be programmed first.

Interrupt sources can be routed either to MCAN\_INT0 or to MCAN\_INT1. By default, all interrupt sources are routed to interrupt line MCAN\_INT0/1. By programming MCAN\_ILE.EINT0 and MCAN\_ILE.EINT1, the interrupt sources can be enabled or disabled separately.

| Instance | ID |

|----------|----|

| MCAN0    | 56 |

| MCAN1    | 57 |

#### 50.4.4 Address Configuration

The LSBs [bits 15:2] for each section of the CAN Message RAM are configured in the respective buffer configuration registers.

The MSBs [bits 31:16] of the CAN Message RAM for CAN0 and CAN1 are configured in 0x00200000.

# 50.5 Functional Description

#### 50.5.1 Operating Modes

#### 50.5.1.1 Software Initialization

Software initialization is started by setting bit MCAN\_CCCR.INIT, either by software or by a hardware reset, when an uncorrected bit error was detected in the Message RAM, or by going Bus\_Off. While MCAN\_CCCR.INIT is set, message transfer from and to the CAN bus is stopped and the status of the CAN bus output CANTX is recessive (HIGH). The counters of the Error Management Logic EML are unchanged. Setting MCAN\_CCCR.INIT does not change any configuration register. Resetting MCAN\_CCCR.INIT finishes the software initialization. Afterwards the Bit Stream Processor BSP synchronizes itself to the data transfer on the CAN bus by waiting for the occurrence of a sequence of 11 consecutive recessive bits ( $\equiv$  Bus\_Idle) before it can take part in bus activities and start the message transfer.

Access to the MCAN configuration registers is only enabled when both bits MCAN\_CCCR.INIT and MCAN\_CCCR.CCE are set (protected write).

MCAN\_CCCR.CCE can only be configured when MCAN\_CCCR.INIT = '1'. MCAN\_CCCR.CCE is automatically cleared when MCAN\_CCCR.INIT = '0'.

The following registers are cleared when MCAN\_CCCR.CCE = '1':

- High Priority Message Status (MCAN\_HPMS)

- Receive FIFO 0 Status (MCAN\_RXF0S)

- Receive FIFO 1 Status (MCAN\_RXF1S)

- Transmit FIFO/Queue Status (MCAN\_TXFQS)

- Transmit Buffer Request Pending (MCAN\_TXBRP)

- Transmit Buffer Transmission Occurred (MCAN\_TXBTO)

- Transmit Buffer Cancellation Finished (MCAN\_TXBCF)

- Transmit Event FIFO Status (MCAN\_TXEFS)

The Timeout Counter value MCAN\_TOCV.TOC is loaded with the value configured by MCAN\_TOCC.TOP when MCAN\_CCCR.CCE = '1'.

In addition, the state machines of the Tx Handler and Rx Handler are held in idle state while MCAN\_CCCR.CCE = '1'.

The following registers are only writeable while MCAN\_CCCR.CCE = '0'

- Transmit Buffer Add Request (MCAN TXBAR)

- Transmit Buffer Cancellation Request (MCAN\_TXBCR)

MCAN\_CCCR.TEST and MCAN\_CCCR.MON can only be set when MCAN\_CCCR.INIT = '1' and MCAN\_CCCR.CCE = '1'. Both bits may be cleared at any time. MCAN\_CCCR.DAR can only be configured when MCAN\_CCCR.INIT = '1' and MCAN\_CCCR.CCE = '1'.

#### 50.5.1.2 Normal Operation

Once the MCAN is initialized and MCAN\_CCCR.INIT is cleared, the MCAN synchronizes itself to the CAN bus and is ready for communication.

After passing the acceptance filtering, received messages including Message ID and DLC are stored into a dedicated Rx Buffer or into Rx FIFO 0 or Rx FIFO 1.

For messages to be transmitted, dedicated Tx Buffers and/or a Tx FIFO or a Tx Queue can be initialized or updated. Automated transmission on reception of remote frames is not implemented.

#### 50.5.1.3 CAN FD Operation

There are two variants in the CAN FD frame format, first the CAN FD frame without bit rate switching where the data field of a CAN frame may be longer than 8 bytes. The second variant is the CAN FD frame where control field, data field, and CRC field of a CAN frame are transmitted with a higher bit rate than the beginning and the end of the frame.

The previously reserved bit in CAN frames with 11-bit identifiers and the first previously reserved bit in CAN frames with 29-bit identifiers will now be decoded as FDF bit. FDF = recessive signifies a CAN FD frame, FDF = dominant signifies a Classic CAN frame. In a CAN FD frame, the two bits following FDF, res and BRS, decide whether the bit rate inside of this CAN FD frame is switched. A CAN FD bit rate switch is signified by res = dominant and BRS = recessive. The coding of res = recessive is reserved for future expansion of the protocol. In case the MCAN receives a frame with FDF = recessive and res = recessive, it will signal a Protocol Exception Event by setting bit MCAN\_PSR.PXE. When Protocol Exception Handling is enabled (MCAN\_CCCR.PXHD = 0), this causes the operation state to change from Receiver (MCAN\_PSR.ACT = 2) to Integrating (MCAN\_PSR.ACT = 00) at the next sample point. In case Protocol Exception Handling is disabled (MCAN\_CCCR.PXHD = 1), the MCAN will treat a recessive res bit as an form error and will respond with an error frame.

CAN FD operation is enabled by programming CCCR.FDOE. In case CCCR.FDOE = '1', transmission and reception of CAN FD frames is enabled. Transmission and reception of Classic CAN frames is always possible. Whether a CAN FD frame or a Classic CAN frame is transmitted can be configured via bit FDF in the respective Tx Buffer element. With CCCR.FDOE = '0', received frames are interpreted as Classic CAN frames, which leads to the transmission of an error frame when receiving a CAN FD frame. When CAN FD operation is disabled, no CAN FD frames are transmitted even if bit FDF of a Tx Buffer element is set. CCCR.FDOE and CCCR.BRSE can only be changed while CCCR.INIT and CCCR.CCE are both set.

With MCAN\_CCCR.FDOE = 0, the setting of bits FDF and BRS is ignored and frames are transmitted in Classic CAN format. With MCAN\_CCCR.FDOE = 1 and MCAN\_CCCR.BRSE = 0, only bit FDF of a Tx Buffer element is evaluated. With MCAN\_CCCR.FDOE = 1 and MCAN\_CCCR.BRSE = 1, transmission of CAN FD frames with bit rate switching is enabled. All Tx Buffer elements with bits FDF and BRS set are transmitted in CAN FD format with bit rate switching.

A mode change during CAN operation is only recommended under the following conditions:

- The failure rate in the CAN FD data phase is significant higher than in the CAN FD arbitration phase. In this case disable the CAN FD bit rate switching option for transmissions.

- During system startup all nodes are transmitting according to ISO11898-1 until it is verified that they are able to communicate in CAN FD format. If this is true, all nodes switch to CAN FD operation.

- Wakeup messages in CAN Partial Networking have to be transmitted in Classic CAN format.

- End-of-line programming in case not all nodes are CAN FD-capable. Non-CAN FD nodes are held in Silent mode until programming has completed. Then all nodes revert to Classic CAN communication.

In the CAN FD format, the coding of the DLC differs from the standard CAN format. The DLC codes 0 to 8 have the same coding as in standard CAN, the codes 9 to 15, which in standard CAN all code a data field of 8 bytes, are coded according to Table 50-3 below.

#### Table 50-3. Coding of DLC in CAN FD

| DLC                  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|----------------------|----|----|----|----|----|----|----|

| Number of Data Bytes | 12 | 16 | 20 | 24 | 32 | 48 | 64 |

In CAN FD frames, the bit timing will be switched inside the frame, after the BRS (Bit Rate Switch) bit, if this bit is recessive. Before the BRS bit, in the CAN FD arbitration phase, the nominal CAN bit timing is used as defined by the Nominal Bit Timing and Prescaler register (MCAN\_NBTP). In the following CAN FD data phase, the fast CAN bit timing is used as defined by the Data Bit Timing and Prescaler register (MCAN\_DBTP). The bit timing reverts back from the fast timing at the CRC delimiter or when an error is detected, whichever occurs first.

The maximum configurable bit rate in the CAN FD data phase depends on the CAN core clock frequency. Example: with a CAN clock frequency of 20 MHz and the shortest configurable bit time of 4  $t_q$ , the bit rate in the data phase is 5 Mbit/s.

In both data frame formats, CAN FD and CAN FD with bit rate switching, the value of the bit ESI (Error Status Indicator) is determined by the transmitter's error state at the start of the transmission. If the transmitter is error passive, ESI is transmitted recessive, else it is transmitted dominant.

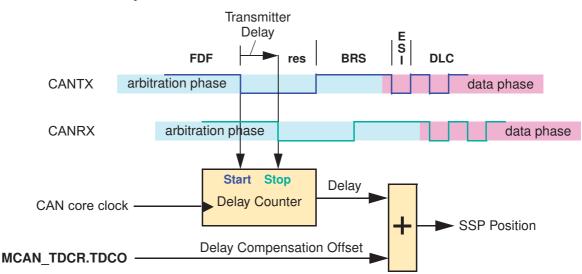

#### 50.5.1.4 Transmitter Delay Compensation

During the data phase of a CAN FD transmission only one node is transmitting, all others are receivers. The length of the bus line has no impact. When transmitting via pin CANTX the protocol controller receives the transmitted data from its local CAN transceiver via pin CANRX. The received data is delayed by the transmitter delay. In case this delay is greater than NTSEG1 (time segment before sample point), a bit error is detected. In order to enable a data phase bit time that is even shorter than the transmitter delay, the delay compensation is introduced. Without transmitter delay compensation, the bit rate in the data phase of a CAN FD frame is limited by the transmitter delay.

#### Description

The MCAN protocol unit has implemented a delay compensation mechanism to compensate the transmitter delay, thereby enabling transmission with higher bit rates during the CAN FD data phase independent of the delay of a specific CAN transceiver.

To check for bit errors during the data phase, the delayed transmit data is compared against the received data at the secondary sample point. If a bit error is detected, the transmitter will react to this bit error at the next following regular sample point. During arbitration phase the delay compensation is always disabled.

The transmitter delay compensation enables configurations where the data bit time is shorter than the transmitter delay, it is described in detail in the new ISO11898-1. It is enabled by setting bit MCAN\_DBTP.TDC.

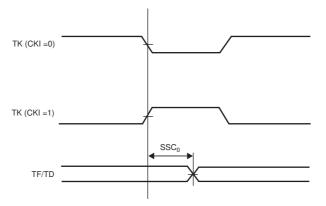

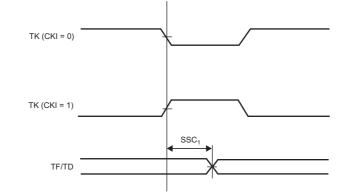

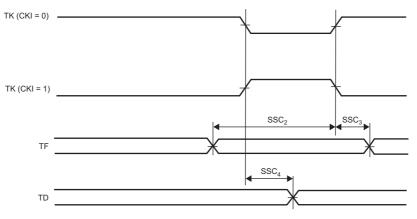

The received bit is compared against the transmitted bit at the SSP. The SSP position is defined as the sum of the measured delay from the MCAN's transmit output CANTX through the transceiver to the receive input CANRX plus the transmitter delay compensation offset as configured by MCAN\_TDCR.TDCO. The transmitter delay compensation offset is used to adjust the position of the SSP inside the received bit (e.g. half of the bit time in the data phase). The position of the secondary sample point is rounded down to the next integer number of CAN core clock periods.

MCAN\_PSR.TDCV shows the actual transmitter delay compensation value. MCAN\_PSR.TDCV is cleared when MCAN\_CCCR.INIT is set and is updated at each transmission of an FD frame while MCAN\_DBTP.TDC is set.

The following boundary conditions have to be considered for the transmitter delay compensation implemented in the MCAN:

- The sum of the measured delay from CANTX to CANRX and the configured transceiver delay compensation offset MCAN\_TDCR.TDCO has to be less than 6 bit times in the data phase.

- The sum of the measured delay from CANTX to CANRX and the configured transceiver delay compensation offset MCAN\_TDCR.TDCO has to be less or equal 127 CAN core clock periods. In case this sum exceeds 127 CAN core clock periods, the maximum value of 127 CAN core clock periods is used for transceiver delay compensation.

- The data phase ends at the sample point of the CRC delimiter, that stops checking of receive bits at the SSPs.

#### **Transmitter Delay Measurement**

If transmitter delay compensation is enabled by programming MCAN\_DBTP.TDC = '1', the measurement is started within each transmitted CAN FD frame at the falling edge of bit FDF to bit res. The measurement is stopped when this edge is seen at the receive input CANRX of the transmitter.

The resolution of this measurement is one mtq.

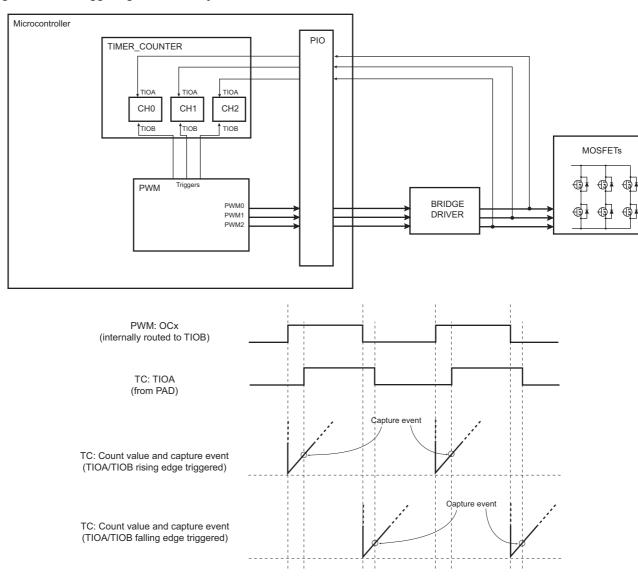

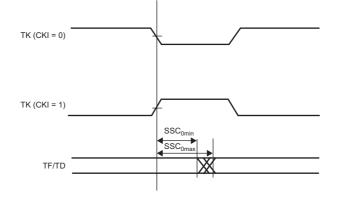

#### Figure 50-2. Transmitter Delay Measurement

To avoid that a dominant glitch inside the received FDF bit ends the delay compensation measurement before the falling edge of the received res bit, resulting in a to early SSP position, the use of a transmitter delay compensation filter window can be enabled by programming MCAN\_TDCR.TDCF.

This defines a minimum value for the SSP position. Dominant edges on CANRX, that would result in an earlier SSP position are ignored for transmitter delay measurement. The measurement is stopped when the SSP position is at least MCAN\_TDCR.TDCF AND CANRX is low.

#### 50.5.1.5 Restricted Operation Mode

In Restricted Operation mode, the node is able to receive data and remote frames and to give acknowledge to valid frames, but it does not send data frames, remote frames, active error frames, or overload frames. In case of an error condition or overload condition, it does not send dominant bits, instead it waits for the occurrence of bus idle condition to resynchronize itself to the CAN communication. The error counters are not incremented. The processor can set the MCAN into Restricted Operation mode by setting bit MCAN\_CCCR.ASM. The bit can only be set by the processor when both MCAN\_CCCR.CCE and MCAN\_CCCR.INIT are set to '1'. The bit can be reset by the processor at any time.

Restricted Operation mode is automatically entered when the Tx Handler was not able to read data from the Message RAM in time. To leave Restricted Operation mode, the processor has to reset MCAN\_CCCR.ASM.

The Restricted Operation mode can be used in applications that adapt themselves to different CAN bit rates. In this case the application tests different bit rates and leaves the Restricted Operation mode after it has received a valid frame.

Note: The Restricted Operation Mode must not be combined with the Loop Back mode (internal or external).

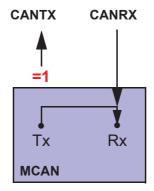

#### 50.5.1.6 Bus Monitoring Mode

The MCAN is set in Bus Monitoring mode by setting MCAN\_CCCR.MON. In Bus Monitoring mode (see ISO11898-1, 10.12 Bus monitoring), the MCAN is able to receive valid data frames and valid remote frames, but cannot start a transmission. In this mode, it sends only recessive bits on the CAN bus. If the MCAN is required to send a dominant bit (ACK bit, overload flag, active error flag), the bit is rerouted internally so that the MCAN monitors this dominant bit, although the CAN bus may remain in recessive state. In Bus Monitoring mode, the Tx Buffer Request Pending register (MCAN\_TXBRP) is held in reset state.

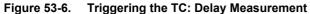

The Bus Monitoring mode can be used to analyze the traffic on a CAN bus without affecting it by the transmission of dominant bits. Figure 50-4 shows the connection of signals CANTX and CANRX to the MCAN in Bus Monitoring mode.

# Atmel

Figure 50-3. Pin Control in Bus Monitoring Mode

**Bus Monitoring Mode**

## 50.5.1.7 Disabled Automatic Retransmission

According to the CAN Specification (see ISO11898-1, 6.3.3 Recovery Management), the MCAN provides means for automatic retransmission of frames that have lost arbitration or that have been disturbed by errors during transmission. By default automatic retransmission is enabled. To support time-triggered communication as described in ISO 11898-1, chapter 9.2, the automatic retransmission may be disabled via MCAN CCCR.DAR.

#### Frame Transmission in DAR Mode

In DAR mode, all transmissions are automatically cancelled after they start on the CAN bus. A Tx Buffer's Tx Request Pending bit TXBRP.TRPx is reset after successful transmission, when a transmission has not yet been started at the point of cancellation, has been aborted due to lost arbitration, or when an error occurred during frame transmission.

- Successful transmission: Corresponding Tx Buffer Transmission Occurred bit MCAN\_TXBTO.TOx set Corresponding Tx Buffer Cancellation Finished bit MCAN\_TXBCF.CFx not set

- Successful transmission in spite of cancellation: Corresponding Tx Buffer Transmission Occurred bit MCAN\_TXBTO.TOx set Corresponding Tx Buffer Cancellation Finished bit MCAN\_TXBCF.CFx set

- Arbitration lost or frame transmission disturbed: Corresponding Tx Buffer Transmission Occurred bit MCAN\_TXBTO.TOx not set Corresponding Tx Buffer Cancellation Finished bit MCAN\_TXBCF.CFx set

In case of a successful frame transmission, and if storage of Tx events is enabled, a Tx Event FIFO element is written with Event Type ET = "10" (transmission in spite of cancellation).

#### 50.5.1.8 Power-down (Sleep Mode)

The MCAN can be set into Power-down mode via bit MCAN\_CCCR.CSR.

When all pending transmission requests have completed, the MCAN waits until bus idle state is detected. Then the MCAN sets MCAN\_CCCR.INIT to prevent any further CAN transfers. Now the MCAN acknowledges that it is ready for power down by setting to one the bit MCAN\_CCCR.CSA. In this state, before the clocks are switched off, further register accesses can be made. A write access to MCAN\_CCCR.INIT will have no effect. Now the bus clock (peripheral clock) and the CAN core clock may be switched off.

To leave Power-down mode, the application has to turn on the MCAN clocks before clearing CC Control Register flag MCAN\_CCCR.CSR. The MCAN will acknowledge this by clearing MCAN\_CCCR.CSA. The application can then restart CAN communication by clearing the bit CCCR.INIT.

#### 50.5.1.9 Test Modes

To enable write access to the MCAN Test register (MCAN\_TEST) (see Section 50.6.5), bit MCAN\_CCCR.TEST must be set. This allows the configuration of the test modes and test functions.

Four output functions are available for the CAN transmit pin CANTX by programming MCAN\_TEST.TX. Additionally to its default function – the serial data output – it can drive the CAN Sample Point signal to monitor the MCAN's bit timing and it can drive constant dominant or recessive values. The actual value at pin CANRX can be read from MCAN\_TEST.RX. Both functions can be used to check the CAN bus' physical layer.

Due to the synchronization mechanism between CAN clock and system bus clock domain, there may be a delay of several system bus clock periods between writing to MCAN\_TEST.TX until the new configuration is visible at output pin CANTX. This applies also when reading input pin CANRX via MCAN\_TEST.RX.

Note: Test modes should be used for production tests or self-test only. The software control for pin CANTX interferes with all CAN protocol functions. It is not recommended to use test modes for application.

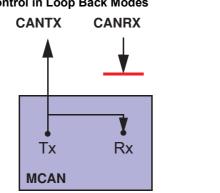

#### **External Loop Back Mode**

The MCAN can be set in External Loop Back mode by setting the bit MCAN\_TEST.LBCK. In Loop Back mode, the MCAN treats its own transmitted messages as received messages and stores them (if they pass acceptance filtering) into an Rx Buffer or an Rx FIFO. Figure 50-4 shows the connection of signals CANTX and CANRX to the MCAN in External Loop Back mode.

This mode is provided for hardware self-test. To be independent from external stimulation, the MCAN ignores acknowledge errors (recessive bit sampled in the acknowledge slot of a data/remote frame) in Loop Back mode. In this mode, the MCAN performs an internal feedback from its Tx output to its Rx input. The actual value of the CANRX input pin is disregarded by the MCAN. The transmitted messages can be monitored at the CANTX pin.

#### Internal Loop Back Mode

Internal Loop Back mode is entered by setting bits MCAN\_TEST.LBCK and MCAN\_CCCR.MON. This mode can be used for a "Hot Selftest", meaning the MCAN can be tested without affecting a running CAN system connected to the pins CANTX and CANRX. In this mode, pin CANRX is disconnected from the MCAN, and pin CANTX is held recessive. Figure 50-4 shows the connection of CANTX and CANRX to the MCAN when Internal Loop Back mode is enabled.

# Figure 50-4. Pin Control in Loop Back Modes

External Loop Back Mode

Internal Loop Back Mode

### 50.5.2 Timestamp Generation

For timestamp generation the MCAN supplies a 16-bit wrap-around counter. A prescaler TSCC.TCP can be configured to clock the counter in multiples of CAN bit times (1...16). The counter is readable via MCAN\_TSCV.TSC. A write access to the Timestamp Counter Value register (MCAN\_TSCV) resets the counter to zero. When the timestamp counter wraps around, interrupt flag MCAN\_IR.TSW is set.

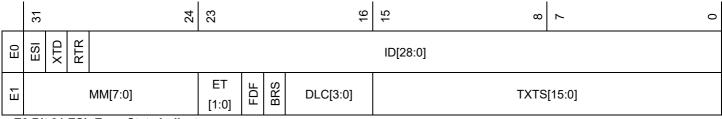

On start of frame reception / transmission the counter value is captured and stored into the timestamp section of an Rx Buffer / Rx FIFO (RXTS[15:0]) or Tx Event FIFO (TXTS[15:0]) element.

By programming bit MCAN\_TSCC.TSS an external 16-bit timestamp can be used.

#### 50.5.3 Timeout Counter

To signal timeout conditions for Rx FIFO 0, Rx FIFO 1, and the Tx Event FIFO, the MCAN supplies a 16-bit Timeout Counter. It operates as down-counter and uses the same prescaler controlled by TSCC.TCP as the Timestamp Counter. The Timeout Counter is configured via the Timeout Counter Configuration register (MCAN\_TOCC). The actual counter value can be read from MCAN\_TOCV.TOC. The Timeout Counter can only be started while MCAN\_CCCR.INIT = '0'. It is stopped when MCAN\_CCCR.INIT = '1', e.g. when the MCAN enters Bus\_Off state.

The operating mode is selected by MCAN\_TOCC.TOS. When operating in Continuous mode, the counter starts when MCAN\_CCCR.INIT is reset. A write to MCAN\_TOCV presets the counter to the value configured by MCAN\_TOCC.TOP and continues down-counting.

When the Timeout Counter is controlled by one of the FIFOs, an empty FIFO presets the counter to the value configured by MCAN\_TOCC.TOP. Down-counting is started when the first FIFO element is stored. Writing to MCAN\_TOCV has no effect.

When the counter reaches zero, interrupt flag MCAN\_IR.TOO is set. In Continuous mode, the counter is immediately restarted at MCAN\_TOCC.TOP.

Note: The clock signal for the Timeout Counter is derived from the CAN Core's sample point signal. Therefore the point in time where the Timeout Counter is decremented may vary due to the synchronization / re-synchronization mechanism of the CAN Core. If the bit rate switch feature in CAN FD is used, the timeout counter is clocked differently in arbitration and data field.

#### 50.5.4 Rx Handling

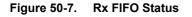

The Rx Handler controls the acceptance filtering, the transfer of received messages to the Rx Buffers or to one of the two Rx FIFOs, as well as the Rx FIFO's Put and Get Indices.

#### 50.5.4.1 Acceptance Filtering

The MCAN offers the possibility to configure two sets of acceptance filters, one for standard identifiers and one for extended identifiers. These filters can be assigned to an Rx Buffer or to Rx FIFO 0,1. For acceptance filtering each list of filters is executed from element #0 until the first matching element. Acceptance filtering stops at the first matching element. The following filter elements are not evaluated for this message.

The main features are:

- Each filter element can be configured as

- range filter (from to)

- filter for one or two dedicated IDs

- classic bit mask filter

- Each filter element is configurable for acceptance or rejection filtering

- Each filter element can be enabled / disabled individually

- Filters are checked sequentially, execution stops with the first matching filter element

Related configuration registers are:

- Global Filter Configuration (MCAN\_GFC)

- Standard ID Filter Configuration (MCAN\_SIDFC)

- Extended ID Filter Configuration (MCAN\_XIDFC)

- Extended ID and Mask (MCAN\_XIDAM)

Depending on the configuration of the filter element (SFEC/EFEC) a match triggers one of the following actions:

- Store received frame in FIFO 0 or FIFO 1

- Store received frame in Rx Buffer

- Store received frame in Rx Buffer and generate pulse at filter event pin

- Reject received frame

- Set High Priority Message interrupt flag (MCAN\_IR.HPM)

- Set High Priority Message interrupt flag (MCAN\_IR.HPM) and store received frame in FIFO 0 or FIFO 1

Acceptance filtering is started after the complete identifier has been received. After acceptance filtering has completed, and if a matching Rx Buffer or Rx FIFO has been found, the Message Handler starts writing the received message data in portions of 32 bit to the matching Rx Buffer or Rx FIFO. If the CAN protocol controller has detected an error condition (e.g. CRC error), this message is discarded with the following impact on the effected Rx Buffer or Rx FIFO:

Rx Buffer

New Data flag of matching Rx Buffer is not set, but Rx Buffer (partly) overwritten with received data. For error type, see MCAN\_PSR.LEC and MCAN\_PSR.DLEC.

• Rx FIFO

Put index of matching Rx FIFO is not updated, but related Rx FIFO element (partly) overwritten with received data. For error type, see MCAN\_PSR.LEC and MCAN\_PSR.DLEC. In case the matching Rx FIFO is operated in Overwrite mode, the boundary conditions described in "Rx FIFO Overwrite Mode" have to be considered.

Note: When an accepted message is written to one of the two Rx FIFOs, or into an Rx Buffer, the unmodified received identifier is stored independent of the filter(s) used. The result of the acceptance filter process is strongly depending on the sequence of configured filter elements.

#### **Range Filter**

The filter matches for all received frames with Message IDs in the range defined by SF1ID/SF2ID resp. EF1ID/EF2ID.

There are two possibilities when range filtering is used together with extended frames:

EFT = "00": The Message ID of received frames is ANDed with MCAN\_XIDAM before the range filter is applied.

EFT = "11": MCAN\_XIDAM is not used for range filtering.

#### **Filter for Specific IDs**

A filter element can be configured to filter for one or two specific Message IDs. To filter for one specific Message ID, the filter element has to be configured with SF1ID = SF2ID resp. EF1ID = EF2ID.

#### **Classic Bit Mask Filter**

Classic bit mask filtering is intended to filter groups of Message IDs by masking single bits of a received Message ID. With classic bit mask filtering SF1ID/EF1ID is used as Message ID filter, while SF2ID/EF2ID is used as filter mask.

A zero bit at the filter mask will mask out the corresponding bit position of the configured ID filter, e.g. the value of the received Message ID at that bit position is not relevant for acceptance filtering. Only those bits of the received Message ID where the corresponding mask bits are one are relevant for acceptance filtering.

In case all mask bits are one, a match occurs only when the received Message ID and the Message ID filter are identical. If all mask bits are zero, all Message IDs match.

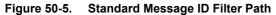

#### **Standard Message ID Filtering**

Figure 50-5 below shows the flow for standard Message ID (11-bit Identifier) filtering. The Standard Message ID Filter element is described in Section 50.5.7.5.

Controlled by MCAN\_GFC and MCAN\_SIDFC Message ID, Remote Transmission Request bit (RTR), and the Identifier Extension bit (IDE) of received frames are compared against the list of configured filter elements.

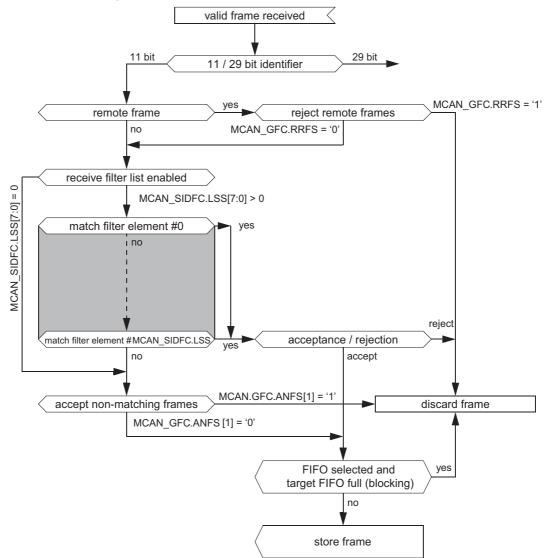

#### **Extended Message ID Filtering**

Figure 50-6 below shows the flow for extended Message ID (29-bit Identifier) filtering. The Extended Message ID Filter element is described in Section 50.5.7.6.

Controlled by MCAN\_GFC and MCAN\_XIDFC Message ID, Remote Transmission Request bit (RTR), and the Identifier Extension bit (IDE) of received frames are compared against the list of configured filter elements.

MCAN\_XIDAM is ANDed with the received identifier before the filter list is executed.

#### Figure 50-6. Extended Message ID Filter Path

# **Atmel**

#### 50.5.4.2 Rx FIFOs

Rx FIFO 0 and Rx FIFO 1 can be configured to hold up to 64 elements each. Configuration of the two Rx FIFOs is done via the Rx FIFO 0 Configuration register (MCAN\_RXF0C) and the Rx FIFO 1 Configuration register (MCAN\_RXF1C).

Received messages that passed acceptance filtering are transferred to the Rx FIFO as configured by the matching filter element. For a description of the filter mechanisms available for Rx FIFO 0 and Rx FIFO 1, see Section 50.5.4.1. The Rx FIFO element is described in Section 50.5.7.2.

To avoid an Rx FIFO overflow, the Rx FIFO watermark can be used. When the Rx FIFO fill level reaches the Rx FIFO watermark configured by MCAN\_RXFnC.FnWM, interrupt flag MCAN\_IR.RFnW is set. When the Rx FIFO Put Index reaches the Rx FIFO Get Index, an Rx FIFO Full condition is signalled by MCAN\_RXFnS.FnF. In addition, the interrupt flag MCAN\_IR.RFnF is set.

When reading from an Rx FIFO, Rx FIFO Get Index MCAN\_RXFnS.FnGI × FIFO Element Size has to be added to the corresponding Rx FIFO start address MCAN\_RXFnC.FnSA.

| Table 50-4. Rx Buffer / FIFO Eler |

|-----------------------------------|

|-----------------------------------|

| MCAN_RXESC.RBDS[2:0]<br>MCAN_RXESC.FnDS[2:0] | Data Field<br>[bytes] | FIFO Element Size<br>[RAM words] |

|----------------------------------------------|-----------------------|----------------------------------|

| 0                                            | 8                     | 4                                |

| 1                                            | 12                    | 5                                |

| 2                                            | 16                    | 6                                |

| 3                                            | 20                    | 7                                |

| 4                                            | 24                    | 8                                |

| 5                                            | 32                    | 10                               |

| 6                                            | 48                    | 14                               |

| 7                                            | 64                    | 18                               |

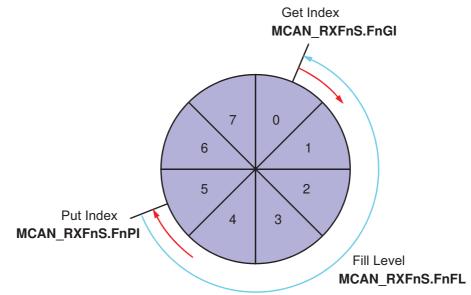

#### **Rx FIFO Blocking Mode**

The Rx FIFO Blocking mode is configured by MCAN\_RXFnC.FnOM = '0'. This is the default operating mode for the Rx FIFOs.

When an Rx FIFO full condition is reached (MCAN\_RXFnS.FnPI = MCAN\_RXFnS.FnGI), no further messages are written to the corresponding Rx FIFO until at least one message has been read out and the Rx FIFO Get Index has been incremented. An Rx FIFO full condition is signalled by MCAN\_RXFnS.FnF = '1'. In addition, the interrupt flag MCAN\_IR.RFnF is set.

In case a message is received while the corresponding Rx FIFO is full, this message is discarded and the message lost condition is signalled by MCAN\_RXFnS.RFnL = '1'. In addition, the interrupt flag MCAN\_IR.RFnL is set.

#### **Rx FIFO Overwrite Mode**

The Rx FIFO Overwrite mode is configured by MCAN\_RXFnC.FnOM = '1'.

When an Rx FIFO full condition (MCAN\_RXFnS.FnPI = MCAN\_RXFnS.FnGI) is signalled by MCAN\_RXFnS.FnF = '1', the next message accepted for the FIFO will overwrite the oldest FIFO message. Put and get index are both incremented by one.

When an Rx FIFO is operated in Overwrite mode and an Rx FIFO full condition is signalled, reading of the Rx FIFO elements should start at least at get index + 1. The reason for that is, that it might happen, that a received message is written to the Message RAM (put index) while the processor is reading from the Message RAM (get index). In this case inconsistent data may be read from the respective Rx FIFO element. Adding an offset to the get index when reading from the Rx FIFO avoids this problem. The offset depends on how fast the processor accesses the Rx FIFO. Figure 50-8 shows an offset of two with respect to the get index when reading the Rx FIFO. In this case the two messages stored in element 1 and 2 are lost.

After reading from the Rx FIFO, the number of the last element read has to be written to the Rx FIFO Acknowledge Index MCAN\_RXFnA.FnA. This increments the get index to that element number. In case the put index has not been incremented to this Rx FIFO element, the Rx FIFO full condition is reset (MCAN\_RXFnS.FnF = '0').

# Atmel

#### 50.5.4.3 Dedicated Rx Buffers

The MCAN supports up to 64 dedicated Rx Buffers. The start address of the dedicated Rx Buffer section is configured via MCAN\_RXBC.RBSA.

For each Rx Buffer, a Standard or Extended Message ID Filter Element with SFEC / EFEC = 7 and SFID2 / EFID2[10:9] = 0 has to be configured (see Section 50.5.7.5 and Section 50.5.7.6).

After a received message has been accepted by a filter element, the message is stored into the Rx Buffer in the Message RAM referenced by the filter element. The format is the same as for an Rx FIFO element. In addition, the flag MCAN\_IR.DRX (Message stored in dedicated Rx Buffer) in MCAN\_IR is set.

| Filter<br>Element | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |

|-------------------|----------------------------|----------------------------|--------------------------|

| 0                 | ID message 1               | 0                          | 0                        |

| 1                 | ID message 2               | 0                          | 1                        |

| 2                 | ID message 3               | 0                          | 2                        |

Table 50-5.

Example Filter Configuration for Rx Buffers

After the last word of a matching received message has been written to the Message RAM, the respective New Data flag in the New Data 1 register (MCAN\_NDAT1) and New Data 2 register (MCAN\_NDAT2) is set. As long as the New Data flag is set, the respective Rx Buffer is locked against updates from received matching frames. The New Data flags have to be reset by the processor by writing a '1' to the respective bit position.

While an Rx Buffer's New Data flag is set, a Message ID Filter Element referencing this specific Rx Buffer will not match, causing the acceptance filtering to continue. Following Message ID Filter Elements may cause the received message to be stored into another Rx Buffer, or into an Rx FIFO, or the message may be rejected, depending on filter configuration.

#### **Rx Buffer Handling**

- Reset interrupt flag IR.DRX

- Read New Data registers

- Read messages from Message RAM

- Reset New Data flags of processed messages

#### 50.5.4.4 Debug on CAN Support

Debug messages are stored into Rx Buffers. For debug handling three consecutive Rx buffers (e.g. #61, #62, #63) have to be used for storage of debug messages A, B, and C. The format is the same as for an Rx Buffer or an Rx FIFO element (see Section 50.5.7.2 "Rx Buffer and FIFO Element").

Advantage: Fixed start address for the DMA transfers (relative to MCAN\_RXBC.RBSA), no additional configuration required.

For filtering of debug messages Standard / Extended Filter Elements with SFEC / EFEC = '111' have to be set up. Messages matching these filter elements are stored into the Rx Buffers addressed by SFID2 / EFID2[5:0].

After message C has been stored, the DMA request output m\_can\_dma\_req is activated and the three messages can be read from the Message RAM under DMA control. The RAM words holding the debug messages will not be changed by the MCAN while m\_can\_dma\_req is activated. The behavior is similar to that of an Rx Buffer with its New Data flag set.

After the DMA has completed, the MCAN is prepared to receive the next set of debug messages.

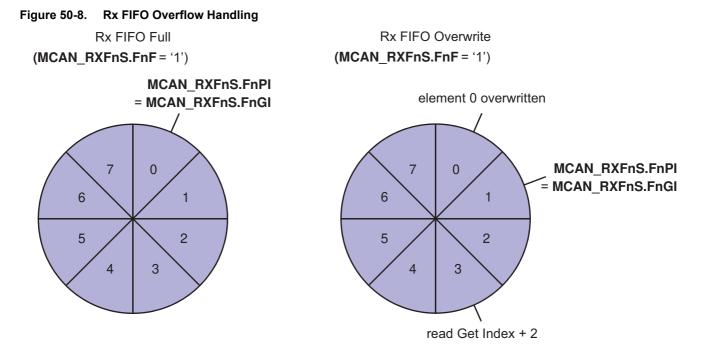

#### Filtering for Debug Messages

Filtering for debug messages is done by configuring one Standard / Extended Message ID Filter Element for each of the three debug messages. To enable a filter element to filter for debug messages SFEC / EFEC has to be

programmed to "111". In this case fields SFID1 / SFID2 and EFID1 / EFID2 have a different meaning (see Section 50.5.7.5 and Section 50.5.7.6). While SFID2 / EFID2[10:9] controls the debug message handling state machine, SFID2 / EFID2[5:0] controls the location for storage of a received debug message.

When a debug message is stored, neither the respective New Data flag nor MCAN\_IR.DRX are set. The reception of debug messages can be monitored via RXF1S.DMS.

|                   |                            | <b>J</b>                   |                          |

|-------------------|----------------------------|----------------------------|--------------------------|

| Filter<br>Element | SFID1[10:0]<br>EFID1[28:0] | SFID2[10:9]<br>EFID2[10:9] | SFID2[5:0]<br>EFID2[5:0] |

| 0                 | ID debug message A         | 1                          | 11 1101                  |

| 1                 | ID debug message B         | 2                          | 11 1110                  |

| 2                 | ID debug message C         | 3                          | 11 1111                  |

Table 50-6.

Example Filter Configuration for Debug Messages

#### **Debug Message Handling**

The debug message handling state machine ensures that debug messages are stored to three consecutive Rx Buffers in the correct order. If some messages are missing, the process is restarted. The DMA request is activated only when all three debug messages A, B, C have been received in the correct order.

The status of the debug message handling state machine is signalled via MCAN\_RXF1S.DMS.

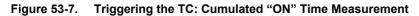

#### Figure 50-9. Debug Message Handling State Machine

- T0: reset m\_can\_dma\_req output, enable reception of debug messages A, B, and C

- T1: reception of debug message A

- T2: reception of debug message A

- T3: reception of debug message C

- T4: reception of debug message B

- T5: reception of debug messages A, B

- T6: reception of debug message C

- T7: DMA transfer completed

- T8: reception of debug message A,B,C (message rejected)

### 50.5.5 Tx Handling

The Tx Handler handles transmission requests for the dedicated Tx Buffers, the Tx FIFO, and the Tx Queue. It controls the transfer of transmit messages to the CAN Core, the Put and Get Indices, and the Tx Event FIFO. Up to 32 Tx Buffers can be set up for message transmission. The CAN mode for transmission (Classic CAN or CAN FD) can be configured separately for each Tx Buffer element. The Tx Buffer element is described in Section 50.5.7.3. Table 50-7 describes the possible configurations for frame transmission.

| MCAN    | MCAN_CCCR |         | r Element |                               |

|---------|-----------|---------|-----------|-------------------------------|

| BRSE    | FDOE      | FDF BRS |           | Frame Transmission            |

| ignored | 0         | ignored | ignored   | Classic CAN                   |

| 0       | 1         | 0       | ignored   | Classic CAN                   |

| 0       | 1         | 1       | ignored   | FD without bit rate switching |

| 1       | 1         | 0       | ignored   | Classic CAN                   |

| 1       | 1         | 1       | 0         | FD without bit rate switching |

| 1       | 1         | 1       | 1         | FD with bit rate switching    |

Table 50-7.

Possible Configurations for Frame Transmission

Note: AUTOSAR requires at least three Tx Queue Buffers and support of transmit cancellation.

The Tx Handler starts a Tx scan to check for the highest priority pending Tx request (Tx Buffer with lowest Message ID) when MCAN\_TXBRP is updated, or when a transmission has been started.

#### 50.5.5.1 Transmit Pause

The transmit pause feature is intended for use in CAN systems where the CAN message identifiers are (permanently) specified to specific values and cannot easily be changed. These message identifiers may have a higher CAN arbitration priority than other defined messages, while in a specific application their relative arbitration priority should be inverse. This may lead to a case where one ECU sends a burst of CAN messages that cause another ECU's CAN messages to be delayed because that other messages have a lower CAN arbitration priority.

If e.g. CAN ECU-1 has the transmit pause feature enabled and is requested by its application software to transmit four messages, it will, after the first successful message transmission, wait for two CAN bit times of bus idle before it is allowed to start the next requested message. If there are other ECUs with pending messages, those messages are started in the idle time, they would not need to arbitrate with the next message of ECU-1. After having received a message, ECU-1 is allowed to start its next transmission as soon as the received message releases the CAN bus.

The transmit pause feature is controlled by bit MCAN\_CCCR.TXP. If the bit is set, the MCAN will, each time it has successfully transmitted a message, pause for two CAN bit times before starting the next transmission. This enables other CAN nodes in the network to transmit messages even if their messages have lower prior identifiers. Default is transmit pause disabled (MCAN\_CCCR.TXP = '0').

This feature looses up burst transmissions coming from a single node and it protects against "babbling idiot" scenarios where the application program erroneously requests too many transmissions.

#### 50.5.5.2 Dedicated Tx Buffers

Dedicated Tx Buffers are intended for message transmission under complete control of the processor. Each dedicated Tx Buffer is configured with a specific Message ID. In case that multiple Tx Buffers are configured with the same Message ID, the Tx Buffer with the lowest buffer number is transmitted first.

If the data section has been updated, a transmission is requested by an Add Request via MCAN\_TXBAR.ARn. The requested messages arbitrate internally with messages from an optional Tx FIFO or Tx Queue and externally with messages on the CAN bus, and are sent out according to their Message ID.

A dedicated Tx Buffer allocates Element Size 32-bit words in the Message RAM (see Table 50-8). Therefore the start address of a dedicated Tx Buffer in the Message RAM is calculated by adding transmit buffer index  $(0...31) \times$  Element Size to the Tx Buffer Start Address TXBC.TBSA.

| TXESC.TBDS[2:0] | Data Field<br>[bytes] | Element Size<br>[RAM words] |

|-----------------|-----------------------|-----------------------------|

| 0               | 8                     | 4                           |

| 1               | 12                    | 5                           |

| 2               | 16                    | 6                           |

| 3               | 20                    | 7                           |

| 4               | 24                    | 8                           |

| 5               | 32                    | 10                          |

| 6               | 48                    | 14                          |

| 7               | 64                    | 18                          |

#### 50.5.5.3 Tx FIFO

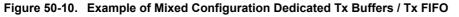

Tx FIFO operation is configured by programming MCAN\_TXBC.TFQM to '0'. Messages stored in the Tx FIFO are transmitted starting with the message referenced by the Get Index MCAN\_TXFQS.TFGI. After each transmission the Get Index is incremented cyclically until the Tx FIFO is empty. The Tx FIFO enables transmission of messages with the same Message ID from different Tx Buffers in the order these messages have been written to the Tx FIFO. The MCAN calculates the Tx FIFO Free Level MCAN\_TXFQS.TFFL as difference between Get and Put Index. It indicates the number of available (free) Tx FIFO elements.

New transmit messages have to be written to the Tx FIFO starting with the Tx Buffer referenced by the Put Index MCAN\_TXFQS.TFQPI. An Add Request increments the Put Index to the next free Tx FIFO element. When the Put Index reaches the Get Index, Tx FIFO Full (MCAN\_TXFQS.TFQF = '1') is signalled. In this case no further messages should be written to the Tx FIFO until the next message has been transmitted and the Get Index has been incremented.

When a single message is added to the Tx FIFO, the transmission is requested by writing a '1' to the TXBAR bit related to the Tx Buffer referenced by the Tx FIFO's Put Index.

When multiple (n) messages are added to the Tx FIFO, they are written to n consecutive Tx Buffers starting with the Put Index. The transmissions are then requested via MCAN\_TXBAR. The Put Index is then cyclically incremented by n. The number of requested Tx buffers should not exceed the number of free Tx Buffers as indicated by the Tx FIFO Free Level.

When a transmission request for the Tx Buffer referenced by the Get Index is cancelled, the Get Index is incremented to the next Tx Buffer with pending transmission request and the Tx FIFO Free Level is recalculated. When transmission cancellation is applied to any other Tx Buffer, the Get Index and the FIFO Free Level remain unchanged.

A Tx FIFO element allocates Element Size 32-bit words in the Message RAM (see Table 50-8). Therefore the start address of the next available (free) Tx FIFO Buffer is calculated by adding Tx FIFO/Queue Put Index MCAN\_TXFQS.TFQPI (0...31) × Element Size to the Tx Buffer Start Address MCAN\_TXBC.TBSA.

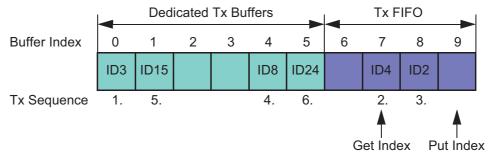

#### 50.5.5.4 Tx Queue

Tx Queue operation is configured by programming MCAN\_TXBC.TFQM to '1'. Messages stored in the Tx Queue are transmitted starting with the message with the lowest Message ID (highest priority). In case that multiple Queue Buffers are configured with the same Message ID, the Queue Buffer with the lowest buffer number is transmitted first.

New messages have to be written to the Tx Buffer referenced by the Put Index MCAN\_TXFQS.TFQPI. An Add Request cyclically increments the Put Index to the next free Tx Buffer. In case that the Tx Queue is full (MCAN\_TXFQS.TFQF = '1'), the Put Index is not valid and no further message should be written to the Tx Queue until at least one of the requested messages has been sent out or a pending transmission request has been cancelled.

The application may use register MCAN\_TXBRP instead of the Put Index and may place messages to any Tx Buffer without pending transmission request.