#### 42.9.6 SSC Transmit Frame Mode Register Name: SSC TFMR Address: 0xF800401C (0), 0xFC00401C (1) Access: Read/Write 31 30 29 28 27 26 25 24 FSLEN EXT FSEDGE 23 22 21 20 19 18 17 16 FSDEN FSOS **FSLEN** 15 14 10 9 8 13 12 11 DATNB \_ \_ 7 6 5 4 3 2 0 1 MSBF DATDEF DATLEN \_

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

# • DATLEN: Data Length

0: Forbidden value (1-bit data length not supported).

Any other value: The bit stream contains DATLEN + 1 data bits.

# • DATDEF: Data Default Value

This bit defines the level driven on the TD pin while out of transmission. Note that if the pin is defined as multidrive by the PIO Controller, the pin is enabled only if the SCC TD output is 1.

# MSBF: Most Significant Bit First

0: The lowest significant bit of the data register is shifted out first in the bit stream.

1: The most significant bit of the data register is shifted out first in the bit stream.

# DATNB: Data Number per Frame

This field defines the number of data words to be transferred after each transfer start, which is equal to (DATNB + 1).

# • FSLEN: Transmit Frame Sync Length

This field defines the length of the Transmit Frame Sync signal and the number of bits shifted out from the Transmit Sync Data Register if FSDEN is 1.

This field is used with FSLEN\_EXT to determine the pulse length of the Transmit Frame Sync signal.

Pulse length is equal to FSLEN + (FSLEN\_EXT  $\times$  16) + 1 Transmit Clock period.

# • FSOS: Transmit Frame Sync Output Selection

| Value | Name     | Description                             |

|-------|----------|-----------------------------------------|

| 0     | NONE     | None, TF pin is an input                |

| 1     | NEGATIVE | Negative Pulse, TF pin is an output     |

| 2     | POSITIVE | Positive Pulse, TF pin is an output     |

| 3     | LOW      | Driven Low during data transfer         |

| 4     | HIGH     | Driven High during data transfer        |

| 5     | TOGGLING | Toggling at each start of data transfer |

# • FSDEN: Frame Sync Data Enable

0: The TD line is driven with the default value during the Transmit Frame Sync signal.

1: SSC\_TSHR value is shifted out during the transmission of the Transmit Frame Sync signal.

# • FSEDGE: Frame Sync Edge Detection

Determines which edge on frame sync will generate the interrupt TXSYN (Status Register).

| Value | N | lame     | Description             |

|-------|---|----------|-------------------------|

| 0     | P | OSITIVE  | Positive Edge Detection |

| 1     | Ν | IEGATIVE | Negative Edge Detection |

# • FSLEN\_EXT: FSLEN Field Extension

Extends FSLEN field. For details, refer to FSLEN bit description above.

# 42.9.7 SSC Receive Holding Register

| Name:<br>Address: | SSC_RHR<br>0xF8004020 (0) | , 0xFC004020 ( | 1) |    |    |    |    |  |  |

|-------------------|---------------------------|----------------|----|----|----|----|----|--|--|

| Access:           | Read-only                 |                |    |    |    |    |    |  |  |

| 31                | 30                        | 29             | 28 | 27 | 26 | 25 | 24 |  |  |

|                   | RDAT                      |                |    |    |    |    |    |  |  |

| 23                | 22                        | 21             | 20 | 19 | 18 | 17 | 16 |  |  |

|                   |                           |                | RD | AT |    |    |    |  |  |

| 15                | 14                        | 13             | 12 | 11 | 10 | 9  | 8  |  |  |

|                   |                           |                | RD | AT |    |    |    |  |  |

| 7                 | 6                         | 5              | 4  | 3  | 2  | 1  | 0  |  |  |

|                   |                           |                | RD | AI |    |    |    |  |  |

# • RDAT: Receive Data

Right aligned regardless of the number of data bits defined by DATLEN in SSC\_RFMR.

| 42.9.8 SS | SC Transmit Holdi              | ng Register |    |    |    |    |    |  |  |  |

|-----------|--------------------------------|-------------|----|----|----|----|----|--|--|--|

| Name:     | SSC_THR                        |             |    |    |    |    |    |  |  |  |

| Address:  | 0xF8004024 (0), 0xFC004024 (1) |             |    |    |    |    |    |  |  |  |

| Access:   | Write-only                     |             |    |    |    |    |    |  |  |  |

| 31        | 30                             | 29          | 28 | 27 | 26 | 25 | 24 |  |  |  |

|           | TDAT                           |             |    |    |    |    |    |  |  |  |

| 23        | 22                             | 21          | 20 | 19 | 18 | 17 | 16 |  |  |  |

|           |                                |             | TD | AT |    |    |    |  |  |  |

| 15        | 14                             | 13          | 12 | 11 | 10 | 9  | 8  |  |  |  |

|           |                                |             | TD | AT |    |    |    |  |  |  |

| 7         | 6                              | 5           | 4  | 3  | 2  | 1  | 0  |  |  |  |

|           |                                |             | TD | AT |    |    |    |  |  |  |

# • TDAT: Transmit Data

Right aligned regardless of the number of data bits defined by DATLEN in SSC\_TFMR.

| 42.9.9 SSC Receive Synchronization Holding Register |                |                                |          |          |    |    |    |  |  |  |

|-----------------------------------------------------|----------------|--------------------------------|----------|----------|----|----|----|--|--|--|

| Name:                                               | SSC_RSHR       | SSC_RSHR                       |          |          |    |    |    |  |  |  |

| Address:                                            | 0xF8004030 (0) | 0xF8004030 (0), 0xFC004030 (1) |          |          |    |    |    |  |  |  |

| Access:                                             | Read-only      |                                |          |          |    |    |    |  |  |  |

| 31                                                  | 30             | 29                             | 28       | 27       | 26 | 25 | 24 |  |  |  |

| _                                                   | -              | —                              | _        | -        | -  | —  | -  |  |  |  |

| 23                                                  | 22             | 21                             | 20       | 19       | 18 | 17 | 16 |  |  |  |

| —                                                   | -              | _                              | _        | -        | -  | _  | —  |  |  |  |

| 15                                                  | 14             | 13                             | 12       | 11       | 10 | 9  | 8  |  |  |  |

|                                                     |                |                                | RSI      | DAT      |    |    |    |  |  |  |

| 7                                                   | 6              | 5                              | 4<br>RSI | 3<br>DAT | 2  | 1  | 0  |  |  |  |

RSDAT: Receive Synchronization Data

| 42.9.10 SS | 42.9.10 SSC Transmit Synchronization Holding Register |                                |     |          |    |    |    |  |  |  |

|------------|-------------------------------------------------------|--------------------------------|-----|----------|----|----|----|--|--|--|

| Name:      | SSC_TSHR                                              | SSC_TSHR                       |     |          |    |    |    |  |  |  |

| Address:   | 0xF8004034 (0)                                        | 0xF8004034 (0), 0xFC004034 (1) |     |          |    |    |    |  |  |  |

| Access:    | Read/Write                                            |                                |     |          |    |    |    |  |  |  |

| 31         | 30                                                    | 29                             | 28  | 27       | 26 | 25 | 24 |  |  |  |

| -          | -                                                     | -                              | -   | -        | -  | -  | -  |  |  |  |

| 23         | 22                                                    | 21                             | 20  | 19       | 18 | 17 | 16 |  |  |  |

| -          | -                                                     | _                              | _   | _        | -  | _  | -  |  |  |  |

| 15         | 14                                                    | 13                             | 12  | 11       | 10 | 9  | 8  |  |  |  |

|            |                                                       |                                | TSI | DAT      |    |    |    |  |  |  |

| 7          | 6                                                     | 5                              | 4   | 3<br>DAT | 2  | 1  | 0  |  |  |  |

|            |                                                       |                                | 151 | JAI      |    |    |    |  |  |  |

• TSDAT: Transmit Synchronization Data

| 42.9.11 SS | C Receive Comp | are 0 Register                 |        |    |    |    |    |  |  |  |  |

|------------|----------------|--------------------------------|--------|----|----|----|----|--|--|--|--|

| Name:      | SSC_RC0R       | SSC_RCOR                       |        |    |    |    |    |  |  |  |  |

| Address:   | 0xF8004038 (0) | 0xF8004038 (0), 0xFC004038 (1) |        |    |    |    |    |  |  |  |  |

| Access:    | Read/Write     |                                |        |    |    |    |    |  |  |  |  |

| 31         | 30             | 29                             | 28     | 27 | 26 | 25 | 24 |  |  |  |  |

| _          | -              | —                              | —      | —  | —  | -  | —  |  |  |  |  |

| 23         | 22             | 21                             | 20     | 19 | 18 | 17 | 16 |  |  |  |  |

| _          | -              | -                              | -      | _  | -  | _  | -  |  |  |  |  |

| 15         | 14             | 13                             | 12     | 11 | 10 | 9  | 8  |  |  |  |  |

|            |                |                                | C      | >0 |    |    |    |  |  |  |  |

| 7          | 6              | 5                              | 4<br>C | 3  | 2  | 1  | 0  |  |  |  |  |

|            |                |                                | C      | U  |    |    |    |  |  |  |  |

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

• CP0: Receive Compare Data 0

#### 42.9.12 SSC Receive Compare 1 Register Name: SSC\_RC1R Address: 0xF800403C (0), 0xFC00403C (1) Access: Read/Write 31 30 29 27 24 28 26 25 \_ \_ \_ \_ \_ \_ --23 22 21 20 19 18 17 16 \_ \_ \_ \_ \_ \_ \_ \_ 15 14 13 12 11 10 9 8 CP1 7 6 5 4 3 2 1 0 CP1

This register can only be written if the WPEN bit is cleared in the SSC Write Protection Mode Register.

• CP1: Receive Compare Data 1

# 42.9.13 SSC Status Register

| Name:<br>Address: | SSC_SR<br>0xF8004040 (0) | , 0xFC004040 ( | (1)   |       |       |         |       |

|-------------------|--------------------------|----------------|-------|-------|-------|---------|-------|

| Access:           | Read-only                |                |       |       |       |         |       |

| 31                | 30                       | 29             | 28    | 27    | 26    | 25      | 24    |

| _                 | -                        | -              | -     | -     | -     | -       | _     |

| 23                | 22                       | 21             | 20    | 19    | 18    | 17      | 16    |

| -                 | -                        | -              | -     | -     | -     | RXEN    | TXEN  |

| 15                | 14                       | 13             | 12    | 11    | 10    | 9       | 8     |

| _                 | -                        | —              | -     | RXSYN | TXSYN | CP1     | CP0   |

| 7                 | 6                        | 5              | 4     | 3     | 2     | 1       | 0     |

| -                 | -                        | OVRUN          | RXRDY | _     | _     | TXEMPTY | TXRDY |

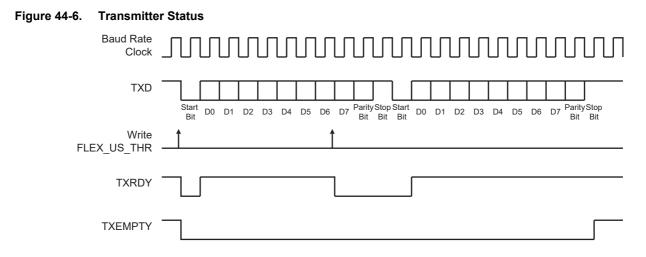

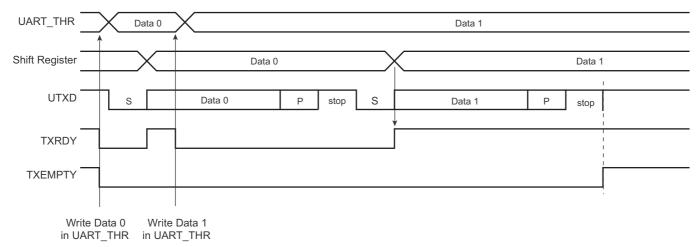

# • TXRDY: Transmit Ready

0: Data has been loaded in SSC\_THR and is waiting to be loaded in the transmit shift register (TSR).

1: SSC\_THR is empty.

# • TXEMPTY: Transmit Empty

0: Data remains in SSC\_THR or is currently transmitted from TSR.

1: Last data written in SSC\_THR has been loaded in TSR and last data loaded in TSR has been transmitted.

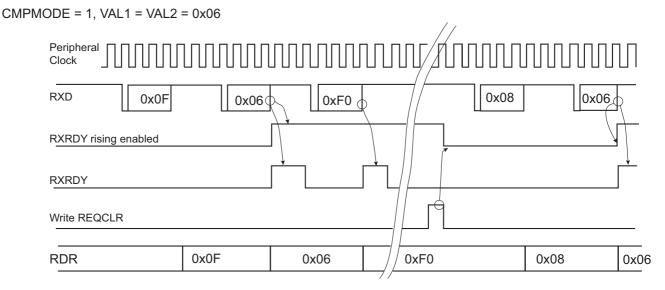

### • RXRDY: Receive Ready

0: SSC\_RHR is empty.

1: Data has been received and loaded in SSC\_RHR.

### OVRUN: Receive Overrun

0: No data has been loaded in SSC\_RHR while previous data has not been read since the last read of the Status Register. 1: Data has been loaded in SSC\_RHR while previous data has not yet been read since the last read of the Status Register.

### • CP0: Compare 0

0: A compare 0 has not occurred since the last read of the Status Register.

1: A compare 0 has occurred since the last read of the Status Register.

### CP1: Compare 1

0: A compare 1 has not occurred since the last read of the Status Register.

1: A compare 1 has occurred since the last read of the Status Register.

# • TXSYN: Transmit Sync

0: A Tx Sync has not occurred since the last read of the Status Register.

1: A Tx Sync has occurred since the last read of the Status Register.

# • RXSYN: Receive Sync

0: An Rx Sync has not occurred since the last read of the Status Register.

1: An Rx Sync has occurred since the last read of the Status Register.

# • TXEN: Transmit Enable

- 0: Transmit is disabled.

- 1: Transmit is enabled.

# • RXEN: Receive Enable

- 0: Receive is disabled.

- 1: Receive is enabled.

# 42.9.14 SSC Interrupt Enable Register

| Name:<br>Address: | SSC_IER<br>0xF8004044 (0) | , 0xFC004044 ( | 1)    |       |       |         |       |

|-------------------|---------------------------|----------------|-------|-------|-------|---------|-------|

| Access:           | Write-only                |                |       |       |       |         |       |

| 31                | 30                        | 29             | 28    | 27    | 26    | 25      | 24    |

| _                 | -                         | _              | -     | -     | -     | -       | -     |

| 23                | 22                        | 21             | 20    | 19    | 18    | 17      | 16    |

| _                 | -                         | _              | -     | -     | -     | -       | -     |

| 15                | 14                        | 13             | 12    | 11    | 10    | 9       | 8     |

| _                 | —                         | —              | —     | RXSYN | TXSYN | CP1     | CP0   |

| 7                 | 6                         | 5              | 4     | 3     | 2     | 1       | 0     |

| -                 | -                         | OVRUN          | RXRDY | -     | -     | TXEMPTY | TXRDY |

# • TXRDY: Transmit Ready Interrupt Enable

0: No effect.

1: Enables the Transmit Ready Interrupt.

# • TXEMPTY: Transmit Empty Interrupt Enable

- 0: No effect.

- 1: Enables the Transmit Empty Interrupt.

# • RXRDY: Receive Ready Interrupt Enable

- 0: No effect.

- 1: Enables the Receive Ready Interrupt.

# • OVRUN: Receive Overrun Interrupt Enable

0: No effect.

1: Enables the Receive Overrun Interrupt.

# • CP0: Compare 0 Interrupt Enable

- 0: No effect.

- 1: Enables the Compare 0 Interrupt.

# • CP1: Compare 1 Interrupt Enable

0: No effect.

1: Enables the Compare 1 Interrupt.

# • TXSYN: Tx Sync Interrupt Enable

0: No effect.

1: Enables the Tx Sync Interrupt.

# • RXSYN: Rx Sync Interrupt Enable

0: No effect.

1: Enables the Rx Sync Interrupt.

# 42.9.15 SSC Interrupt Disable Register

| Name:<br>Address: | SSC_IDR<br>0xF8004048 (0) | . 0xFC004048 ( | (1)   |             |             |          |          |

|-------------------|---------------------------|----------------|-------|-------------|-------------|----------|----------|

| Access:           | Write-only                | ,              |       |             |             |          |          |

| 31                | 30                        | 29             | 28    | 27          | 26          | 25       | 24       |

| _                 | -                         | _              | _     | _           | _           | _        | _        |

| 23                | 22                        | 21             | 20    | 19          | 18          | 17       | 16       |

| 15                | 14                        | 13             | 12    | 11<br>RXSYN | 10<br>TXSYN | 9<br>CP1 | 8<br>CP0 |

| 7                 | 6                         | 5              | 4     | 3           | 2           | 1        | 0        |

| -                 | -                         | OVRUN          | RXRDY | _           | _           | TXEMPTY  | TXRDY    |

# • TXRDY: Transmit Ready Interrupt Disable

0: No effect.

1: Disables the Transmit Ready Interrupt.

# • TXEMPTY: Transmit Empty Interrupt Disable

- 0: No effect.

- 1: Disables the Transmit Empty Interrupt.

# • RXRDY: Receive Ready Interrupt Disable

- 0: No effect.

- 1: Disables the Receive Ready Interrupt.

# • OVRUN: Receive Overrun Interrupt Disable

0: No effect.

1: Disables the Receive Overrun Interrupt.

# CP0: Compare 0 Interrupt Disable

0: No effect.

1: Disables the Compare 0 Interrupt.

# • CP1: Compare 1 Interrupt Disable

0: No effect.

1: Disables the Compare 1 Interrupt.

# • TXSYN: Tx Sync Interrupt Enable

0: No effect.

1: Disables the Tx Sync Interrupt.

# • RXSYN: Rx Sync Interrupt Enable

0: No effect.

1: Disables the Rx Sync Interrupt.

# 42.9.16 SSC Interrupt Mask Register

| Name:<br>Address: | SSC_IMR<br>0xF800404C (0) | , 0xFC00404C | (1)   |       |       |         |       |

|-------------------|---------------------------|--------------|-------|-------|-------|---------|-------|

| Access:           | Read-only                 |              |       |       |       |         |       |

| 31                | 30                        | 29           | 28    | 27    | 26    | 25      | 24    |

| _                 | -                         | _            | -     | -     | -     | -       | _     |

| 23                | 22                        | 21           | 20    | 19    | 18    | 17      | 16    |

| _                 | -                         | _            | -     | _     | _     | -       | _     |

| 15                | 14                        | 13           | 12    | 11    | 10    | 9       | 8     |

| —                 | -                         | Ι            | -     | RXSYN | TXSYN | CP1     | CP0   |

| 7                 | 6                         | 5            | 4     | 3     | 2     | 1       | 0     |

| _                 | -                         | OVRUN        | RXRDY | —     | _     | TXEMPTY | TXRDY |

# • TXRDY: Transmit Ready Interrupt Mask

0: The Transmit Ready Interrupt is disabled.

1: The Transmit Ready Interrupt is enabled.

# • TXEMPTY: Transmit Empty Interrupt Mask

0: The Transmit Empty Interrupt is disabled.

1: The Transmit Empty Interrupt is enabled.

### RXRDY: Receive Ready Interrupt Mask

0: The Receive Ready Interrupt is disabled.

1: The Receive Ready Interrupt is enabled.

### OVRUN: Receive Overrun Interrupt Mask

0: The Receive Overrun Interrupt is disabled.

1: The Receive Overrun Interrupt is enabled.

# • CP0: Compare 0 Interrupt Mask

0: The Compare 0 Interrupt is disabled.

1: The Compare 0 Interrupt is enabled.

### • CP1: Compare 1 Interrupt Mask

# 0: The Compare 1 Interrupt is disabled.

1: The Compare 1 Interrupt is enabled.

# • TXSYN: Tx Sync Interrupt Mask

0: The Tx Sync Interrupt is disabled.

1: The Tx Sync Interrupt is enabled.

- RXSYN: Rx Sync Interrupt Mask

- 0: The Rx Sync Interrupt is disabled.

- 1: The Rx Sync Interrupt is enabled.

# 42.9.17 SSC Write Protection Mode Register

| Name:    | SSC_WPMR       |              |     |     |    |    |      |

|----------|----------------|--------------|-----|-----|----|----|------|

| Address: | 0xF80040E4 (0) | , 0xFC0040E4 | (1) |     |    |    |      |

| Access:  | Read/Write     |              |     |     |    |    |      |

| 31       | 30             | 29           | 28  | 27  | 26 | 25 | 24   |

|          |                |              | WP  | KEY |    |    |      |

| 23       | 22             | 21           | 20  | 19  | 18 | 17 | 16   |

|          |                |              | WP  | KEY |    |    |      |

| 15       | 14             | 13           | 12  | 11  | 10 | 9  | 8    |

|          |                |              | WP  | KEY |    |    |      |

| 7        | 6              | 5            | 4   | 3   | 2  | 1  | 0    |

| _        | -              | _            | _   | _   | _  | _  | WPEN |

# • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x535343 ("SSC" in ASCII).

1: Enables the write protection if WPKEY corresponds to 0x535343 ("SSC" in ASCII).

See Section 42.8.10 "Register Write Protection" for the list of registers that can be protected.

### • WPKEY: Write Protection Key

| Value    | Name   | Description                                                                       |

|----------|--------|-----------------------------------------------------------------------------------|

| 0x535343 | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

|          |        | Always reads as 0.                                                                |

#### 42.9.18 SSC Write Protection Status Register Name: SSC\_WPSR Address: 0xF80040E8 (0), 0xFC0040E8 (1) Access: Read-only 31 30 29 28 27 26 25 24 \_ \_ \_ \_ \_ \_ \_ \_ 23 22 21 20 19 18 17 16 WPVSRC 10 15 14 13 12 9 8 11 WPVSRC 7 2 0 6 5 4 3 1 \_ WPVS \_ \_ \_ \_ \_ \_

# • WPVS: Write Protection Violation Status

0: No write protection violation has occurred since the last read of the SSC\_WPSR.

1: A write protection violation has occurred since the last read of the SSC\_WPSR. If this violation is an unauthorized attempt to write a protected register, the associated violation is reported into field WPVSRC.

# WPVSRC: Write Protect Violation Source

When WPVS = 1, WPVSRC indicates the register address offset at which a write access has been attempted.

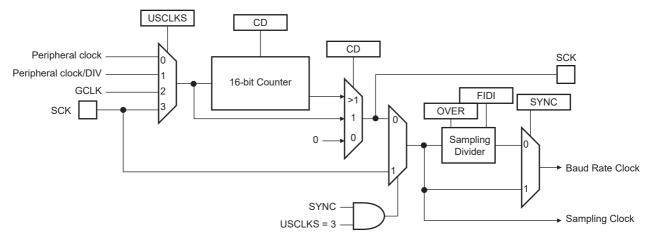

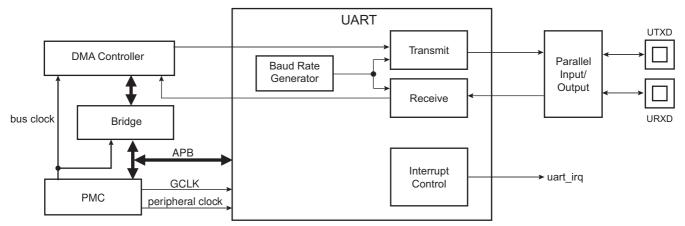

# 43. Two-wire Interface (TWIHS)

# 43.1 Description

The Atmel Two-wire Interface (TWIHS) interconnects components on a unique two-wire bus, made up of one clock line and one data line with speeds of up to 400 kbit/s in Fast mode and up to 3.4 Mbit/s in High-speed slave mode only, based on a byte-oriented transfer format. It can be used with any Atmel Two-wire Interface bus Serial EEPROM and I<sup>2</sup>C-compatible devices, such as a Real-Time Clock (RTC), Dot Matrix/Graphic LCD Controller and temperature sensor. The TWIHS is programmable as a master or a slave with sequential or single-byte access. Multiple master capability is supported.

A configurable baud rate generator permits the output data rate to be adapted to a wide range of core clock frequencies.

Table 43-1 lists the compatibility level of the Atmel Two-wire Interface in Master mode and a full I<sup>2</sup>C compatible device.

| I <sup>2</sup> C Standard                    | Atmel TWI     |

|----------------------------------------------|---------------|

| Standard Mode Speed (100 kHz)                | Supported     |

| Fast Mode Speed (400 kHz)                    | Supported     |

| High-speed Mode (Slave only, 3.4 MHz)        | Supported     |

| 7- or 10-bit <sup>(1)</sup> Slave Addressing | Supported     |

| START Byte <sup>(2)</sup>                    | Not Supported |

| Repeated Start (Sr) Condition                | Supported     |

| ACK and NACK Management                      | Supported     |

| Input Filtering                              | Supported     |

| Slope Control                                | Not Supported |

| Clock Stretching                             | Supported     |

| Multi Master Capability                      | Supported     |

Table 43-1.

Atmel TWI Compatibility with I<sup>2</sup>C Standard

Notes: 1. 10-bit support in Master mode only

2. START + b000000001 + Ack + Sr

# 43.2 Embedded Characteristics

- 2 TWIHSs

- 16-byte Transmit and Receive FIFOs

- Compatible with Atmel Two-wire Interface Serial Memory and I<sup>2</sup>C Compatible Devices<sup>(1)</sup>

- One, Two or Three Bytes for Slave Address

- Sequential Read/Write Operations

- Master and Multimaster Operation (Standard and Fast Modes Only)

- Slave Mode Operation (Standard, Fast and High-Speed Modes)

- Bit Rate: Up to 400 Kbit/s in Fast Mode and 3.4 Mbit/s in High-Speed Mode (Slave Mode Only)

- General Call Supported in Slave Mode

- SleepWalking (Asynchronous and Partial Wakeup)

- SMBus Support

- Connection to DMA Controller (DMA) Channel Capabilities Optimizes Data Transfers

- Register Write Protection

Note: 1. See Table 43-1 for details on compatibility with I<sup>2</sup>C Standard.

# 43.3 List of Abbreviations

# Table 43-2.Abbreviations

| Abbreviation | Description             |

|--------------|-------------------------|

| TWI          | Two-wire Interface      |

| А            | Acknowledge             |

| NA           | Non Acknowledge         |

| Р            | Stop                    |

| S            | Start                   |

| Sr           | Repeated Start          |

| SADR         | Slave Address           |

| ADR          | Any address except SADR |

| R            | Read                    |

| W            | Write                   |

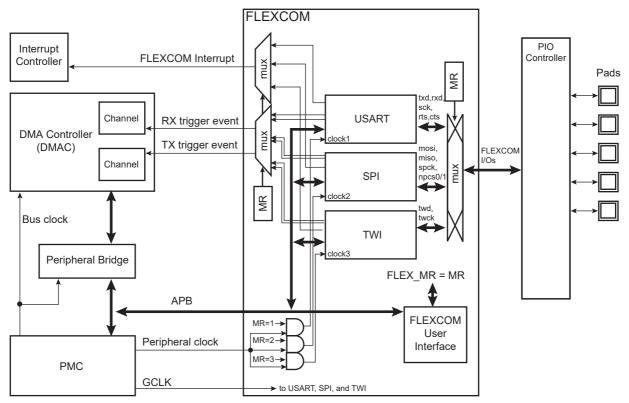

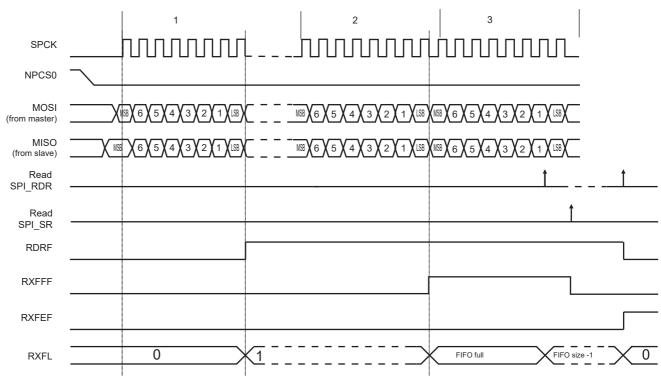

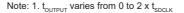

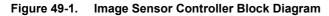

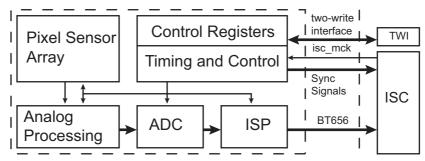

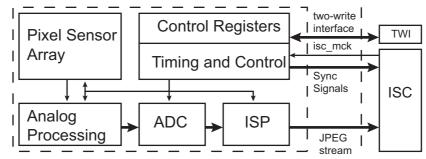

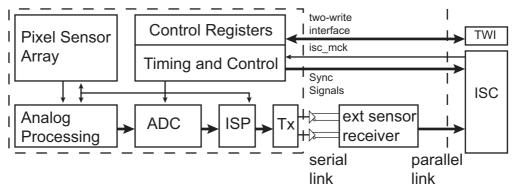

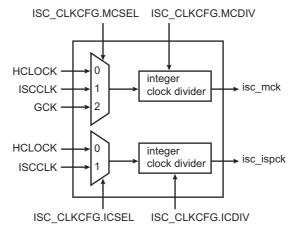

# 43.4 Block Diagram

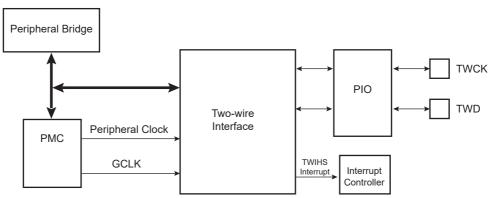

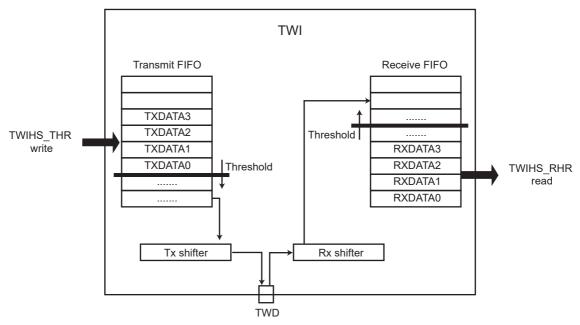

### Figure 43-1. Block Diagram

### 43.4.1 I/O Lines Description

| Pin Name | Pin Description       | Туре         |

|----------|-----------------------|--------------|

| TWD      | Two-wire Serial Data  | Input/Output |

| TWCK     | Two-wire Serial Clock | Input/Output |

### Table 43-3.I/O Lines Description

# 43.5 **Product Dependencies**

# 43.5.1 I/O Lines

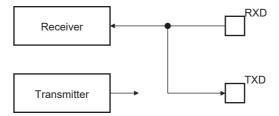

Both TWD and TWCK are bidirectional lines, connected to a positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are high. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function.

TWD and TWCK pins may be multiplexed with PIO lines. To enable the TWIHS, the user must program the PIO Controller to dedicate TWD and TWCK as peripheral lines. When High-speed Slave mode is enabled, the analog pad filter must be enabled.

The user must not program TWD and TWCK as open-drain. This is already done by the hardware.

| Instance | Signal | I/O Line | Peripheral |

|----------|--------|----------|------------|

| TWIHS0   | TWCK0  | PC0      | D          |

| TWIHS0   | TWCK0  | PC28     | E          |

| TWIHS0   | TWCK0  | PD22     | В          |

| TWIHS0   | TWCK0  | PD30     | E          |

| TWIHS0   | TWD0   | PB31     | D          |

| TWIHS0   | TWD0   | PC27     | E          |

| TWIHS0   | TWD0   | PD21     | В          |

| TWIHS0   | TWD0   | PD29     | E          |

| TWIHS1   | TWCK1  | PC7      | С          |

| TWIHS1   | TWCK1  | PD5      | А          |

| TWIHS1   | TWCK1  | PD20     | В          |

| TWIHS1   | TWD1   | PC6      | С          |

| TWIHS1   | TWD1   | PD4      | А          |

| TWIHS1   | TWD1   | PD19     | В          |

# 43.5.2 Power Management

Enable the peripheral clock.

The TWIHS may be clocked through the Power Management Controller (PMC), thus the user must first configure the PMC to enable the TWIHS clock.

# 43.5.3 Interrupt Sources

The TWIHS has an interrupt line connected to the Interrupt Controller. In order to handle interrupts, the Interrupt Controller must be programmed before configuring the TWIHS.

| Table 4 | 43-5. | Peripheral  | IDs |

|---------|-------|-------------|-----|

| 10010   |       | · onpriorai |     |

| Instance | ID |

|----------|----|

| TWIHS0   | 29 |

| TWIHS1   | 30 |

# 43.6 Functional Description

### 43.6.1 Transfer Format

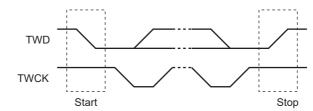

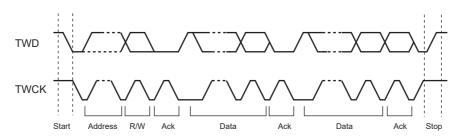

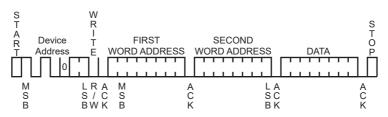

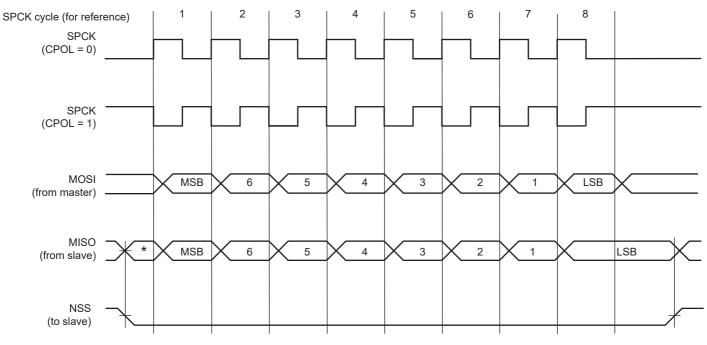

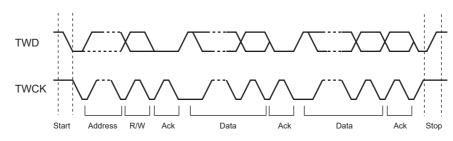

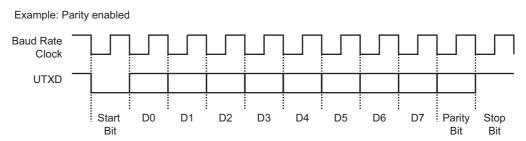

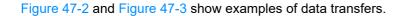

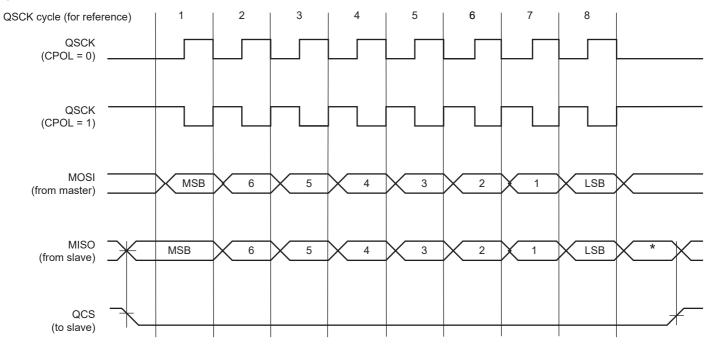

The data put on the TWD line must be 8 bits long. Data is transferred MSB first; each byte must be followed by an acknowledgement. The number of bytes per transfer is unlimited. See Figure 43-3.

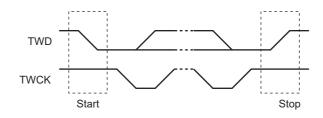

Each transfer begins with a START condition and terminates with a STOP condition. See Figure 43-2.

- A high-to-low transition on the TWD line while TWCK is high defines the START condition.

- A low-to-high transition on the TWD line while TWCK is high defines the STOP condition.

### Figure 43-2. START and STOP Conditions

### Figure 43-3. Transfer Format

### 43.6.2 Modes of Operation

The TWIHS has different modes of operation:

- Master Transmitter mode (Standard and Fast modes only)

- Master Receiver mode (Standard and Fast modes only)

- Multimaster Transmitter mode (Standard and Fast modes only)

- Multimaster Receiver mode (Standard and Fast modes only)

- Slave Transmitter mode (Standard, Fast and High-speed modes)

- Slave Receiver mode (Standard, Fast and High-speed modes)

These modes are described in the following sections.

### 43.6.3 Master Mode

### 43.6.3.1 Definition

The master is the device that starts a transfer, generates a clock and stops it. This operating mode is not available if High-speed mode is selected.

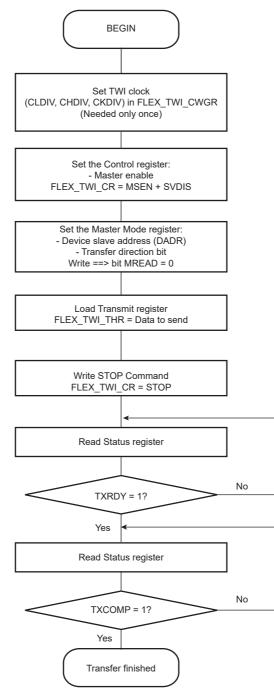

### 43.6.3.2 Programming Master Mode

The following registers must be programmed before entering Master mode:

- 1. TWIHS\_MMR.DADR (+ IADRSZ + IADR if a 10-bit device is addressed): The device address is used to access slave devices in Read or Write mode.

- 2. TWIHS\_CWGR.CKDIV + CHDIV + CLDIV: Clock Waveform register

- 3. TWIHS\_CR.SVDIS: Disables the Slave mode

- 4. TWIHS\_CR.MSEN: Enables the Master mode

- Note: If the TWIHS is already in Master mode, the device address (DADR) can be configured without disabling the Master mode.

### 43.6.3.3 Transfer Rate Clock Source

The TWIHS speed is defined in the TWIHS\_CWGR. The TWIHS baud rate can be based either on the peripheral clock if the CKSRC bit value is '0' or on a GCLK clock if the CKSRC bit value is '1'.

If CKSRC = 1, the baud rate is independent of the system/core clock (MCK) and thus the MCK frequency can be changed without affecting the TWIHS transfer rate.

The GCLK frequency must always be three times lower than the peripheral clock frequency.

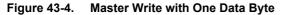

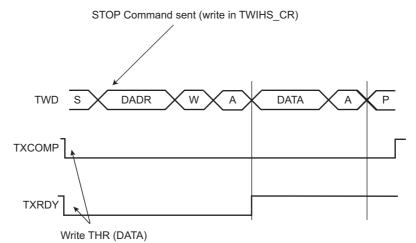

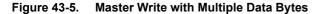

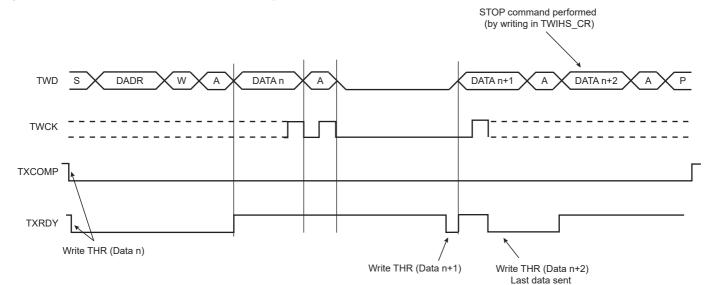

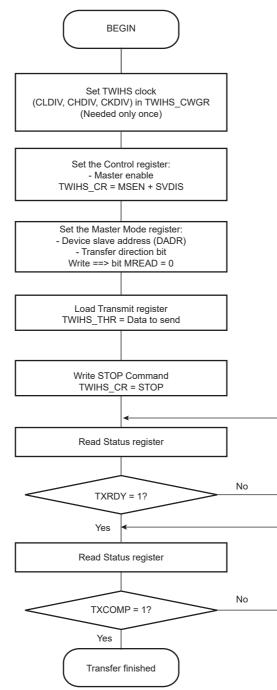

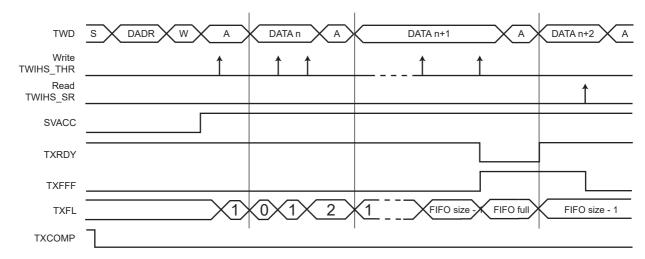

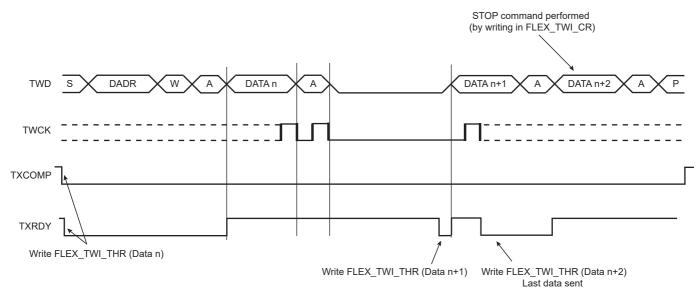

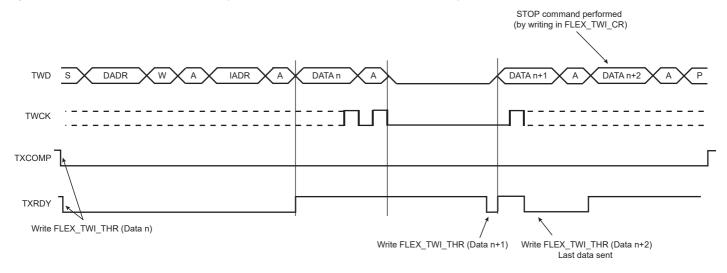

### 43.6.3.4 Master Transmitter Mode

This operating mode is not available if High-speed mode is selected.

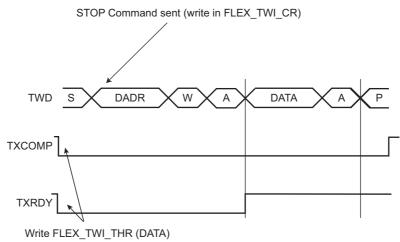

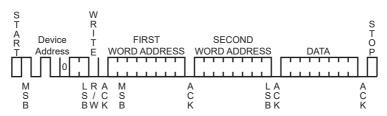

After the master initiates a START condition when writing into the Transmit Holding register (TWIHS\_THR), it sends a 7-bit slave address, configured in the Master Mode register (DADR in TWIHS\_MMR), to notify the slave device. The bit following the slave address indicates the transfer direction, 0 in this case (MREAD = 0 in TWIHS\_MMR).

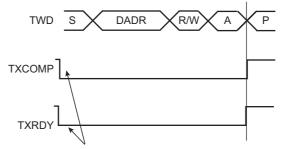

The TWIHS transfers require the slave to acknowledge each received byte. During the acknowledge clock pulse (9th pulse), the master releases the data line (HIGH), enabling the slave to pull it down in order to generate the acknowledge. If the slave does not acknowledge the byte, then the Not Acknowledge flag (NACK) is set in the TWIHS Status Register (TWIHS\_SR) of the master and a STOP condition is sent. The NACK flag must be cleared by reading TWIHS\_SR before the next write into TWIHS\_THR. As with the other status bits, an interrupt can be generated if enabled in the Interrupt Enable register (TWIHS\_IER). If the slave acknowledges the byte, the data written in the TWIHS\_THR is then shifted in the internal shifter and transferred. When an acknowledge is detected, the TXRDY bit is set until a new write in the TWIHS\_THR.

TXRDY is used as Transmit Ready for the DMA transmit channel.

While no new data is written in the TWIHS\_THR, the serial clock line is tied low. When new data is written in the TWIHS\_THR, the SCL is released and the data is sent. Setting the STOP bit in TWIHS\_CR generates a STOP condition.

After a master write transfer, the serial clock line is stretched (tied low) as long as no new data is written in the TWIHS\_THR or until a STOP command is performed.

To clear the TXRDY flag, first set the bit TWIHS\_CR.MSDIS, then set the bit TWIHS\_CR.MSEN.

See Figure 43-4, Figure 43-5, and Figure 43-6.

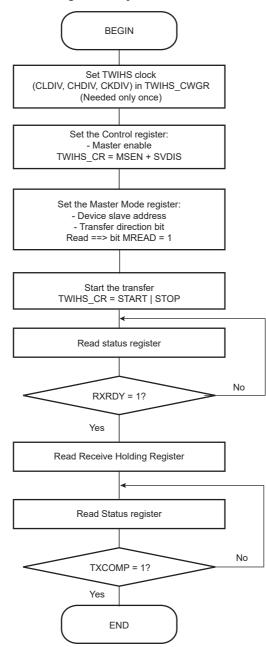

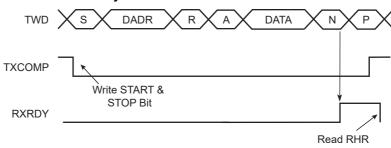

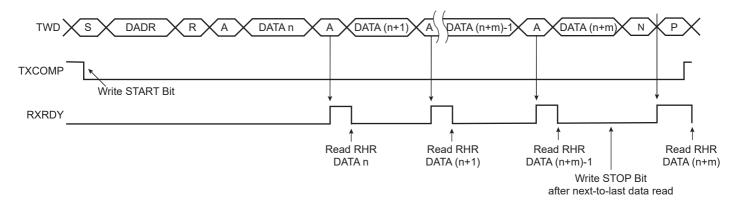

### 43.6.3.5 Master Receiver Mode

Master Receiver mode is not available if High-speed mode is selected.

The read sequence begins by setting the START bit. After the START condition has been sent, the master sends a 7-bit slave address to notify the slave device. The bit following the slave address indicates the transfer direction, 1 in this case (MREAD = 1 in TWIHS\_MMR). During the acknowledge clock pulse (9th pulse), the master releases the data line (HIGH), enabling the slave to pull it down in order to generate the acknowledge. The master polls the data line during this clock pulse and sets the NACK bit in the TWIHS\_SR if the slave does not acknowledge the byte.

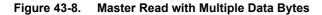

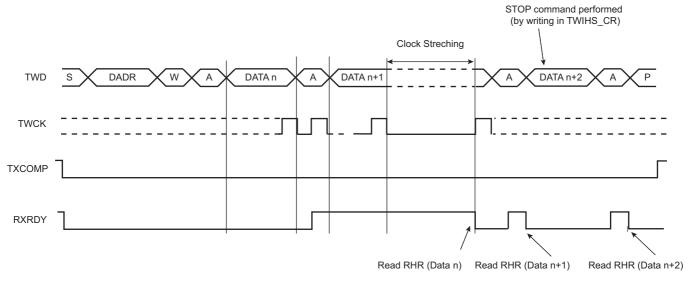

If an acknowledge is received, the master is then ready to receive data from the slave. After data has been received, the master sends an acknowledge condition to notify the slave that the data has been received except for the last data (see Figure 43-7). When the RXRDY bit is set in the TWIHS\_SR, a character has been received in the Receive Holding register (TWIHS\_RHR). The RXRDY bit is reset when reading the TWIHS\_RHR.

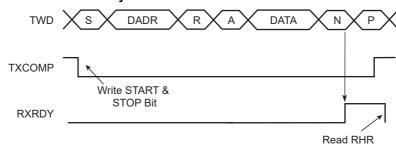

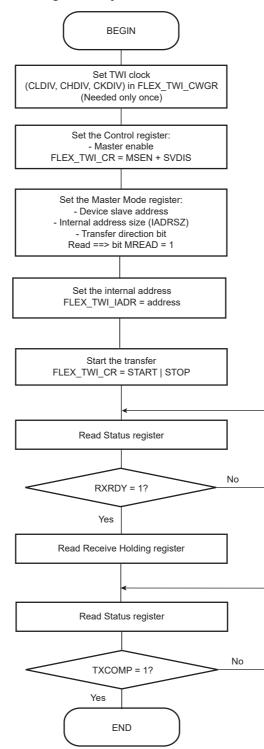

When a single data byte read is performed, with or without internal address (IADR), the START and STOP bits must be set at the same time. See Figure 43-7. When a multiple data byte read is performed, with or without internal address (IADR), the STOP bit must be set after the next-to-last data received (same condition applies for START bit to generate a REPEATED START). See Figure 43-8. For internal address usage, see Section 43.6.3.6 "Internal Address".

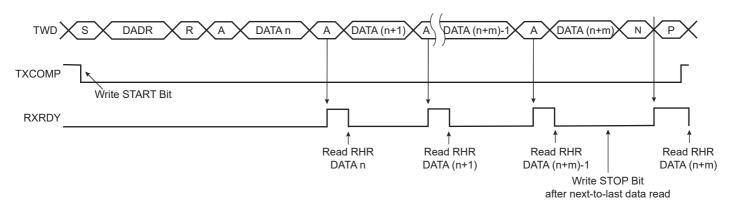

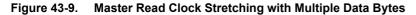

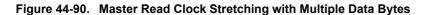

If TWIHS\_RHR is full (RXRDY high) and the master is receiving data, the serial clock line is tied low before receiving the last bit of the data and until the TWIHS\_RHR is read. Once the TWIHS\_RHR is read, the master stops stretching the serial clock line and ends the data reception. See Figure 43-9.

**Warning:** When receiving multiple bytes in Master Read mode, if the next-to-last access is not read (the RXRDY flag remains high), the last access is not completed until TWIHS\_RHR is read. The last access stops on the next-to-last bit (clock stretching). When the TWIHS\_RHR is read, there is only half a bit period to send the STOP (or START) command, else another read access might occur (spurious access).

A possible workaround is to set the STOP (or START) bit before reading the TWIHS\_RHR on the next-to-last access (within IT handler).

### Figure 43-7. Master Read with One Data Byte

RXRDY is used as receive ready for the DMA receive channel.

### 43.6.3.6 Internal Address

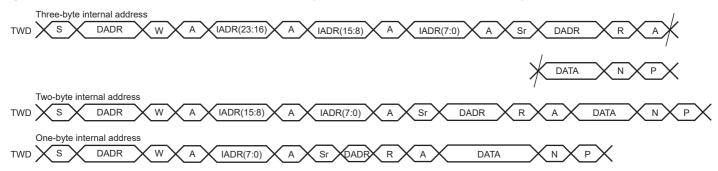

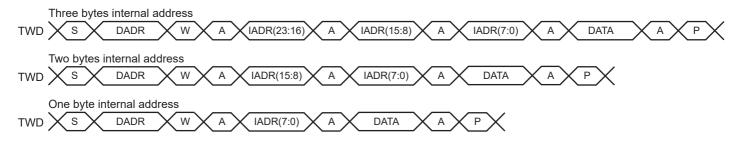

The TWIHS can perform transfers with 7-bit slave address devices and with 10-bit slave address devices.

### 7-bit Slave Addressing

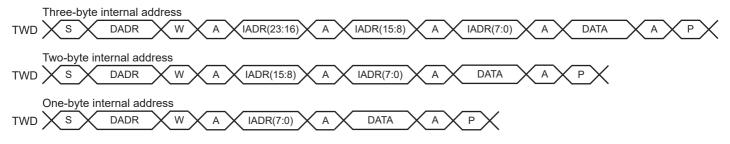

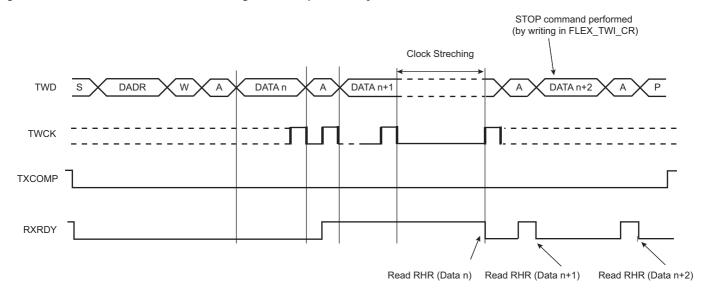

When addressing 7-bit slave devices, the internal address bytes are used to perform random address (read or write) accesses to reach one or more data bytes, e.g. within a memory page location in a serial memory. When performing read operations with an internal address, the TWIHS performs a write operation to set the internal address into the slave device, and then switch to Master Receiver mode. Note that the second START condition (after sending the IADR) is sometimes called "repeated start" (Sr) in I<sup>2</sup>C fully-compatible devices. See Figure 43-11.

See Figure 43-10 and Figure 43-12 for the master write operation with internal address.

The three internal address bytes are configurable through TWIHS\_MMR.

If the slave device supports only a 7-bit address, i.e., no internal address, IADRSZ must be set to 0.

Table 43-6 shows the abbreviations used in Figure 43-10 and Figure 43-11.

| Abbreviation | Definition       |

|--------------|------------------|

| S            | Start            |

| Sr           | Repeated Start   |

| Р            | Stop             |

| W            | Write            |

| R            | Read             |

| A            | Acknowledge      |

| NA           | Not Acknowledge  |

| DADR         | Device Address   |

| IADR         | Internal Address |

Table 43-6.Abbreviations

# Figure 43-10. Master Write with One-, Two- or Three-Byte Internal Address and One Data Byte

### Figure 43-11. Master Read with One-, Two- or Three-Byte Internal Address and One Data Byte

### **10-bit Slave Addressing**

For a slave address higher than seven bits, configure the address size (IADRSZ) and set the other slave address bits in the Internal Address register (TWIHS\_IADR). The two remaining internal address bytes, IADR[15:8] and IADR[23:16], can be used the same way as in 7-bit slave addressing.

Example: Address a 10-bit device (10-bit device address is b1 b2 b3 b4 b5 b6 b7 b8 b9 b10)

- 1. Program IADRSZ = 1,

- 2. Program DADR with 1 1 1 1 0 b1 b2 (b1 is the MSB of the 10-bit address, b2, etc.)

- 3. Program TWIHS\_IADR with b3 b4 b5 b6 b7 b8 b9 b10 (b10 is the LSB of the 10-bit address)

Figure 43-12 shows a byte write to a memory device. This demonstrates the use of internal addresses to access the device.

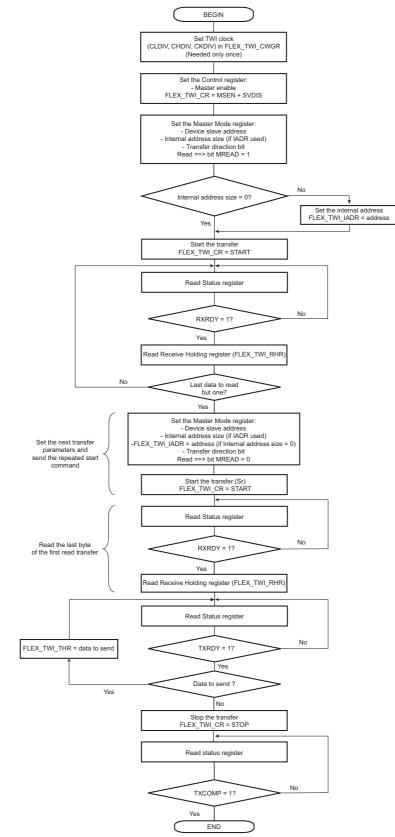

### 43.6.3.7 Repeated Start

In addition to Internal Address mode, REPEATED START (Sr) can be generated manually by writing the START bit at the end of a transfer instead of the STOP bit. In such case, the parameters of the next transfer (direction, SADR, etc.) need to be set before writing the START bit at the end of the previous transfer.

See Section 43.6.3.14 "Read/Write Flowcharts" for detailed flowcharts.

Note that generating a REPEATED START after a single data read is not supported.

### 43.6.3.8 Bus Clear Command

The TWIHS can perform a Bus Clear command:

- 1. Configure the Master mode (DADR, CKDIV, etc).

- 2. Start the transfer by setting the CLEAR bit in the TWIHS\_CR.

Note: If alternative command is used (ACMEN bit set to '1') DATAL field must be set to 0.

### 43.6.3.9 Using the DMA Controller (DMAC) in Master Mode

The use of the DMA significantly reduces the CPU load.

To ensure correct implementation, follow the programming sequences below:

### Data Transmit with the DMA in Master Mode

If Alternative Command mode is disabled (ACMEN bit set to '0'):

The DMA transfer size must be defined with the buffer size minus 1. The remaining character must be managed without DMA to ensure that the exact number of bytes are transmitted regardless of system bus latency conditions during the end of the buffer transfer period.

- 1. Initialize the DMA (channels, memory pointers, size 1, etc.);

- 2. Configure the Master mode (DADR, CKDIV, MREAD = 0, etc.) or Slave mode.

- 3. Enable the DMA.

- 4. Wait for the DMA status flag indicating that the buffer transfer is complete.

- 5. Disable the DMA.

- 6. Wait for the TXRDY flag in TWIHS\_SR.

- 7. Set the STOP bit in TWIHS\_CR.

- 8. Write the last character in TWIHS\_THR.

- 9. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

If Alternative Command mode is enabled (ACMEN bit set to '1'):

- 1. Initialize the transmit DMA (memory pointers, transfer size).

- 2. Configure the Master mode (DADR, CKDIV, etc.) and TWIHS\_ACR.

- 3. Start the transfer by setting the DMA TXTEN bit.

- 4. Wait for the DMA ENDTX flag either by using the polling method or ENDTX interrupt.

- 5. Disable the DMA by setting the DMA TXTDIS bit.

- 6. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

### Data Receive with the DMA in Master Mode

If Alternative Command mode is disabled (ACMEN bit set to '0'):

The DMA transfer size must be defined with the buffer size minus 2. The two remaining characters must be managed without DMA to ensure that the exact number of bytes are received regardless of system bus latency conditions encountered during the end of buffer transfer period.

- 1. Initialize the DMA (channels, memory pointers, size 2, etc.);

- 2. Configure the Master mode (DADR, CKDIV, MREAD = 1, etc.) or Slave mode.

- 3. Enable the DMA.

- 4. (Master Only) Write the START bit in the TWIHS\_CR to start the transfer.

- 5. Wait for the DMA status flag indicating that the buffer transfer is complete.

- 6. Disable the DMA.

- 7. Wait for the RXRDY flag in the TWIHS\_SR.

- 8. Set the STOP bit in TWIHS\_CR.

- 9. Read the penultimate character in TWIHS\_RHR.

- 10. Wait for the RXRDY flag in the TWIHS\_SR.

- 11. Read the last character in TWIHS\_RHR.

- 12. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

If Alternative Command mode is enabled (ACMEN bit set to '1'):

- 1. Initialize the transmit DMA (memory pointers, transfer size).

- 2. Configure the Master mode (DADR, CKDIV, etc.) and TWIHS\_ACR.

- 3. Set the DMA RXTEN bit.

- 4. (Master Only) Write the START bit in the TWIHS\_CR to start the transfer.

- 5. Wait for the DMA ENDTX Flag either by using the polling method or ENDTX interrupt.

- 6. Disable the DMA by setting the DMA TXTDIS bit.

- 7. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

# 43.6.3.10 SMBus Mode

SMBus mode is enabled when a one is written to the SMEN bit in the TWIHS\_CR. SMBus mode operation is similar to I<sup>2</sup>C operation with the following exceptions:

- Only 7-bit addressing can be used.

- The SMBus standard describes a set of timeout values to ensure progress and throughput on the bus. These timeout values must be programmed into TWIHS\_SMBTR.

- Transmissions can optionally include a CRC byte, called Packet Error Check (PEC).

- A set of addresses has been reserved for protocol handling, such as alert response address (ARA) and host header (HH) address. Address matching on these addresses can be enabled by configuring the TWIHS\_CR.

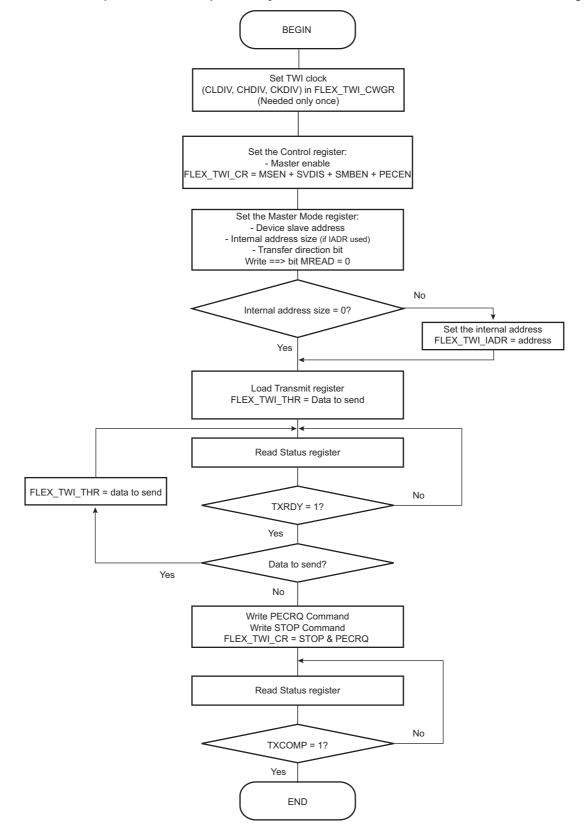

# **Packet Error Checking**

Each SMBus transfer can optionally end with a CRC byte, called the PEC byte. Writing a one to the PECEN bit in TWIHS\_CR enables automatic PEC handling in the current transfer. Transfers with and without PEC can be intermixed in the same system, since some slaves may not support PEC. The PEC LFSR is always updated on every bit transmitted or received, so that PEC handling on combined transfers is correct.

In Master Transmitter mode, the master calculates a PEC value and transmits it to the slave after all data bytes have been transmitted. Upon reception of this PEC byte, the slave compares it to the PEC value it has computed itself. If the values match, the data was received correctly, and the slave returns an ACK to the master. If the PEC values differ, data was corrupted, and the slave returns a NACK value. Some slaves may not be able to check the

received PEC in time to return a NACK if an error occurred. In this case, the slave should always return an ACK after the PEC byte, and another method must be used to verify that the transmission was received correctly.

In Master Receiver mode, the slave calculates a PEC value and transmits it to the master after all data bytes have been transmitted. Upon reception of this PEC byte, the master compares it to the PEC value it has computed itself. If the values match, the data was received correctly. If the PEC values differ, data was corrupted, and the PECERR bit in TWIHS\_SR is set. In Master Receiver mode, the PEC byte is always followed by a NACK transmitted by the master, since it is the last byte in the transfer.

In combined transfers, the PECRQ bit should only be set in the last of the combined transfers. If the Alternative Command mode is enabled, only the NPEC bit should be set.

Consider the following transfer:

S, ADR+W, COMMAND\_BYTE, ACK, SR, ADR+R, DATA\_BYTE, ACK, PEC\_BYTE, NACK, P

See Section 43.6.3.14 "Read/Write Flowcharts" for detailed flowcharts.

# **Timeouts**

The TLOWS and TLOWM fields in TWIHS\_SMBTR configure the SMBus timeout values. If a timeout occurs, the master transmits a STOP condition and leaves the bus. The TOUT bit is also set in TWIHS\_SR.

# 43.6.3.11 SMBus Quick Command (Master Mode Only)

The TWIHS can perform a quick command:

- 1. Configure the Master mode (DADR, CKDIV, etc).

- 2. Write the MREAD bit in the TWIHS\_MMR at the value of the one-bit command to be sent.

- 3. Start the transfer by setting the QUICK bit in the TWIHS\_CR.

- Note: If alternative command is used (ACMEN bit set to '1') DATAL field must be set to 0.

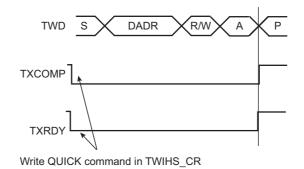

### Figure 43-13. SMBus Quick Command

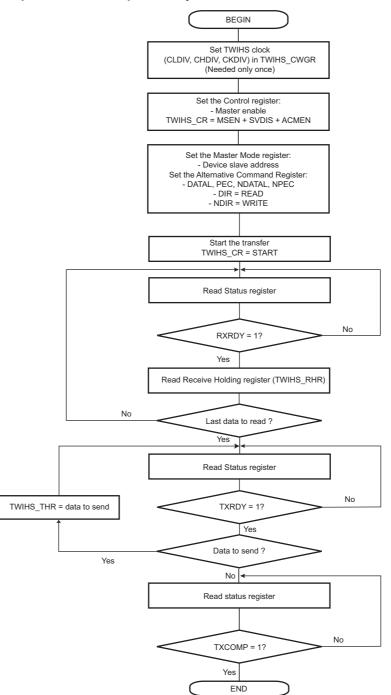

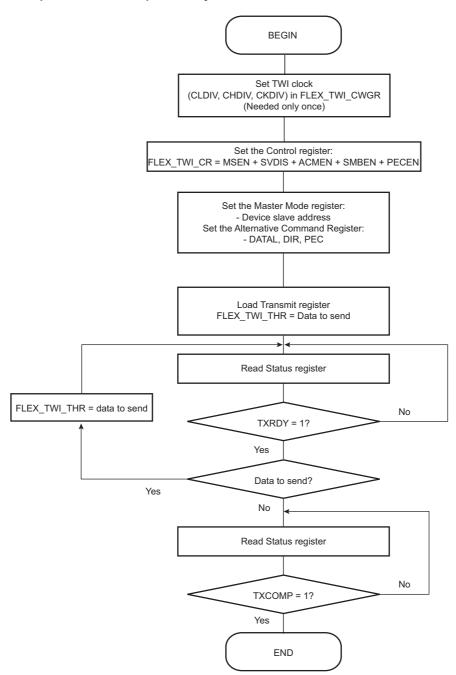

### 43.6.3.12 Alternative Command

Another way to configure the transfer is to enable the Alternative Command mode with the ACMEN bit of the TWIHS Control Register.

In this mode, the transfer is configured through the TWIHS Alternative Command Register. It is possible to define a simple read or write transfer or a combined transfer with a repeated start.

In order to set a simple transfer, the DATAL field and the DIR field of the TWIHS Alternative Command Register must be filled accordingly and the NDATAL field must be cleared. To begin the transfer, either set the START bit in the TWIHS Control Register in case of a read transfer, or write the TWIHS Transmit Holding Register in case of a write transfer.

For a combined transfer linked by a repeated start, the NDATAL field must be filled with the length of the second transfer and NDIR with the corresponding direction.

The PEC and NPEC bits are used to set a PEC field. In the case of a single transfer with PEC, the PEC bit must be set. In the case of a combined transfer, the NPEC bit must be set.

Note: If Alternative Command mode is used, IADRSZ in TWIHS\_MMR must be set to 0.

See Section 43.6.3.14 "Read/Write Flowcharts" for detailed flowcharts.

### 43.6.3.13 Handling Errors in Alternative Command

If a NACK is generated by a slave device or SMBus timeout error, the TWIHS stops the frame immediately, although the DMA transfer may still be active. To prevent a new frame from being restarted with the remaining DMA data (transmit), the TWIHS prevents any start of frame until the LOCK flag is cleared in the TWIHS\_SR.

The LOCK bit in the TWIHS\_SR indicates the state of the TWIHS (locked or not locked).

When the TWIHS is locked, no transfer begins until the LOCK is cleared by the LOCKCLR bit in the TWIHS\_CR and error flags are cleared by reading the TWIHS\_SR.

In case of error, the TWIHS\_THR may have been loaded with a new data. The THRCLR bit in the TWIHS\_CR can be used to flush the TWIHS\_THR. If the THRCLR bit is set, the TXRDY and TXCOMP flags are set.

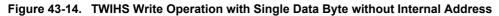

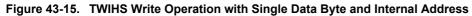

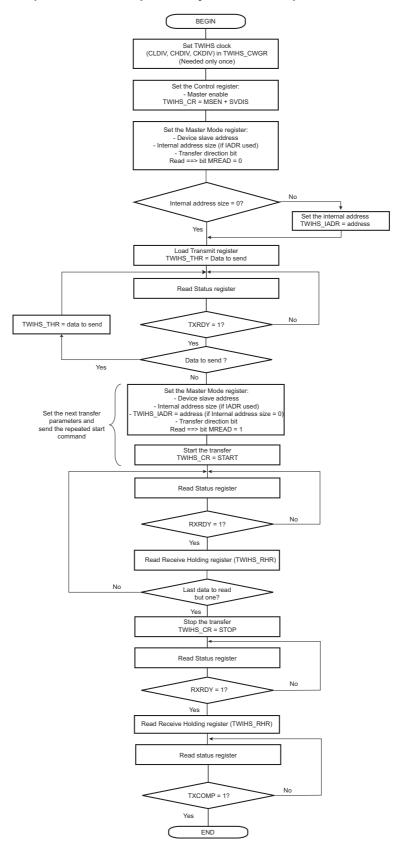

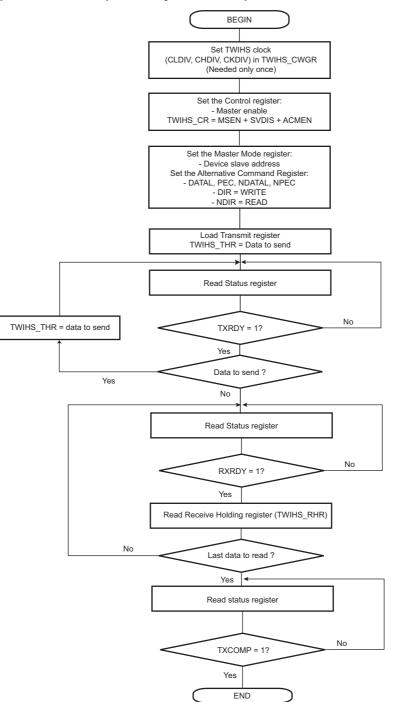

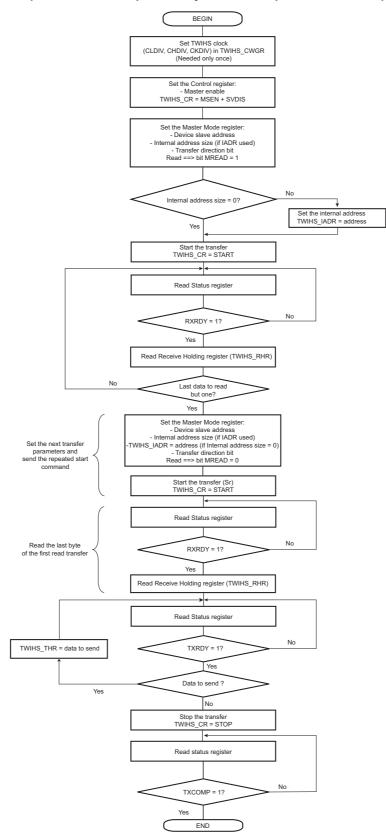

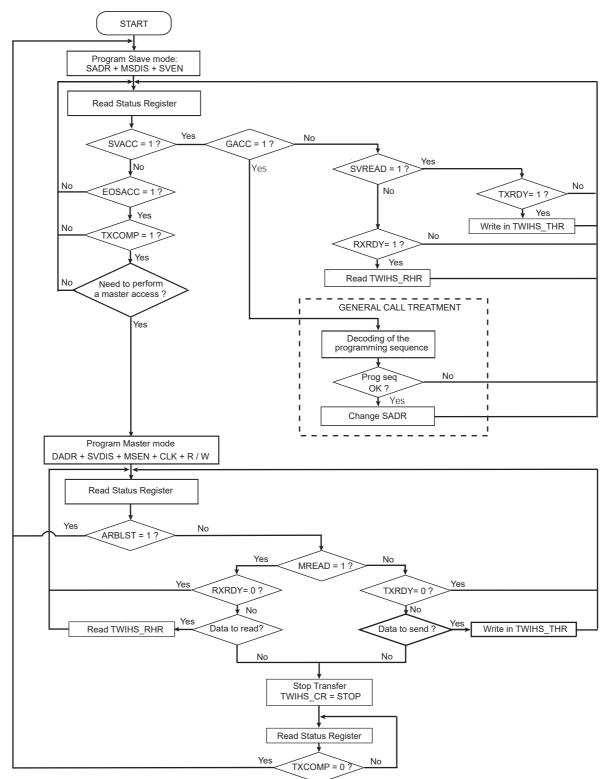

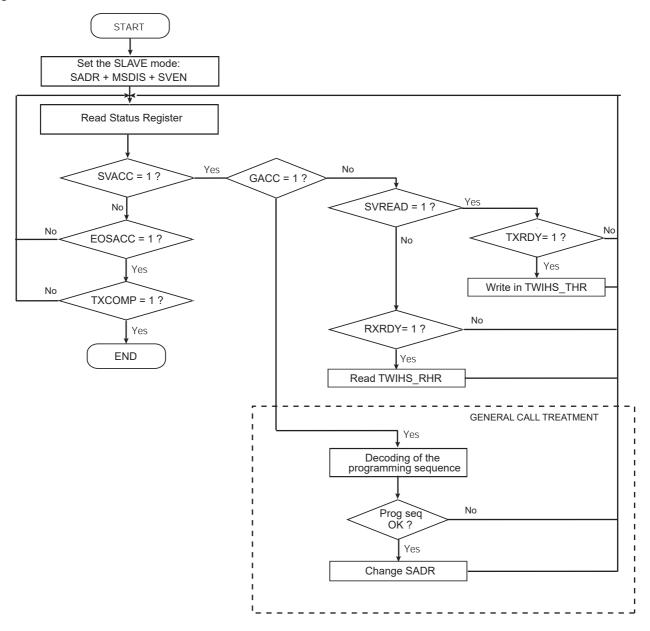

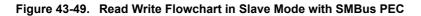

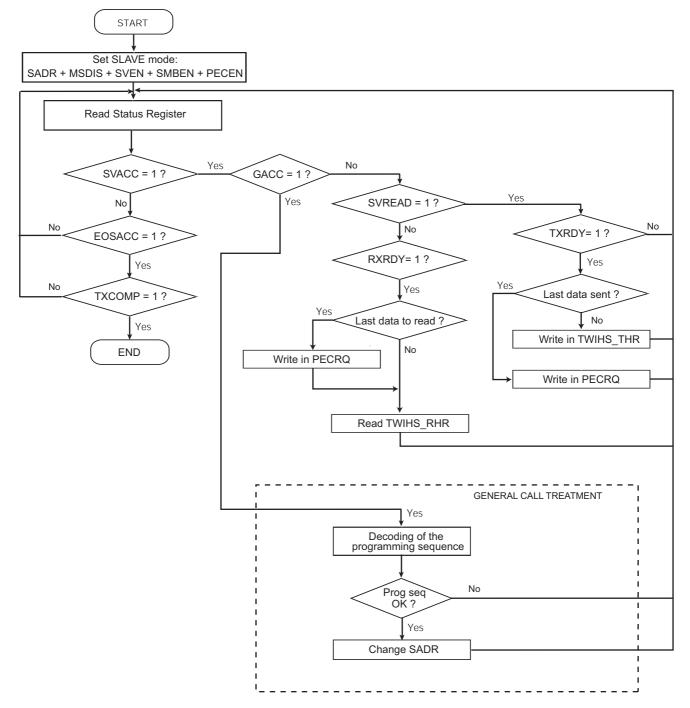

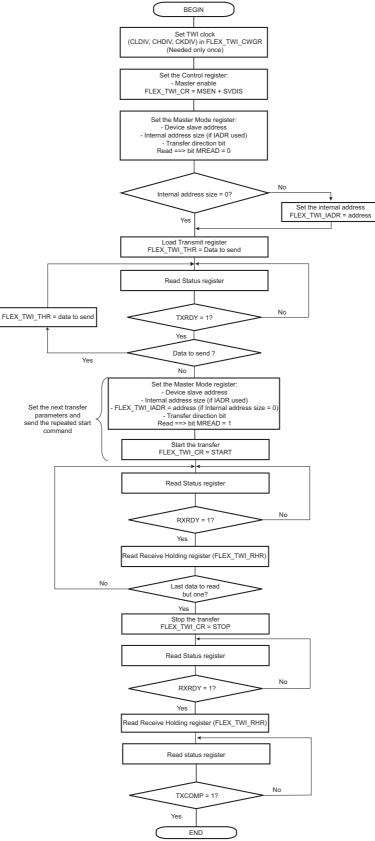

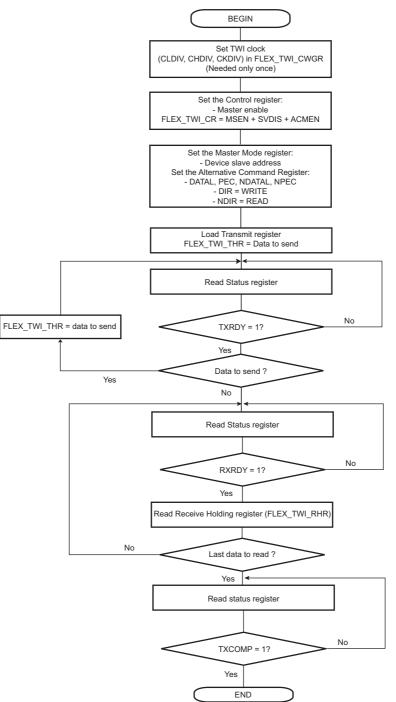

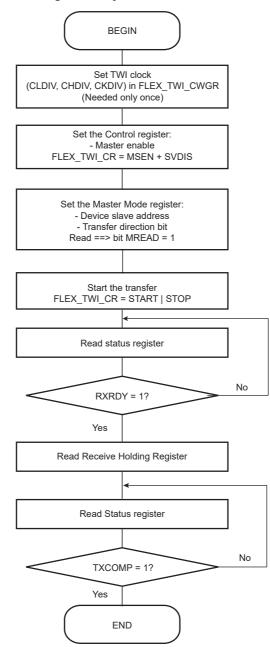

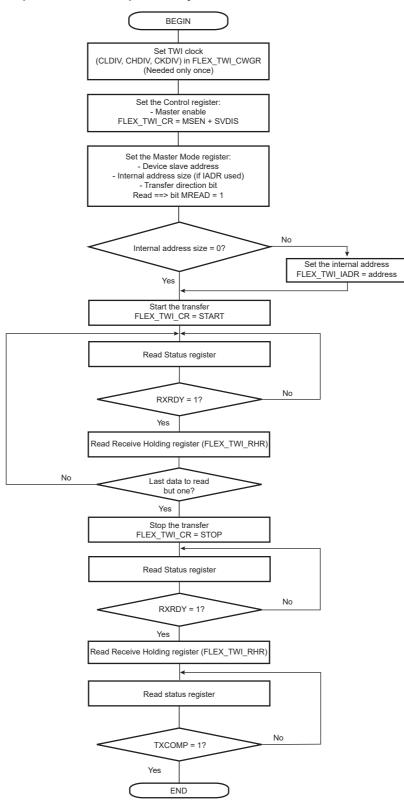

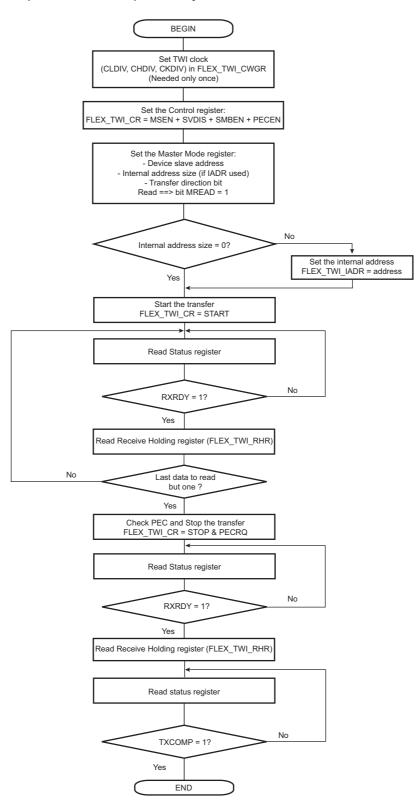

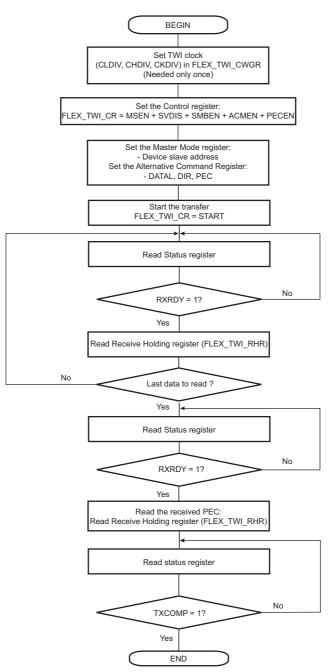

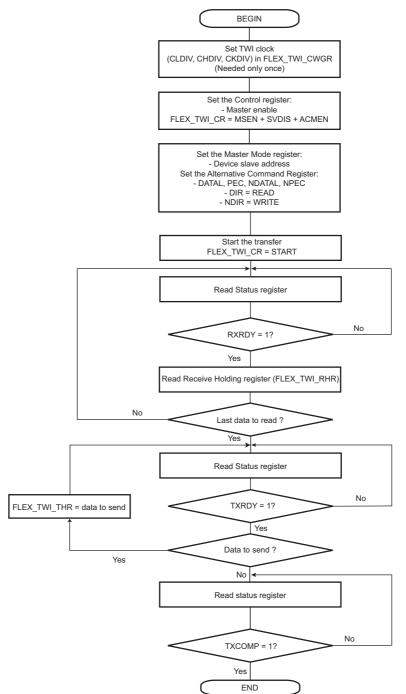

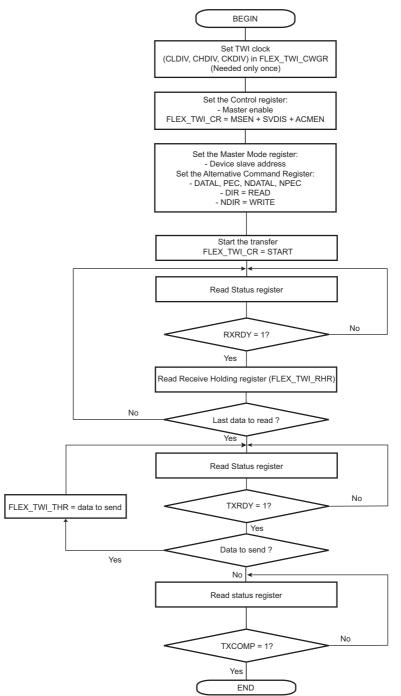

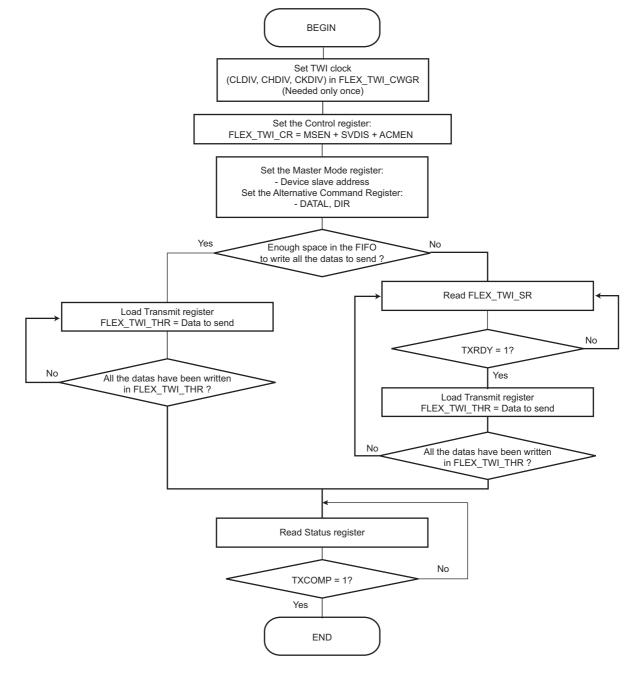

### 43.6.3.14 Read/Write Flowcharts

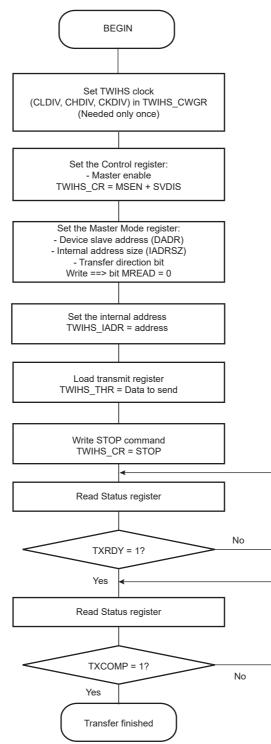

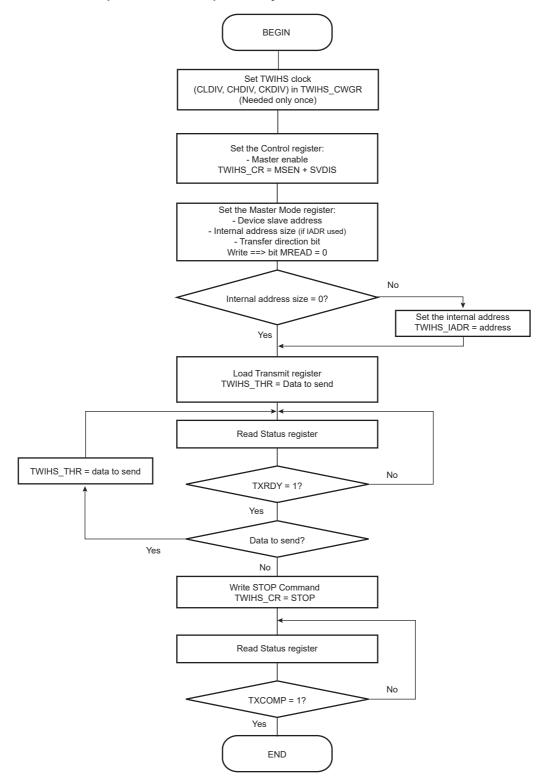

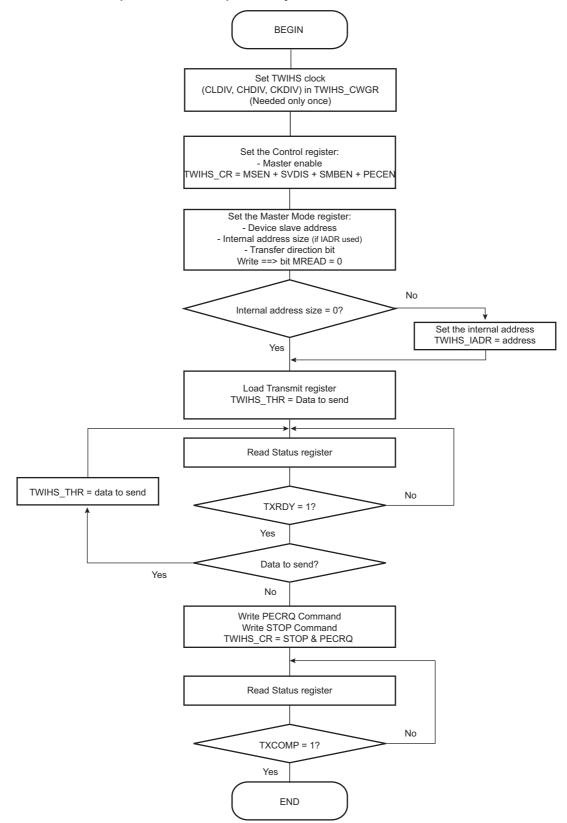

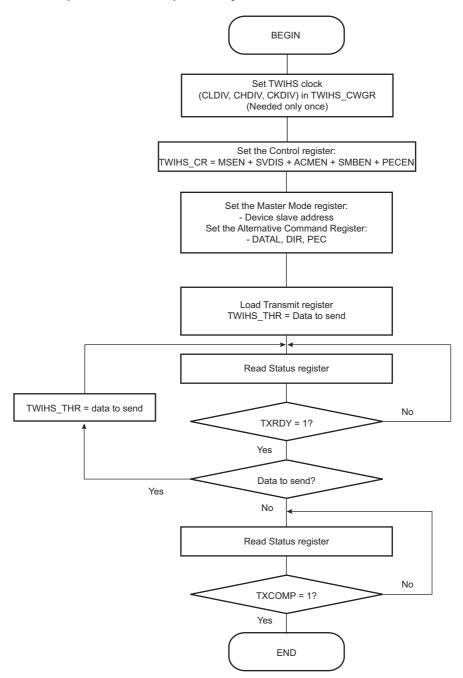

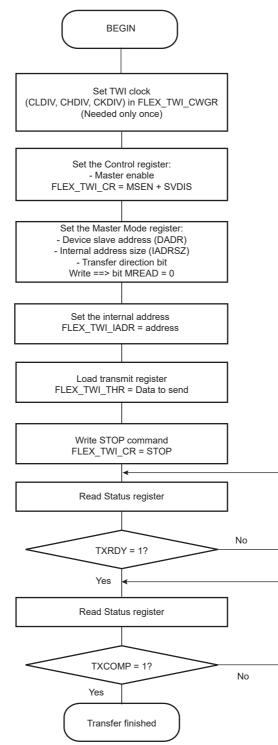

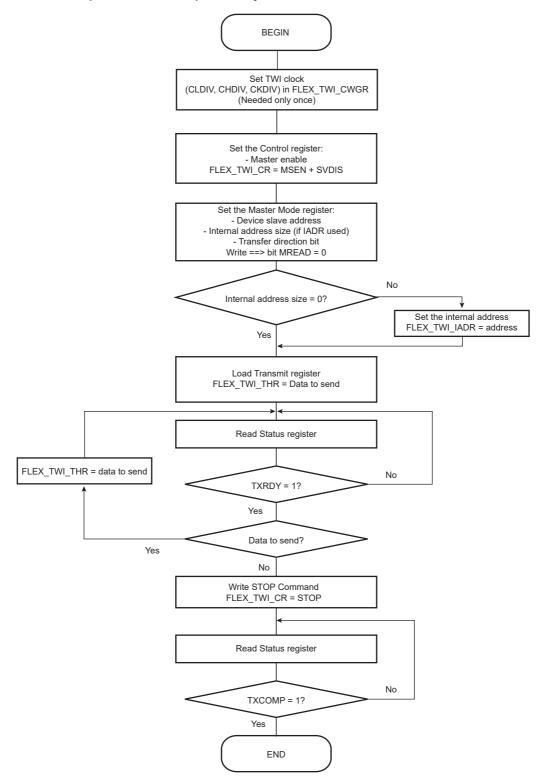

The flowcharts give examples for read and write operations. A polling or interrupt method can be used to check the status bits. The interrupt method requires that TWIHS\_IER be configured first.

**Atmel**

Figure 43-16. TWIHS Write Operation with Multiple Data Bytes with or without Internal Address

**Atmel**

Figure 43-17. SMBus Write Operation with Multiple Data Bytes with or without Internal Address and PEC Sending

# **Atmel**

Figure 43-18. SMBus Write Operation with Multiple Data Bytes with PEC and Alternative Command Mode

Atmel

Figure 43-19. TWIHS Write Operation with Multiple Data Bytes and Read Operation with Multiple Data Bytes (Sr)

Figure 43-20. TWIHS Write Operation with Multiple Data Bytes + Read Operation and Alternative Command Mode + PEC

Atmel

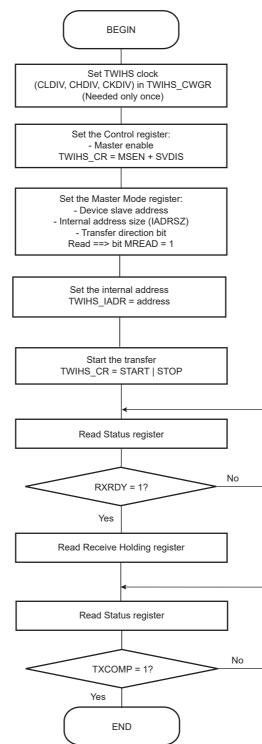

Figure 43-21. TWIHS Read Operation with Single Data Byte without Internal Address

1346 SAMA5D2 Series [DATASHEET] Atmel-11267E-ATARM-SAMA5D2-Datasheet\_25-Jul-16

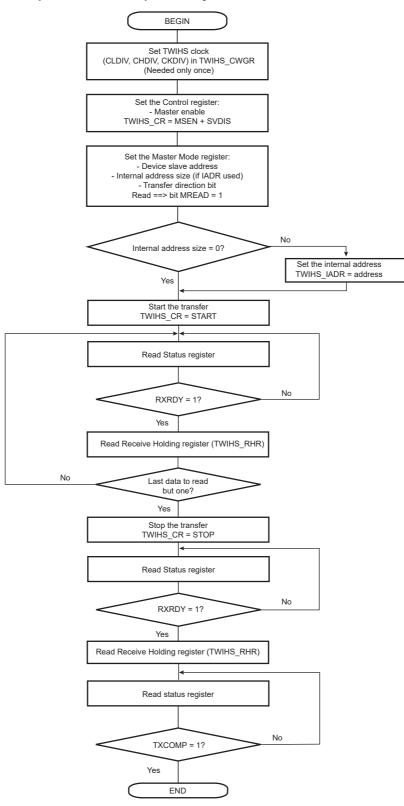

Figure 43-23. TWIHS Read Operation with Multiple Data Bytes with or without Internal Address

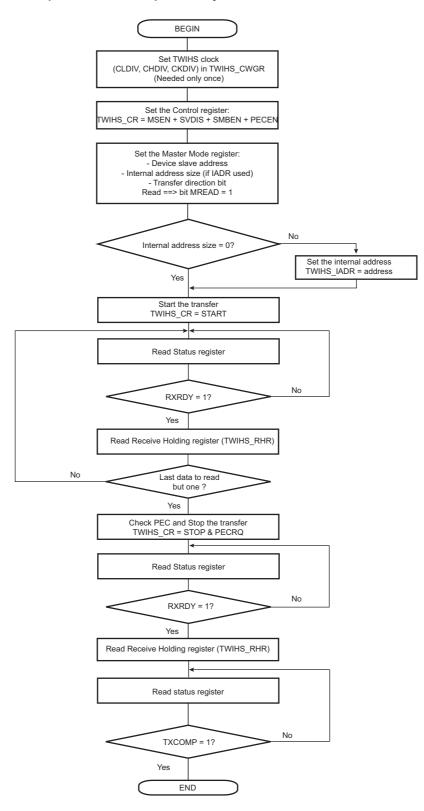

Figure 43-24. TWIHS Read Operation with Multiple Data Bytes with or without Internal Address with PEC

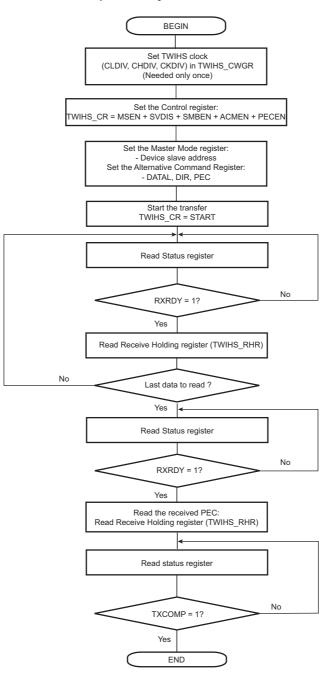

Figure 43-25. TWIHS Read Operation with Multiple Data Bytes with Alternative Command Mode with PEC

Figure 43-26. TWIHS Read Operation with Multiple Data Bytes + Write Operation with Multiple Data Bytes (Sr)

Figure 43-27. TWIHS Read Operation with Multiple Data Bytes + Write with Alternative Command Mode with PEC

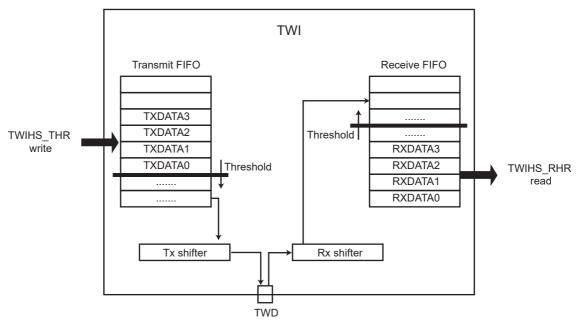

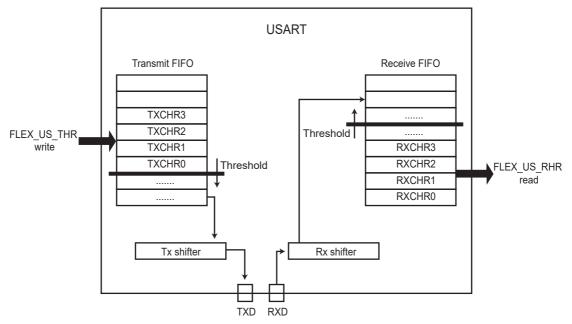

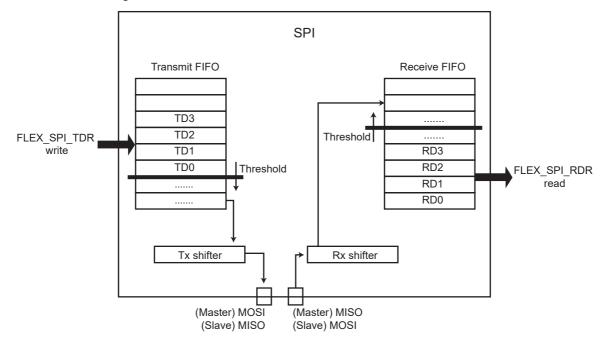

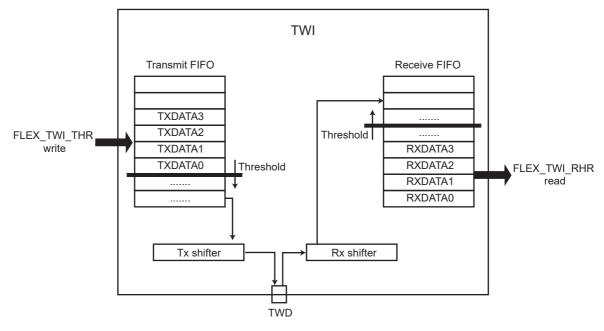

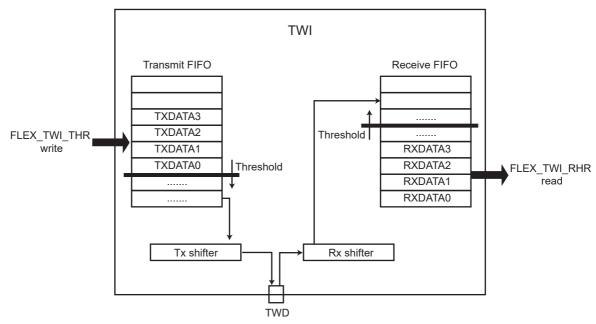

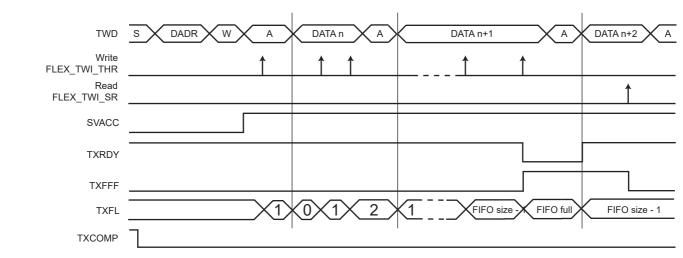

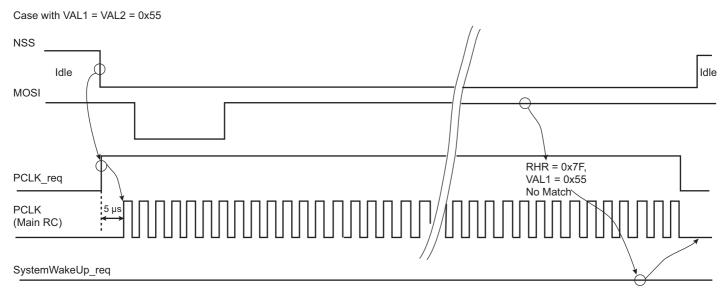

## 43.6.3.15 FIFOs

The TWIHS includes two FIFOs which can be enabled/disabled using the FIFOEN/FIFODIS bits in the TWIHS\_CR. It is recommended to disable both Master and Slave modes before enabling or disabling the FIFO (MSDIS and SVDIS bit in TWIHS\_CR).

Writing the FIFOEN bit to '1' will enable a 16-data Transmit FIFO and a 16-data Receive FIFO.

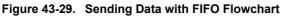

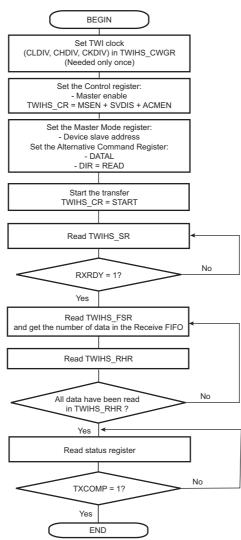

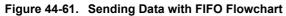

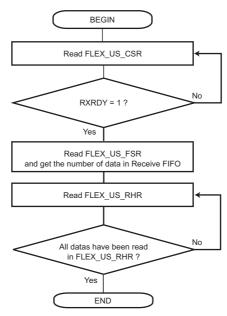

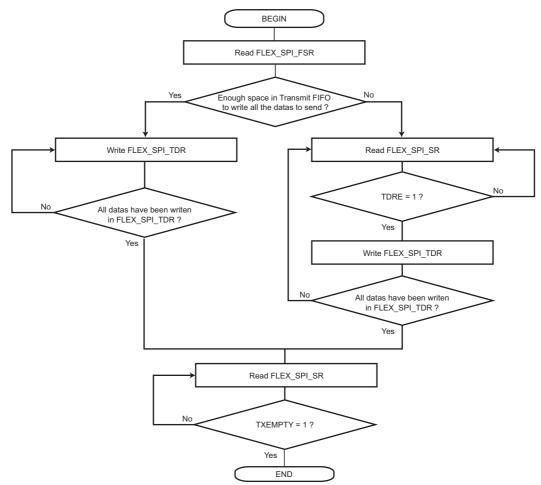

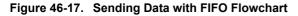

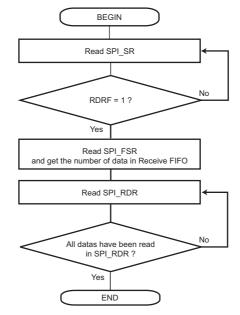

#### Sending Data with FIFO Enabled

With the Transmit FIFO enabled, any write access to the TWIHS Transmit Holding Register (TWIHS\_THR) brings the written data to the Transmit FIFO. As a consequence, it is not mandatory any more to monitor the TXRDY flag state to send multiple data without DMAC.

Knowing the number of data to send and provided there is enough space in the Transmit FIFO, all the data to send can be written successively in the TWIHS\_THR without checking the TXRDY flag between each access. The Transmit FIFO state can be checked reading the TXFL field in the TWIHS FIFO Level Register (TWIHS\_FLR).

Atmel

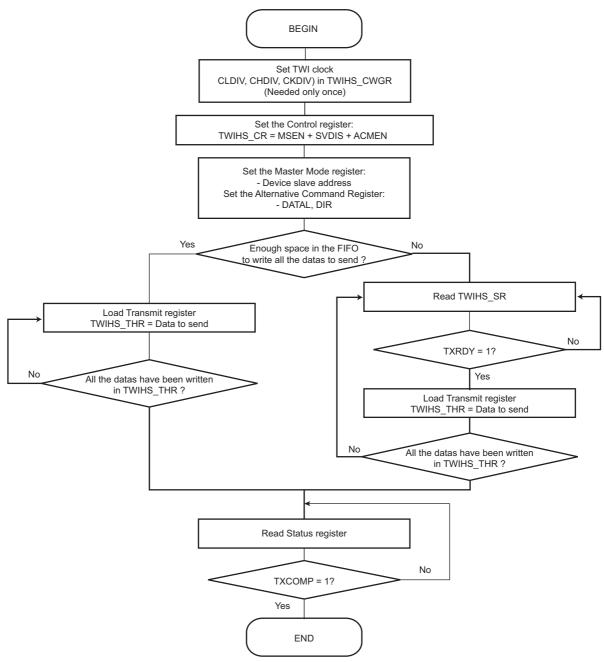

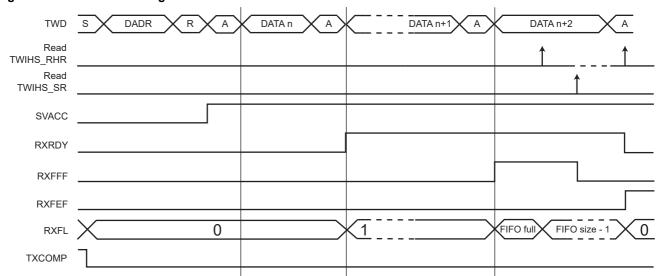

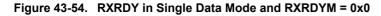

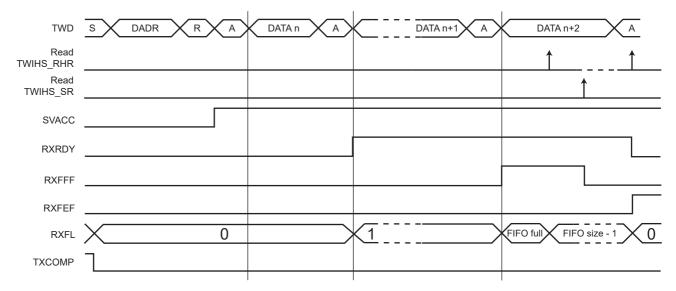

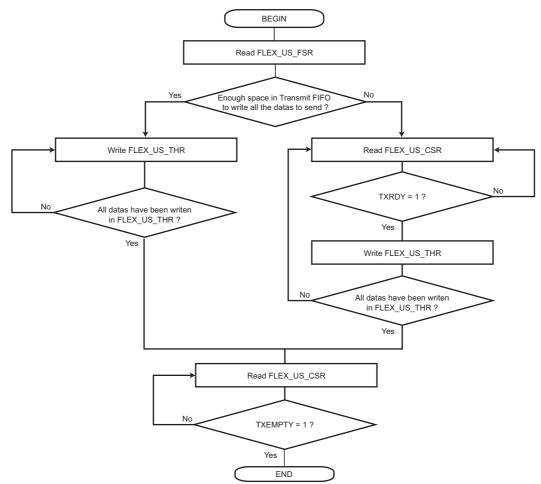

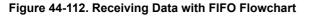

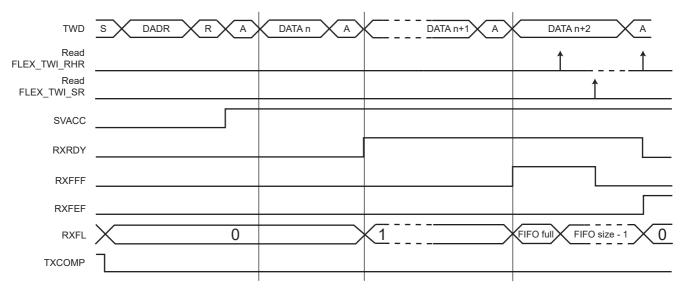

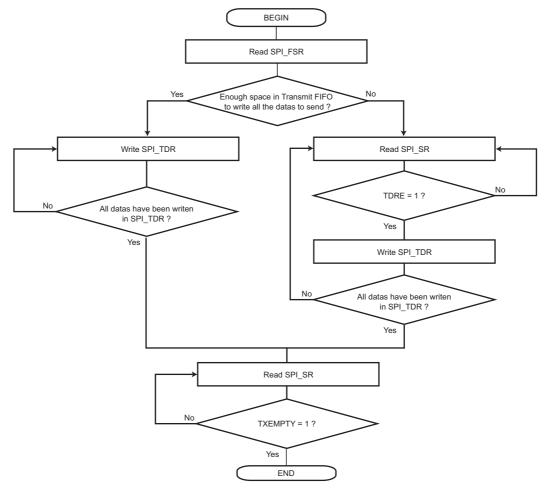

#### **Receiving Data with FIFO Enabled**

With Receive FIFO enabled, any read access on TWIHS\_RHR will pull out a data from the Receive FIFO. As a consequence, it is not mandatory any more to monitor the RXRDY flag when DMAC is not used and there are multiple data to read.

When data are present in the Receive FIFO (RXRDY flag set to '1'), the exact number of data can be checked with the RXFL field in the TWIHS\_FLR and all the data read successively in the TWIHS\_RHR without checking the RXRDY flag between each access.

# **Clearing/Flushing FIFOs**

Each FIFO can be cleared/flushed using the TXFCLR and RXFCLR bits in the TWIHS\_CR.

# **TXRDY and RXRDY Behavior**

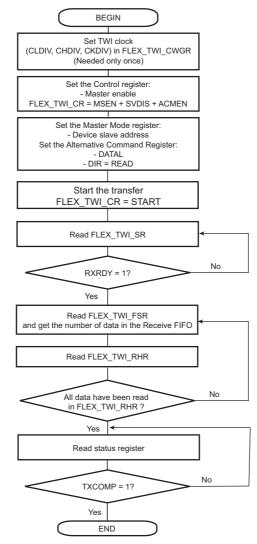

If FIFOs are enabled, the behavior of the TXRDY and RXRDY flags will be slightly different.

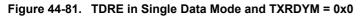

TXRDY will indicate if a data can be written in the Transmit FIFO. By default, the TXRDY flag will then stay at level '1' as long as the Transmit FIFO is not full (TXRDYM = 0x0).

**Atmel**

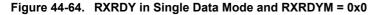

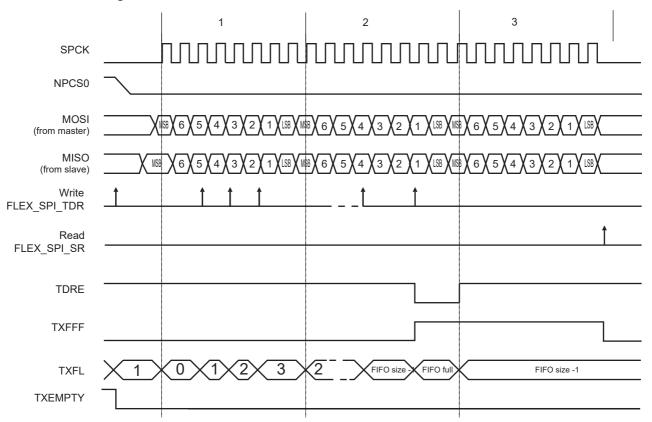

RXRDY will indicate if an unread data is present in the Receive FIFO. By default, the RXRDY flag will then be at level '1' as soon as one unread data is in the Receive FIFO (RXRDYM = 0x0).

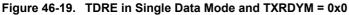

Figure 43-32. RXRDY in Single Data Mode and RXRDYM = 0x0

Figure 43-31. TXRDY in Single Data Mode and TXRDYM = 0x0

TXRDY and RXRDY behavior can be modified using the TXRDYM and RXRDYM fields in the TWIHS FIFO Mode Register (TWIHS\_FMR). In Single Data mode, there is no need to modify the TXRDY and RXRDY behavior; however, it may be useful in Multiple Data Mode.

## Master Multiple Data Mode

When the FIFOs are enabled, they operate in Multiple Data mode.

In Multiple Data mode, it is possible to write/read up to four data in one TWIHS\_THR/TWIHS\_RHR register access.

The number of data to write/read is defined by the size of the register access. If the access is a byte size register access, only one data will be written/read; if the access is a halfword-size register access, then two data will be written/read; finally, if the access is a word-size register access, then four data will be written/read.

Written/Read data are always right-aligned, as shown in Section 43.7.14 "TWIHS Receive Holding Register (FIFO Enabled)" and Section 43.7.17 "TWIHS Transmit Holding Register (FIFO Enabled)".

For instance, if the Transmit FIFO is empty and there are six data to send, you can either:

- Perform six TWIHS\_THR-byte write accesses.

- Perform three TWIHS\_THR-halfword write accesses.

- Perform one TWIHS\_THR-word write access and one TWIHS\_THR halfword write access.

It goes the same with a Receive FIFO containing six data where you can either:

- Perform six TWIHS\_RHR-byte read accesses.

- Perform three TWIHS\_RHR-halfword read accesses.

- Perform one TWIHS\_RHR-word read access and one TWIHS\_RHR-halfword read access.

This mode allows to minimize the number of accesses by concatenating the data to send/read in one access.

## • TXRDY and RXRDY Configuration

In Multiple Data mode, the TXRDYM and RXRDYM fields in the TWIHS\_FMR become useful.

As in Multiple Data mode, it is possible to write several data in the same access it might be useful to configure TXRDY flag behavior to indicate if 1, 2 or 4 data can be written in the FIFO depending on the access to perform on TWIHS\_THR.

If for instance four data are written each time in the TWIHS\_THR it might be useful to configure TXRDYM field to 0x2 value so that TXRDY flag will be at '1' only when at least four data can be written in the Transmit FIFO.

In the same way if four data are read each time in the TWIHS\_RHR it might be useful to configure RXRDYM field to 0x2 value so that RXRDY flag will be at '1' only when at least four unread data are in the Receive FIFO.

## DMAC

If DMAC transfer is used it is mandatory to configure TXRDYM/RXRDYM to the right value depending on the DMAC channel size (byte, halfword or word).

# **Transmit FIFO Lock**

If a frame is terminated early due to a not-acknowledge error (NACK flag), SMBus timeout error (TOUT flag) or master code acknowledge error (MACK flag), a lock is set on the Transmit FIFO preventing any new frame from being sent until it is cleared. This allows clearing the FIFO if needed, reset DMAC channels, etc., without any risk.

The LOCK bit in the TWIHS\_SR is used to check the state of the Transmit FIFO lock.

The Transmit FIFO lock can be cleared setting the TXFLCLR bit to '1' in the TWIHS\_CR.

## **FIFO Pointer Error**

In some specific cases, it is possible to generate a FIFO pointer error.

• Transmit FIFO:

If the Transmit FIFO is full and a write access is performed on the TWIHS\_THR, it will generate a Transmit FIFO pointer error and set the TXFPTEF flag in TWIHS\_FSR.

In Multiple Data mode, if the number of data written in the TWIHS\_THR (according to the register access size) is bigger than the Transmit FIFO free space, it will generate a Transmit FIFO pointer error and set the TXFPTEF flag in TWIHS\_FSR.

• Receive FIFO:

In Multiple Data mode, if the number of data read in the TWIHS\_RHR (according to the register access size) is bigger than the number of unread data in the Receive FIFO, it will generate a Receive FIFO pointer error and set the RXFPTEF flag in TWIHS\_FSR.

Pointer error should not happen if FIFO state is checked before writing/reading in TWIHS\_THR/TWIHS\_RHR. FIFO state can be checked either with TXRDY, RXRDY, TXFL or RXFL. When a pointer error occurs, other FIFO flags might not behave as expected; their state should be ignored.

If a Transmit or Receive pointer error occurs, a software reset must be performed using the SWRST bit in the TWIHS\_CR. Note that issuing a software while transmitting might leave a slave in an unknown state holding the TWD line. In such case, a Bus Clear Command will allow to make the slave release the TWD line (the first frame sent afterwards might not be received properly by the slave).

## **FIFO Thresholds**

Each Transmit and Receive FIFO includes a threshold feature used to set a flag and an interrupt when a FIFO threshold is crossed. Thresholds are defined as a number of data in the FIFO, and the FIFO state (TXFL or RXFL) represents the number of data currently in the FIFO.

• Transmit FIFO:

The Transmit FIFO threshold can be set using the TXFTHRES field in TWIHS\_FMR. Each time the Transmit FIFO goes from the 'above threshold' to the 'equal or below threshold' state, the TXFTHF flag in TWIHS\_FSR is set. This enables the application to know that the Transmit FIFO reached the defined threshold and to refill it before it becomes empty.

• Receive FIFO:

The Receive FIFO threshold can be set using the RXFTHRES field in TWIHS\_FMR. Each time the Receive FIFO goes from the 'below threshold' to the 'equal or above threshold' state, the RXFTHF flag in TWIHS\_FSR is set. This enables the application to know that the Receive FIFO reached the defined threshold and to read some data before it becomes full.

The TXFTHF and RXFTHF flags can be both configured to generate an interrupt using TWIHS\_FIER and TWIHS\_FIDR.

# **FIFO Flags**

FIFOs come with a set of flags which can be configured each to generate an interrupt through TWIHS\_FIER and TWIHS\_FIDR.

FIFO flags state can be read in TWIHS\_FSR. They are cleared on TWIHS\_FSR read.

## 43.6.4 Multimaster Mode

## 43.6.4.1 Definition

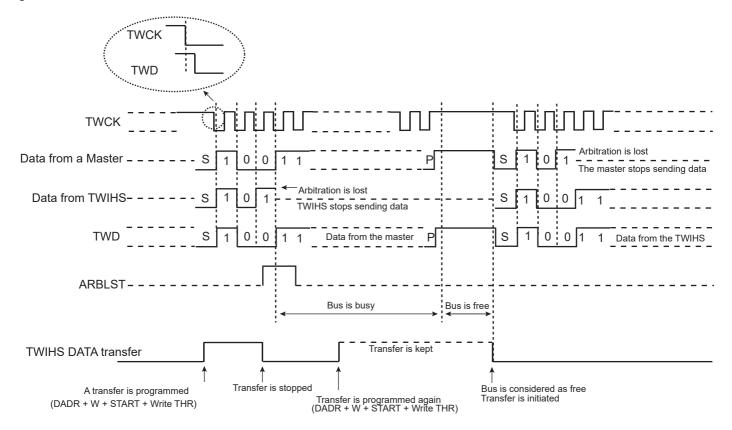

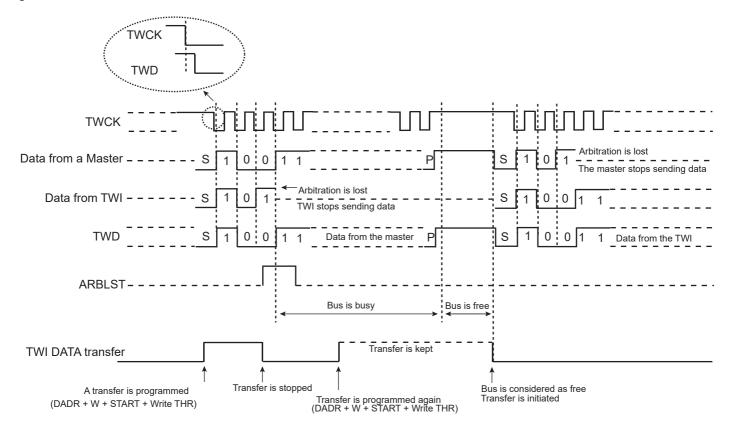

In Multimaster mode, more than one master may handle the bus at the same time without data corruption by using arbitration.

Arbitration starts as soon as two or more masters place information on the bus at the same time, and stops (arbitration is lost) for the master that intends to send a logical one while the other master sends a logical zero.

As soon as arbitration is lost by a master, it stops sending data and listens to the bus in order to detect a stop. When the stop is detected, the master that has lost arbitration may put its data on the bus by respecting arbitration.

Arbitration is illustrated in Figure 43-34.

## 43.6.4.2 Different Multimaster Modes

Two Multimaster modes may be distinguished:

- 1. The TWIHS is considered as a master only and is never addressed.

- 2. The TWIHS may be either a master or a slave and may be addressed.

Note: Arbitration in supported in both Multimaster modes.

## **TWIHS as Master Only**

In this mode, the TWIHS is considered as a master only (MSEN is always at one) and must be driven like a master with the ARBLST (Arbitration Lost) flag in addition.

If arbitration is lost (ARBLST = 1), the user must reinitiate the data transfer.

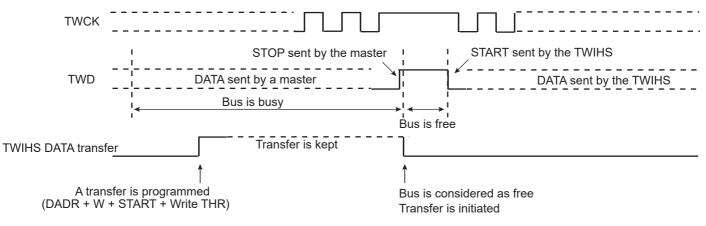

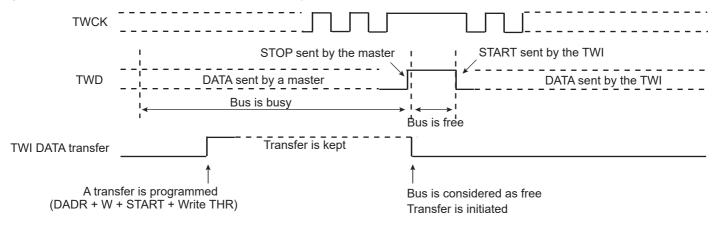

If starting a transfer (ex.: DADR + START + W + Write in THR) and if the bus is busy, the TWIHS automatically waits for a STOP condition on the bus to initiate the transfer (see Figure 43-33).

Note: The state of the bus (busy or free) is not indicated in the user interface.

## **TWIHS as Master or Slave**

The automatic reversal from master to slave is not supported in case of a lost arbitration.

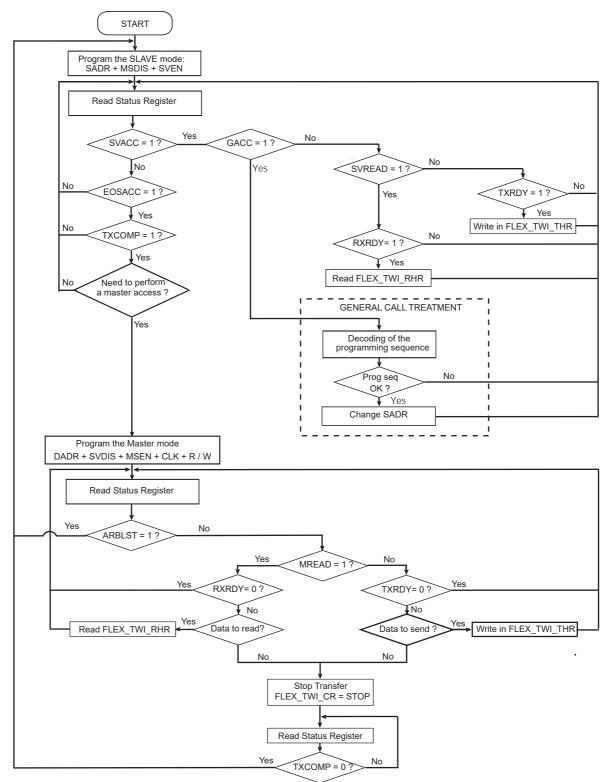

Then, in the case where TWIHS may be either a master or a slave, the user must manage the pseudo Multimaster mode described in the steps below:

- 1. Program the TWIHS in Slave mode (SADR + MSDIS + SVEN) and perform a slave access (if TWIHS is addressed).

- 2. If the TWIHS has to be set in Master mode, wait until TXCOMP flag is at 1.

- 3. Program the Master mode (DADR + SVDIS + MSEN) and start the transfer (ex: START + Write in THR).

- 4. As soon as the Master mode is enabled, the TWIHS scans the bus in order to detect if it is busy or free. When the bus is considered free, the TWIHS initiates the transfer.

- 5. As soon as the transfer is initiated and until a STOP condition is sent, the arbitration becomes relevant and the user must monitor the ARBLST flag.

- 6. If the arbitration is lost (ARBLST is set to 1), the user must program the TWIHS in Slave mode in case the master that won the arbitration needs to access the TWIHS.

- 7. If the TWIHS has to be set in Slave mode, wait until the TXCOMP flag is at 1 and then program the Slave mode.

- Note: If the arbitration is lost and the TWIHS is addressed, the TWIHS does not acknowledge, even if it is programmed in Slave mode as soon as ARBLST is set to 1. Then the master must repeat SADR.

## Figure 43-33. User Sends Data While the Bus is Busy

#### Figure 43-34. Arbitration Cases

The flowchart shown in Figure 43-35 gives an example of read and write operations in Multimaster mode.

Atmel

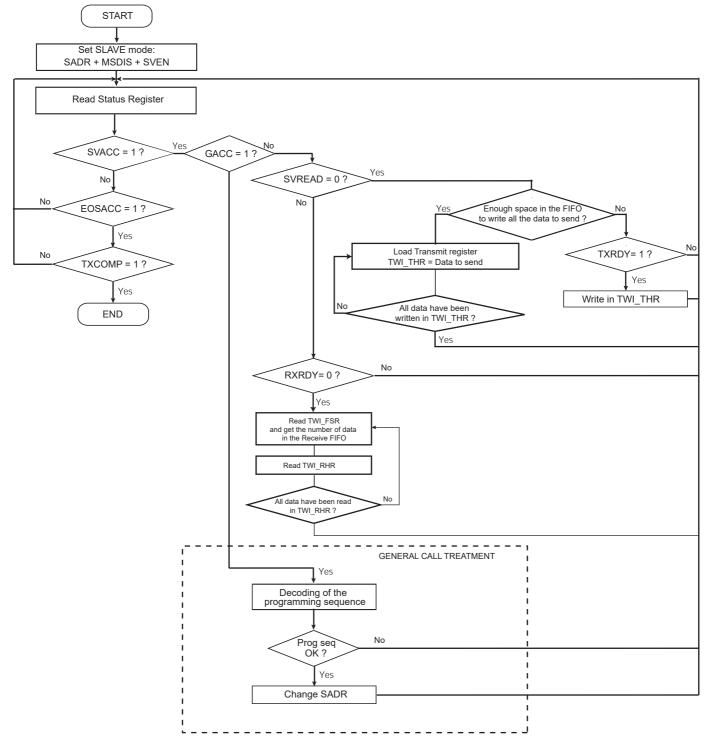

## 43.6.5 Slave Mode

## 43.6.5.1 Definition

Slave mode is defined as a mode where the device receives the clock and the address from another device called the master.

In this mode, the device never initiates and never completes the transmission (START, REPEATED\_START and STOP conditions are always provided by the master).

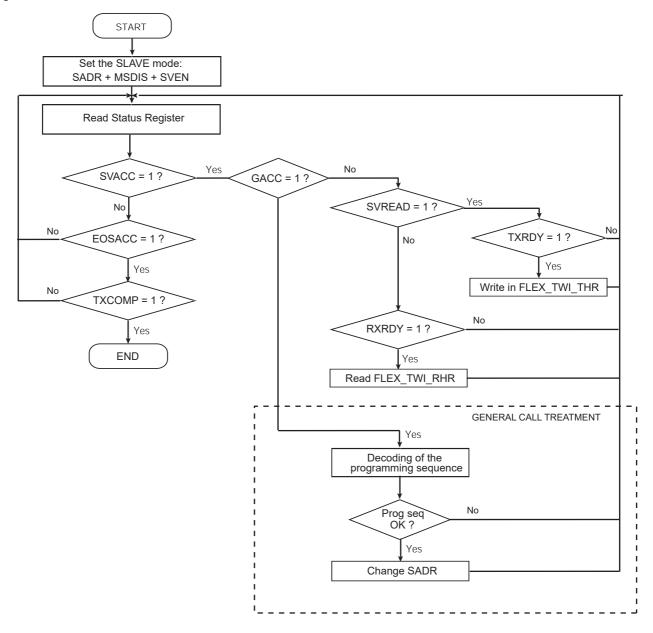

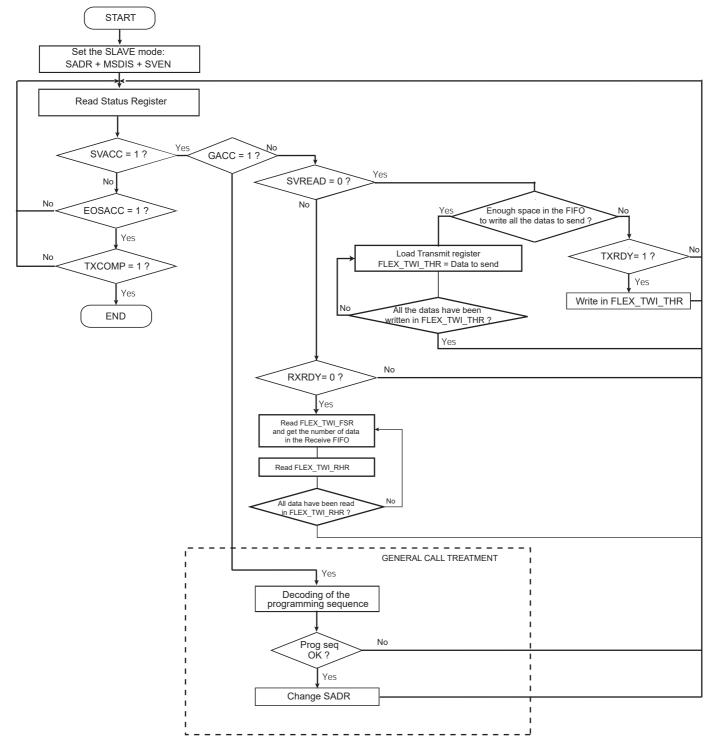

## 43.6.5.2 Programming Slave Mode

The following fields must be programmed before entering Slave mode:

- 1. TWIHS\_SMR.SADR: The slave device address is used in order to be accessed by master devices in Read or Write mode.

- 2. (Optional) TWIHS\_SMR.MASK can be set to mask some SADR address bits and thus allow multiple address matching.

- 3. TWIHS\_CR.MSDIS: Disables the Master mode.

- 4. TWIHS\_CR.SVEN: Enables the Slave mode.

As the device receives the clock, values written in TWIHS\_CWGR are ignored.

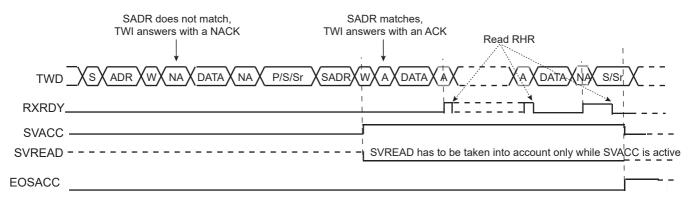

## 43.6.5.3 Receiving Data

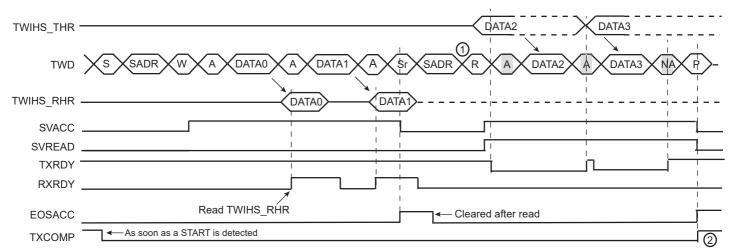

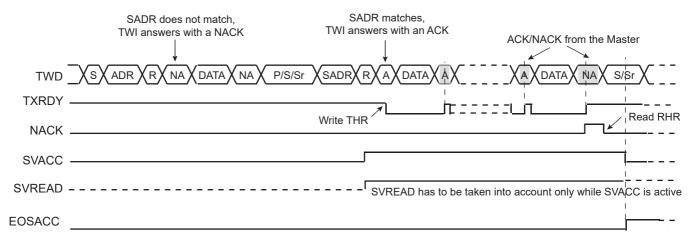

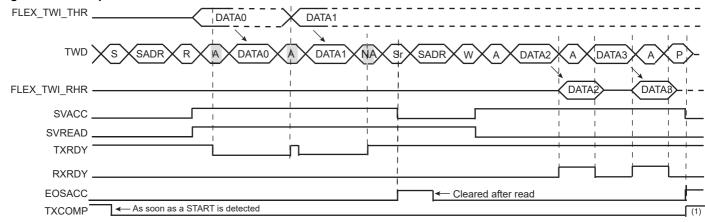

After a START or REPEATED START condition is detected, and if the address sent by the master matches the slave address programmed in the SADR (Slave Address) field, the SVACC (Slave Access) flag is set and SVREAD (Slave Read) indicates the direction of the transfer.

SVACC remains high until a STOP condition or a REPEATED START is detected. When such a condition is detected, the EOSACC (End Of Slave Access) flag is set.

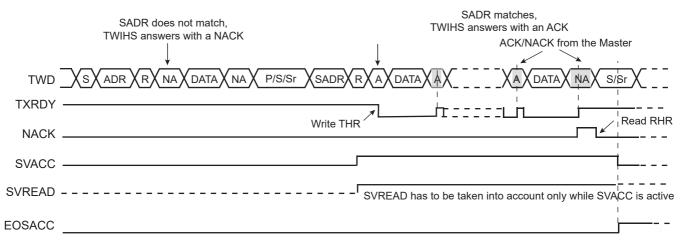

## **Read Sequence**

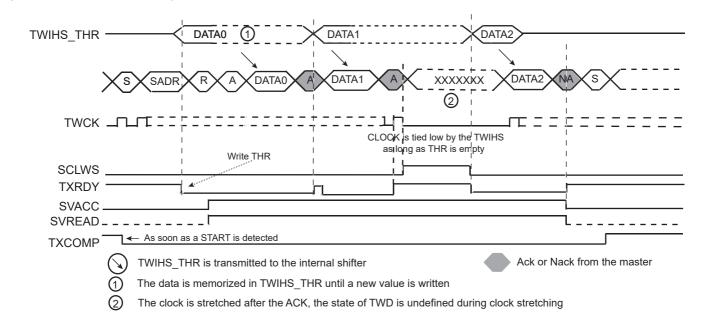

In the case of a read sequence (SVREAD is high), the TWIHS transfers data written in the TWIHS\_THR until a STOP condition or a REPEATED\_START + an address different from SADR is detected. Note that at the end of the read sequence TXCOMP (Transmission Complete) flag is set and SVACC reset.

As soon as data is written in the TWIHS\_THR, TXRDY (Transmit Holding Register Ready) flag is reset, and it is set when the internal shifter is empty and the sent data acknowledged or not. If the data is not acknowledged, the NACK flag is set.

Note that a STOP or a REPEATED START always follows a NACK.

To clear the TXRDY flag, first set the bit TWIHS\_CR.SVDIS, then set the bit TWIHS\_CR.SVEN.

See Figure 43-36.

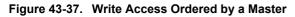

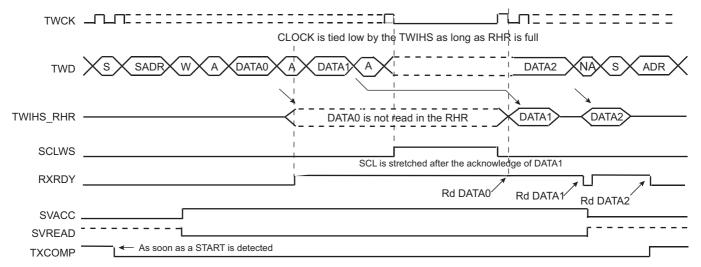

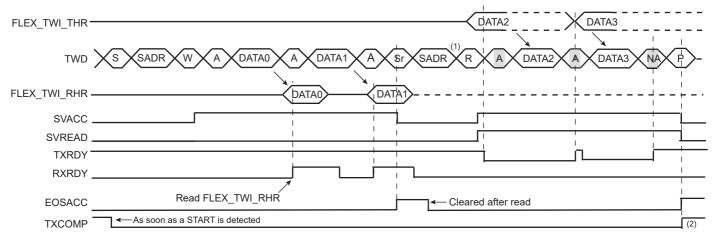

#### **Write Sequence**

In the case of a write sequence (SVREAD is low), the RXRDY (Receive Holding Register Ready) flag is set as soon as a character has been received in the TWIHS\_RHR. RXRDY is reset when reading the TWIHS\_RHR.

The TWIHS continues receiving data until a STOP condition or a REPEATED\_START + an address different from SADR is detected. Note that at the end of the write sequence, the TXCOMP flag is set and SVACC is reset.

See Figure 43-37.

#### **Clock Stretching Sequence**

If TWIHS\_THR or TWIHS\_RHR is not written/read in time, the TWIHS performs a clock stretching.

Clock stretching information is given by the SCLWS (Clock Wait State) bit.

See Figure 43-39 and Figure 43-40.

Note: Clock stretching can be disabled by configuring the SCLWSDIS bit in the TWIHS\_SMR. In that case, the UNRE and OVRE flags indicate an underrun (when TWIHS\_THR is not filled on time) or an overrun (when TWIHS\_RHR is not read on time).

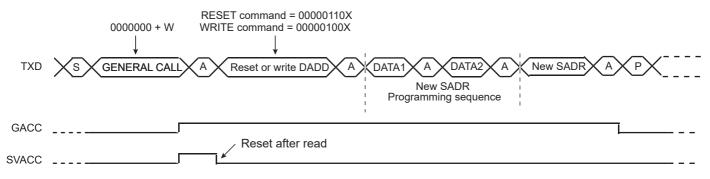

## **General Call**

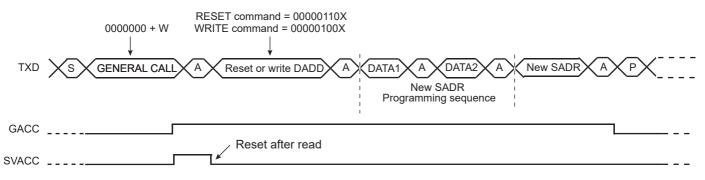

In the case where a GENERAL CALL is performed, the GACC (General Call Access) flag is set.

After GACC is set, the user must interpret the meaning of the GENERAL CALL and decode the new address programming sequence.

See Figure 43-38.

#### 43.6.5.4 Data Transfer

## **Read Operation**

The Read mode is defined as a data requirement from the master.

After a START or a REPEATED START condition is detected, the decoding of the address starts. If the slave address (SADR) is decoded, SVACC is set and SVREAD indicates the direction of the transfer.

Until a STOP or REPEATED START condition is detected, the TWIHS continues sending data loaded in the TWIHS\_THR.

If a STOP condition or a REPEATED START + an address different from SADR is detected, SVACC is reset.

Figure 43-36 describes the read operation.

#### Figure 43-36. Read Access Ordered by a Master

Notes: 1. When SVACC is low, the state of SVREAD becomes irrelevant.

2. TXRDY is reset when data has been transmitted from TWIHS\_THR to the internal shifter and set when this data has been acknowledged or non acknowledged.

## **Write Operation**

The Write mode is defined as a data transmission from the master.

After a START or a REPEATED START, the decoding of the address starts. If the slave address is decoded, SVACC is set and SVREAD indicates the direction of the transfer (SVREAD is low in this case).

Until a STOP or REPEATED START condition is detected, the TWIHS stores the received data in the TWIHS\_RHR.

If a STOP condition or a REPEATED START + an address different from SADR is detected, SVACC is reset.

Figure 43-37 describes the write operation.

- Notes: 1. When SVACC is low, the state of SVREAD becomes irrelevant.

- 2. RXRDY is set when data has been transmitted from the internal shifter to the TWIHS\_RHR and reset when this data is read.

# **General Call**

The general call is performed in order to change the address of the slave.

If a GENERAL CALL is detected, GACC is set.

After the detection of general call, decode the commands that follow.

In case of a WRITE command, decode the programming sequence and program a new SADR if the programming sequence matches.

Figure 43-38 describes the general call access.

## Figure 43-38. Master Performs a General Call

Note: This method enables the user to create a personal programming sequence by choosing the programming bytes and their number. The programming sequence has to be provided to the master.

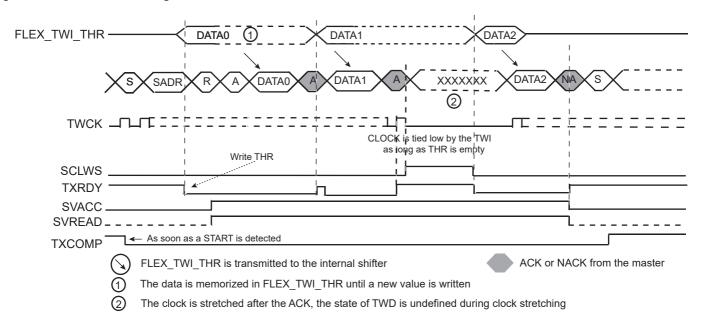

## **Clock Stretching**

In both Read and Write modes, it may occur that TWIHS\_THR/TWIHS\_RHR buffer is not filled/emptied before the transmission/reception of a new character. In this case, to avoid sending/receiving undesired data, a clock stretching mechanism is implemented.

Note: Clock stretching can be disabled by setting the SCLWSDIS bit in the TWIHS\_SMR. In that case the UNRE and OVRE flags indicate an underrun (when TWIHS\_THR is not filled on time) or an overrun (when TWIHS\_RHR is not read on time).

#### **Clock Stretching in Read Mode**

The clock is tied low if the internal shifter is empty and if a STOP or REPEATED START condition was not detected. It is tied low until the internal shifter is loaded.

Figure 43-39 describes the clock stretching in Read mode.

#### Figure 43-39. Clock Stretching in Read Mode

- Notes: 1. TXRDY is reset when data has been written in the TWIHS\_THR to the internal shifter and set when this data has been acknowledged or non acknowledged.

- At the end of the read sequence, TXCOMP is set after a STOP or after a REPEATED\_START + an address different from SADR.

- 3. SCLWS is automatically set when the clock stretching mechanism is started.

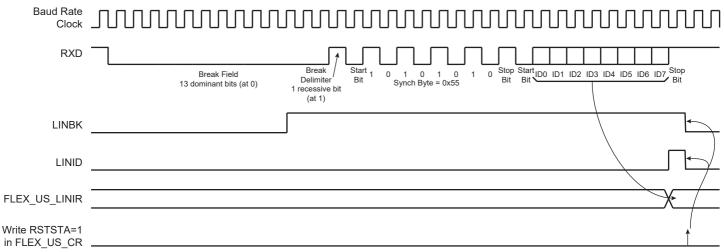

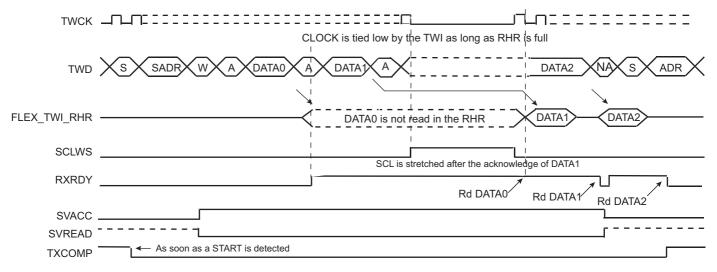

## **Clock Stretching in Write Mode**

The clock is tied low if the internal shifter and the TWIHS\_RHR is full. If a STOP or REPEATED\_START condition was not detected, it is tied low until TWIHS RHR is read.

Figure 43-40 describes the clock stretching in Write mode.

#### Figure 43-40. Clock Stretching in Write Mode

Notes: 1. At the end of the read sequence, TXCOMP is set after a STOP or after a REPEATED\_START + an address different from SADR.

2. SCLWS is automatically set when the clock stretching mechanism is started and automatically reset when the mechanism is finished.

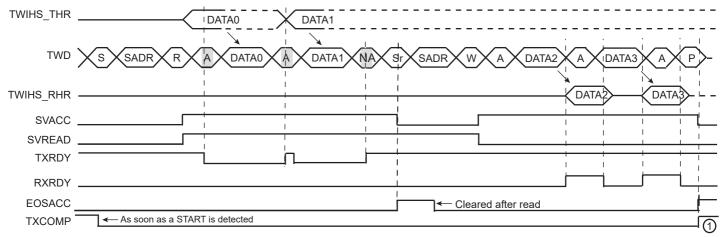

Reversal after a Repeated Start

## **Reversal of Read to Write**

The master initiates the communication by a read command and finishes it by a write command.

Figure 43-41 describes the REPEATED START and the reversal from Read mode to Write mode.

## Figure 43-41. Repeated Start and Reversal from Read Mode to Write Mode

Note: TXCOMP is only set at the end of the transmission. This is because after the REPEATED START, SADR is detected again.

# **Reversal of Write to Read**

The master initiates the communication by a write command and finishes it by a read command. Figure 43-42 describes the REPEATED START and the reversal from Write mode to Read mode.

# Figure 43-42. Repeated Start and Reversal from Write Mode to Read Mode

Notes: 1. In this case, if TWIHS\_THR has not been written at the end of the read command, the clock is automatically stretched before the ACK.

2. TXCOMP is only set at the end of the transmission. This is because after the REPEATED START, SADR is detected again.

## 43.6.5.5 Using the DMA Controller (DMAC) in Slave Mode

The use of the DMAC significantly reduces the CPU load.

# Data Transmit with the DMA in Slave Mode

The following procedure shows an example to transmit data with DMA.

- 1. Initialize the transmit DMA (memory pointers, transfer size, etc).

- 2. Configure the Slave mode.

- 3. Enable the DMA.

- 4. Wait for the DMA status flag indicating that the buffer transfer is complete.

- 5. Disable the DMA.

- 6. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

# Data Receive with the DMA in Slave Mode

The following procedure shows an example to transmit data with DMA where the number of characters to receive is known.

- 1. Initialize the DMA (channels, memory pointers, size, etc.).

- 2. Configure the Slave mode.

- 3. Enable the DMA.

- 4. Wait for the DMA status flag indicating that the buffer transfer is complete.

- 5. Disable the DMA.

- 6. (Only if peripheral clock must be disabled) Wait for the TXCOMP flag to be raised in TWIHS\_SR.

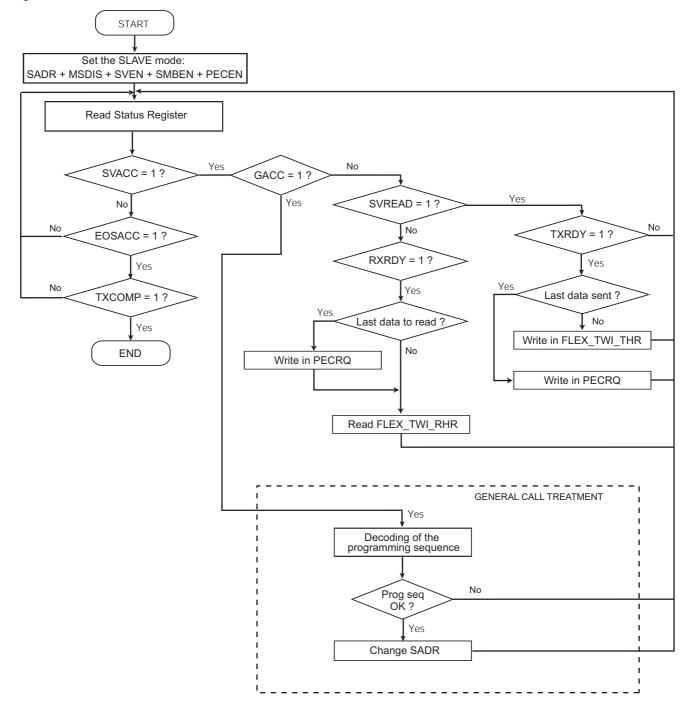

## 43.6.5.6 SMBus Mode

SMBus mode is enabled when a one is written to the SMEN bit in the TWIHS\_CR. SMBus mode operation is similar to I<sup>2</sup>C operation with the following exceptions:

- Only 7-bit addressing can be used.

- The SMBus standard describes a set of timeout values to ensure progress and throughput on the bus. These timeout values must be programmed into the TWIHS\_SMBTR.

- Transmissions can optionally include a CRC byte, called Packet Error Check (PEC).

- A set of addresses have been reserved for protocol handling, such as alert response address (ARA) and host header (HH) address. Address matching on these addresses can be enabled by configuring the TWIHS\_CR.

## Packet Error Checking

Each SMBus transfer can optionally end with a CRC byte, called the PEC byte. Writing a one to the PECEN bit in TWIHS\_CR will send/check the PEC field in the current transfer. The PEC generator is always updated on every bit transmitted or received, so that PEC handling on the following linked transfers is correct.

In Slave Receiver mode, the master calculates a PEC value and transmits it to the slave after all data bytes have been transmitted. Upon reception of this PEC byte, the slave compares it to the PEC value it has computed itself. If the values match, the data was received correctly, and the slave returns an ACK to the master. If the PEC values differ, data was corrupted, and the slave returns a NACK value. The PECERR bit in TWIHS\_SR is set automatically if a PEC error occurred.

In Slave Transmitter mode, the slave calculates a PEC value and transmits it to the master after all data bytes have been transmitted. Upon reception of this PEC byte, the master compares it to the PEC value it has computed itself. If the values match, the data was received correctly. If the PEC values differ, data was corrupted, and the master must take appropriate action.

See Section 43.6.5.10 "Slave Read Write Flowcharts" for detailed flowcharts.

## **Timeouts**

The TWIHS SMBus Timing Register (TWIHS\_SMBTR) configures the SMBus timeout values. If a timeout occurs, the slave leaves the bus. The TOUT bit is also set in TWIHS\_SR.

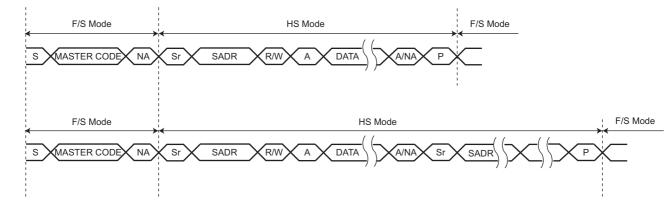

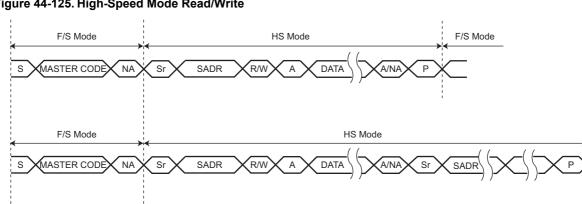

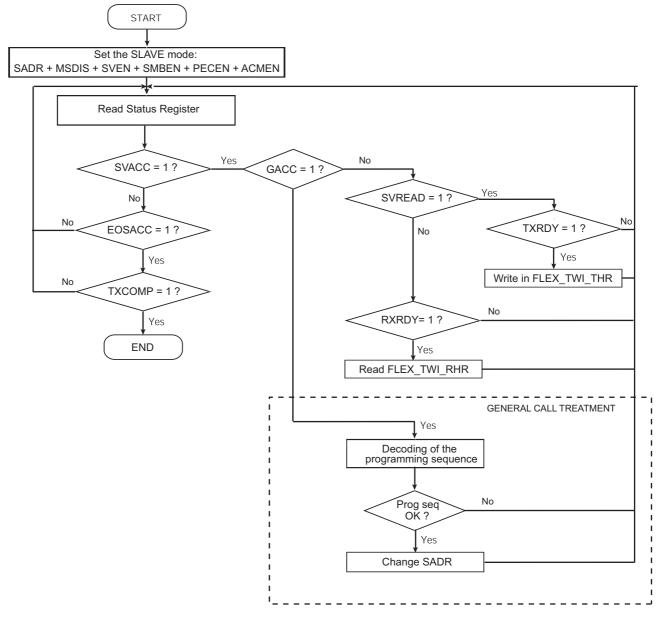

## 43.6.5.7 High-Speed Slave Mode

High-speed mode is enabled when a one is written to the HSEN bit in the TWIHS\_CR. Furthermore, the analog pad filter must be enabled, a one must be written to the PADFEN bit in the TWIHS\_FILTR and the FILT bit must be cleared. TWIHS High-speed mode operation is similar to TWIHS operation with the following exceptions:

- 1. A master code is received first at normal speed before entering High-speed mode period.

- 2. When TWIHS High-speed mode is active, clock stretching is only allowed after acknowledge (ACK), notacknowledge (NACK), START (S) or REPEATED START (Sr) (as consequence OVF may happen).

TWIHS High-speed mode allows transfers of up to 3.4 Mbit/s.

The TWIHS slave in High-speed mode requires that the peripheral clock runs at a minimum of 14 MHz if slave clock stretching is enabled (SCLWSDIS bit at '0'). If slave clock stretching is disabled (SCLWSDIS bit at '1'), the peripheral clock must run at a minimum of 11 MHz (assuming the system has no latency).

- Note: When slave clock stretching is disabled, the TWIHS\_RHR must always be read before receiving the next data (MASTER write frame). It is strongly recommended to use either the polling method on the RXRDY flag in TWIHS\_SR, or the DMA. If the receive is managed by an interrupt, the TWIHS interrupt priority must be set to the right level and its latency minimized to avoid receive overrun.

- Note: When slave clock stretching is disabled, the TWIHS\_THR must be filled with the first data to send before the beginning of the frame (MASTER read frame). It is strongly recommended to use either the polling method on the TXRDY flag in TWIHS\_SR, or the DMA. If the transmit is managed by an interrupt, the TWIHS interrupt priority must be set to the right level and its latency minimized to avoid transmit underrun.

## **Read/Write Operation**

A TWIHS high-speed frame always begins with the following sequence:

- 1. START condition (S)

- 2. Master Code (0000 1XXX)

- 3. Not-acknowledge (NACK)

When the TWIHS is programmed in Slave mode and TWIHS High-speed mode is activated, master code matching is activated and internal timings are set to match the TWIHS High-speed mode requirements.

# Figure 43-43. High-Speed Mode Read/Write

# Usage

TWIHS High-speed mode usage is the same as the standard TWIHS (See Section 43.6.3.14 "Read/Write Flowcharts").

## 43.6.5.8 Alternative Command

In Slave mode, Alternative Command mode is useful when SMBus mode is enabled to send or check the PEC byte.

Alternative Command mode is enabled by setting the ACMEN bit of the TWIHS Control Register and the transfer is configured in TWIHS\_ACR.

For a combined transfer with PEC, only the NPEC bit in TWIHS\_ACR must be set as the PEC byte is sent once at the end of the frame.

See Section 43.6.5.10 "Slave Read Write Flowcharts" for detailed flowcharts.

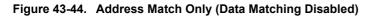

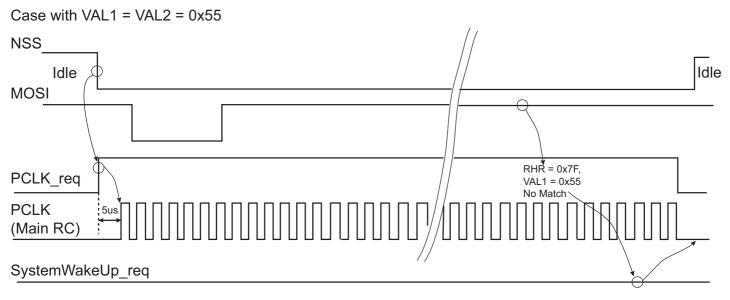

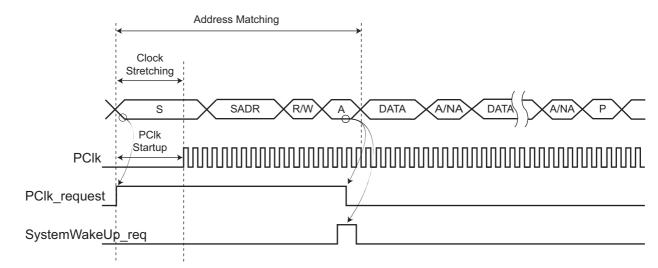

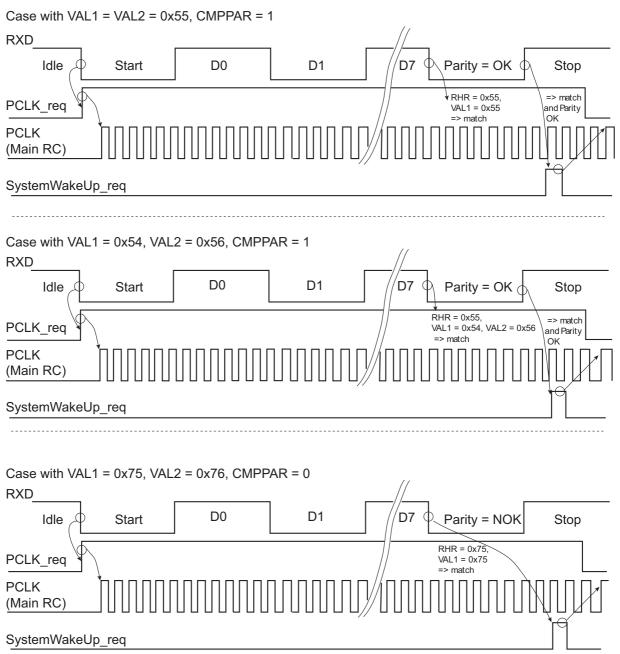

## 43.6.5.9 Asynchronous Partial Wakeup (SleepWalking)

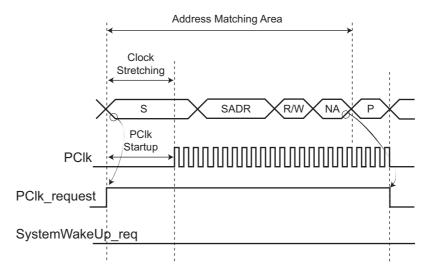

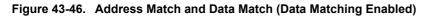

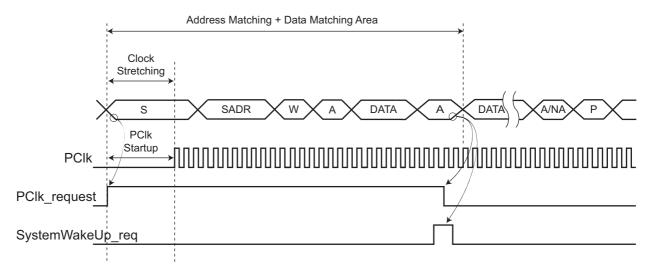

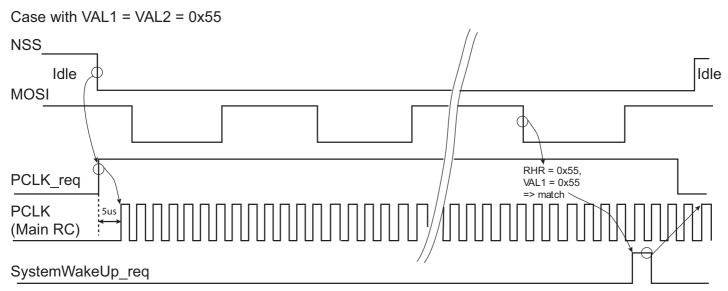

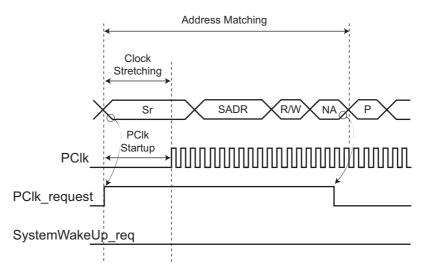

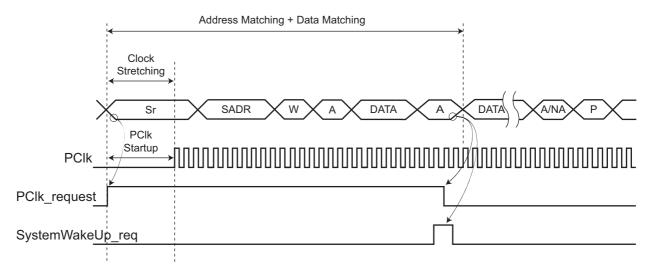

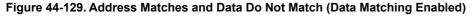

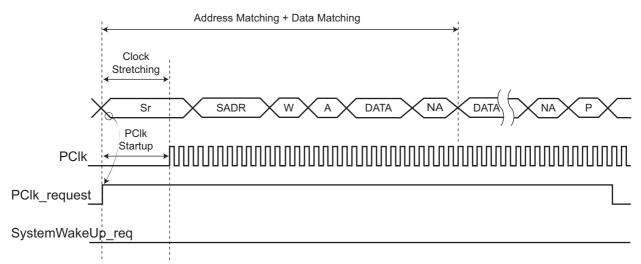

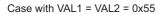

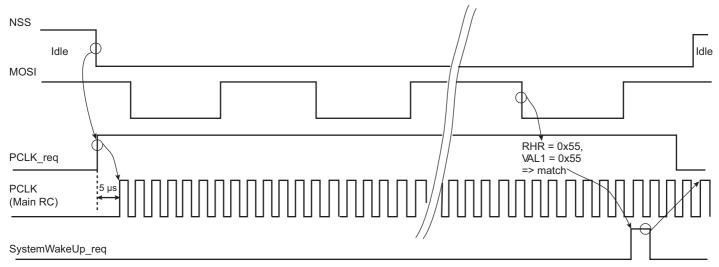

The TWIHS includes an asynchronous start condition detector. It is capable of waking the device up from a Sleep mode upon an address match (and optionally an additional data match), including Sleep modes where the TWIHS peripheral clock is stopped.

After detecting the START condition on the bus, the TWIHS stretches TWCK until the TWIHS peripheral clock has started. The time required for starting the TWIHS depends on which Sleep mode the device is in. After the TWIHS peripheral clock has started, the TWIHS releases its TWCK stretching and receives one byte of data (slave address) on the bus. At this time, only a limited part of the device, including the TWIHS module, receives a clock, thus saving power. If the address phase causes a TWIHS address match (and, optionally, if the first data byte causes data match as well), the entire device is woken up and normal TWIHS address matching actions are performed. Normal TWIHS transfer then follows. If the TWIHS is not addressed (or if the optional data match fails), the TWIHS peripheral clock is automatically stopped and the device returns to its original Sleep mode.

The TWIHS has the capability to match on more than one address. The SADR1EN, SADR2EN and SADR3EN bits in TWIHS\_SMR enable address matching on additional addresses which can be configured through SADR1, SADR2 and SADR3 fields in the TWIHS\_SWMR. The SleepWalking matching process can be extended to the first received data byte if DATAMEN bit in TWIHS\_SMR is set and, in this case, a complete matching includes address matching and first received data matching. The field DATAM in TWIHS\_SWMR configures the data to match on the first received byte.

When the system is in Active mode and the TWIHS enters Asynchronous Partial Wakeup mode, the flag SVACC must be programmed as the unique source of the TWIHS interrupt and the data match comparison must be disabled.