# High speed CAN Transceivers Application Note

TLE6250G

TLE6250GV33

TLE6251DS

TLE6251G

Author : Stéphane Fraissé

Automotive Power

Never stop thinking

Edition 2006-04-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2006. All Rights Reserved.

#### Attention please!

The information given in this Data Sheet shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# High speed CAN

| Revisior          | n History: | 2006-04-01                         |

|-------------------|------------|------------------------------------|

| Previous Version: |            | none                               |

| Page              | Subjects ( | major changes since last revision) |

|                   |            |                                    |

|                   |            |                                    |

|                   |            |                                    |

|                   |            |                                    |

|                   |            |                                    |

|                   |            |                                    |

| <b>1</b><br>1.1<br>1.2 | Introduction. Recessive Level. Dominant level.                                                                                                                                                               | 2    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.2                    | Driver symmetry.                                                                                                                                                                                             |      |

| 2                      | In Vehicle Network.                                                                                                                                                                                          |      |

| 2.1                    | Type of supplies in the vehicle.                                                                                                                                                                             |      |

| 2.1.1                  | Unsupplied modules in the parked car. (Clamp 15)                                                                                                                                                             |      |

| 2.1.2<br>2.1.3         | Supplied modules in the parked car. (Clamp 30)                                                                                                                                                               |      |

| 2.1.3                  | Mixed network.                                                                                                                                                                                               |      |

| 2.2.1                  | High current applications.                                                                                                                                                                                   |      |

| 2.2.1                  | Low current application.                                                                                                                                                                                     |      |

| 2.2.2                  | The Transceiver in the automotive environment.                                                                                                                                                               |      |

| 2.3.1                  | Low battery voltage.                                                                                                                                                                                         |      |

| 2.3.1.1                | TLE6250G.                                                                                                                                                                                                    |      |

| 2.3.1.2                | TLE6251DS.                                                                                                                                                                                                   |      |

| 2.3.1.3                | TLE6251G                                                                                                                                                                                                     |      |

| 2.3.2                  | High battery voltage.                                                                                                                                                                                        | 7    |

| 2.3.2.1                | TLE6250G / TLE6251DS                                                                                                                                                                                         | 8    |

| 2.3.2.2                | TLE6251G                                                                                                                                                                                                     |      |

| 2.3.3                  | Reverse polarity.                                                                                                                                                                                            |      |

| 2.3.3.1                | TLE6250G / TLE6251DS.                                                                                                                                                                                        |      |

| 2.3.3.2                | TLE6251G                                                                                                                                                                                                     |      |

| 2.3.4                  | Short circuit on the bus.                                                                                                                                                                                    |      |

| 2.3.4.1                | Termination resistors case in short circuit to Vbat.                                                                                                                                                         |      |

| 2.3.5                  | Temperature.                                                                                                                                                                                                 |      |

| 2.3.6                  | Ground shift.                                                                                                                                                                                                |      |

| 2.3.7                  | Loss of ground.                                                                                                                                                                                              |      |

| 2.3.8                  | Loss of Battery.                                                                                                                                                                                             |      |

| 3                      | Power management, transceiver supply.                                                                                                                                                                        |      |

| 3.1                    | TLE6250G                                                                                                                                                                                                     |      |

| 3.1.1                  | TLE6250G in unsupplied mode.                                                                                                                                                                                 |      |

| 3.1.2                  | TLE6250G in inhibit mode.                                                                                                                                                                                    |      |

| 3.1.3                  | TLE6250G in normal mode.                                                                                                                                                                                     |      |

| 3.1.4<br>3.1.4.1       | TLE6250G in fault condition.                                                                                                                                                                                 |      |

| 3.1.4.1                | Average maximum current in fault condition.       Peak maximum current and decoupling capacitor.         Peak maximum current and decoupling capacitor.       Peak maximum current and decoupling capacitor. |      |

| 3.1.4.2                | TLE6250G junction temperature.                                                                                                                                                                               |      |

| 3.2                    | TLE6251DS                                                                                                                                                                                                    |      |

| 3.2.1                  | TLE6251DS in unsupplied mode.                                                                                                                                                                                |      |

| 3.2.2                  | TLE6251DS in stand by mode.                                                                                                                                                                                  |      |

| 3.2.3                  | TLE6251DS in normal mode.                                                                                                                                                                                    |      |

| 3.2.4                  | TLE6251DS in fault condition.                                                                                                                                                                                |      |

| 3.2.5                  | TLE6251DS junction temperature.                                                                                                                                                                              | . 15 |

| 3.3                    | TLE6251G.                                                                                                                                                                                                    |      |

| 3.3.1                  | TLE6251G in unsupplied mode.                                                                                                                                                                                 | . 16 |

| 3.3.2                  | TLE6251G in sleep mode                                                                                                                                                                                       | . 16 |

| 3.3.3                  | TLE6251G in Stand by mode.                                                                                                                                                                                   |      |

| 3.3.4                  | TLE6251G in receive only mode.                                                                                                                                                                               |      |

| 3.3.5                  | TLE6251G in normal mode                                                                                                                                                                                      | . 17 |

| 3.3.6          | TLE6251G in fault condition.                                      |    |

|----------------|-------------------------------------------------------------------|----|

| 3.3.7          | TLE6251G junction temperature.                                    |    |

| 3.3.8          | Choice of the voltage regulator.                                  | 17 |

| 4              | Interface with micro controller.                                  | 18 |

| 4.1            | TLE6250G/GV33                                                     | 18 |

| 4.1.1          | Pin Vcc                                                           | 18 |

| 4.1.2          | Pin RM (only for the TLE6250G version).                           | 19 |

| 4.1.3          | Pin INH.                                                          | 19 |

| 4.1.4          | Pin V33 or Vio (only for TLE6250GV33).                            | 19 |

| 4.1.5          | Pin TxD.                                                          | 20 |

| 4.1.6          | Pin RxD                                                           | 20 |

| 4.2            | TLE6251DS                                                         | 22 |

| 4.2.1          | Pin STB                                                           | 22 |

| 4.2.2          | Pin TxD.                                                          | 22 |

| 4.2.2.1        | Hardware description.                                             | 22 |

| 4.2.2.2        | Time out function.                                                | 22 |

| 4.2.2.3        | Time out function. Baud rate limitation.                          | 23 |

| 4.2.3          | Pin RxD.                                                          | 23 |

| 4.2.3.1        | Hardware description.                                             | 23 |

| 4.2.3.2        | Wake up behavior.                                                 | 23 |

| 4.2.3.3        | Delay from stand by to normal mode.                               | 24 |

| 4.3            | TLE6251G.                                                         |    |

| 4.3.1          | Pin TxD.                                                          | 25 |

| 4.3.2          | Pin RxD.                                                          | 25 |

| 4.3.3          | Pin EN                                                            | 25 |

| 4.3.4          | Pin NSTB.                                                         | 25 |

| 4.3.5          | Pin VµC                                                           | 26 |

| 4.3.5.1        | $V\mu C$ pin's maximum current.                                   | 26 |

| 4.3.5.2        | Vµc under voltage detection.                                      |    |

| 4.3.6          | pin Vcc                                                           | 27 |

| 4.3.7          | Pin NERR.                                                         | 27 |

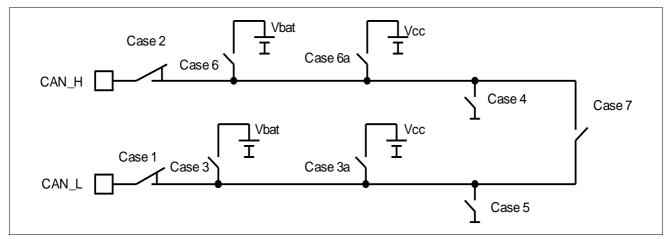

| 4.3.7.1        | Possible bus errors cases.                                        | 27 |

| 4.3.7.2        | Pin NERR in short circuit.                                        | 27 |

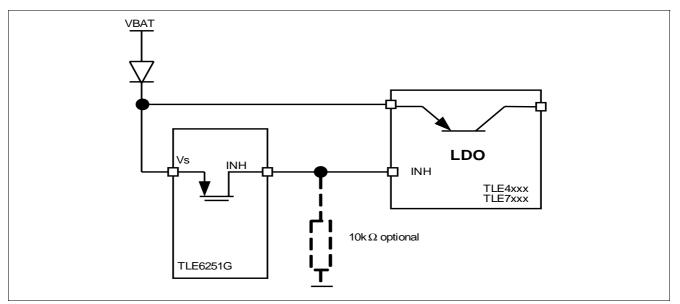

| 4.3.8          | Pin INH.                                                          | 27 |

| 4.3.8.1        | Pin INH purpose.                                                  | 27 |

| 4.3.8.2        | Pin INH power capability.                                         |    |

| 4.3.8.3        | Pin INH driving the INH input of an Voltage regulator.            |    |

| 4.3.8.4        | Wake up timing with pin INH.                                      |    |

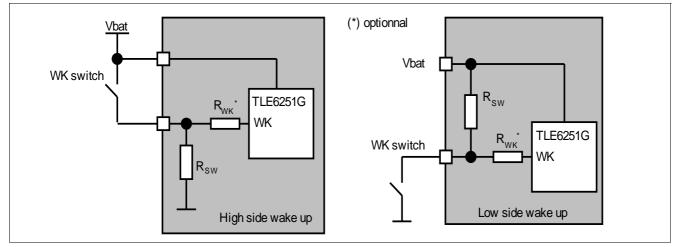

| 4.3.9          | pin WK                                                            | 29 |

| 4.3.10         | . Software issues consideration for TLE6251G.                     |    |

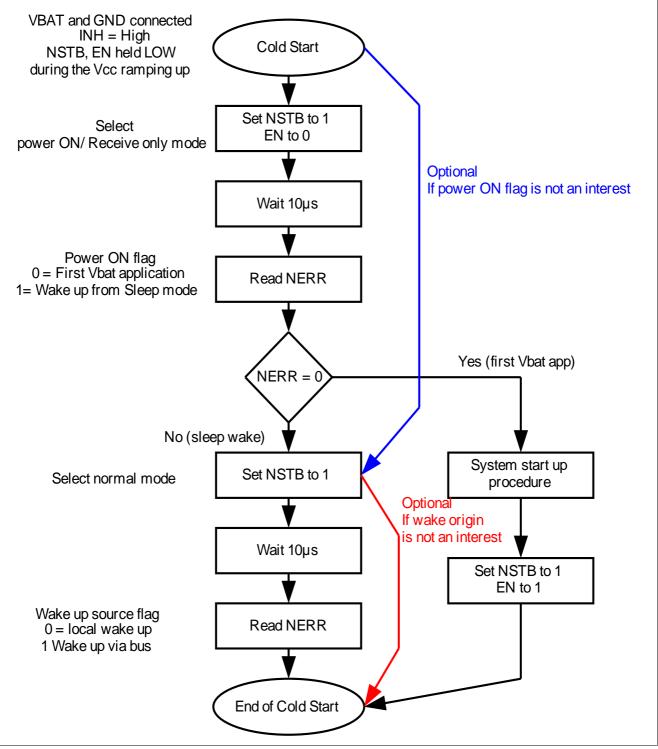

| 4.3.10.1       | Cold start.                                                       |    |

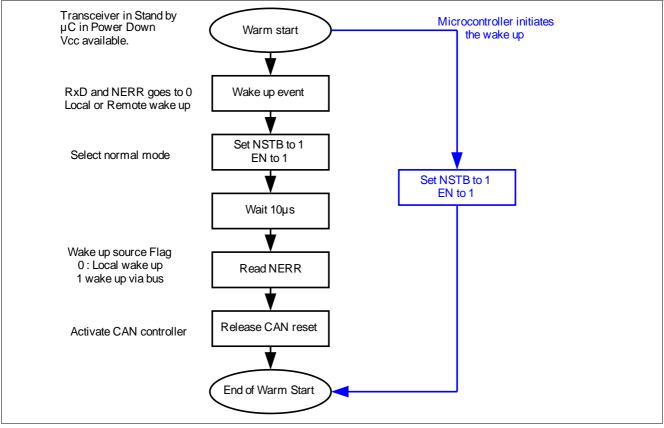

| 4.3.10.2       | Hot start.                                                        |    |

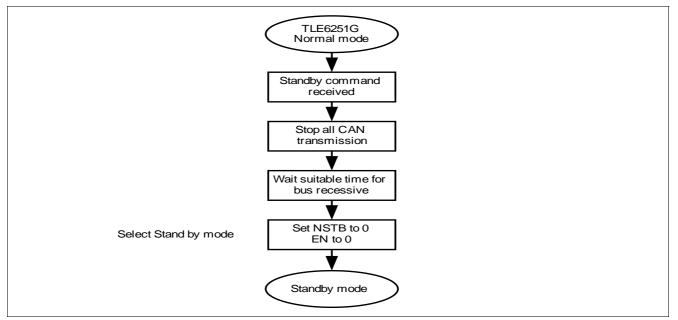

| 4.3.10.3       | Enter the Standby mode.                                           |    |

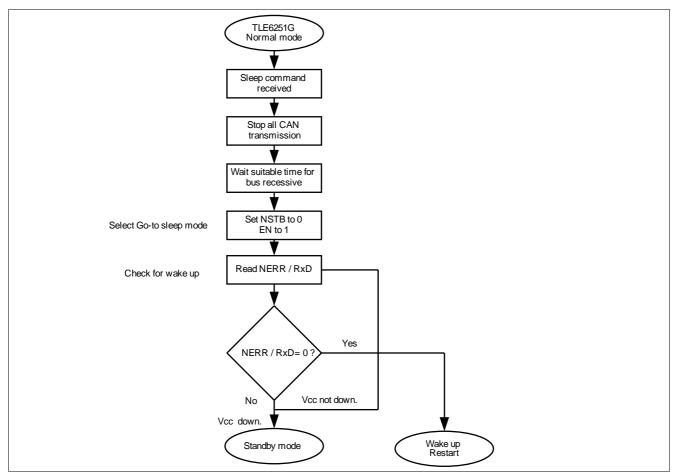

| 4.3.10.4       | Enter the Sleep mode.                                             |    |

| 5              | Bus pins. Terminations concepts.                                  |    |

| <b>5</b> .1    | Termination resistors.                                            |    |

| 5.1<br>5.2     |                                                                   |    |

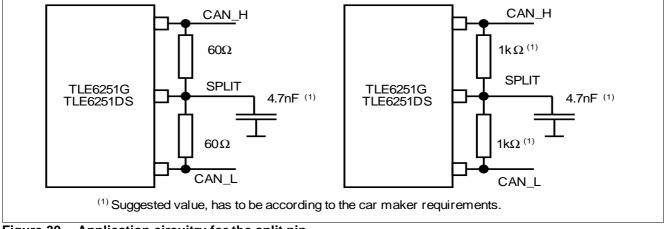

| 5.∠<br>5.2.1   | Split pin.                                                        |    |

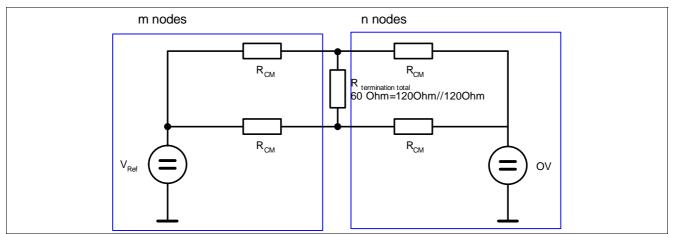

| 5.2.1<br>5.2.2 | Recessive voltage in a mixed Clamp 15 / 30 network, without SPLIT |    |

|                |                                                                   |    |

| 5.3            | CAN_H / CAN_L                                                     | 40 |

| <ul> <li>6</li> <li>6.1</li> <li>6.1.1</li> <li>6.1.2</li> <li>6.1.3</li> <li>6.1.4</li> <li>6.2</li> <li>6.3.1</li> <li>6.3.2</li> <li>6.3.3</li> <li>6.4</li> <li>6.5</li> <li>7</li> <li>7.1</li> <li>7.2</li> <li>7.2.1</li> <li>7.2.2</li> <li>7.3</li> <li>7.3.1</li> <li>7.3.1.2</li> <li>7.3.2.1</li> <li>7.3.2.2</li> <li>7.3.2.3</li> <li>7.3.2.4</li> <li>7.3.3</li> <li>7.4</li> </ul> | ESD Aspects.         ESD tests definition.         Human Body Model test. (MIL-STD 883).         Gun test. (IEC 61000-4-2).         Charged Device Model (DDM).         Machine Model (MM).         ESD protection.         Modules under ESD gun test.         Device without any external protection circuitry.         ESD level reached with a choke coil.         ESD level reached with a choke coil and ESD diode or varistor.         PCB layout.         Conclusion.         EMC aspect.         EM Immunity against transcients.         EM Immunity against RF disturbances.         The Stripline test. ISO 11452-5.         The Bulk Current Injection test. (BCI). ISO 11452-4.         Infineon transceivers in the EMI disturbances.         Immunity against transcients.         Immunity against transcients.         Damage test.         Malfunction test.         Immunity against RF disturbances.         Immunity against RF disturbances.         BCI test limitation         Principle of the DPI test.         Results of Infineon's transceiver under DPI test.         Improvement of the DPI result. Use of choke coil.         Emission         Conclusion. | $\begin{array}{c} 41\\ 41\\ 42\\ 43\\ 43\\ 44\\ 45\\ 47\\ 49\\ 49\\ 49\\ 49\\ 49\\ 49\\ 50\\ 50\\ 51\\ 52\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55\\ 55$ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8                                                                                                                                                                                                                                                                                                                                                                                                  | Products summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                         |

| 9                                                                                                                                                                                                                                                                                                                                                                                                  | References.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57                                                                                                                                                      |

| Figure 1  | Typical high speed CAN signal                                                                                                        | 2  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | Dominant level                                                                                                                       |    |

| Figure 2  | Common mode voltage definition.                                                                                                      |    |

| -         | -                                                                                                                                    |    |

| Figure 4  | Typical Clamp 15 application                                                                                                         |    |

| Figure 5  | Typical Clamp 30 application                                                                                                         |    |

| Figure 6  | Mixed CL15 and CL30 network                                                                                                          |    |

| Figure 7  | Typical high current application                                                                                                     |    |

| Figure 8  | Undervoltage detection mechanism for Vs.                                                                                             |    |

| Figure 9  | Current in the termination resistors in case of short circuit to Vbat.                                                               |    |

| Figure 10 | System with one ground shift event                                                                                                   |    |

| Figure 11 | Typical DC ground shift signal.                                                                                                      |    |

| Figure 12 | CAN signals with AC ground shift.                                                                                                    |    |

| Figure 13 | Loss of ground with inductive load                                                                                                   |    |

| Figure 14 | Buffer capacitor in function of the baud rate.                                                                                       |    |

| Figure 15 | Quiescent current computation in stand by mode                                                                                       |    |

| Figure 16 | Quiescent current computation in sleep mode, with and without inhibit functionnality                                                 |    |

| Figure 17 | Block diagram of TLE6250G/ TLE6250GV33                                                                                               |    |

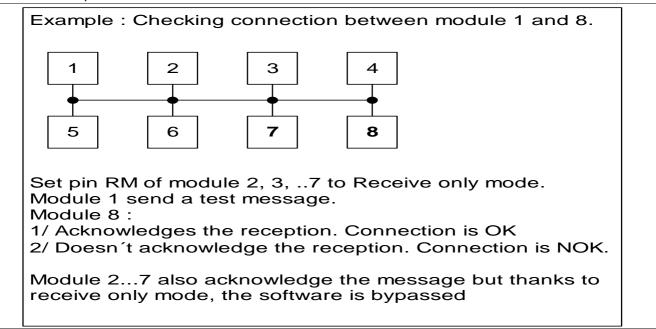

| Figure 18 | Module connection verification, using receive only mode functionnality                                                               |    |

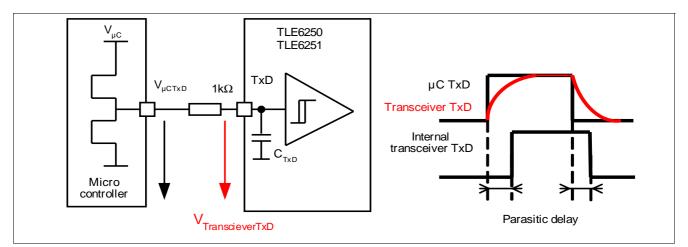

| Figure 19 | parasitic delay in case of serial resistor                                                                                           |    |

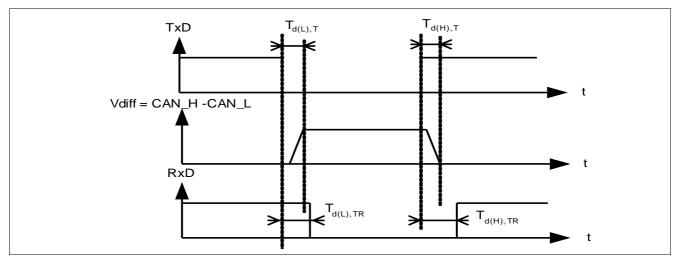

| Figure 20 | receiver timing                                                                                                                      |    |

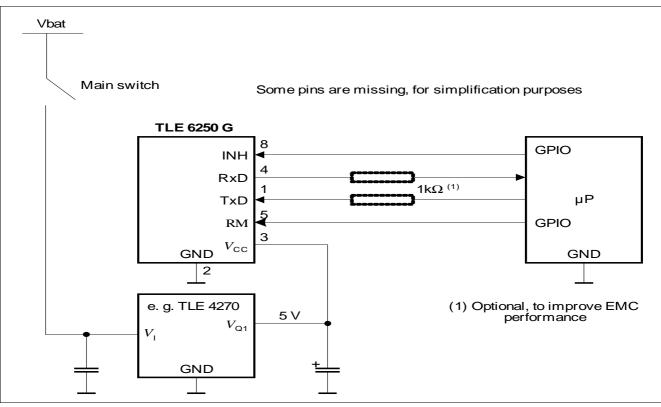

| Figure 21 | Typical application for TLE6250G.                                                                                                    |    |

| Figure 22 | Typical application for TLE6250GV33                                                                                                  | 21 |

| Figure 23 | Pin out comparison TLE6251DS and TLE6250G                                                                                            |    |

| Figure 24 | Permanent dominant time out feature                                                                                                  |    |

| Figure 25 | Wake up timing.                                                                                                                      | 23 |

| Figure 26 | Delay from stand by to normal mode timing                                                                                            | 24 |

| Figure 27 | Typical application for the TLE6251DS                                                                                                | 24 |

| Figure 28 | Pin out comparison TLE6251DS and TLE6251G                                                                                            | 25 |

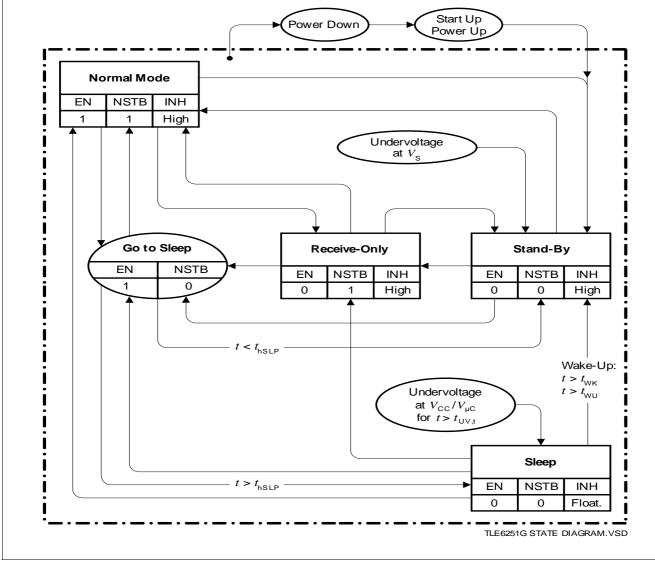

| Figure 29 | TLE6251G Mode state diagram                                                                                                          | 26 |

| Figure 30 | Possible failure cases failures on the bus word list. (According ISO 11898)                                                          | 27 |

| Figure 31 | Circuitry for the INH output                                                                                                         | 28 |

| Figure 32 | Possible wake up circuitries                                                                                                         | 29 |

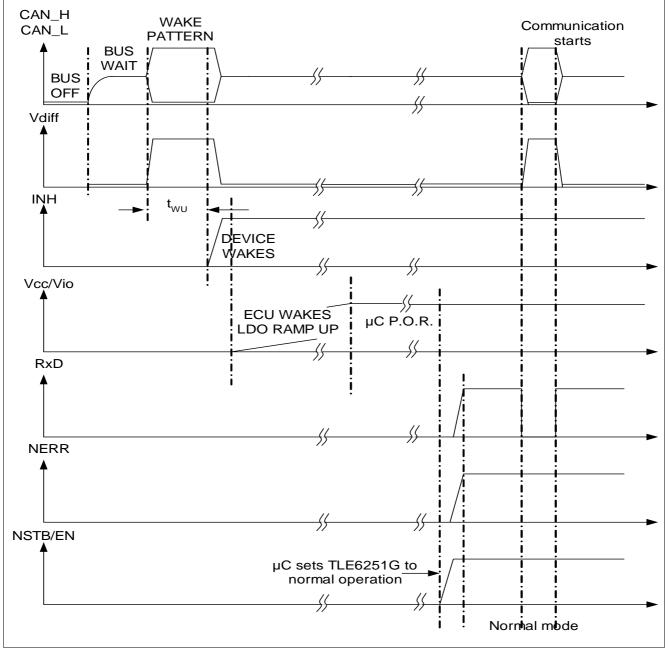

| Figure 33 | Wake up timing with INH function. Cold start.                                                                                        |    |

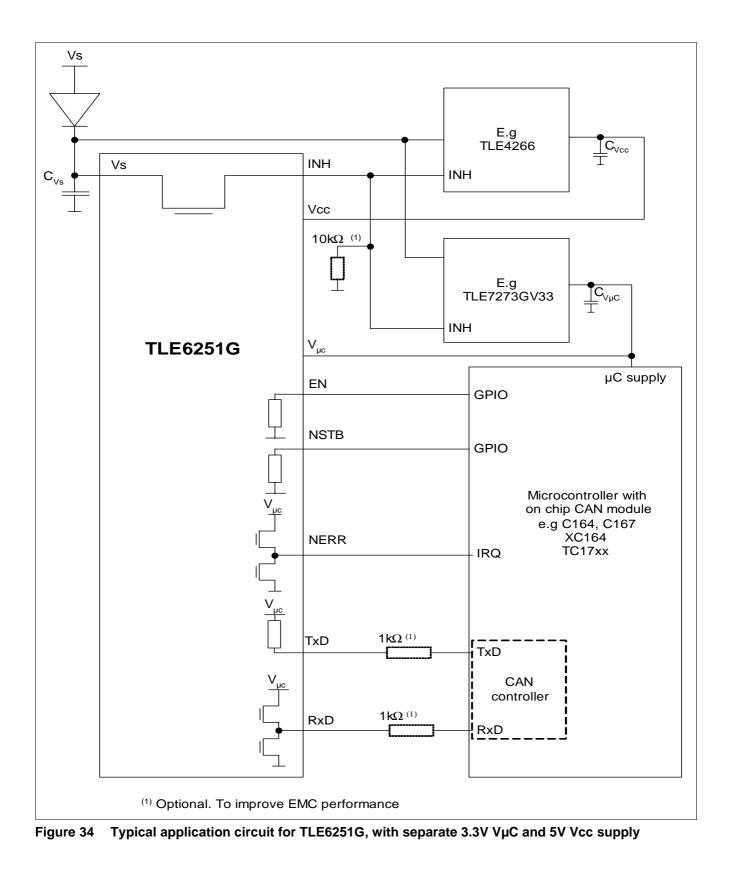

| Figure 34 | Typical application circuit for TLE6251G, with separate 3.3V VµC and 5V Vcc supply                                                   |    |

| Figure 35 | Flow diagram for an ECU cold start                                                                                                   |    |

| Figure 36 | Flow diagram for an ECU warm start                                                                                                   |    |

| Figure 37 | Flow diagram to enter Stand by mode                                                                                                  |    |

| Figure 38 | Flow diagram to enter Sleep mode                                                                                                     |    |

| Figure 39 | Application circuitry for the split pin.                                                                                             |    |

| Figure 40 | Equivalent electrical schematic for a mixed network without split pin.                                                               |    |

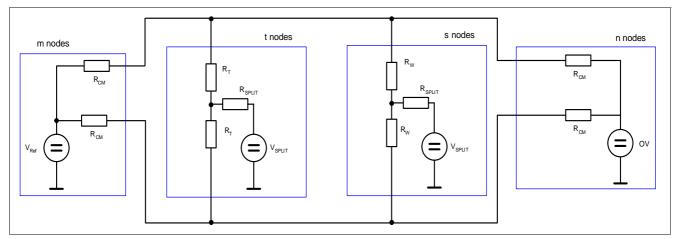

| Figure 41 | Equivalent electrical schematic for a mixed network with SPLIT pin                                                                   |    |

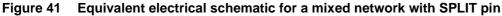

| Figure 42 | Recessive level for different configurations in a mixed network with split                                                           |    |

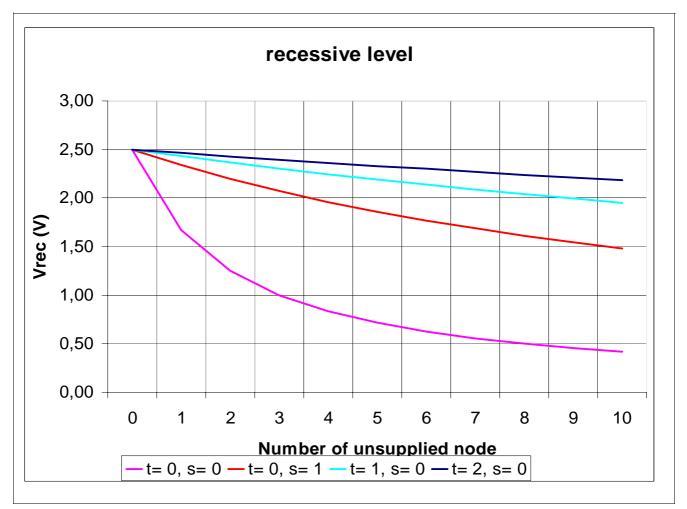

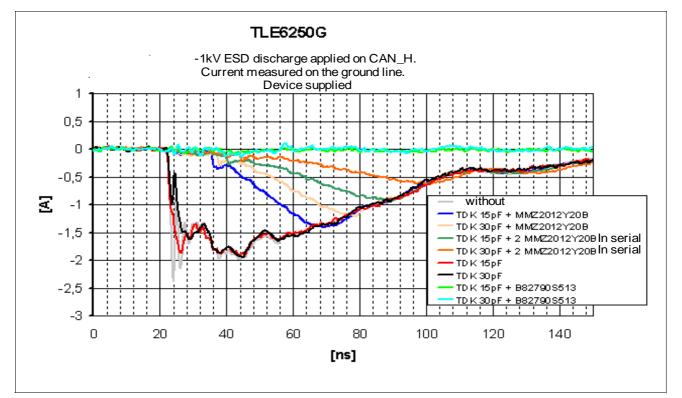

| Figure 43 | Current flowing in the TLE6250G ground, function of the ESD voltage. Device unsupplied                                               |    |

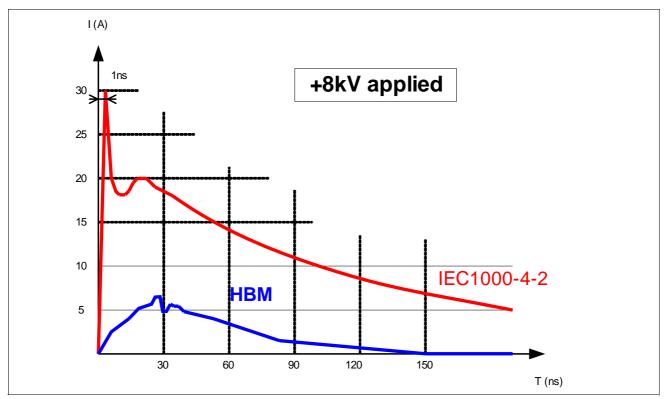

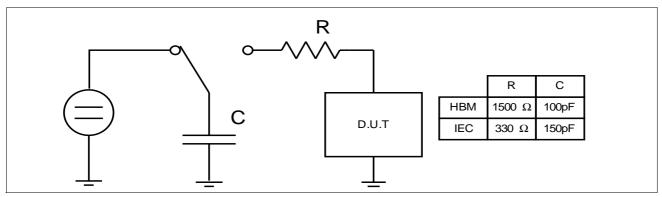

| Figure 44 | Comparison of the current between HBM and gun test.                                                                                  |    |

| Figure 45 | ESD test equipement                                                                                                                  |    |

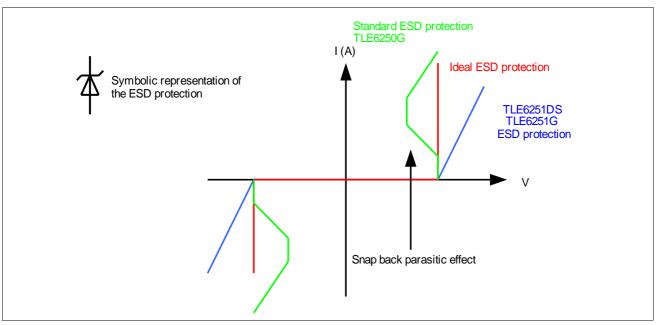

| Figure 46 | Standard and Infineon ESD protection                                                                                                 |    |

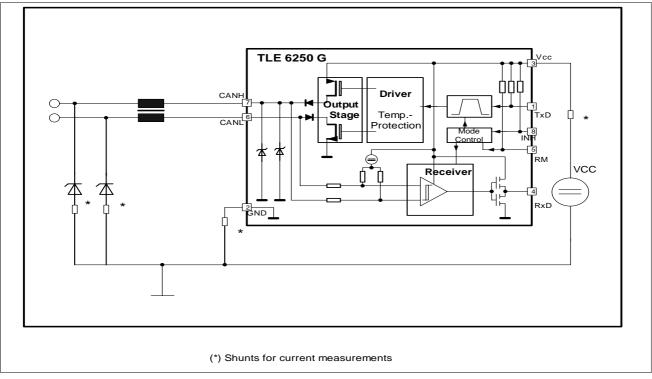

| Figure 47 | Schematic of the test                                                                                                                |    |

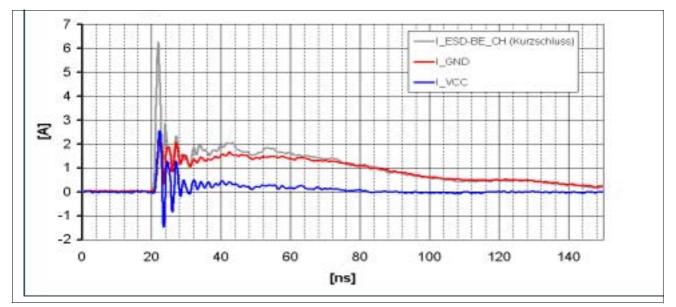

| Figure 48 | Positive ESD discharge, device supplied. Read out of the ground and supply current                                                   |    |

| Figure 49 | Negative ESD discharge, device supplied. Read out of the ground and supply current                                                   |    |

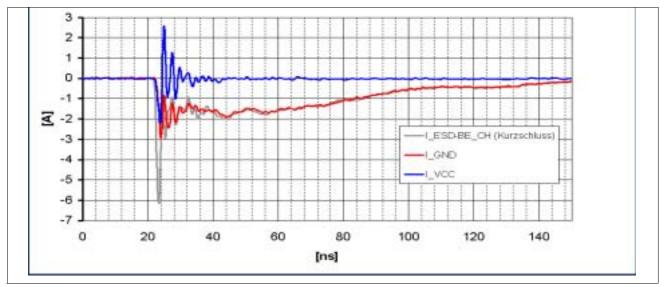

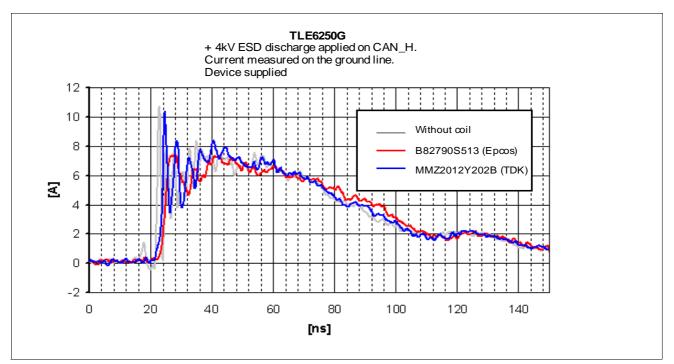

| Figure 50 | ESD discharge, device supplied. Read out of the ground current. With choke coil                                                      |    |

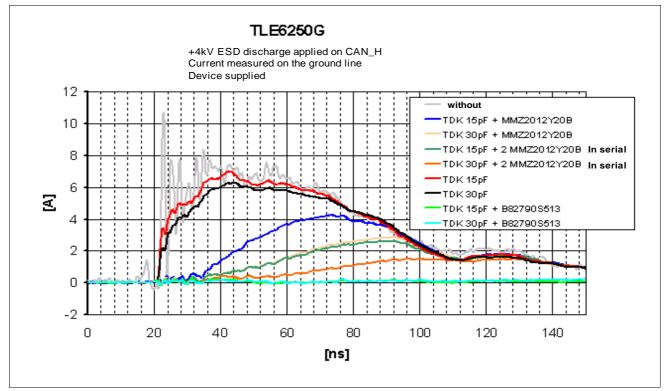

| Figure 50 | Positive ESD discharge, device supplied. Read out of the ground current. With choke contraction of the ground current. With varistor |    |

| 9010.01   |                                                                                                                                      | 10 |

| Figure 52 | Negative ESD discharge, device supplied. Read out of the ground current. With varistor | 46 |

|-----------|----------------------------------------------------------------------------------------|----|

| Figure 53 | Bad PCB example for ESD.                                                               | 47 |

| Figure 54 | Good PCB design for ESD robustness                                                     | 48 |

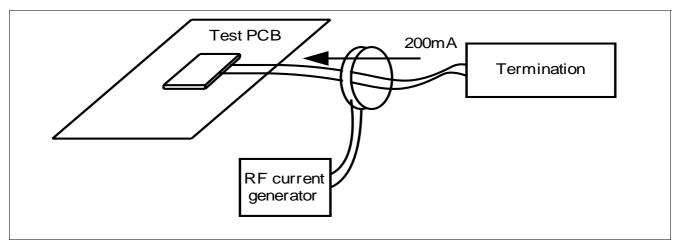

| Figure 55 | BCI test limitation example                                                            | 50 |

| Figure 56 | DPI test set up                                                                        | 51 |

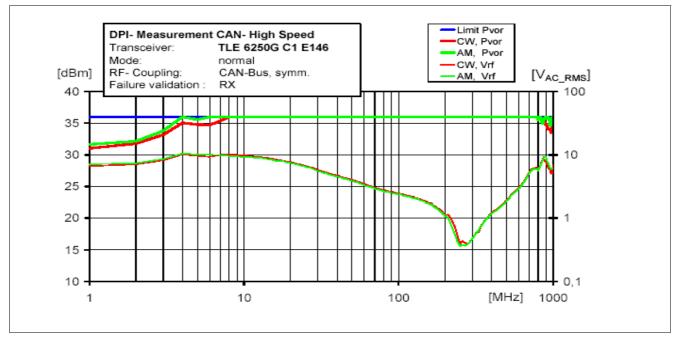

| Figure 57 | DPI test results example : The TLE6250G                                                | 52 |

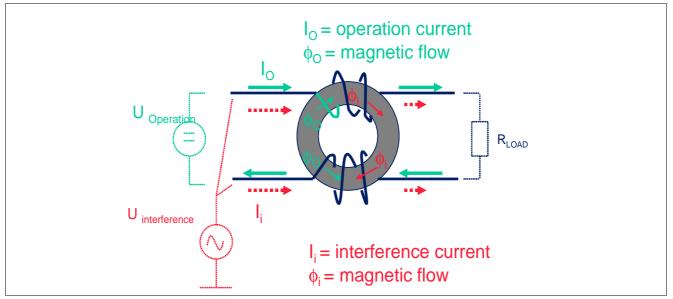

| Figure 58 | Choke coil principle                                                                   | 53 |

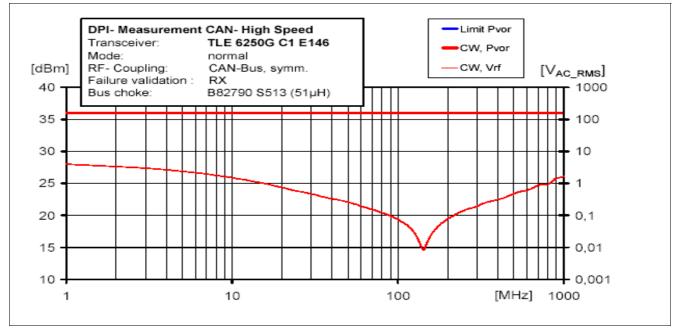

| Figure 59 | DPI test results with choke coil for the TLE6250G.                                     | 53 |

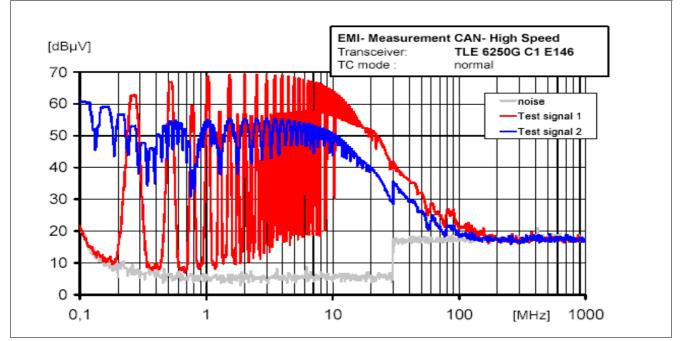

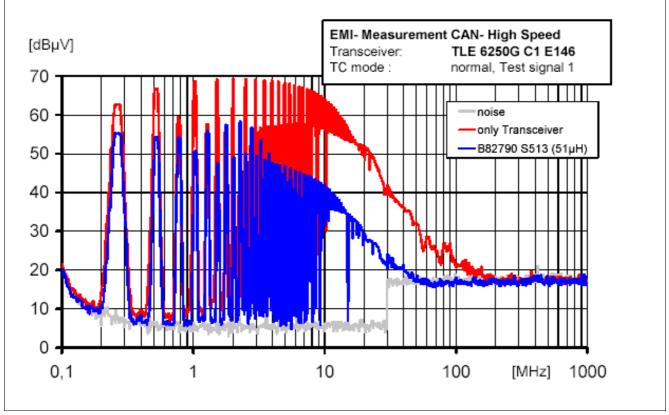

| Figure 60 | EME test results with TLE6250G, without chock coil                                     | 54 |

| Figure 61 | EME test results with TLE6250G with and without chock coil                             | 54 |

| Table 1 | DC parameters for recessive output of CAN node | 2  |

|---------|------------------------------------------------|----|

|         | DC parameters for dominant output of CAN node  |    |

|         | Driver symmetry                                |    |

| Table 4 | Damage test                                    | 19 |

Introduction. Recessive Level.

# 1 Introduction.

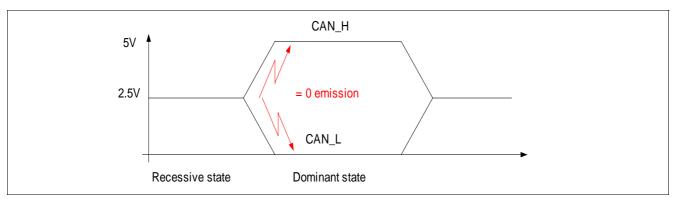

The increasing number of electronics equipment in todays cars implies a lot of information exchange. To avoid a massive usage of wires between modules, a digital protocol has been created. This protocol has been named CAN for Controller Area Network. CAN allows communication, to a speed up to 1Mbit/s. To avoid noisy communication in terms of electromagnetic emission, the medium is a twisted pair and the electrical signal is differential. **Figure 1** shows the typical signal of high speed CAN, and the basic reason for low electro-magnetic emission. When CAN\_H rises, some parasitic are emitted. In the same time, CAN\_L goes down, in the same proportion. The sum of these parasitics are 0, so to say the electromagnetic emission is limited.

This application note is intended to present the high speed CAN application and the usage of Infineon CAN transceivers in these applications. This document refers to international standard ISO 11898-2 [5], SAE J2284, ISO 11898-5 [6], and well as to the TLE6250G [1],TLE6251DS [2], and TLE6251G [3] datasheets.

First part of the document will describes high speed CAN network in the automotive environnement. Then it will focus on transceivers itself for easy interfacing with micro-controller, and will conclude by application hints to successfully reach the challenges of such networks require.

# 1.1 Recessive Level.

During the recessive state, the signal is specified by the ISO 11898-2 [5] and ISO11898-5 [6]. The Table 1 gives the parameters (extract of the ISO11898-2 [5] table 4).

| Parameter                       | Notation           | Unit | min  | Nom | Max | Condition |

|---------------------------------|--------------------|------|------|-----|-----|-----------|

| Output bus voltage              | V <sub>CAN_H</sub> | V    | 2,0  | 2,5 | 3   | no load   |

|                                 | V <sub>CAN_L</sub> | V    | 2,0  | 2,5 | 3   |           |

| Differential output bus voltage | V <sub>diff</sub>  | mV   | -500 | 0   | 50  | no load   |

| Differential input voltage      | V <sub>diff</sub>  | V    | -1   |     | 0,5 |           |

Table 1 DC parameters for recessive output of CAN node

# 1.2 Dominant level.

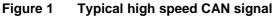

During the dominant state, the signal is specified by the ISO 11898-2 [5] and ISO11898-5 [6]. The **Figure 2** shows the definition of the parameters, described in **Table 2** (extract of the ISO11898-2 [5] table 5).

Introduction. Driver symmetry.

| Table 2 | DC parameters for | dominant out | put of CAN node |

|---------|-------------------|--------------|-----------------|

|         |                   |              |                 |

| Parameter                       | Notation           | Unit | min  | Nom | Max  | Condition               |

|---------------------------------|--------------------|------|------|-----|------|-------------------------|

| Output bus voltage              | V <sub>CAN_H</sub> | V    | 2,75 | 3,5 | 4,5  | load R <sub>L</sub> / 2 |

|                                 | V <sub>CAN_L</sub> | V    | 0,5  | 1,5 | 2,25 |                         |

| Differential output bus voltage | V <sub>diff</sub>  | V    | 1,5  | 2   | 3    | load R <sub>L</sub> / 2 |

| Differential input voltage      | V <sub>diff</sub>  | V    | -0,9 |     | 5    | load R <sub>L</sub> / 2 |

# 1.3 Driver symmetry.

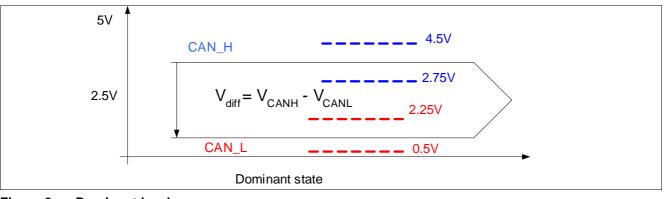

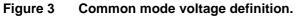

In the ISO11898-5 [6], the driver symmetry is specified. This is to improve the EMC behaviour. The **Figure 3** shows the definition of the parameter, unsymmetry appears often when CAN\_H and CAN\_L are not perfectly synchronized. The **Table 3** gives the specified values.

#### Table 3Driver symmetry

| Prameter        | Notation         | Unit | Min | Nom | Max | Condition          |

|-----------------|------------------|------|-----|-----|-----|--------------------|

| Driver symmetry | V <sub>SYM</sub> | V    | 0,9 | 1   | 1,1 | Load = 120Ω, 4.7nF |

|                 |                  |      |     |     |     | F = 250kHz,        |

#### In Vehicle Network. Type of supplies in the vehicle.

# 2 In Vehicle Network.

# 2.1 Type of supplies in the vehicle.

According to car makers requirements, the modules can be supplied or not supplied when car is parked. Main reason for unsupplied modules is current saving for the car's battery, when supplied modules can quickly wake up on CAN request, or monitoring discretes inputs like switches.

# 2.1.1 Unsupplied modules in the parked car. (Clamp 15)

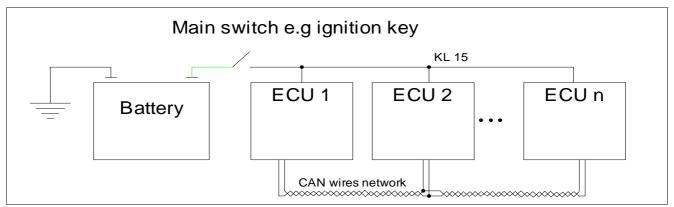

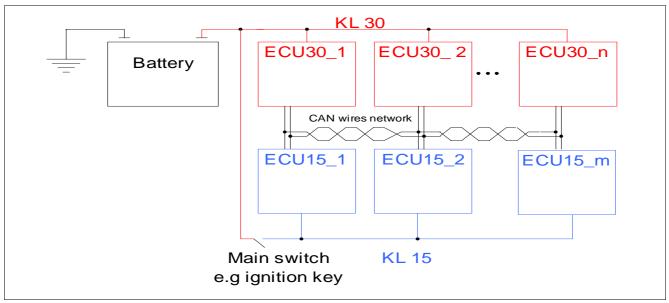

Unsupplied modules are mainly under hood applications as engine control unit. When the car is parked, a main switch cut the battery supply off (see **Figure 4**). This supply line is often called Clamp 15 or KL15 (Klemme 15 in German). Since the battery isn't present, the voltage regulator is off and the transceiver is unsupplied. We will see later on (**Chapter 5.2**) the basic requirements of such applications for the transceivers.

Figure 4 Typical Clamp 15 application

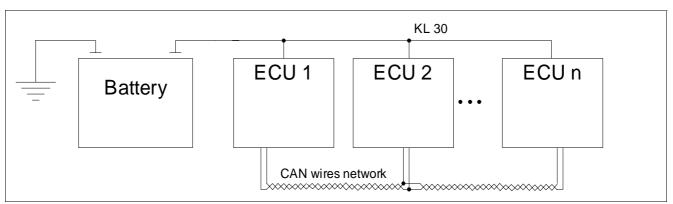

# 2.1.2 Supplied modules in the parked car. (Clamp 30)

Supplied modules, even when car is parked are mainly requested in the body of the vehicle, as door modules, RF keyless receiver, etc... The battery voltage comes directly to the module. This supply line is often called Clamp 30 or KL30 (Klemme 30 in German). Since the battery is present, the LDO is or can be ON, and the transceiver is or can be supplied. We will see in the **Chapter 5.2** the basic requirements of such applications for the transceivers.

# 2.1.3 Mixed network.

It's also possible to mix the two solutions. Some modules are CAN or discretes switches wakeable, some are only supplied by a main switch. Figure 6 shows the application principle. The Chapter 5.2 describes the challenges to achieve with this kind of mixed network.

Figure 6 Mixed CL15 and CL30 network

# 2.2 Ground line.

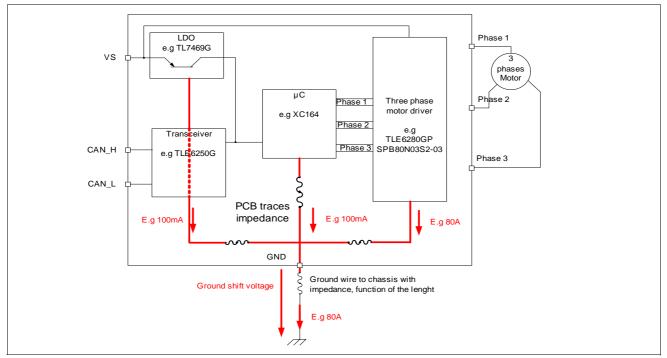

The ground line has a big influence on the electronic equipment, especially for communication purposes, since the physical layer depends on voltage level. The 0V reference is the chassis of the vehicle. The ground pin of the module might not be at this chassis reference. If the ground is shifted between modules, each transceivers are at different ground level and so communication mismatch might occurs.

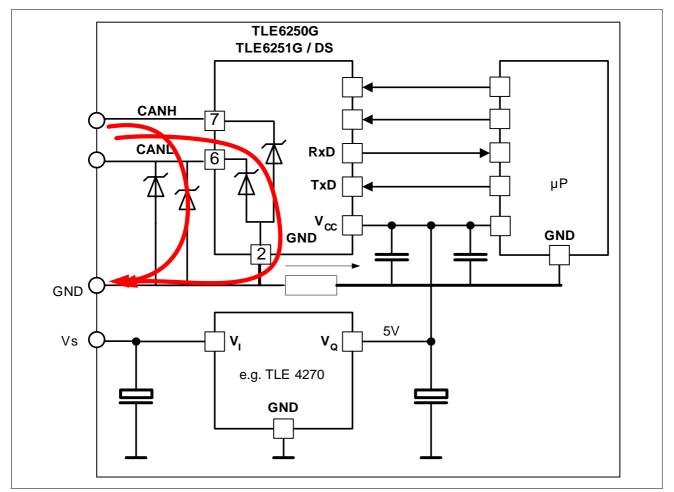

The ground line also influences the EMC and ESD performance of the module and of the vehicle. See **Chapter 6** and **Chapter 7**.

# 2.2.1 High current applications.

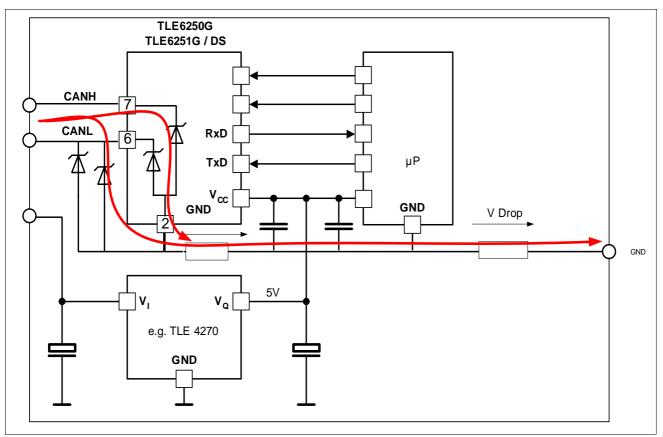

The ground reference of the vehicle is the chassis. Some applications like power-steering, starter-alternator, etc... have a huge current to ground (80Amps or even higher). Moreover, the current is often not DC. Special consideration should be taken with respect to ground cable and its resistor, as well as its inductance has to be taken into account. **Figure 7** shows a typical high current module. Wiring companies often give the resistance of the cable, in  $\Omega$ /km. A standard 1mm<sup>2</sup> cross section cable has a resistance of about 20  $\Omega$ /km. A 80 Amps application with a 1m cable means then a ground shift of about 1.6V, without considering the connectors, and PCB traces resistance. This voltage drop cannot be neglected. The **Figure 7** also shows a possible voltage drop, inside the module due to the PCB trace. This will mainly affect the ESD and EMC robustness. Please refer to the **Chapter 6** and **Chapter 7**.

Figure 7 Typical high current application

# 2.2.2 Low current application.

Most of applications are low current applications, where the voltage drop in the ground wire is close to zero and so the ground current can be neglected.

# 2.3 The Transceiver in the automotive environment.

This chapter describes the behavior of the transceivers in the automotive environment, meaning for example, loss of ground, low battery voltage, cranking pulse, load dump, etc... Each car maker (OEM) specify its own environmental specification so that application note cannot cover all cases, but gives application hints on how to deal with these issues.

# 2.3.1 Low battery voltage.

This situation happens mainly during the cranking of the engine. Except for the TLE6251G, the transceivers are not directly connected to the battery voltage. The transceiver is then mainly dependant on the voltage regulator behavior. Please refers to **Chapter 3.3.8**, for the voltage regulator's choice.

# 2.3.1.1 TLE6250G.

The TLE6250G has no special under voltage function integrated. To get the device working and warranted, the  $V_{cc}$  pin should be higher than the minimum operating voltage specified in the data sheet [1] so 4.5V. Below this value, it is observed that the device is still working, sending and receiving data, but the parameters are not warranted and not compliant to the ISO standard. The recessive voltage is proportional to the V<sub>cc</sub>, typical half V<sub>cc</sub>. For example, with a V<sub>cc</sub> of 4V, the recessive voltage will be 2V typical. It is then recommended to monitor the battery voltage by an external circuitry or early warning function of the voltage regulator, to avoid miscommunication during this time.

When the  $V_{cc}$  voltage is too low, typical 3V, the device is in OFF state, comparable to unsupplied.

# 2.3.1.2 TLE6251DS.

The TLE6251DS doesn't integrate any under voltage function and behaves as the TLE6250G. Please refers to **Chapter 2.3.1.1**.

# 2.3.1.3 TLE6251G.

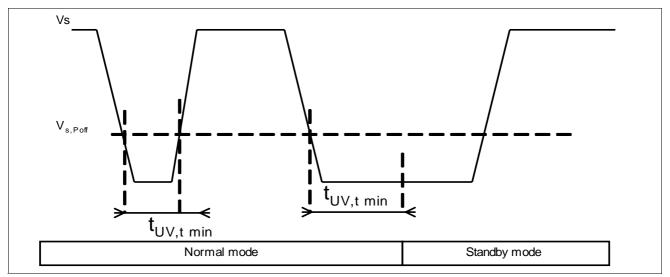

The TLE6251G integrates undervoltage detection for all supply pins, Vs,  $V_{cc}$  and  $V_{\mu C}$ . If one of these pins see a voltage below the specified minimum values (see [3]), the device goes after a filtering blanking time to standby mode, in case Vs is in undervoltage, or to Sleep Mode in case of undervoltage detection on  $V_{cc}$  or  $V_{\mu C}$ . Please refers to Figure 8 for explanation of Vs. Please also refers to Chapter 4.3.5.2, for undervoltage detection on  $V_{\mu C}/V_{cc}$ .

Figure 8 Undervoltage detection mechanism for Vs.

Since the undervoltage mechanism is below the minimum operating voltage (for production spread and temperature dependancy reasons), between these under voltage states and minumum operation, the device is active and operates, without warranted conformity to the ISO standard. Last but not least, the Vs undervoltage detection threshold is buffered with an hysteresis.

# 2.3.2 High battery voltage.

We discuss here all high battery voltage conditions, like jump start, load dump, or highest nominal battery voltage. The voltage should not exceed the absolute maximum rating. Otherwise, the device could be damaged or destroyed. The high battery voltage as well as load dump are voltage regulator issues. Since the dissipated power in the LDO is directly proportional to the input voltage, (see Equation (1)), the issue is to get rid of the power in the LDO.

Power loss in a LDO:  $P_{loss} = (Vbat - V_{cc}) * I_{out} + V_{bat} * I_{q}$

(1)

$I_{out}$  is the output current of the LDO.

$I_q$  is the current consumption of the LDO (values can be found in the LDO datasheet).

If the power dissipation challenge is passed, the application will work properly.

# 2.3.2.1 TLE6250G / TLE6251DS.

For 12V applications, the concern of the high operating battery voltage is limited to two very special cases, double failure (CAN\_H or CAN\_L shorted to battery and high voltage operation). The absolute maximum rating warranties no destruction of the device because the highest voltage seen is the 34V load dump.

The only concerns is the power dissipation, when CAN\_L is shorted to battery. The device limits the current, but with battery voltage, the temperature will increase dramatically and the device might go into thermal shutdown. (failure case 3 and 6, see Figure 30).

# 2.3.2.2 TLE6251G.

In addition to the TLE6250G and TLE6251DS (see **Chapter 2.3.2.1**) remarks, the TLE6251G includes an high side switch. In case of high battery voltage, the power loss in the switch cannot be neglected and so it is recommended to not connect a low ohmic load on the INH output. The INH pin should be considered as a high voltage signal only. See also **Chapter 4.3.8**.

# 2.3.3 Reverse polarity.

Same remark as for the **Chapter 2.3.2**. The issue is mainly carried by the voltage regulator. Anyway, some possible current path exists and has to be described in the following sections.

# 2.3.3.1 TLE6250G / TLE6251DS.

A possible failure would be a current flowing into the CAN\_L output stage DMOS, due to its parasitic body diode. To avoid this, the TLE6250G and TLE6251DS includes in serial a diode on the bus output lines. Please see block diagrams of the devices in the data sheets [1] [2] [3].

# 2.3.3.2 TLE6251G.

The TLE6251G includes a P channel DMOS high side switch (pin INH). The maximum reverse battery voltage the device can withstand is very small (-300mV)[3]. It is then necessary to protect the Vs pin of the TLE6251G with a diode, preferably Schottky diode to get rid of the low voltage issue (Chapter 2.3.1). The power loss in this diode is negligible, since the Vs pin doesn't need a high current, whatever the mode the device is. It is then suggested to use the diode in common with the voltage regulators.

# 2.3.4 Short circuit on the bus.

Unfortunatly, the short circuit is a problem which can occur in the vehicle when the signal goes out the electronic module. All cases of short circuit are described in the **Figure 30**. The transceiver family from Infineon withstand all these cases, but communication cannot be warranted anymore. The **Chapter 3** describes in details the resulting current to be handled by the voltage regulator.

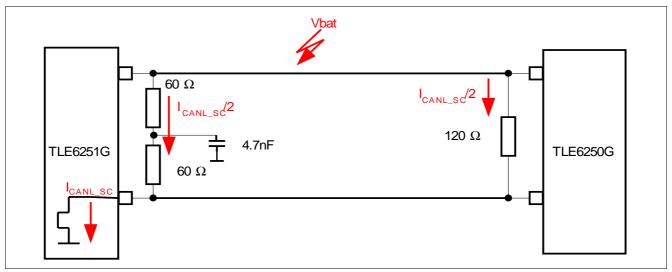

# 2.3.4.1 Termination resistors case in short circuit to Vbat.

In case CAN\_H is in short circuit to Vbat, (failure case 6, see Figure 30), the power loss in the termination resistors has to be taken into account. The Figure 9 shows the path of the current, in the case the termination is splitted ( $2x60\Omega$  or  $120\Omega$ ). Purpose of the Split is described in Chapter 5.2. The transceiver will limit the current to the I<sub>CANL SC</sub> value, if the battery voltage is higher than 12V.

Power loss in the resistor : 1/2 x  $R_{termination} \times I_{CANL_SC}^2$ .

The coefficient 1/2 comes to the ratio recessive dominant. See also Chapter 3.1.4

According to Equation (2), the power loss in the  $60\Omega$  resistors will be at an average of 300mW and in the  $120\Omega$  resistor an average of 600mW. This power has to be taken into account when designing the network termination resistors.

(2)

Figure 9 Current in the termination resistors in case of short circuit to Vbat.

Please also notice that in case of CAN\_H shorted to Vbat, due to the voltage drop in the resistors, it is possible to see an "appearing" permanent dominant signal.

# 2.3.5 Temperature.

The Infineon transceiver family is qualified from -40°C to 150°C, as required by the automotive standard. The **Chapter 3** will show the power consumption of the devices, in the different cases.

# 2.3.6 Ground shift.

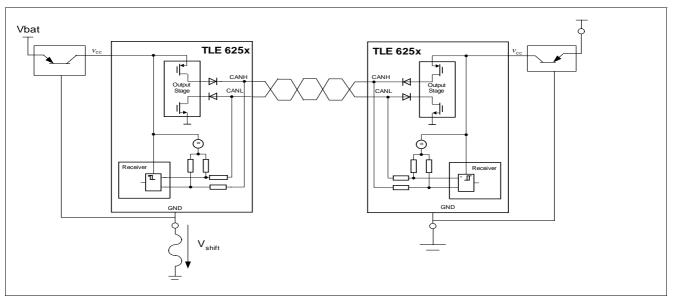

In the **Chapter 2.2** we have seen the influence on the ground line for the module. We will now describe the application of interfacing an high current application and a low current application. **Figure 10** shows an application with one ground shift module, in connection with one not connected. We limit the drawing to two modules for simplification purpose, the description remains valid with several modules.

Figure 10 System with one ground shift event

When the module subjected to a ground shift is transmitting, the CAN\_H and CAN\_L output stages of receiving nodes are OFF. In other words, the receivers for both CAN\_H and CAN\_L are modeled as resistors to ground.

The values can be found in the datasheet of the respective products considered, under the name R<sub>i</sub>. Since the sender has its ground shifted to a V<sub>shift</sub> value, the recessive level V<sub>rec</sub> seen from the chassis ground is no longer 2.5V typical but V<sub>rec</sub> + V<sub>shift</sub>. The same shift has to be taken into account for the dominant signal. This voltage is the voltage seen by the receiver. The Infineon transceivers are differential transceivers, with a wide common mode range. The CAN\_H and CAN\_L DC value are not of primary importance, if below the absolute maximum rating. Only the difference voltage (CAN\_H - CAN\_L) is taken into account by the receiver. Figure 11 shows a typical CAN signal with a DC ground shift of +2V, and Figure 12 shows a rough ground shift due to high inrush in the application load. In both cases, the communication remains excellent.

The recessive system level when the ground shifted module is sending, is equaled to the mean value of all transceivers recessive voltages. Equation (3) gives the value of the system recessive voltage in that case.

Vrec = [(Vrec\_1+ Vshift\_1) + (Vrec\_2 + Vshift\_2) + ... (Vrec\_n + Vshift\_n)] / n (3)

n is the number of connected modules.

Vrec\_1, 2...n are the specific recessive level of the transceiver on nodes 1, 2, ...n

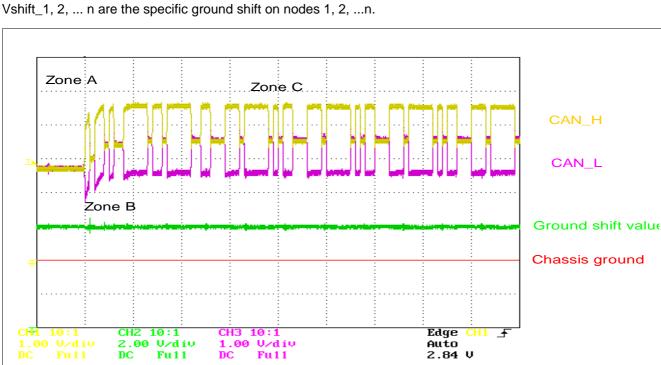

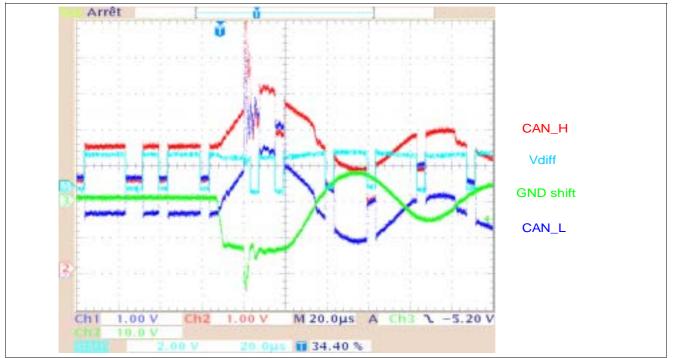

Figure 11 Typical DC ground shift signal.

Zone A : Shows the recessive voltage of the system, so close to the nominal recessive value of 2.5V

Zone B: When the transmitter starts to communicate (zone B), the signal grows quickly, and load the capacitors of the system. (parasitics of the wiring, terminations capacitors, ...).

Zone C : The communication is stabilized, and the recessive voltage is reaching the value, as computed on Equation (3).

It is important to notice that the supply current of the transceiver will increase.

If n represents the number of nodes on the network,

R<sub>in</sub> is the impedance to ground of the CAN\_H / CAN\_L input for each nodes,

V<sub>shift</sub> is the ground shift voltage,

The extra supply current is :  $I_{cc shift} = V_{shift} / (R_{i n} / n)$ , assuming all input resistances identical

Figure 12 CAN signals with AC ground shift.

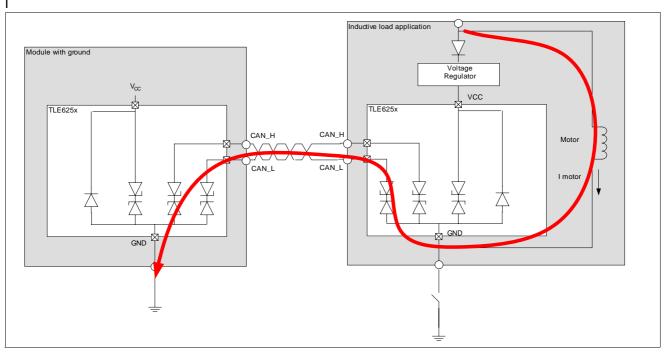

#### 2.3.7 Loss of ground.

In case of loss of ground, the voltage regulator output ( $V_{cc}$ ) might goes to the battery voltage. It means the  $V_{cc}$  input of the transceiver might be at the 12V battery potential. The transceiver is of course no longer supplied, so it behaves as unpowered state, but brings a pull-up to battery to the bus, via the input resistors of the receiver. From a system point of view, the behavior is like a short circuit to battery via a weak pull up, the transceiver is the weak pull-up. The CAN signals are no more in conformance with the ISO standard but the communication between the non-affected module remains OK, since the high speed CAN protocol is differential and a limp home functionnality is possible.

Figure 13 Loss of ground with inductive load

If the application is using an inductive load, a risk of destruction is possible, if the inductive load has no freewheeling diode. Figure 13 shows the issue. When the ground disconnects, the coil has to be demagnetized and the current is flowing in the less ohmic path available. One of the lowest ohmic path on the application is the CAN transceiver. The inductive load increases the voltage until turning on the ESD protection and the current is flowing. The ESD protection isn't designed to withstand such a long energy and the transceiver is very quickly destroyed by E.O.S. (Electrical Over Stress). The only solution is to plan a free wheehling diode on the inductive load. No protection can be done at the transceiver level.

# 2.3.8 Loss of Battery.

In case of loss of battery, no issue can be expected, and the device behaves as in unsupplied state. Please refers to the **Chapter 3.1.1** (TLE6250G), **Chapter 3.2.1** (TLE6251DS) and **Chapter 3.3.1** (TLE6251G) for additional information on the behavior of the device, when unsupplied.

#### Power management, transceiver supply.TLE6250G.

# **3** Power management, transceiver supply.

Each transceiver product has its own power management features, from the basic features of the TLE6250G to the complex power management of the TLE6251G. The following chapter will describe which power consumption on the different supplies pin will be achieved with the different devices.

# 3.1 TLE6250G.

The TLE6250G is the first High Speed Transceiver product Infineon has introduced the market. This part has no power management. Anyhow, the part includes an inhibit functionality, to switch the device completly. This device is perfectly matching application on the KL15 powernet, so unsupplied when the vehicle is parked.

# 3.1.1 TLE6250G in unsupplied mode.

When the TLE6250G is unsupplied, it brings on the bus an pull down resistors specified in the datasheet (parameter  $R_i$ )

# 3.1.2 TLE6250G in inhibit mode.

In inhibit mode, the power consumption on the Vcc, (specified in [1]  $I_{CC, STB}$ ) is below 10µA. The complete device is disabled. The TLE6250G brings on the bus an pull down resistors specified in the datasheet (parameter  $R_i$ ).

# 3.1.3 TLE6250G in normal mode.

In normal mode, the device needs a current on the Vcc of maximum 70mA in dominant state, and 10mA on recessive state [1]. To estimate the power consumption in normal mode, a cyclic ratio of 50% can be assumed, because we can consider the communication is overall 50% dominant, 50% recessive. In normal mode, the device will need a maximum average current of:

$I_{CC, AVG} = (I_{CC, REC} + I_{CC, DOM}) / 2 = 40 \text{mA}.$

# 3.1.4 TLE6250G in fault condition.

# 3.1.4.1 Average maximum current in fault condition.

In presence of bus failure, the Vcc supply current for the transceiver can increase significantly, in case of CAN\_H shorted to ground. (case 4, see Figure 30). It is recommended to dimension the Voltage regulator for the worst case, especially when the Vcc also supplies the micro controller. It is important to notice the Vcc supply current increase only in dominant state, the recessive current remains almost unchanged. With the same assumption as the Chapter 3.1.3, the average fault current will be:

$I_{CC, AVG, fault} = (I_{CC, REC} + I_{CANH, SC}) / 2 = 105,5mA$

This current is the maximum average current the device will demand on the Vcc supply line.

# 3.1.4.2 Peak maximum current and decoupling capacitor.

The peak current is higher than described in **Chapter 3.1.4.1**, and it is recommended to filter the maximum peak current by the decoupling capacitor's the Voltage regulator needs for stability reason. The worst case scenario is to have 17 dominant bits in a row. At the moment the CAN controller starts a transmission, the dominant Start Of Frame bit is not fed back to RxD and thus forces an Error Frame due to the bit failure condition. The first bit of the error frame again is not reflected at RxD and forces the next error frame (Tx Error Counter + 8). Latest after 17bit times, depending on the TX Error Counter Level before starting this transmission, the CAN controller reaches the error passive limit and stops sending dominant bits. During this 17bits, the maximum current will be I<sub>CANH, SC</sub>. To filter this peak current, we need first to compute the delta current the capacitor should deliver.

$\Delta I_{CC MAX, SC} = I_{CANH, SC} - I_{CC,REC} = 190 \text{mA}.$

#### Power management, transceiver supply.TLE6251DS.

The worst case bypass capacitor then calculates to:

$C_{buff} = \Delta I_{CC, MAX, SC} \times t_{DOM, MAX} / \Delta V_{max}$

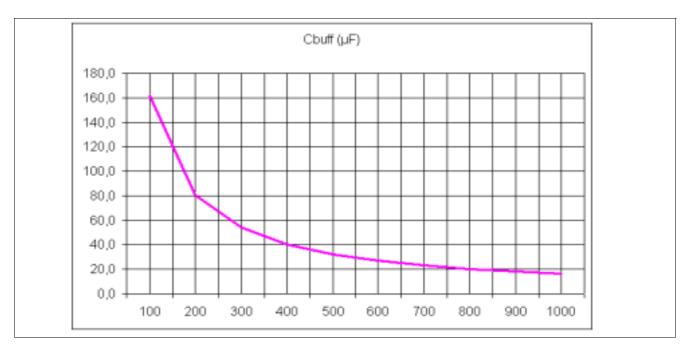

**Figure 14** gives the result, function of the baud rate of the decoupling capacitor value, with an allowed  $\Delta V_{max}$  of 200mV. This value is an excess value, since the voltage regulator will react. This reaction time is only dependent on the device used and so cannot be described here.

Figure 14 Buffer capacitor in function of the baud rate.

# 3.1.5 TLE6250G junction temperature.

In the **Chapter 3.1.3**, we have seen the worst case current consumption in normal condition, with a 5V supply. This leads to a nominal power dissipation of :  $0.5 \times (70\text{mA} \times 3.5\text{V} + 10\text{mA} \times 5\text{V}) = 150\text{mW}$ . The SO8 package offers an Rthja of 185K/W in the worst case. The junction temperature is then increased by 28K worst case. In case of short circuit, the power dissipation will increase of course. The transceiver might go to thermal shutdown. In that case, the receiver is still active, only the power stage is disabled, behavior is identical to receive only mode.

# 3.2 TLE6251DS.

TLE6251DS offers a standby mode. In this mode, the device is still able to receive some data, with the target to wake up a micro controller. This device is then compliant to Clamp 15 as well as Clamp 30 (see Chapter 2.1) powernets and thanks to the very high ohmic behavior in unsupplied mode (Chapter 3.2.1), perfectly suitable for the Clamp 15 part of a mixed KL15 / KL30 network.

# 3.2.1 TLE6251DS in unsupplied mode.

TLE6251DS has an improved behavior during unsupplied case. The R<sub>i</sub> resistors of the receivers are cutted, and the current flowing into the pin CAN\_H / CAN\_L is limited. The datasheet [2] gives the value (paramater I<sub>CANH, L,</sub>  $_{Ik}$ ) to 5µA worst case. It leads to a equivalent resistor of 1M $\Omega$  minimum. Thanks to this, the device perfectly fits the request of the Clamp 15 mixed with Clamp 30. The pull down resistor will be limited, compared to the TLE6250G.

#### Power management, transceiver supply.TLE6251G.

# 3.2.2 TLE6251DS in stand by mode.

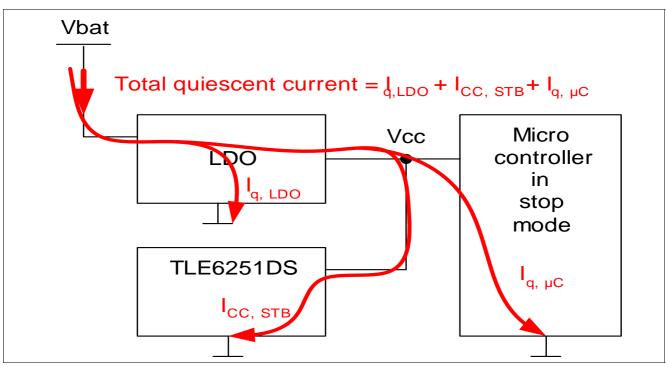

In that mode, the TLE6251DS needs a maximum current supply  $I_{CC, STB}$  of 30µA, 20µA typical [2]. Figure 15 shows how to compute the quiescent current of the application, (actuators excluded).

Figure 15 Quiescent current computation in stand by mode.

It is important to notice that in this quiescent current "grand total", the biggest part is often the Voltage regulator contribution ( $I_{q, LDO}$ ), if the Voltage regulator is designed in standard bipolar technology. (TLE42xx or TLE44xx Infineon products). To get rid of this issue, it is recommended to use the new Voltage regulator family from Infineon, in the SPT5 technology, (TLE72xx and TLE74xx). For example, the supply current of the TLE4275 is worst case 200µA [7] at 25°C when the TLE7270 is 30µA [8], for similar maximum output current and functions. With an SPT5 Voltage regulator and TLE6251DS, the leakage current the module will need in a parked car should be in the range of 70µA (depending on the micro controller stop mode supply current).

# 3.2.3 TLE6251DS in normal mode.

In normal mode, the TLE6251DS behaves as the TLE6250G. Please refers to Chapter 3.1.3

# 3.2.4 TLE6251DS in fault condition.

Please refer to Chapter 3.1.4.

# 3.2.5 TLE6251DS junction temperature.

Please refer to Chapter 3.1.5.

# 3.3 TLE6251G.

The TLE6251G has an enhanced energy management, allowing the device to control the entire supply chain of the electronic module, targeting to achieve the lowest quiescent current. It perfectly fits the Clamp 30 application. There's no voltage supply sequencing. Vcc, V $\mu$ C and Vs can be powered in indifferent orders.

#### Power management, transceiver supply.TLE6251G.

# 3.3.1 TLE6251G in unsupplied mode.

Same remarks as for the TLE6251DS, see Chapter 3.2.1.

# 3.3.2 TLE6251G in sleep mode.

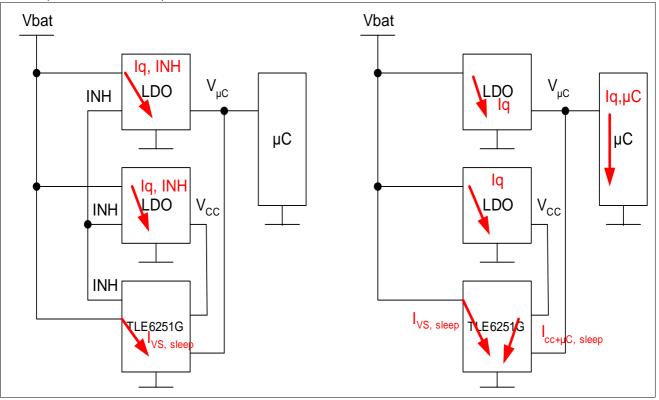

In sleep mode, the quiescent current of the device is  $25\mu$ A typical,  $35\mu$ A worst case on the Vs pin [3]. If the V<sub>cc</sub> and V<sub>µC</sub> are OFF, using the INH functionality (see also **Chapter 4.3.8**), then the entire module will need no more current (actuators excluded).

In case the V<sub>cc</sub> and / or V<sub> $\mu$ C</sub> are supplied, an extra leakage current has to be taken into account, and the overall quiescent current of the module will increase dramatically. **Figure 16** shows the two cases. The I<sub>q, INH</sub> values are given in the data sheet and are typically in the range of one  $\mu$ A.

# 3.3.3 TLE6251G in Stand by mode.

The stand-by mode is entered at power up or after under voltage as Vs. Compared to sleep mode, the TLE6251G turns ON the high side switch of the INH output so an extra leakage current has to be taken into account. 25µA maximum to turn ON and supply the high side internally [3]. It is also necessary to compute the extra current of the INH load which is connected to the INH output, which is application dependant.

The TLE6251G includes a under voltage detection on its three supply pins, Vs, Vcc and V<sub>µc</sub>. In case the application requires to keep the device in standby mode for a long time (higher than the minimum under voltage blanking time, see also **Chapter 4.3.5.2**), then, both Vcc and V<sub>µC</sub> have to be present. Otherwise, the TLE6251G will go automatically to sleep mode. It means the quiescent current of an application with TLE6251G remaining in stand by mode is bigger than the sleep mode, since the voltage regulators must remains ON, even if no or few current are consumed.

#### Power management, transceiver supply.TLE6251G.

# 3.3.4 TLE6251G in receive only mode.

In receive only mode, the device is functional and needs the same current as in normal mode, recessive state.

#### 3.3.5 TLE6251G in normal mode.

In the normal mode, the TLE6251G behaves as the TLE6250G so please refers to **Chapter 3.1.3**, with the correct values given in the data sheet [3].

# 3.3.6 TLE6251G in fault condition.

As for the TLE6250G and TLE6251DS, the current consumption on the  $V_{cc}$  pin will increase dramatically. Please refer to chapter **Chapter 3.1.4**. Since the bus error management is only valid after four transitions of bus (from recessive to dominant), the worst case scenario with 17 consecutive bits dominant has to be taken into account as well.

# 3.3.7 TLE6251G junction temperature.

In normal condition, the device needs 40mA on the 5V  $V_{cc}$  supply. The SO14 package offers a  $R_{THJA}$  of maximum 120K/W, leading to a junction temperature increase of 24K, compared to the ambient temperature.

#### 3.3.8 Choice of the voltage regulator.

The voltage regulator has to be chosen in the family of the low drop output (LDO), as the Infineon's TLE42xx, TLE74xx. TLE74xx. These LDOs families allow input voltage down to 5.5V at their input pin. To filter the bounces on the battery supply line, the application requires a big input capacitor. This capacitor has to be protected against reverse polarity by adding a diode. This diode has to be chosen with the lowest voltage drop (Schottky diode, typical 200mV) in its forward path. So to say that the LDO delivers a proper 5V with a minimum of 5.7V battery voltage. Below, the 5V cannot be warranted anymore, and the LDO follows the battery voltage. For the transceiver it means as well the level will be smaller, and follows the battery line, until a threshold when the communication will stop completly. It should be able to deliver 40mA DC current (see Chapter 3.1.3), only for the transceiver. The LDO should also allow to work with a peak current of 105mA (see Chapter 3.1.4.1) for the communication, it is not needed to warranty 105mA DC condition. The decoupling capacitor at the output of the LDO is described in Chapter 3.1.4.2. If the LDO is used only to supply the transceiver, the TLE4266-2G.[9], offering a minimum of 150mA peak current, an INH input, in SOT223, fits perfectly.

# 4 Interface with micro controller.

A CAN transceiver is the physical layer between the protocol controller (micro controller, state machine), to the physical transmission medium. Following is a description, of TLE6250 and TLE6251 family, of the interface between the micro controller and the Infineon's used transceiver.

# 4.1 TLE6250G/GV33.

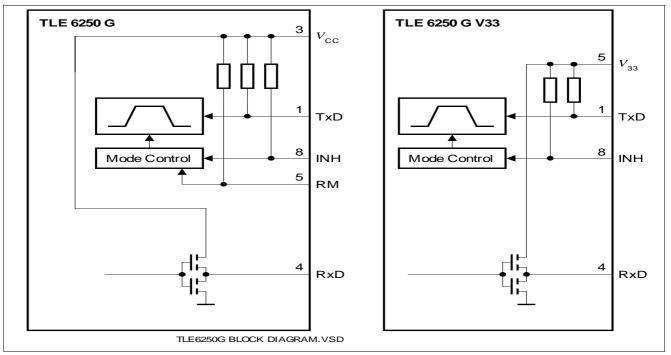

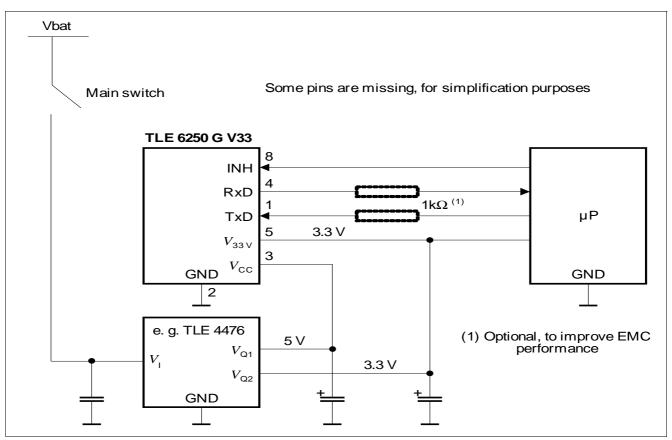

**Figure 17** shows the pin out and a brief description of the logic pins of the TLE6250G and TLE6250GV33, adapted to 3.3V logic level. Following is a description of the logical pin and **Figure 21** and **Figure 22** gives the standard schematic of the application.

Figure 17 Block diagram of TLE6250G/ TLE6250GV33

#### 4.1.1 Pin $V_{cc}$

The pin  $V_{cc}$  gives the proper 5V supply to build the CAN\_H and CAN\_L signal, as well as the receiver supply and internal voltage reference supply to build the recessive state level. In case of TLE6250G use, the logic pins are pulled up to Vcc. Chapter 3.3.8 gives additional information about how to size correctly the voltage regulator supply.

# 4.1.2 Pin RM (only for the TLE6250G version).

The pin RM or Receive only Mode is a special feature from the TLE6250G. This pin allows to inhibit the data streaming on the TxD pin, which blocks the transmission. Main functionality of the receive only mode is to allow diagnostic (to avoid the aknowledge bit realized by software), to check modules connections, see **Figure 18**, or to avoid miss-communication on the medium due to a micro controller failure. To enter the Receive-only Mode, a logical zero has to be applied on the pin. To set the device in normal operation, so to activate the data streaming from the micro controller on the TxD pin, the RM pin has to be set to a logical 1. Since the TLE6250G integrates a pull up resistor, by default the device is in normal operation. In case the Receive only mode is not used, the pin can to be left opened.

Figure 18 Module connection verification, using receive only mode functionnality

# 4.1.3 Pin INH.

The pin INH is used to set the device in stand by mode or normal operation. The stand by mode is used to reach the lowest quiescent current possible on the Vcc pin. To enter the stand by operation mode, the pin has to be at a logical 1. As the device integrates an internal pull up, by default, the device is in stand by mode.

To enter the normal operation, a logical 0 has to be applied. In that case, the maximum current flowing out the INH pin is  $525\mu$ A. In case the INH mode is not needed, the pin has to be set to ground directly.

# 4.1.4 Pin $V_{33}$ or $V_{io}$ (only for TLE6250GV33).

The pin  $V_{33}$  or  $V_{io}$  is needed for operation with 3.3V I/O micro controllers to get the correct level between the micro controller and transceiver. This pin needs some current, mainly to supply the RxD pin (see Chapter 4.1.6). This pin can also be supplied by a 5V voltage regulator of course, when the application is requesting a separate supply for the micro controller and the transceiver. In case the  $V_{io}$  voltage is 0V, the TxD pin is 0V as well and the risk is to have a permanent dominant signal on the bus. The TLE6250GV33 includes the functionnality to not react to the TxD pin if  $V_{io}$  is 0V. In that case, the CAN\_H and CAN\_L output switches are OFF and the device is recessive. In the opposite case, if  $V_{cc}$  is OFF, and  $V_{io}$  is 0N, the RxD might be permanently low (dominant), and could trouble the software. To avoid this, in case  $V_{cc} = 0V$ , the RxD pin is permanently high (recessive).

# 4.1.5 Pin TxD.

The transceiver receives the digital bit stream to be transmitted from micro controller onto the bus via the pin TxD. Sometimes, the signal at TxD show steep edges at bit transitions, likely to degrade the EMC performance of the total module. In this case it is recommended to place or to plan a serial 1k $\Omega$  resistor into the TxD line between the transceiver and the micro controller. Along with the TLE6250G internal capacitance (value) this would help to smooth the edges to some degree. For high speed communication up to 1Mbit/s, the resistor might generates on extra delay and this has to be taken into account, please refers to Figure 19. The parasitic capacitor  $C_{TxD}$  is not specified, for testing reasons. The standard value used for the Infineon's transceiver is 10pF, 15pF to consider the worst case.

Figure 19 parasitic delay in case of serial resistor.

# 4.1.6 Pin RxD.

The analog bit stream received from the bus is output at pin RXD for further processing within the micro controller. As with pin TXD a series resistor of about  $1k\Omega$  can be used to smooth the edges at bit transitions. Again the additional delay within RXD has to be taken into account, if high bus speeds close to 1Mbit/s are used. The output stage of the RxD pin is a push pull stage. The output is not protected against over-current. Nevertheless, in case the RxD pin is in short circuit, a current of about 15mA typical can flow in or out (depends on short to ground or short to Vcc). This typical failure happens when the pin is forced to ground or 5V. The pin RxD follows the bus, meaning it also repeats what the TxD pin sends. The Figure 20 shows the propagation delay concept.

Figure 20 receiver timing

Figure 21 Typical application for TLE6250G

Figure 22 Typical application for TLE6250GV33.

#### Interface with micro controller. TLE6251DS.

# 4.2 TLE6251DS.

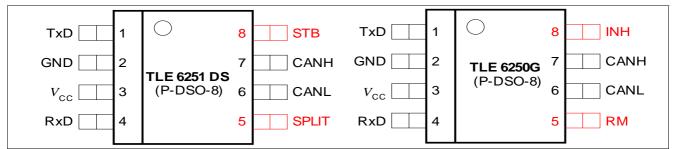

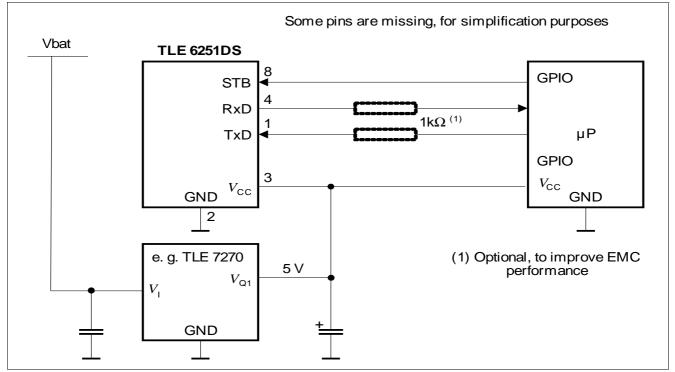

Compared to the TLE6250G, TLE6251DS has almost the same pin out (see **Figure 23**). The TLE6251DS is able to wake up the micro controller on bus activities. We will now describe the logic pins of the TLE6251DS. **Figure 27** describes the typical application interface between TLE6251DS and micro controller. TLE6251DS fits only to 5V micro controller interface.

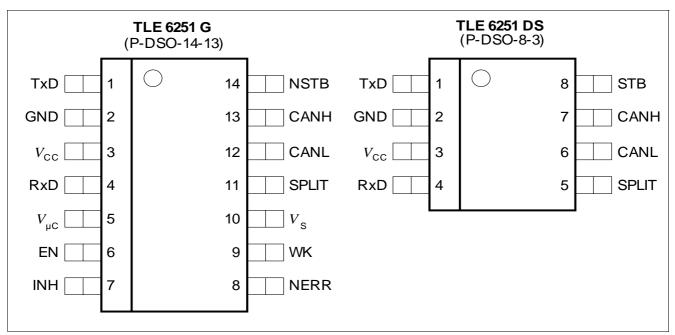

Figure 23 Pin out comparison TLE6251DS and TLE6250G

# 4.2.1 Pin STB.

The STB pin (STand By) is used to set the TLE6251DS in the standby or normal mode. To set the device to normal operation, a logical 0 has to be applied. (and logical 1 to set the device to standby mode). As the pin has an integrated pull-up, by default the device is in standby mode. In case the standby feature isn't needed, the pin should be connected to ground.

# 4.2.2 Pin TxD.

# 4.2.2.1 Hardware description.

Please refers to the Chapter 4.1.5, description of the TxD of the TLE6250G.

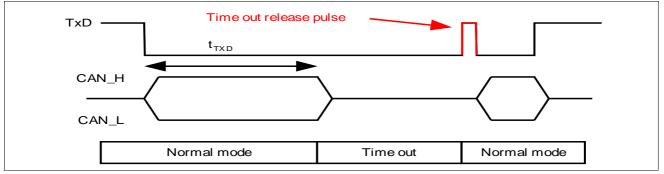

# 4.2.2.2 Time out function.

The TLE6251DS has a permanent dominant disable time. **Figure 4.2.3** describes this feature. It's used in case the micro controller goes to faulty condition and sets the TxD pin to a permanent 0 logic level. In that case, the bus is permanently dominant and the entire network is down due to the faulty micro controller. To avoid this, the permanent dominant disable time will automatically relax the bus to recessive level if the TxD pin is low for more than t<sub>TxD</sub>. The value can be found in the TLE6251DS data sheet [2]. To come back to normal operation, the TxD pin has to go back to a logical 1. No special filter timing for the recovery is applied. It means there's no constrained on the minimum time TxD pin has to be at logical 1 to leave the permanent dominant disable function. Anyway, the function is realized with a flip flop so the reset pulse should be longer than the propagation delay in the flip flop cell, so 20ns.

#### Interface with micro controller. TLE6251DS.

# 4.2.2.3 Time out function. Baud rate limitation.

This feature limits the minimum possible baud rate. According to the CAN protocol a maximum of eleven successive dominant bits is allowed on TXD only (worst case of five successive dominant bits followed immediately by an error frame). With a minimum value given in the data sheet for TxD of  $300\mu s$  [2], so to say that 11 bits should be faster than  $300\mu s$ , the baud rate of the application must be higher than 36.6kbit/s to be sure to comply to the CAN protocol. Min baud rate = max dominant bits / t<sub>TXD</sub>.

# 4.2.3 Pin RxD.

#### 4.2.3.1 Hardware description.

The RxD pin is as for the TLE6250G, see Chapter 4.1.6, a push pull stage. In case of short circuit to ground or  $V_{cc}$ , the current is limited to maximum 20mA (see datasheet [2]  $I_{scRxD}$ ).

#### 4.2.3.2 Wake up behavior.

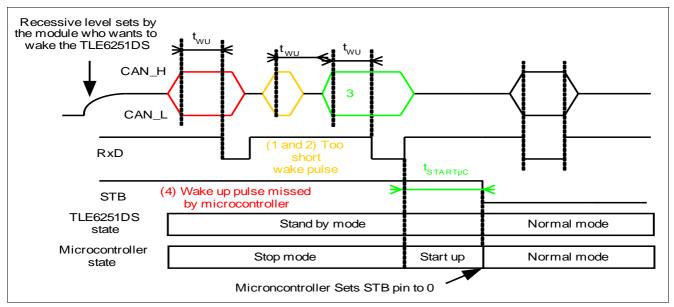

The RxD pin is used to wake the micro controller up. To realize the wake up mechanism, the micro controller should be in stop mode and the RxD pin should be an interrupt input in order to wake. Figure 25 gives the timing of the wake function. The parameter  $t_{WU}$  is given in the data sheet of the TLE6251DS [2] and is directly copied from the ISO 11898-5 norm[6]. It has to be understood as:

- In case the pulse on the bus is shorter than the minimum value of t<sub>WU</sub>, the device will/has to never wake up. This is to avoid parasitic wakes up due to Electro Magnetic disturbances for example.

- 2. In case the pulse on the bus is in between the minimum value and the maximum value, the device might wake up, depending on the temperature, production spread, etc....

- 3. In case the pulse on the bus is longer than the maximum value of  $t_{WU}$ , the device will/has to wake up.

- 4. Since the application micro controller might missed the first edge, the TLE6251DS is following the bus toggling.

Figure 25 Wake up timing.

#### Interface with micro controller. TLE6251DS.

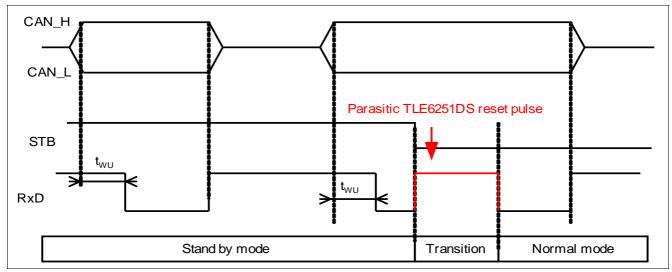

# 4.2.3.3 Delay from stand by to normal mode.

To achieve a very good quiescent current in standby mode, the TLE6251DS has two receivers, a low power mode and a normal mode. When the micro controller set the device to normal operation with the STB pin, and the bus is dominant, a parasitic pulse on the RxD pin is observed. This is due to the commutation from the low power receiver to the normal receiver. Figure 26 describes the timing of this possible parasitic pulse. Unless this parasitic pulse maximum duration isn't specified, it is never longer than 50µs.

Figure 26 Delay from stand by to normal mode timing.

Figure 27 Typical application for the TLE6251DS.

# 4.3 TLE6251G.

TLE6251G has the same pin-out compared to TLE6251DS (see **Figure 28**), with inverse logic for the STB pin, and with additional functionalities. The TLE6251G is able to wake a micro controller, as well as the power supplies on bus activities. We will now describe the logic pins of the TLE6251G. **Figure 34** describes the typical application interface between TLE6251G and the micro controller.

Figure 28 Pin out comparison TLE6251DS and TLE6251G

# 4.3.1 Pin TxD.

Please refer to Chapter 4.2.2

# 4.3.2 Pin RxD.

Please refer to Chapter 4.2.3, TLE6251DS without the wake behavior.

#### 4.3.3 Pin EN.

The EN pin (enable) is used to set the TLE6251G to normal operation. The device is disabled with a logical 0, and enabled with a logical 1. The EN pin has a pull down integrated. By default, the device is disabled.

# 4.3.4 Pin NSTB.