# Multilayer Capacitors, SMD Multilayer Ceramic Capacitors, 1812, X7R

#### SPECIFICATION:

| Construction form     | 1812               |

|-----------------------|--------------------|

| Ceramic type          | X7R                |

| Capacitance tolerance | ±10%               |

| Dimensions L x H x W  | 4.5 x 3.0 x 3.2 mm |

| Temperature range     | -55+125 ℃          |

| Height                | 3.0 mm             |

| Length                | 4.5 mm             |

| Width                 | 3.2 mm             |

### PRODUCT RANGE:

| Art. Nr.               | Capacitance | Rated voltage |

|------------------------|-------------|---------------|

| RND 150-1812B102K302N1 | 1.0 nF      | 3000 VDC      |

| RND 150-1812B103K102N1 | 10 nF       | 1000 VDC      |

| RND 150-1812B103K631N1 | 10 nF       | 630 VDC       |

| RND 150-1812B104K631N1 | 100 nF      | 630 VDC       |

| RND 150-1812B105K101N1 | 1.0 μF      | 100 VDC       |

| RND 150-1812B222K631N1 | 2.2 nF      | 630 VDC       |

## PCB design

Chip components are susceptible to board stress since the component itself is mounted directly on the board. They are also sensitive to mechanical and thermal stress when solder, which may cause chip cracked.

Please take solder form and component layout into consideration to eliminate stress.

#### Pattern form

(1) Placing of chip components and component.

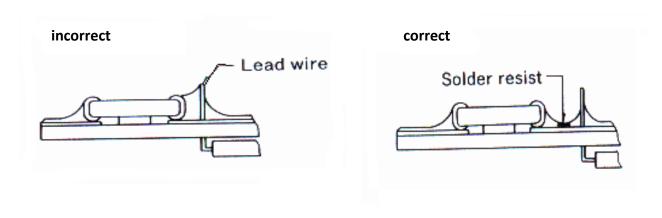

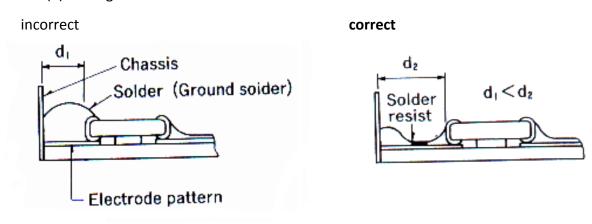

(2) Placing close to chassis.

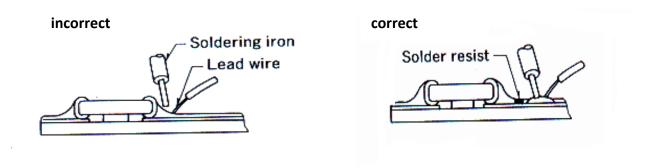

(3) Placing leaded components after chip component.

## (4) Lateral mounting

## Component direction

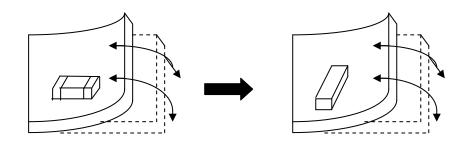

To design a mounting position that minimizes the stress imposed on the chip during flexing or bending of the board.

(1) put the component lateral to the direction in which stress acts.

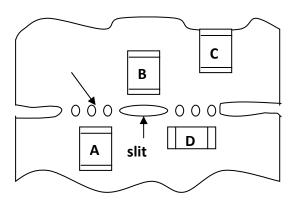

(2) Component layout close to board separation point. Susceptibility to stress in the order: A > C > B = D

#### 12.3. Land Pattern

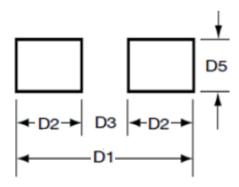

When capacitors are mounted on P.C. board, the amount of solder directly affect the performance of capacitors. Therefore, the following items should be carefully considered in the design of solder land pattern.

- (1) The greater the amount of solder, the higher the stress on the chip capacitors, and lead to cracking and breaking likely. It is necessary the appropriate size and configuration of the solder pads should be designed to have proper amount of solder on the termination.

- (2) When two or more capacitors are soldered together onto the same land or pad, the pad must be designed so that each capacitor's soldering point is separated by solderresist.

The following diagram and table for recommended pad dimensions.

Dimensions in millimeters

0201 0402 0603 0805 1210 1808 1825 2220 2225 **Type** 1206 1812 4.00 D1 0.65 1.50 2.30 2.80 4.00 5.40 5.30 5.30 7.00 7.00 0.21 D2 0.50 0.80 0.90 0.90 0.90 1.05 0.90 0.90 1.35 1.35 0.23 0.50 0.70 1.00 2.20 2.20 3.30 3.50 3.50 4.30 4.30 D3 0.30 D5 0.50 0.80 1.30 1.60 2.50 2.30 3.80 6.50 5.00 6.50

Unit: mm