### ANALOG DEVICES

# Ultralow Power Energy Harvester PMUs with MPPT and Charge Management

### **Data Sheet**

### ADP5091/ADP5092

#### **FEATURES**

Boost regulator with maximum power point tracking (MPPT) with dynamic sensing or no sensing mode Hysteresis mode for best ultralight load efficiency Operating quiescent current of SYS pin ( $V_{IN} > V_{CBP} \ge V_{MINOP}$ ): 510 nA Sleeping quiescent current of SYS pin (V<sub>CBP</sub> < V<sub>MINOP</sub>): 390 nA Input voltage operating range: 0.08 V to 3.3 V Fast cold start from 380 mV (typical) with charge pump Programmable shutdown point on MINOP pin based on the input open circuit voltage (OCV) 150 mA regulated output from 1.5 V to 3.6 V Battery terminal charging threshold (2.2 V to 5.2 V) to support charging storage elements **Optional BACK\_UP power path management** Radio frequency (RF) transmission conducive to shutting down the switcher temporarily via microcontroller unit (MCU) communication

#### **APPLICATIONS**

Photovoltaic (PV) cell energy harvesting Thermoelectric generators (TEGs) energy harvesting Industrial monitoring Self powered wireless sensor devices Portable and wearable devices with energy harvesting

#### **GENERAL DESCRIPTION**

The ADP5091/ADP5092 are intelligent, integrated energy harvesting, ultralow power management unit (PMU) solutions that convert dc power from PV cells or TEGs. These devices charge storage elements such as rechargeable Li-Ion batteries, thin film batteries, super capacitors, or conventional capacitors, and power up small electronic devices and battery free systems.

The ADP5091/ADP5092 provide efficient conversion of the harvested limited power from a 6  $\mu$ W to 600 mW range with submicrowatt operation losses. With the internal cold start circuit, the regulator can start operating at an input voltage as low as 380 mV. After cold startup, the regulator is functional at an input voltage range of 0.08 V to 3.3 V. An additional 150 mA regulated output can be programmed by an external resistor divider or the VID pin.

The MPPT control keeps the input voltage ripple in a fixed range to maintain stable dc-to-dc boost conversion. The dynamic sensing mode and no sensing mode, both programming regulation points of the input voltage, allow extraction of the highest possible energy from the harvester. A programmable minimum operation threshold enables boost shutdown during a low input condition.

#### Rev. A

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

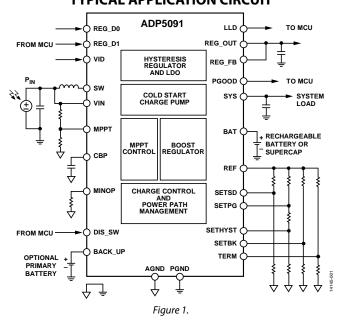

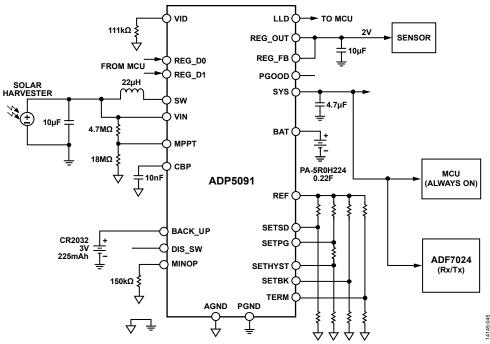

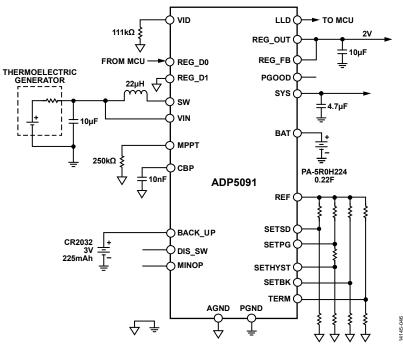

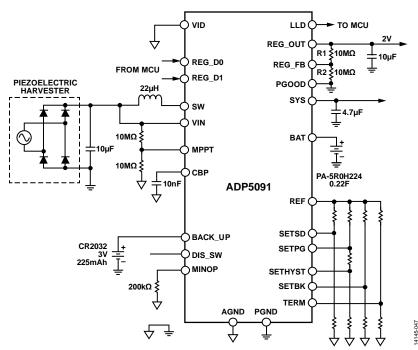

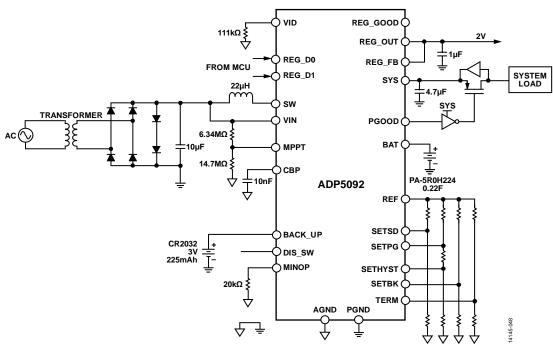

### TYPICAL APPLICATION CIRCUIT

As a low light indicator for a microprocessor, the LLD pin of the ADP5091 is the MINOP comparator output. However, the REG\_GOOD flag of the ADP5092 monitors the REG\_OUT voltage. In addition, the DIS\_SW pin can temporarily shut down the boost regulator and is RF transmission friendly.

The charging control function of the ADP5091/ADP5092 protects the rechargeable energy storage, which is achieved by monitoring the battery voltage with the programmable charging termination voltage and the shutdown discharging voltage. In addition, a programmable PGOOD flag monitors the SYS voltage.

An optional primary cell battery can be connected and managed by an integrated power path management control block that is programmable to switch the power source from the energy harvester, rechargeable battery, and primary cell battery.

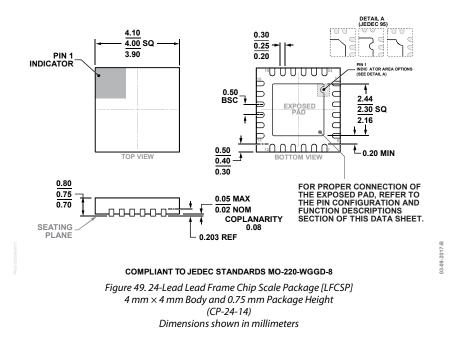

The ADP5091/ADP5092 are available in a 24-lead LFCSP and are rated for a  $-40^{\circ}$ C to  $+125^{\circ}$ C temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016-2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features                                                                          |

|-----------------------------------------------------------------------------------|

| Applications1                                                                     |

| Typical Application Circuit 1                                                     |

| General Description                                                               |

| Revision History 2                                                                |

| Detailed Functional Block Diagram 3                                               |

| Specifications                                                                    |

| Regulated Output Specifications 6                                                 |

| Absolute Maximum Ratings7                                                         |

| Thermal Resistance7                                                               |

| ESD Caution7                                                                      |

| Pin Configurations and Function Descriptions                                      |

| Typical Performance Characteristics                                               |

| Theory of Operation                                                               |

| Fast Cold Start-Up Circuit ( $V_{SYS} < V_{SYS_TH}$ , $V_{IN} > V_{IN_COLD}$ ) 16 |

| Main Boost Regulator ( $V_{BAT\_TERM} > V_{SYS} > V_{SYS\_TH}$ )16                |

| VIN Open Circuit and MPPT16                                                       |

| Minimum Operation Threshold Function17                                            |

| Disabling Boost17                                                                 |

| Regulated Output Working Mode17                                                   |

| REG_D0 and REG_D117                                                               |

#### **REVISION HISTORY**

| 5/2017—Rev. 0 to Rev. A                                 |            |

|---------------------------------------------------------|------------|

| Changes to Figure 2                                     |            |

| Changes to Figure 7, Figure 10, Figure 7 Caption, and 1 | Figure 10  |

| Caption                                                 |            |

| Changes to Figure 11 and Figure 11 Caption              |            |

| Changed CP-24-10 to CP-24-14                            | Throughout |

| Updated Outline Dimensions                              |            |

| Changes to Ordering Guide                               |            |

#### 7/2016—Revision 0: Initial Version

|    | Regulated Output Configuration             | 17 |

|----|--------------------------------------------|----|

|    | REG_GOOD (ADP5092 Only)                    | 18 |

|    | Energy Storage Charge Management           | 18 |

|    | Backup Storage Path                        | 18 |

|    | Backup and BAT Selection Threshold         | 19 |

|    | Battery Overcharging Protection            | 19 |

|    | Battery Discharging Protection             | 19 |

|    | Power Good (PGOOD)                         | 20 |

|    | Power Path Working Flow                    | 20 |

|    | Current-Limit and Short-Circuit Protection | 20 |

|    | Thermal Shutdown                           | 21 |

| Aŗ | oplications Information                    | 23 |

|    | Energy Harvester Selection                 | 23 |

|    | Energy Storage Element Selection           | 23 |

|    | Inductor Selection                         | 23 |

|    | Capacitor Selection                        | 24 |

|    | Layout and Assembly Considerations         | 24 |

|    | Typical Application Circuits               | 25 |

| Fa | ctory Programmable Options                 | 27 |

| 01 | utline Dimensions                          | 28 |

|    | Ordering Guide                             | 28 |

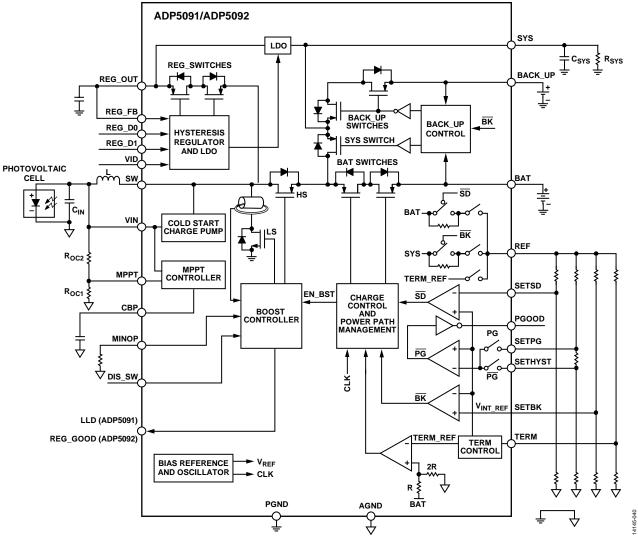

### **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Detailed Functional Block Diagram

### SPECIFICATIONS

Voltage input ( $V_{IN}$ ) = 1.2 V,  $V_{SYS} = V_{BAT} = 3$  V,  $T_J = -40^{\circ}$ C to +125°C for minimum/maximum specifications, and  $T_A = 25^{\circ}$ C for typical specifications, unless otherwise noted. External components include the following: inductance (L) = 22  $\mu$ H, input capacitance ( $C_{IN}$ ) = 4.7  $\mu$ F, and  $C_{SYS} = 4.7 \mu$ F.

| Parameter                                                                         | Symbol                                    | Test Conditions/Comments                           | Min  | Тур              | Max  | Unit |

|-----------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|------|------------------|------|------|

| QUIESCENT CURRENT                                                                 |                                           |                                                    |      |                  |      |      |

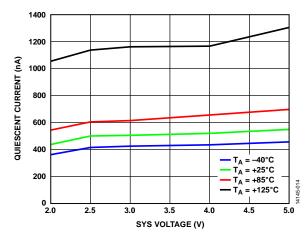

| Operating Quiescent Current of SYS Pin<br>( $V_{IN} > V_{CBP} \ge V_{MINOP}$ )    | Iq_sys                                    | REG_D0 = low, REG_D1 = low                         |      | 510              | 1000 | nA   |

|                                                                                   |                                           | REG_D0 = high, REG_D1 = low                        |      | 650              | 1150 | nA   |

|                                                                                   |                                           | $REG_D0 = low, REG_D1 = high$                      |      | 750              | 1290 | nA   |

|                                                                                   |                                           | REG_D0 = high, REG_D1 = high                       |      | 760              | 1300 | nA   |

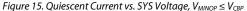

| Sleeping Quiescent Current of SYS Pin<br>(V <sub>CBP</sub> < V <sub>MINOP</sub> ) | I <sub>IQ_SLEEP_SYS</sub>                 | REG_D0 = low, REG_D1 = low                         |      | 390              | 880  | nA   |

| COLD START CIRCUIT                                                                |                                           |                                                    |      |                  |      |      |

| Minimum Input Voltage for Cold Start                                              | V <sub>IN_COLD</sub>                      | $V_{SYS} = 0 V, 0^{\circ}C < T_A < 85^{\circ}C$    |      | 380              | 500  | mV   |

| Minimum Input Power for Cold Start<br>End of Cold Start Operation                 | PIN_COLD                                  |                                                    |      | 6                |      | μW   |

| Threshold                                                                         | V <sub>SYS_TH</sub>                       |                                                    | 1.73 | 1.87             | 2.00 | V    |

| Hysteresis                                                                        | V <sub>SYS_HYS</sub>                      |                                                    |      | 95               |      | mV   |

| BOOST REGULATOR                                                                   |                                           |                                                    |      |                  |      |      |

| Input Voltage Operating Range                                                     | VIN                                       | Cold start completed                               | 0.08 |                  | 3.3  | V    |

| Input Power Operating Range                                                       | P <sub>IN</sub>                           | Cold start completed, $V_{IN} = 3 V$               |      |                  | 600  | mW   |

| Start Charging BAT Threshold on SYS                                               | V <sub>SYS_CHG</sub>                      |                                                    | 2.00 | 2.19             | 2.35 | V    |

| Start Charging BAT Hysteresis on SYS                                              | $V_{\text{SYS}\_\text{CHG}\_\text{HYS}}$  |                                                    |      | 150              |      | mV   |

| Input Peak Current                                                                | I <sub>IN_PEAK</sub>                      | Factory trim, 1 bit, Option 0                      |      | 200              | 250  | mA   |

|                                                                                   |                                           | Option 1                                           |      | 300              |      | mA   |

| Low-Side Switch On Resistance                                                     | RLS_DS_ON                                 | Pin to pin measurement                             |      | 0.44             | 0.6  | Ω    |

| High-Side Switch On Resistance                                                    | R <sub>HS_DS_ON</sub>                     | Pin to pin measurement                             |      | 0.85             | 1.2  | Ω    |

| SYS Switch On Resistance                                                          | R <sub>SYS_DS_ON</sub>                    |                                                    |      | 0.32             | 0.70 | Ω    |

| DIS_SW Voltage                                                                    |                                           |                                                    |      |                  |      |      |

| High                                                                              | $V_{\text{DIS}\_\text{SW}\_\text{HIGH}}$  |                                                    | 1    |                  |      | V    |

| Low                                                                               | $V_{\text{DIS}\_\text{SW}\_\text{LOW}}$   |                                                    |      |                  | 0.5  | V    |

| DIS_SW Delay                                                                      | $t_{\text{DIS}\_\text{SW}\_\text{DELAY}}$ |                                                    |      | 1                |      | μs   |

| VIN CONTROL AND MINOP                                                             |                                           |                                                    |      |                  |      |      |

| VIN Open Circuit Voltage                                                          |                                           |                                                    |      |                  |      |      |

| Default Sampling Cycle                                                            | t <sub>ocv_cycle</sub>                    | Factory trim, 2 bit (4 sec, 8 sec, 16 sec, 32 sec) |      | 16               |      | sec  |

| Sampling Time                                                                     | tocv_sampl                                |                                                    |      | 256              |      | ms   |

| MINOP Bias Current                                                                | IMINOP                                    |                                                    | 1.58 | 2.00             | 2.45 | μΑ   |

| MINOP Operation Voltage Threshold<br>of Dynamic MPPT Sensing Mode                 | Vminop_dsm                                |                                                    |      |                  | 1.5  | V    |

| MPPT Bias Current of MPPT No<br>Sensing Mode                                      | I <sub>MPPT</sub>                         |                                                    | 1.7  | 2.0              | 2.3  | μA   |

| LLD (ADP5091 Only)                                                                |                                           |                                                    |      |                  |      |      |

| Pull-Up Resistor                                                                  |                                           |                                                    |      | 12               | 17   | kΩ   |

| Pull-Down Resistor                                                                |                                           |                                                    |      | 12               | 17   | kΩ   |

| High Voltage                                                                      | $V_{\text{LLD}\_\text{IH}}$               |                                                    |      | $V_{\text{REG}}$ |      | V    |

| Leakage Current at CBP Pin                                                        | ICBP_LEAK                                 |                                                    |      | 10               | 2000 | pА   |

### **Data Sheet**

### ADP5091/ADP5092

| Parameter                         | Symbol                  | Test Conditions/Comments                            | Min                | Тур   | Мах                           | Unit |

|-----------------------------------|-------------------------|-----------------------------------------------------|--------------------|-------|-------------------------------|------|

| ENERGY STORAGE MANAGEMENT         |                         |                                                     |                    |       |                               |      |

| Internal Reference Voltage        | VINT_REF                |                                                     | 0.955              | 1.011 | 1.067                         | V    |

| Battery Stop Discharging          |                         |                                                     |                    |       |                               |      |

| Threshold                         | VSETSD                  |                                                     | 2.0                |       | $V_{\text{BAT}\_\text{TERM}}$ | V    |

| Hysteresis Resistor               | R <sub>SETSD_HYS</sub>  |                                                     | 80                 | 115   | 160                           | kΩ   |

| Battery Terminal Charging         |                         |                                                     |                    |       |                               |      |

| Threshold                         | V <sub>BAT_TERM</sub>   |                                                     | 2.2                |       | 5.2                           | V    |

| Hysteresis                        | VBAT_TERM_HYS           |                                                     |                    | 3     | 3.1                           | %    |

| PGOOD Rising Threshold at SYS Pin | V <sub>SYS_PG</sub>     |                                                     | V <sub>SETSD</sub> |       | V <sub>BAT_TERM</sub>         | V    |

| PGOOD Pull-Up Resistor            |                         |                                                     |                    | 11.6  | 17.0                          | kΩ   |

| PGOOD Pull-Down Resistor          |                         |                                                     |                    | 11.6  | 17.0                          | kΩ   |

| PGOOD High Voltage                | $V_{PGOOD_HIGH}$        |                                                     |                    | Vsys  |                               | v    |

| Battery Switches On Resistance    | R <sub>BAT_SW_ON</sub>  | Pin to pin measurement                              |                    | 0.59  | 0.85                          | Ω    |

| Battery Source Current            | IBAT                    |                                                     |                    |       | 1                             | А    |

| Leakage Current at BAT Pin        | I <sub>BAT_LEAK</sub>   | $V_{BAT} = 2 V, V_{SETSD} = 2.2 V, V_{SYS} = 2 V$   |                    | 22    | 50                            | nA   |

|                                   |                         | $V_{BAT} = 3.3 V, V_{SETSD} = 2.2 V, V_{SYS} = 0 V$ |                    | 3.5   | 35                            | nA   |

| BACK_UP POWER PATH                |                         |                                                     |                    |       |                               |      |

| Turning Off BACK_UP Switch        |                         |                                                     |                    |       |                               |      |

| Threshold on BAT                  | V <sub>SETBK</sub>      |                                                     | 2.0                |       | V <sub>BAT_TERM</sub>         | V    |

| Hysteresis Resistor               | Rsetbk_hys              |                                                     | 80                 | 115   | 160                           | kΩ   |

| BACK_UP Switches On Resistance    |                         |                                                     |                    | 0.85  | 1.20                          | Ω    |

| BACK_UP and BAT Comparator        |                         | $V_{SYS} \ge V_{SYS_{TH}}$                          |                    |       |                               |      |

| Offset                            | V <sub>BKP_OFFSET</sub> |                                                     | 158                | 190   | 271                           | mV   |

| Hysteresis                        | V <sub>BAT_HYS</sub>    |                                                     | 68                 | 75    | 108                           | mV   |

| BACK_UP Current Capability        | I <sub>BKP</sub>        | V <sub>SYS</sub> < V <sub>SYS_TH</sub>              |                    | 250   |                               | μA   |

| Leakage Current at BACK_UP Pin    | I <sub>BKP_LEAK</sub>   | $V_{BACK\_UP} = V_{SYS} = V_{BAT} = 3 V$            |                    | 16    | 40                            | nA   |

| THERMAL SHUTDOWN                  |                         |                                                     |                    |       |                               |      |

| Threshold                         | T <sub>SHDN</sub>       | $V_{SYS} \ge V_{SYS_{TH}}$                          |                    | 142   |                               | °C   |

| Hysteresis                        | T <sub>HYS</sub>        |                                                     |                    | 15    |                               | °C   |

#### **REGULATED OUTPUT SPECIFICATIONS**

$V_{IN} = 1.2 \text{ V}, V_{SYS} = V_{BAT} = 3 \text{ V}, V_{REG_OUT} = 2 \text{ V}, L = 22 \text{ }\mu\text{H}, C_{IN} = 4.7 \text{ }\mu\text{F}, C_{SYS} = 4.7 \text{ }\mu\text{F}, C_{REG_OUT} = 4.7 \text{ }\mu\text{F}, T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C} \text{ for minimum/maximum specifications, and } T_A = 25^{\circ}\text{C} \text{ for typical specifications, unless otherwise noted.}$

| Parameter                                | Symbol                       | Test Conditions/Comments                                                                                        | Min                             | Тур                             | Max                             | Unit   |

|------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|--------|

| REGULATED OUTPUT                         | -                            |                                                                                                                 |                                 |                                 |                                 |        |

| Output Options by VID Control            | VREG OUT                     |                                                                                                                 | 1.5                             |                                 | 3.6                             | v      |

| Rating Current                           | IREG OUT                     | $V_{REG OUT} = 1.5 V \text{ to } 3.6 V$                                                                         |                                 | 150                             |                                 | mA     |

| REG_OUT Pull-Down Resistance             | Rreg_out                     |                                                                                                                 |                                 | 235                             |                                 | Ω      |

| REG_OUT IN BOOST MODE                    | _                            |                                                                                                                 |                                 |                                 |                                 |        |

| REG_OUT Wake Threshold                   | V <sub>REG_WAKE</sub>        |                                                                                                                 | 1.008 ×<br>V <sub>reg_out</sub> | 1.027 ×<br>V <sub>reg_out</sub> | 1.048 ×<br>V <sub>reg_out</sub> | V      |

| REG_OUT Wake Threshold<br>Hysteresis     | Vreg_wake_hys                |                                                                                                                 |                                 | 1                               |                                 | %      |

| Adjustable REG_OUT Wake<br>Threshold     | Vadj_reg_wake                |                                                                                                                 | 1.008                           | 1.028                           | 1.048                           | V      |

| Adjustable REG_OUT Sleep<br>Threshold    | Vadj_reg_sleep               |                                                                                                                 | 1.018                           | 1.038                           | 1.058                           | V      |

| High-Side Switches On Resistance         | R <sub>BST_DS_ON</sub>       |                                                                                                                 |                                 | 1.63                            | 2.15                            | Ω      |

| Current-Limit Threshold of Boost<br>Mode | I <sub>REG_BST_LIM</sub>     |                                                                                                                 |                                 | 100                             | 155                             | mA     |

| REG_OUT IN LOW DROPOUT (LDO)<br>MODE     |                              |                                                                                                                 |                                 |                                 |                                 |        |

| REG_OUT Accuracy                         | $V_{\text{REG}\_LDO}$        | $0 \mu\text{A} < I_{\text{OUT}} < 150 \text{mA}, V_{\text{SYS}} = (V_{\text{REG}_{\text{OUT}}} + 0.5 \text{V})$ | -3.5                            |                                 | +3.5                            | %      |

| Adjustable REG_OUT Accuracy              | $V_{\text{REG\_LDO\_ADJ}}$   | louτ = 1 mA                                                                                                     | 0.999                           | 1.015                           | 1.028                           | V      |

|                                          |                              | $0 \mu A < I_{OUT} < 150 mA, V_{SYS} = (V_{REG_OUT} + 0.5 V)$                                                   | 0.985                           | 1.015                           | 1.045                           | V      |

| REG_OUT Dropout                          | VREG_DROP                    | Ι <sub>ουτ</sub> = 150 mA                                                                                       |                                 | 200                             |                                 | mV     |

| Current-Limit Threshold of LDO<br>Mode   | I <sub>REG_LIM</sub>         | $V_{SYS} \geq V_{SYS\_TH}$                                                                                      | 200                             | 260                             |                                 | mA     |

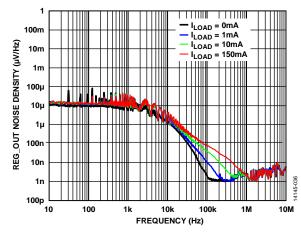

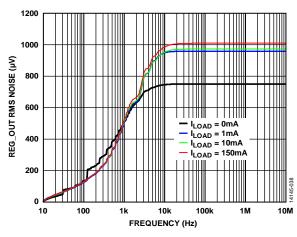

| Output Noise                             | OUT <sub>NOISE</sub>         | 10 Hz to 100 kHz                                                                                                |                                 | 700                             |                                 | μV rms |

| Power Supply Rejection Ratio             | PSRR                         | 100 Hz                                                                                                          |                                 | 60                              |                                 | dB     |

|                                          |                              | 1 kHz                                                                                                           |                                 | 40                              |                                 | dB     |

| REG_D0 and REG_D1                        |                              |                                                                                                                 |                                 |                                 |                                 |        |

| Input Logic                              |                              |                                                                                                                 |                                 |                                 |                                 |        |

| High                                     | Vreg_dx_ih                   |                                                                                                                 | 1.2                             |                                 |                                 | V      |

| Low                                      | $V_{\text{REG}_DX_IL}$       |                                                                                                                 |                                 |                                 | 0.4                             | V      |

| Input Leakage Current                    | IREG_DX_LEAK                 |                                                                                                                 |                                 | 20                              |                                 | nA     |

| REG_GOOD (ADP5092 ONLY)                  |                              |                                                                                                                 |                                 |                                 |                                 |        |

| Rising Threshold                         | $V_{\text{REG}_{GOOD}}$      |                                                                                                                 | 89.5                            | 92.5                            | 95.7                            | %      |

| Hysteresis V <sub>REG</sub>              |                              |                                                                                                                 |                                 | 2                               |                                 | %      |

| Pull-Up Resistor                         |                              |                                                                                                                 |                                 | 11.6                            | 17                              | kΩ     |

| Pull-Down Resistor                       |                              |                                                                                                                 |                                 | 11.6                            | 17                              | kΩ     |

| High Voltage                             | $V_{\text{REG}_{GOOD}_{IH}}$ |                                                                                                                 |                                 | V <sub>REG_OUT</sub>            |                                 | V      |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                                                                                | Rating           |

|----------------------------------------------------------------------------------------------------------|------------------|

| VIN, MPPT, CBP, MINOP                                                                                    | -0.3 V to +3.6 V |

| DIS_SW, TERM, SETPG, SETSD, SETBK,<br>PGOOD, SETHYST, REF, REG_D0, VID,<br>REG_D1, LLD, REG_GOOD to AGND | –0.3 V to +6.0 V |

| SW, SYS, BAT, BACK_UP, REG_OUT, REG_FB to PGND                                                           | –0.3 V to +6.0 V |

| PGND to AGND                                                                                             | –0.3 V to +0.3 V |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 4.

| Package Type  | θ <sub>JA</sub> | οıc | Unit |

|---------------|-----------------|-----|------|

| 24-Lead LFCSP | 58.7            | 36  | °C/W |

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

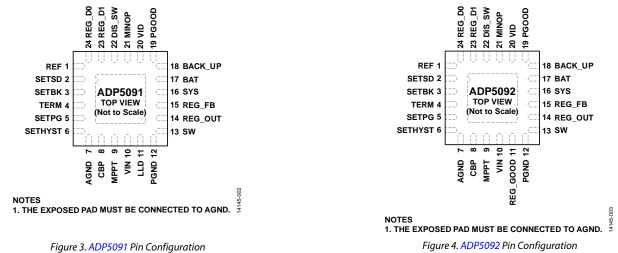

### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### **Table 5. Pin Function Descriptions**

| Pin No. <sup>1</sup>     |     |          |                                                                                                                                                                                                                                                        |  |

|--------------------------|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADP5091 ADP5092 Mnemonic |     | Mnemonic | Description                                                                                                                                                                                                                                            |  |

| 1                        | 1   | REF      | Internal Voltage Reference Monitoring Node for the SETSD, SETPG, SETBK, and TERM Pins.                                                                                                                                                                 |  |

| 2                        | 2   | SETSD    | Shutdown Setting. The SETSD pin sets the shutdown discharging voltage based on the BAT pin voltage level.                                                                                                                                              |  |

| 3                        | 3   | SETBK    | BACK_UP Disabled Threshold Monitoring BAT Voltage Setting. Connect the SETBK pin to the AGND pin without the BACK_UP storage element.                                                                                                                  |  |

| 4                        | 4   | TERM     | Termination Charging Voltage. This pin sets the termination charging voltage based on the BAT pin voltage level.                                                                                                                                       |  |

| 5                        | 5   | SETPG    | Power-Good Rising Threshold Monitoring SYS Node Voltage Level Setting.                                                                                                                                                                                 |  |

| 6                        | 6   | SETHYST  | PGOOD Falling Hysteresis Setting. Connect a resistor between SETPG and SETHYST to program the PGOOD falling hysteresis.                                                                                                                                |  |

| 7                        | 7   | AGND     | Analog Ground.                                                                                                                                                                                                                                         |  |

| 8                        | 8   | СВР      | Capacitor Bypass. This pin samples and holds the maximum power point level. Connect a 10 nF capacitor from the CBP pin to the AGND pin. When the MPPT pin is disabled, tie the CBP pin to an external reference that is lower than the VIN pin.        |  |

| 9                        | 9   | MPPT     | Maximum Power Point Tracking. This pin sets the maximum power point ratio for the different energy harvesters with a resistor divider. In no sensing mode, place a resistor through AGND to set the MPPT voltage. The typical current value is 2.0 μA. |  |

| 10                       | 10  | VIN      | Input Supply from Energy Harvester Source. Connect at least a 10 $\mu F$ capacitor as close as possible between VIN and PGND.                                                                                                                          |  |

| 11                       | N/A | LLD      | Low Light Density Indicator to Microcontroller for the ADP5091. LLD pulls high at the MINOP voltage higher than the CBP voltage.                                                                                                                       |  |

| N/A                      | 11  | REG_GOOD | Regulated Output Power Good for the ADP5092.                                                                                                                                                                                                           |  |

| 12                       | 12  | PGND     | Power Ground.                                                                                                                                                                                                                                          |  |

| 13                       | 13  | SW       | Switching Node for the Inductive Boost Regulator with a Connection to an External Inductor. Connect a 22 $\mu$ H inductor between SW and VIN.                                                                                                          |  |

| 14                       | 14  | REG_OUT  | Regulated Output. Connect at least a 4.7 µF capacitor as close as possible between REG_OUT and PGND.                                                                                                                                                   |  |

| 15                       | 15  | REG_FB   | Regulated Output Feedback Voltage Sense Input. The fixed output connects this pin to REG_OUT.<br>The adjustable output connects this pin to a resistor divider from REG_OUT.                                                                           |  |

| 16                       | 16  | SYS      | Output Supply to System Load. Connect at least a 4.7 $\mu\text{F}$ capacitor as close as possible between SYS and PGND.                                                                                                                                |  |

| 17                       | 17  | BAT      | SYS Output Supply Storage. This pin places the rechargeable battery or super capacitor as a storage for the SYS output supply.                                                                                                                         |  |

| 18                       | 18  | BACK_UP  | Optional Input Supply from the Backup Primary Battery Cell.                                                                                                                                                                                            |  |

| Pin No. <sup>1</sup> |         |          |                                                                                                                                                                                                                                                                                                                                                    |  |

|----------------------|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADP5091              | ADP5092 | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                        |  |

| 19                   | 19      | PGOOD    | Output Signal to Microcontroller. This pin maintains a pulled high level when SYS is higher than the SETPG threshold.                                                                                                                                                                                                                              |  |

| 20                   | 20      | VID      | Voltage Configuration Pin for REG_OUT. This pin sets up to eight different regulated outputs tied low through a resistor to AGND. The output configuration details are in Table 7.                                                                                                                                                                 |  |

| 21                   | 21      | MINOP    | Minimum Operating Power. Place a resistor on MINOP to set the minimum operating input voltage level. The boost regulator starts switching when the CBP voltage exceeds the MINOP voltage. When the MINOP pin is floating, the IC operates in no sensing mode with a fixed MPPT level. Connect this pin through AGND to disable the MINOP function. |  |

| 22                   | 22      | DIS_SW   | Control Signal from Microcontroller or RF Transceiver to Stop Switching Boost Charger.                                                                                                                                                                                                                                                             |  |

| 23                   | 23      | REG_D1   | Regulated Output Working Mode Set D1. Enable LDO mode by pulling this pin high.                                                                                                                                                                                                                                                                    |  |

| 24                   | 24      | REG_D0   | Regulated Output Working Mode Set D0. Enable boost mode by pulling this pin high.                                                                                                                                                                                                                                                                  |  |

|                      |         | EPAD     | Exposed Pad. The exposed pad must be connected to AGND.                                                                                                                                                                                                                                                                                            |  |

<sup>1</sup> N/A means not applicable.

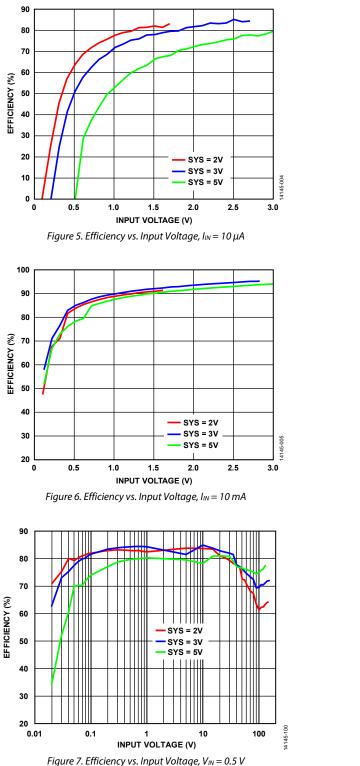

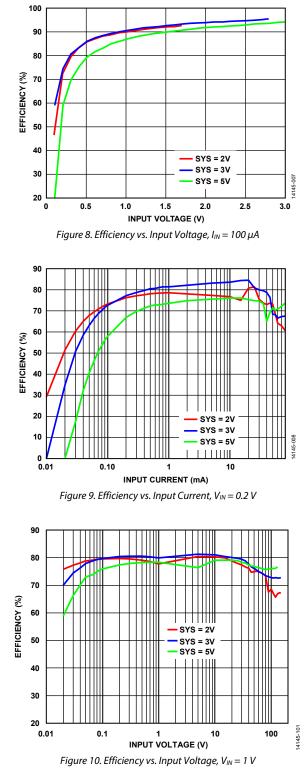

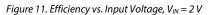

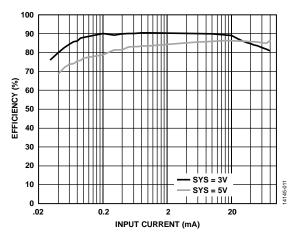

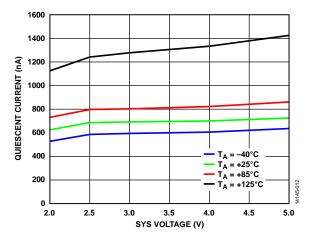

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{\text{BAT\_TERM}} = 3.5 \text{ V}, V_{\text{SYS}\_PG} = 2.8 \text{ V}, V_{\text{SETSD}} = 2.4 \text{ V}, \text{MPPT} (\text{OCV}) = 80\%, L = 22 \text{ }\mu\text{H}, C_{\text{IN}} = 10 \text{ }\mu\text{F}, C_{\text{SYS}} = 4.7 \text{ }\mu\text{F}, C_{\text{REG\_OUT}} = 10 \text{ }\mu\text{F}, C_{\text{CBP}} = 10 \text{ }n\text{F}.$

### **Data Sheet**

#### 100 95 90 EFFICIENCY (%) 85 80 75 SYS = 3V SYS = 5V 70 65 60 L 0.01 0.1 1 10 100 14145-102 INPUT VOLTAGE (V)

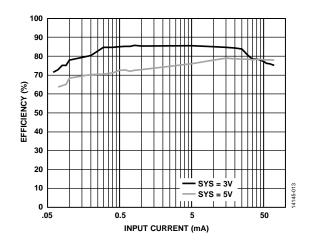

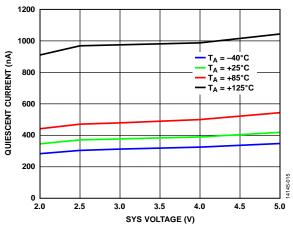

Figure 12. Efficiency vs. Input Current,  $V_{IN} = 1 V$ ,  $V_{REG_OUT} = 2 V$ ,  $I_{REG_OUT} = 10 \mu A$

Figure 13. Quiescent Current vs. SYS Voltage,  $V_{REG_{D0}} = V_{REG_{D1}} = V_{SYS}$ ,  $V_{MINOP} \le V_{CBP}$

### ADP5091/ADP5092

Figure 14. Efficiency vs. Input Current,  $V_{IN} = 0.5 V$ ,  $V_{REG_{OUT}} = 2 V$ ,  $I_{REG_{OUT}} = 10 \mu A$

Figure 16. Quiescent Current vs. SYS Voltage, V<sub>MINOP</sub> > V<sub>CBP</sub>

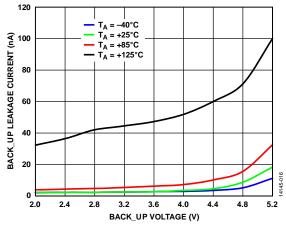

Figure 17. BACK\_UP Leakage Current vs. BACK\_UP Voltage

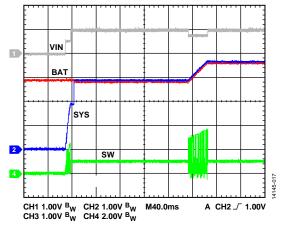

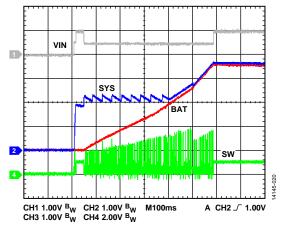

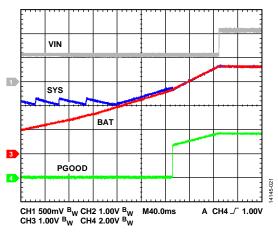

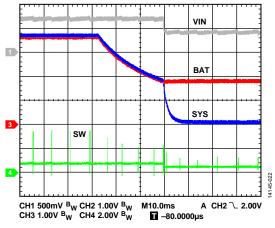

Figure 18. Startup with 100 µF Battery, VBAT > VSETSD

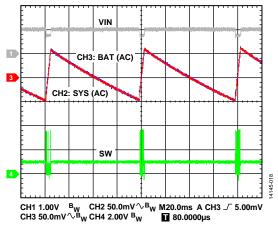

Figure 19. Output Ripple of TERM Function with 100 µA Load

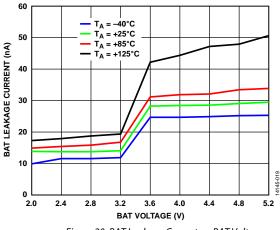

Figure 20. BAT Leakage Current vs. BAT Voltage

Figure 23. Battery Protection Function Waveform

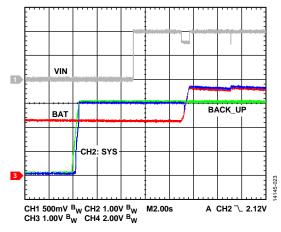

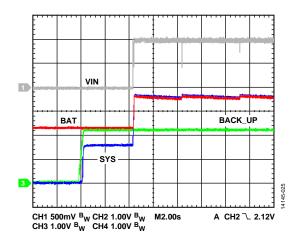

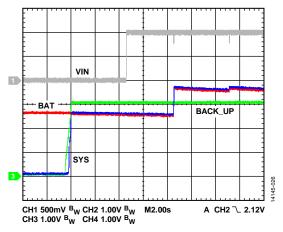

Figure 24. Backup Function, V<sub>BAT</sub> < V<sub>SETBK</sub>, V<sub>BACK\_UP</sub> > V<sub>BAT</sub>

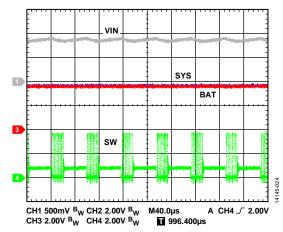

Figure 25. Main Boost Pulse Frequency Modulation (PFM) Waveform with 200  $\mu A$  Load

Figure 26. BACK\_UP Function, VBAT < VSETBK, VBACK\_UP < VBAT

### ADP5091/ADP5092

Figure 29. MPPT No Sensing Mode,  $R_{MPPT} = 400 \text{ k}\Omega$

Figure 32. MPPT Dynamic Sensing Mode

Figure 34. REG\_OUT Ripple (Boost Mode)

### Data Sheet

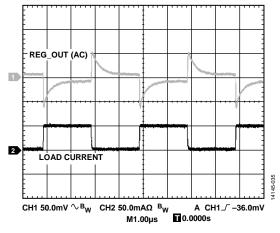

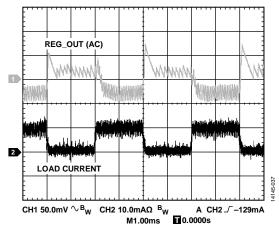

Figure 36. REG\_OUT Load Transient (LDO),  $I_{REG_OUT}$  from 10  $\mu$ A to 50 mA

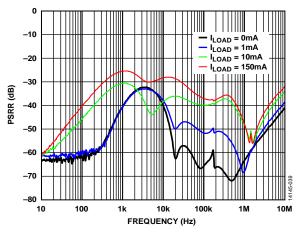

Figure 37. REG\_OUT Noise Density vs. Frequency at Various Current Loads ( $I_{LOAD}$ )

### ADP5091/ADP5092

Figure 38. REG\_OUT Load Transient (Hybrid),  $I_{\text{REG}_{OUT}}$  from 10  $\mu\text{A}$  to 10 mA

Figure 40. Power Supply Rejection Ratio (PSRR) vs. Frequency

### THEORY OF OPERATION

The ADP5091/ADP5092 are intelligent, integrated energy harvesting, ultralow power management solutions that include a cold start-up circuit, one synchronous main boost controller, and one regulated output hybrid controller with integrated switches, a charging controller with integrated switches, and backup power path switches. The main boost controller converts maximum power from low voltage, high impedance dc sources, such as PV cells, TEGs, and piezoelectric modules, to store energy in a rechargeable battery or capacitor with storage protection and provides power to the load. Another regulated output with automatic hysteresis boost/LDO mode, or pure LDO mode, is optimized to provide high efficiency across low output currents (10  $\mu$ A), see Figure 14) to high currents of 200 mA. The ADP5091/ ADP5092 can also control an additional power path from a primary battery cell to the system. An external signal can temporarily stop the two boost circuits to prevent interference with RF transmission.

## $\label{eq:FAST_COLD_START-UP_CIRCUIT} \begin{aligned} FAST COLD START-UP CIRCUIT (V_{\text{SYS}} < V_{\text{SYS}\_\text{TH}}, \\ V_{\text{IN}} > V_{\text{IN}\_\text{COLD}}) \end{aligned}$

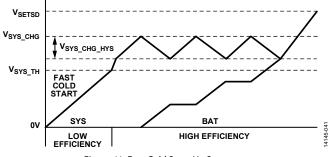

The fast cold start-up circuit extracts energy available at the VIN pin and charges only the capacitors at the SYS pin up to  $V_{SYS\_TH}$  above which the main boost regulator and charge controller start working. The efficient boost regulator charges storage elements on the BAT pin when the SYS voltage is more than the internal BAT charging threshold ( $V_{SYS\_CHG}$ ). When the SYS voltage is less than the internal BAT charging threshold with a hysteresis, it stops charging the BAT pin and restarts charging the SYS pin to ensure that it does not enter cold startup. Figure 41 shows the fast cold start-up sequence.

The cold start-up circuit is required when the VIN pin is more than the minimum input voltage for the cold start ( $V_{IN\_COLD}$ ), and the energy storage voltage at the SYS pin is less than the end of the cold start operation threshold ( $V_{SYS\_TH}$ ). To complete the cold startup, the energy harvester must supply sufficient power (see the Energy Harvester Selection section). The cold startup, with much lower efficiency compared to the main boost regulator, achieves a short start-up time, creating a low shutdown current from the system load enabled by the PGOOD signal. To bypass the cold startup, place a primary battery at the BACK\_UP pin (see the Backup Storage Path section).

Figure 41. Fast Cold Start-Up Sequence

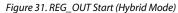

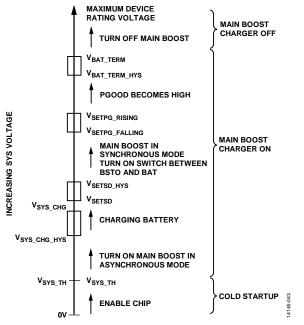

#### MAIN BOOST REGULATOR ( $V_{BAT_{TERM}} > V_{SYS} > V_{SYS_{TH}}$ )

The switching mode synchronous boost regulator, with an external inductor connected between the VIN and the SW pins, operates in pulse frequency modulation (PFM) mode, transferring energy stored in the input capacitor to the energy storage connected to the BAT pin. The MPPT control loop regulates the VIN voltage at the level sampled at the MPPT pin and stored at the capacitor through the CBP and the AGND pins. To maintain the high efficiency of the regulator across a wide input power range, the current sense circuitry employs an internal dither peak current limit to control the inductor current.

The main boost regulator operation reaches an asynchronous mode via the energy storage controller if the BAT pin voltage is less than the battery terminal charging threshold programmed at the SETSD pin, or stops switching if the BAT pin voltage is more than the battery overcharging threshold programmed at the TERM pin. The boost regulator disables when the voltage on the CBP pin decreases to the threshold set by the resistor at the MINOP pin. In addition, the boost is periodically stopped by an open voltage sampling circuit and can also be temporary disabled by driving the DIS\_SW pin high.

#### VIN OPEN CIRCUIT AND MPPT

By floating the MINOP pin, the MPPT no sensing mode can operate on a fixed MPPT voltage. The MPPT pin, with a 2.0  $\mu$ A (typical) bias current through a resistor, sets the MPPT voltage, which is the boost input regulation reference.

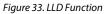

When the MINOP pin voltage is set lower than V<sub>MINOP\_DSM</sub> through a resistor to AGND, the ADP5091/ADP5092 operate in MPPT dynamic sensing mode. The boost input regulation reference is the open circuit voltage at the VIN pin scaled to a ratio programmed by the resistor divider at the MPPT pin. To keep the VIN voltage operating at the maximum power points available from the energy harvester at the input of the ADP5091/ADP5092, periodically sample the MPPT voltage and store it in the capacitor connected to the CBP pin. The reference voltage refreshes every 16 sec (default value) by periodically disabling the boost regulator for 256 ms (default value) and by sampling the ratio of the open circuit voltage when the BAT voltage level exceeds the SETSD rising threshold. The factory bit can program the sampling cycle. Set the reference voltage by

$$V_{MPPT} = V_{IN} \left( Open \ Circuit \right) \left( \frac{R_{OC1}}{R_{OC1} + R_{OC2}} \right)$$

(1)

where:

$V_{\it IN}$  (Open Circuit) is the input open circuit voltage (V\_{\rm IN\\_OCV}) of the input voltage.

See Figure 2 for Roc1 and Roc2.

### Data Sheet

The typical MPPT ratio depends on the type of harvester. For example, it is 0.7 to 0.85 for PV cells, and 0.5 for TEGs. The sampling OCV rate is adjustable depending on the previously sampled OCV level. To disable the MPPT function, leave the MPPT pin floating and set the CBP pin to an external voltage reference lower than the VIN voltage.

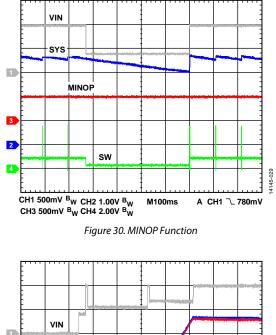

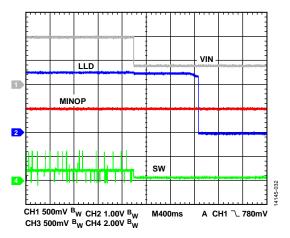

#### MINIMUM OPERATION THRESHOLD FUNCTION

By setting the MINOP pin voltage lower than the MINOP operation voltage range of the dynamic MPPT sensing mode  $(V_{\text{MINOP}\_DSM})$  through a resistor to AGND, the minimum operation threshold function can disable the main boost regulator to prevent discharging the storage element when the energy generated by the harvester is less than the system consumption. When the voltage of the CBP pin decreases to the threshold set by the resistor at the MINOP pin, the boost regulator stops switching. The typical MINOP bias current is 2.00  $\mu$ A. The minimum operation threshold function disables the MPPT function to achieve the sleeping quiescent current of 390 nA (typical). Disable this function by connecting the MINOP pin to the AGND pin.

The low light density (LLD) indicator (ADP5091 only) is the MINOP comparator output that signals the microprocessor to calculate the cycle with insufficient input energy in a certain period.

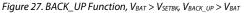

#### **DISABLING BOOST**

For noise or electromagnetic interference (EMI) sensitive applications, pull the DIS\_SW pin high to stop the boost switcher temporarily to prevent interference with RF circuits. Pull the DIS\_SW pin low to resume the boost switching. The transition delay is 1  $\mu$ s (typical).

#### **REGULATED OUTPUT WORKING MODE**

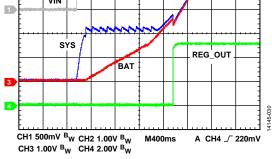

The 150 mA regulated output of the ADP5091/ADP5092 not only operates in the hysteresis boost mode or the LDO mode but also operates in the hybrid mode in which the regulator can smoothly transition between these two modes automatically. After the BAT voltage exceeds the SETSD threshold or the SYS voltage is greater than SETPG threshold, the regulator can be enabled.

In hysteresis boost mode, the boost regulator in the ADP5091/ ADP5092 charges the output voltage slightly higher than its preset output voltage. When the output voltage increases until the output sense signal exceeds the hysteresis comparator upper threshold (the sleep threshold), the regulator enters sleep mode. In sleep mode, to allow a low quiescent current as well as high efficiency performance, the low-side and high-side switches and a majority of the circuitry are disabled.

During sleep mode, the output capacitor supplies the energy into the load, the output voltage decreases until it falls below the hysteresis comparator lower threshold (the wake threshold), and the boost regulator wakes up and generates the pulse-width modulation (PWM) pulses to charge the output again. The hysteresis mode allows the regulator to act as the keep alive power supply. In LDO mode, the output generates power from the SYS pin with at least a small 4.7  $\mu$ F ceramic output capacitor. Using new innovative design techniques, the LDO provides ultralow quiescent current and superior transient performance for digital and RF applications, and supports noise sensitive applications.

In hybrid mode, the VIN and SYS pins both extract energy to the REG\_OUT pin. When the load power is lower than the input power, the regulator exits LDO mode and obtains the energy only from the input side.

#### REG\_D0 AND REG\_D1

The REG\_D0 and REG\_D1 pins allow flexible configuration of the working mode of the regulated output. Table 6 details the working mode configuration set by these two pins.

#### Table 6. Regulated Output Working Mode Configuration

| REG_D0         | REG_D1         |

|----------------|----------------|

| Low            | Not applicable |

| High           | Not applicable |

| Not applicable | Low            |

| Not applicable | High           |

|                | Low            |

#### **REGULATED OUTPUT CONFIGURATION**

The 150 mA regulated output of the ADP5091/ADP5092 is available in eight fixed output voltage options ranging from 1.5 V to 3.6 V by connecting one resistor through the VID pin to the AGND pin. Table 7 shows the output voltage options set by the VID pin.

#### Table 7. Output Voltage Options Set by the VID Pin

| 1.0 | 1                          |                                    |

|-----|----------------------------|------------------------------------|

|     | VID Configuration          | Output Voltage Set by the VID Pin  |

|     | Short to Ground            | Programmed with external resistors |

|     | Floating                   | $V_{OUT} = 2.5 V$                  |

|     | $R_{VID} = 7 \ k\Omega$    | V <sub>OUT</sub> = 1.5 V           |

|     | $R_{VID} = 14 \ k\Omega$   | V <sub>OUT</sub> = 1.8 V           |

|     | $R_{VID} = 27.7 \ k\Omega$ | V <sub>OUT</sub> = 3.6 V           |

|     | $R_{VID} = 55.6 \ k\Omega$ | V <sub>OUT</sub> = 3.3 V           |

|     | $R_{VID} = 111 \ k\Omega$  | $V_{OUT} = 2.0 V$                  |

|     | $R_{VID} = 221 \ k\Omega$  | $V_{OUT} = 3.0 V$                  |

|     | $R_{VID} = 442 \ k\Omega$  | $V_{OUT} = 2.8 V$                  |

The external resistor divider or the VID pin can program the regulated output. The ratio of the two external resistors sets the adjustable output voltage range of 1.5 V to 3.6 V, as shown in Figure 47. The device acts as a servo to the output to maintain the voltage at the REG\_FB pin at 1.0 V referenced to ground. The current in R1 is then equal to 1.0 V/R2, and the current in R1 is the current in R2 plus the REG\_FB pin bias current. Calculate the output voltage by

$$V_{OUT} = 1.02 \text{ V} \times (1 + R1/R2)$$

(2)

where:  $V_{OUT} = V_{REG_OUT}$ . See Figure 47 for *R1* and *R2*.

To minimize quiescent current, it is recommended to use large resistance values for R1 and R2.

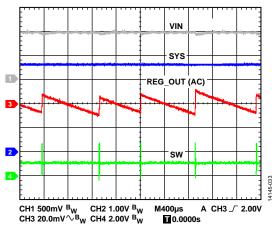

#### REG\_GOOD (ADP5092 ONLY)

A logic high on the REG\_GOOD pin indicates that the REG\_OUT voltage is above 92.5% (typical) of its nominal output for a delay time greater than approximately 2 ms. The logic high level on REG\_GOOD is equal to the REG\_OUT voltage, and the logic low level is ground. When the REG\_OUT voltage falls below a 2% hysteresis (typical) of the rising threshold, the REG\_GOOD pin goes low. The logic high level has about 11.6 k $\Omega$  internally in series to limit the available current.

#### **ENERGY STORAGE CHARGE MANAGEMENT**

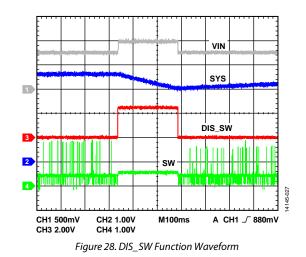

Energy storage is connected to the BAT pin. The storage can be a rechargeable battery, super capacitor, or 100  $\mu$ F or larger capacitor. The energy storage controller manages the charging and discharging operations, monitors the SYS pin voltage, and asserts the PGOOD signal high when it is above the threshold programmed at the SETPG pin.

When the BAT pin voltage exceeds the battery terminal charging threshold programmed at the TERM pin, the boost operation terminates to prevent battery overcharging. The battery terminal charging threshold is programmable from 2.2 V to 5.2 V. When the BAT voltage drops below the battery stop charging threshold level programmed at the SETSD pin, the switches between the BAT pin and the SYS pin are turned off to prevent a deep, destructive battery discharge, and the boost operates in asynchronous mode. Although there is no current limit at the SYS and the BAT pins, it is recommended to limit the system load current to lower than 1000 mA. The large system load current generates a droop between the SYS pin and the rechargeable battery at the BAT pin, with consideration given to the resistance of the SYS switch, the BAT switch, and the rechargeable battery internal resistance.

When no input source is attached, discharge the SYS pin to ground before attaching a storage element to the BAT pin. After hot plugging a charged storage element, release the SYS pin because a SYS voltage that is less than the end of the cold start operation threshold ( $V_{SYS_TH}$ ) results in the BAT switch remaining off to protect the storage element until the SYS voltage reaches  $V_{SYS_TH}$ . The BAT switches remaining off can also be described as store mode, a state with the lowest leakage (3.5 nA typical) that allows a long store period without discharging the storage element on BAT.

#### **BACKUP STORAGE PATH**

The ADP5091/ADP5092 provide an optional backup storage energy path, an integrated backup controller, and two back to back power switches between the BACK\_UP pin and the SYS pin. When the system operates at a condition where the harvested and stored energy is periodically insufficient, attach a backup energy storage element to the BACK\_UP pin.

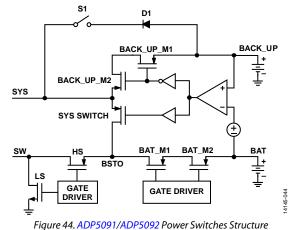

The backup controller enables when the SYS voltage exceeds the end of the cold start operation threshold (V<sub>SYS\_TH</sub>). Before the BAT voltage lowers the SETBK threshold, the backup switches turn off. While the BAT voltage is less than the SETBK threshold, the switches status depends on the voltage level of the BACK\_UP pin and the BAT pin. The internal BACK\_UP\_Mx and BACK\_UP control circuit automatically determine the BACK\_UP switches (BACK\_UP\_M1 and BACK\_UP\_M2) on/off status and selects the high voltage terminal as the power source of SYS. The 190 mV (typical) comparator input offset of the BAT pin prevents the input source and the BAT pin from charging the BACK\_UP pin (see Figure 44).

In addition, the backup storage element can bypass the cold startup with inrush current protection circuitry. Nevertheless, the current capability is only 250  $\mu$ A (typical) when plugging in the backup battery before completing the cold start. It is recommended to restrict the system load current from the SYS pin to ensure that the power path can enter normal operation status. Table 9 explains the power path working state. For long-term store mode, disconnect the backup storage element and then discharge SYS to ground.

#### **BACKUP AND BAT SELECTION THRESHOLD**

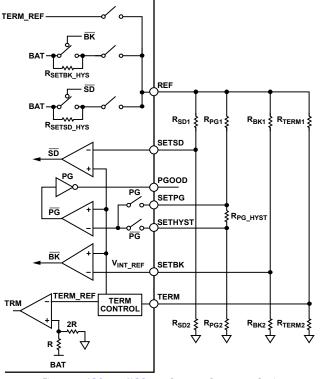

To determine when to enable the BACK\_UP function, the switch threshold on the BAT pin must be set by using external resistors at SETBK pin. When the BAT voltage is lower than the SETBK threshold, the internal BACK\_UP\_Mx control circuit automatically selects the high voltage terminal as the SYS power source. Figure 42 shows the  $V_{\text{SETBK}}$  falling threshold voltage given by Equation 3.

$$V_{SETBK} = V_{INT_{-REF}} \left( 1 + \frac{R_{BKI}}{R_{BK2}} \right)$$

(3)

The ADP5091/ADP5092 have an internal resistor,  $R_{\text{SETBK}-\text{HYS}} = 115 \text{ k}\Omega$  (typical), to program the hysteresis, given by Equation 4.

$$V_{SETBK_{HYS}} = V_{SETBK} \times \frac{R_{SETBK_{HYS}}}{R_{F}}$$

(4)

where  $R_E$  is the equivalent resistor of the four external configuration resistor dividers.

Considering the quiescent current consumption, the sum of the resistors that comprise the resistor divider ( $R_{\text{SETBK}_HYS}$ ,  $R_{\text{BK1}}$ , and  $R_{\text{BK2}}$ ) must be greater than 6 M $\Omega$ , that is,

$$R_{SETBK_HYS} + R_{BK1} + R_{BK2} > 6 M\Omega$$

<sup>(5)</sup>

The equivalent resistor of the four external configuration resistor dividers  $(R_E)$  is equivalent to the paralleling value of the three resistor dividers.

Figure 42. ADP5091/ADP5092 Program Paramater Setting

#### **BATTERY OVERCHARGING PROTECTION**

To prevent rechargeable batteries from being overcharged and damaged, the battery terminal charging threshold ( $V_{BAT\_TERM}$ ) must be set by using external resistors. Figure 42 shows the  $V_{BAT\_TERM}$  rising threshold voltage given by Equation 6.

$$V_{BAT\_TERM} = \frac{3}{2} \times V_{INT\_REF} \times \left(1 + \frac{R_{TERM1}}{R_{TERM2}}\right)$$

(6)

Considering the quiescent current consumption, the sum of the resistors must be more than 6 M $\Omega$ , that is,

$$R_{TERM1} + R_{TERM2} \ge 6 \text{ M}\Omega \tag{7}$$

The battery terminal charging threshold is given by  $V_{BAT\_TERM\_HYS}$ , which is internally set to the battery terminal charging threshold minus an internal hysteresis voltage denoted by  $V_{BAT\_TERM\_HYS}$ . When the voltage at the battery exceeds the  $V_{BAT\_TERM\_HYS}$ . When the voltage at the battery exceeds the  $V_{BAT\_TERM\_HYS}$  the main boost regulator disables. The main boost starts again when the battery voltage falls below the  $V_{BAT\_TERM\_HYS}$  level. When input energy is excessive, the VBAT pin voltage ripples between the  $V_{BAT\_TERM\_AHYS}$  levels.

#### **BATTERY DISCHARGING PROTECTION**

To prevent rechargeable batteries from being deeply discharged and damaged, the battery stop discharging threshold ( $V_{SETSD}$ ) must be set by using external resistors. Figure 42 shows the  $V_{SETSD}$  falling threshold voltage given by Equation 8.

$$V_{SETSD} = V_{INT_{-}REF} \left( 1 + \frac{R_{SDI}}{R_{SD2}} \right)$$

(8)

The ADP5091/ADP5092 have an internal resistor,  $R_{SETSD_HYS} = 115 \text{ k}\Omega$  (typical), to program the hysteresis, given by Equation 9.

$$V_{SETSD_{HYS}} = V_{SETSD} \times \frac{R_{SETSD_{HYS}}}{R_{F}}$$

<sup>(9)</sup>

Considering the quiescent current consumption, the sum of the resistors that comprise the resistor divider ( $R_{SETSD_HYS}$ ,  $R_{SD1}$ , and  $R_{SD2}$ ) must be more than 6 M $\Omega$ , that is,

$$R_{SETSD_HYS} + R_{SD1} + R_{SD2} \ge 6 \text{ M}\Omega \tag{10}$$

The equivalent resistor of the three external configuration resistor dividers  $(R_E)$  is equivalent to the paralleling value of the three resistor dividers.

4145-04

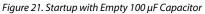

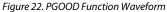

#### **POWER GOOD (PGOOD)**

The ADP5091/ADP5092 allow users to set a programmable PGOOD voltage threshold, which indicates that the SYS voltage is at an acceptable level. It must be set by using external resistors. Figure 42 shows the  $V_{SETPG}$  falling threshold voltage given by Equation 11.

$$V_{SETPG\_FALLING} = V_{INT\_REF} \left( 1 + \frac{R_{PGI}}{R_{PG2} + R_{PG\_HYST}} \right)$$

(11)

The SETHYST pin can program the hysteresis with an external resistor ( $R_{PG_HYST}$ ) given by Equation 12.

$$V_{SETPG\_RISING} = V_{INT\_REF} \left( 1 + \frac{R_{PGI} + R_{PG\_HYST}}{R_{PG2}} \right)$$

(12)

Considering the quiescent current consumption, the sum of the resistors that comprise the power-good resistor divider  $(R_{PG_{-HYST}}, R_{PG1}, and R_{PG2})$  must be more than 6 M $\Omega$ , that is,

$R_{PG_HYST} + R_{PG1} + R_{PG2} \ge 6 \text{ M}\Omega$

The logic high level on PGOOD is equal to the SYS voltage and the logic low level is ground. The logic high level has approximately 11.6 k $\Omega$  (typical) internally in series to limit the available current. The V<sub>SETPG\_FALLING</sub> threshold must be greater than the V<sub>SETSD</sub> threshold.

For the best operation of the system, use PGOOD to enable the system load or to turn on an ultralow power load switch or to drive an external positive channel field effect transistor (PFET) between SYS and the system load via an inverter to determine when the system load can be connected or removed (see Figure 48).

Table 8 shows programming threshold resistor examples corresponding to various voltages with a 10 M $\Omega$  resistor divider. Figure 43 shows various threshold voltages states.

**POWER PATH WORKING FLOW**

Figure 44 shows the power switches structure when the backup primary battery is used. During the cold start, when a primary battery connects to the BACK\_UP pin, the S1 switch turns on. The primary battery with the Diode D1 forward voltage drop can be the SYS power source.

After completing the cold start, if the BAT voltage is above the SETBK falling threshold, the BACK\_UP switches remain off. When the BAT voltage is lower than the SETBK falling threshold, the backup control automatically selects the high voltage terminal as the SYS power source as long as the SYS voltage is more than  $V_{SYS\_CHG}$ . The backup control also prevents the BACK\_UP primary battery from charging the BAT pin. Meanwhile, the BAT offset of the comparator prevents the input source from charging the BACK\_UP primary battery. Table 9 shows the power path of the working state.

#### CURRENT-LIMIT AND SHORT-CIRCUIT PROTECTION

The boost regulator and regulated output in hysteresis boost mode in the ADP5091/ADP5092 includes current-limit protection circuitry to limit the amount of positive current flowing through the low-side boost switch. The boost regulator current-limit protection circuitry is a cycle-by-cycle, three-level peak currentlimit protection with a third level of 200 mA (typical), and the regulated output current-limit protection circuitry is 100 mA (typical). In LDO mode, the current-limit protection is designed to limit the current when the output load reaches 260 mA (typical). When the output load exceeds 260 mA, the output voltage reduces to maintain a constant current limit.

Although there is no current limit at the SYS and the BAT pins, it is recommended to limit the system load current to lower than 1000 mA. The total resistance of the SYS switch and the BAT switch (1.03  $\Omega$ , typical) generates a voltage drop when the system load sinks a large current from BAT. It is also necessary to consider the internal resistance of the storage elements connected to the BAT pin.

Figure 43. ADP5091/ADP5092 Various Threshold Voltages States (See Equation 8 and Equation 9)

#### THERMAL SHUTDOWN

In the event that the ADP5091/ADP5092 junction temperature rises above 142°C, the thermal shutdown circuit turns off the switch between the BAT pin and the SYS pin to prevent the damage of the energy storage at a high ambient temperature. In addition, the boost operation terminates. A 15°C hysteresis is

Table 8. Programming Threshold Resistors (See Figure 42)

included, allowing the ADP5091/ADP5092 to return to operation when the on-chip temperature drops to less than 127°C. When exiting thermal shutdown, the boost and the energy storage controller resume their functions.

| Voltage Threshold (V) | <b>R</b> <sub>BK1</sub> , <b>R</b> <sub>SD1</sub> , and <b>R</b> <sub>PG1</sub> (MΩ) | <b>R</b> <sub>BK2</sub> , <b>R</b> <sub>SD2</sub> , and <b>R</b> <sub>PG2</sub> (MΩ) | <b>R</b> <sub>TERM1</sub> ( <b>M</b> Ω) | <b>R</b> <sub>TERM2</sub> ( <b>M</b> Ω) |

|-----------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|

| 2                     | 5                                                                                    | 5                                                                                    | Not applicable                          | Not applicable                          |

| 2.1                   | 5.23                                                                                 | 4.75                                                                                 | Not applicable                          | Not applicable                          |

| 2.2                   | 5.49                                                                                 | 4.53                                                                                 | 3.2                                     | 6.81                                    |

| 2.3                   | 5.62                                                                                 | 4.32                                                                                 | 3.48                                    | 6.49                                    |

| 2.4                   | 5.9                                                                                  | 4.12                                                                                 | 3.74                                    | 6.2                                     |

| 2.5                   | 6.04                                                                                 | 4                                                                                    | 4                                       | 6.04                                    |

| 2.6                   | 6.19                                                                                 | 3.83                                                                                 | 4.22                                    | 5.76                                    |

| 2.7                   | 6.34                                                                                 | 3.74                                                                                 | 4.42                                    | 5.6                                     |

| 2.8                   | 6.49                                                                                 | 3.57                                                                                 | 4.64                                    | 5.36                                    |

| 2.9                   | 6.6                                                                                  | 3.48                                                                                 | 4.87                                    | 5.23                                    |

| 3                     | 6.65                                                                                 | 3.32                                                                                 | 5                                       | 5                                       |

| 3.1                   | 6.8                                                                                  | 3.24                                                                                 | 5.11                                    | 4.87                                    |

| 3.2                   | 6.81                                                                                 | 3.09                                                                                 | 5.36                                    | 4.7                                     |

| 3.3                   | 6.98                                                                                 | 3.01                                                                                 | 5.49                                    | 4.53                                    |

| 3.4                   | 6.98                                                                                 | 2.94                                                                                 | 5.6                                     | 4.42                                    |

| 3.5                   | 7.15                                                                                 | 2.87                                                                                 | 5.76                                    | 4.3                                     |

| 3.6                   | 7.15                                                                                 | 2.8                                                                                  | 5.9                                     | 4.12                                    |

| 3.7                   | 7.32                                                                                 | 2.7                                                                                  | 5.9                                     | 4.02                                    |

| 3.8                   | 7.32                                                                                 | 2.61                                                                                 | 6.04                                    | 3.92                                    |

| 3.9                   | 7.5                                                                                  | 2.55                                                                                 | 6.19                                    | 3.83                                    |

| 4                     | 7.5                                                                                  | 2.5                                                                                  | 6.2                                     | 3.74                                    |