Sample &

Buy

#### LM3673

SNVS434M-JULY 2006-REVISED NOVEMBER 2016

# LM3673 2-MHz, 350-mA Step-Down DC-DC Converter

Technical

Documents

## 1 Features

- 16-µA Typical Quiescent Current

- 350-mA Maximum Load Capability

- 2-MHz PWM Fixed Switching Frequency (Typical)

- Automatic PFM/PWM Mode Switching

- Available in Fixed and Adjustable Output Voltages

- Internal Synchronous Rectification for High Efficiency

- Internal Soft Start

- 0.01-µA Typical Shutdown Current

- Operates From a Single Li-Ion Cell Battery

- Current Overload and Thermal Shutdown

Protection

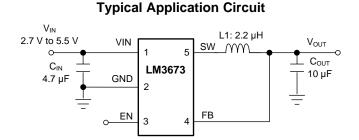

- Only Three Tiny Surface-Mount External Components Required (One Inductor, Two Ceramic Capacitors)

## 2 Applications

- Mobile Phones

- PDAs

- MP3 Players

- W-LAN

- Portable Instruments

- Digital Still Cameras

- Portable Hard Disk Drives

## 3 Description

Tools &

Software

The LM3673 step-down DC-DC converter is optimized for powering low voltage circuits from a single Li-Ion cell battery and input voltage rails from 2.7 V to 5.5 V. It provides up to 350-mA load current over the entire input voltage range. There are several different fixed voltage output options available, as well as an adjustable output voltage version ranging from 1.1 V to 3.3 V.

Support &

Community

**.**...

The device offers superior features and performance for mobile phones and similar portable systems. The LM3673 uses intelligent automatic switching between pulse width modulation (PWM) and pulse frequency modulation (PFM) for better efficiency. During PWM mode, the device operates at a fixed-frequency of

2 MHz (typical). Hysteretic PFM mode extends the battery life by reducing the quiescent current to 16  $\mu$ A (typical) during light load and standby operation. Internal synchronous rectification provides high efficiency during PWM mode operation. In shutdown mode, the device turns off and reduces battery consumption to 0.01  $\mu$ A (typical).

The LM3673 is available in a tiny 5-pin DSBGA package. A high switching frequency of 2 MHz (typical) allows the use of three tiny surface-mount components: an inductor and two ceramic capacitors.

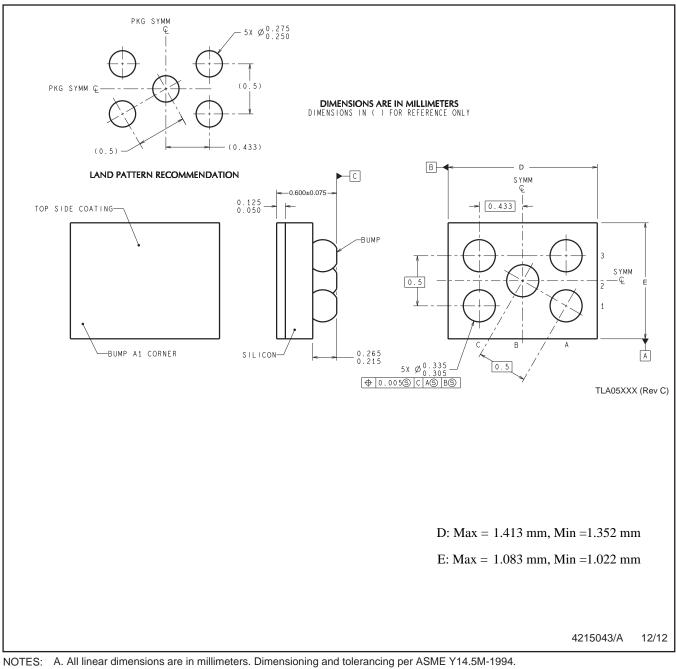

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (MAX)     |  |  |

|-------------|-----------|---------------------|--|--|

| LM3673      | DSBGA (5) | 1.413 mm × 1.083 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

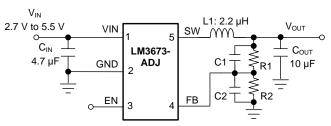

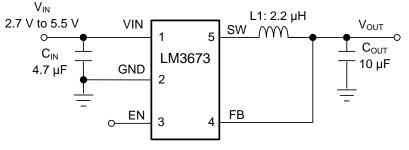

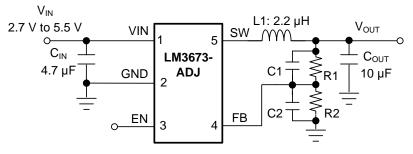

## **Typical Application Circuit for ADJ Version**

Texas Instruments

www.ti.com

## **Table of Contents**

| 1 | Fea  | tures 1                         | 9  |

|---|------|---------------------------------|----|

| 2 | Арр  | lications 1                     |    |

| 3 | Des  | cription 1                      |    |

| 4 | Rev  | ision History 2                 | 10 |

| 5 | Volt | age Options 3                   | 11 |

| 6 |      | Configuration and Functions     |    |

| 7 | Spe  | cifications 4                   |    |

|   | 7.1  | Absolute Maximum Ratings 4      |    |

|   | 7.2  | ESD Ratings 4                   | 12 |

|   | 7.3  | Recommended Operating Ratings 4 |    |

|   | 7.4  | Thermal Information 4           |    |

|   | 7.5  | Electrical Characteristics 5    |    |

|   | 7.6  | Typical Characteristics 6       |    |

| 8 | Deta | ailed Description               |    |

|   | 8.1  | Overview                        |    |

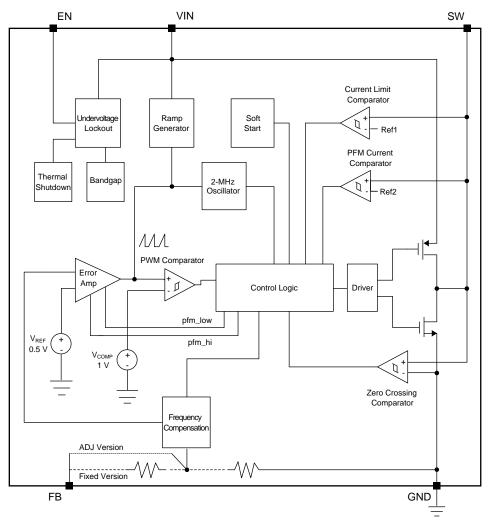

|   | 8.2  | Functional Block Diagram 9      |    |

|   | 8.3  | Feature Description 10          | 13 |

|   | 8.4  | Device Functional Modes 11      |    |

|   |      |                                 |    |

| )  | Арр  | lication and Implementation                     | 13 |

|----|------|-------------------------------------------------|----|

|    | 9.1  | Application Information                         | 13 |

|    | 9.2  | Typical Applications                            | 13 |

| 0  | Pow  | ver Supply Recommendations                      | 19 |

| 11 | Lay  | out                                             | 20 |

|    | 11.1 | Layout Guidelines                               | 20 |

|    | 11.2 | Layout Example                                  | 21 |

|    | 11.3 | DSBGA Package Assembly and Use                  | 21 |

| 12 | Dev  | ice and Documentation Support                   | 22 |

|    | 12.1 | Device Support                                  | 22 |

|    | 12.2 | Documentation Support                           | 22 |

|    | 12.3 | Receiving Notification of Documentation Updates | 22 |

|    | 12.4 | Community Resources                             | 22 |

|    | 12.5 | Trademarks                                      | 22 |

|    | 12.6 | Electrostatic Discharge Caution                 | 22 |

|    | 12.7 | Glossary                                        | 22 |

| 13 |      | hanical, Packaging, and Orderable               |    |

|    | Info | rmation                                         | 22 |

|    |      |                                                 |    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | Changes from Revision L (October 2015) to Revision M                                                                                                                                                                                                                                                                |      |  |  |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| • | Changed Figure 16 so that "Nfet on drains conductor" says "Nfet on drains inductor"                                                                                                                                                                                                                                 | 12   |  |  |  |

| C | hanges from Revision K (April 2013) to Revision L                                                                                                                                                                                                                                                                   | Page |  |  |  |

| • | Added Device Information and Pin Configuration and Functions sections, ESD Ratings table, Feature Description,<br>Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Device and<br>Documentation Support, and Mechanical, Packaging, and Orderable Information sections | 1    |  |  |  |

| • | Deleted Dissipation Ratings table - obsolete info                                                                                                                                                                                                                                                                   | 4    |  |  |  |

| C | hanges from Revision J (April 2013) to Revision K                                                                                                                                                                                                                                                                   | Page |  |  |  |

| • | Changed layout of National Data Sheet to TI format                                                                                                                                                                                                                                                                  | 20   |  |  |  |

## 5 Voltage Options

| ORDERABLE NUMBER <sup>(1)(2)</sup> | VOLTAGE OPTION |  |  |

|------------------------------------|----------------|--|--|

| LM3673TL-ADJ/NOPB                  | ADJ            |  |  |

| LM3673TLX-ADJ/NOPB                 | ADJ            |  |  |

| LM3673TL-1.2/NOPB                  | 1.2            |  |  |

| LM3673TLX-1.2/NOPB                 | 1.2            |  |  |

| LM3673TL-1.5/NOPB                  | 1.5            |  |  |

| LM3673TLX-1.5/NOPB                 | 1.5            |  |  |

| LM3673TL-1.8/NOPB                  | 1.8            |  |  |

| LM3673TLX-1.8/NOPB                 |                |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

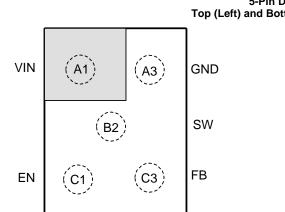

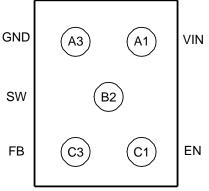

## 6 Pin Configuration and Functions

YZR Package 5-Pin DSBGA Top (Left) and Bottom (Right) Views

## **Pin Functions**

| PIN    |      | 1/0    | DECODIDION                                                                                                                                                                                                                                             |  |

|--------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME | I/O    | DESCRIPTION                                                                                                                                                                                                                                            |  |

| A1     | VIN  | Power  | Power supply input. Connect to the input filter capacitor (Figure 17).                                                                                                                                                                                 |  |

| A3     | GND  | Ground | Ground pin                                                                                                                                                                                                                                             |  |

| B2     | SW   | Analog | witching node connection to the internal PFET switch and NFET synchronous rectifier.                                                                                                                                                                   |  |

| C1     | EN   | Input  | nable pin. The device is in shutdown mode when voltage to this pin is < 0.4 V and enabled hen > 1 V. Do not leave this pin floating.                                                                                                                   |  |

| СЗ     | FB   | Analog | Feedback analog input. Connect directly to the output filter capacitor for fixed voltage versions. For adjustable version external resistor dividers are required (Figure 18). The internal resistor dividers are disabled for the adjustable version. |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                               | MIN     | MAX                    | UNIT |

|-----------------------------------------------|---------|------------------------|------|

| VIN pin: voltage to GND                       | -0.2    | 6                      | V    |

| FB, SW, EN pins                               | GND-0.2 | (V <sub>IN</sub> + 0.2 | V    |

| Continuous power dissipation <sup>(3)</sup>   |         | Internally Limited     |      |

| Junction temperature, T <sub>J-MAX</sub>      |         | 125                    | °C   |

| Maximum lead temperature (soldering, 10 sec.) |         | 260                    | °C   |

| Storage temperature, T <sub>stg</sub>         | -65     | 150                    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

(3) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J$ = 150°C (typical) and disengages at  $T_J$ = 130°C (typical).

## 7.2 ESD Ratings

|                    |                                                                   |               | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|---------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000         | V     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Machine model | ±200  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                                    | MIN | NOM MAX | UNIT |

|----------------------------------------------------|-----|---------|------|

| Input voltage <sup>(3)</sup>                       | 2.7 | 5.5     | V    |

| Recommended load current                           | 0   | 350     | mA   |

| Junction temperature, T <sub>J</sub>               | -30 | 125     | °C   |

| Ambient temperature, T <sub>A</sub> <sup>(4)</sup> | -30 | 85      | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

(3) The input voltage range recommended for ideal applications performance for the specified output voltages are as follows: V<sub>IN</sub> = 2.7 V to 4.5 V for 1.1 V ≤ V<sub>OUT</sub> < 1.5 V; V<sub>IN</sub> = 2.7 V to 5.5 V for 1.5 V ≤ V<sub>OUT</sub> < 1.8 V; V<sub>IN</sub> = (V<sub>OUT</sub> + V<sub>DROPOUT</sub>) to 5.5 V for 1.8 V ≤ V<sub>OUT</sub> ≤ 3.3 V where V<sub>DROPOUT</sub> = I<sub>LOAD</sub> × (R<sub>DSON, PFET</sub> + R<sub>INDUCTOR</sub>)

(4) In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to

(4) In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX</sub>), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction to ambient thermal resistance of the package (R<sub>θJA</sub>) in the application, as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX</sub> - (R<sub>θJA</sub> × P<sub>D-MAX</sub>).

## 7.4 Thermal Information

|                       |                                                       | LM3673      |      |  |

|-----------------------|-------------------------------------------------------|-------------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                         | YZR (DSBGA) | UNIT |  |

|                       |                                                       | 5 PINS      |      |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance <sup>(2)</sup> | 181.0       | °C/W |  |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance             | 0.9         | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                  | 110.3       | °C/W |  |

| TLΨ                   | Junction-to-top characterization parameter            | 7.4         | °C/W |  |

| ΨЈВ                   | Junction-to-board characterization parameter          | 110.3       | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics.

(2) Junction-to-ambient thermal resistance is highly application and board layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

## 7.5 Electrical Characteristics

Typical limits apply for  $T_{J} = 25^{\circ}$ C. Unless otherwise specified, minimum and maximum limits apply over the full operating ambient temperature range ( $-30^{\circ}C \le T_A \le +85^{\circ}C$ ). Unless otherwise noted, specifications apply to the LM3673TL with V<sub>IN</sub> =  $EN = 3.6 V.^{(1)(2)(3)}$

|                       | PARAMETER                      | TEST CONDITIONS                                                                                       | MIN   | TYP    | MAX  | UNIT |

|-----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------|-------|--------|------|------|

| V <sub>IN</sub>       | Input voltage                  | See <sup>(4)</sup>                                                                                    | 2.7   |        | 5.5  | V    |

|                       | Feedback voltage (fixed / ADJ) | PWM mode <sup>(5)</sup>                                                                               | -2.5% |        | 2.5% |      |

| V <sub>FB</sub>       | Line regulation                | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$<br>$\text{I}_{\text{OUT}} = 20 \text{ mA}$ |       | 0.025  |      | %/V  |

|                       | Load regulation                | 150 mA $\leq$ I <sub>OUT</sub> $\leq$ 350 mA V <sub>IN</sub> = 3.6 V                                  |       | 0.0015 |      | %/mA |

| V <sub>REF</sub>      | Internal reference voltage     |                                                                                                       |       | 0.5    |      | V    |

| I <sub>SHDN</sub>     | Shutdown supply current        | EN = 0V                                                                                               |       | 0.01   | 1    | μA   |

| l <sub>Q</sub>        | DC bias current into $V_{IN}$  | No load, device is not switching (FB forced higher than programmed output voltage)                    |       | 16     | 35   | μA   |

| R <sub>DSON (P)</sub> | Pin-pin resistance for PFET    | $V_{IN} = V_{GS} = 3.6 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                                 |       | 350    | 450  | mΩ   |

| R <sub>DSON (N)</sub> | Pin-pin resistance for NFET    | $V_{IN} = V_{GS} = 3.6 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                                 |       | 150    | 250  | mΩ   |

| I <sub>LIM</sub>      | Switch peak current limit      | Open loop <sup>(6)</sup>                                                                              | 590   | 750    | 855  | mA   |

| V <sub>IH</sub>       | Logic high input               |                                                                                                       | 1     |        |      | V    |

| V <sub>IL</sub>       | Logic low input                |                                                                                                       |       |        | 0.4  | V    |

| I <sub>EN</sub>       | Enable (EN) input current      |                                                                                                       |       | 0.01   | 1    | μA   |

| fosc                  | Internal oscillator frequency  | PWM mode <sup>(5)</sup>                                                                               | 1.6   | 2      | 2.6  | MHz  |

(1) All voltages are with respect to the potential at the GND pin.

Minimum and maximum limits are specified by design, test or statistical analysis. Typical numbers are not verified, but do represent the (2) most likely norm.

(3) The parameters in the electrical characteristic table are tested at V<sub>IN</sub>= 3.6 V unless otherwise specified. For performance over the input voltage range refer to datasheet curves.

(4) The input voltage range recommended for ideal applications performance for the specified output voltages are as follows: VIN = 2.7 V to 4.5 V for 1.1 V  $\leq$  V<sub>OUT</sub> < 1.5 V; V<sub>IN</sub> = 2.7 V to 5.5 V for 1.5 V  $\leq$  V<sub>OUT</sub> < 1.8 V; V<sub>IN</sub> = (V<sub>OUT</sub> + V<sub>DROPOUT</sub>) to 5.5 V for 1.8 V  $\leq$  V<sub>OUT</sub>  $\leq$  3.3 V, where  $V_{DROPOUT} = I_{LOAD} \times (R_{DSON, PFET} + R_{INDUCTOR})$ . Test condition: for  $V_{OUT}$  less than 2.5 V,  $V_{IN} = 3.6$  V; for  $V_{OUT}$  greater than or equal to 2.5 V,  $V_{IN} = V_{OUT} + 1$  V.

Refer to for closed-loop data and its variation with regards to supply voltage and temperature. Electrical Characteristics reflects open-(6)loop data (FB = 0 V and current drawn from SW pin ramped up until cycle-by-cycle current limit is activated). Closed-loop current limit is the peak inductor current measured in the application circuit by increasing output current until output voltage drops by 10%.

LM3673 SNVS434M – JULY 2006–REVISED NOVEMBER 2016

www.ti.com

STRUMENTS

EXAS

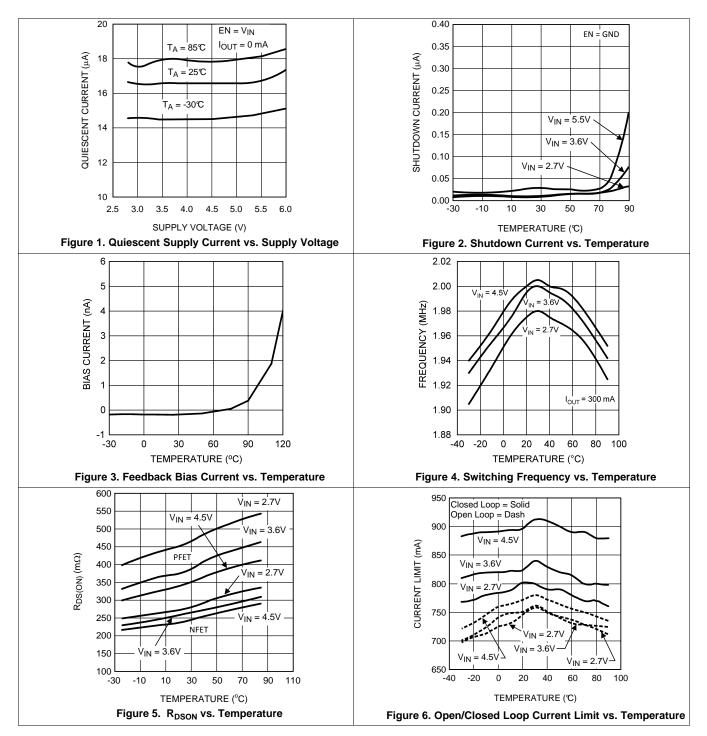

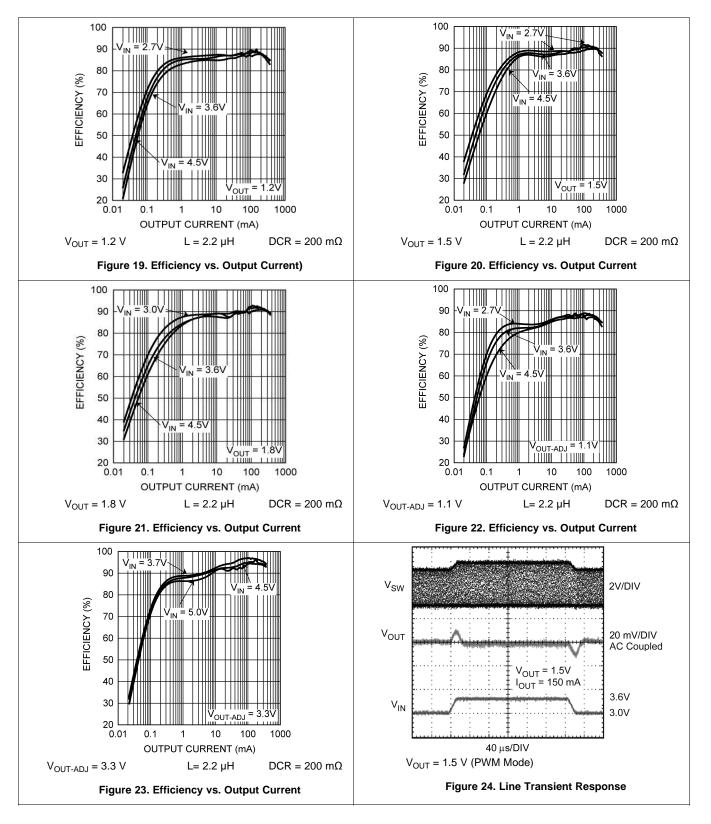

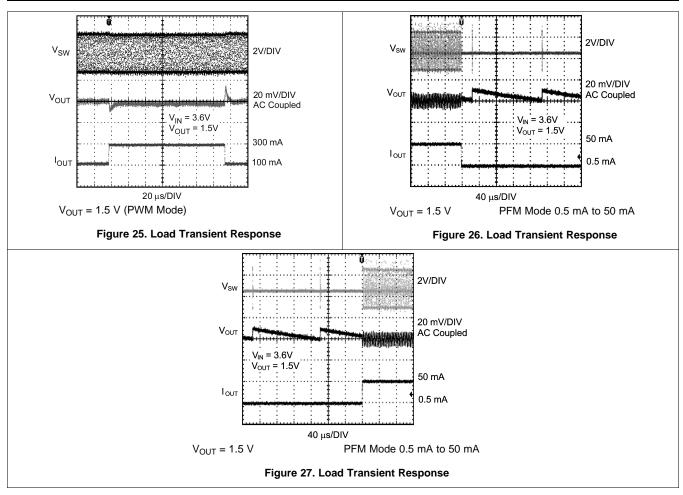

## 7.6 Typical Characteristics

LM3673TL typical application (Figure 17),  $V_{IN}$  = 3.6 V,  $V_{OUT}$ = 1.5 V,  $T_A$  = 25°C, unless otherwise noted.

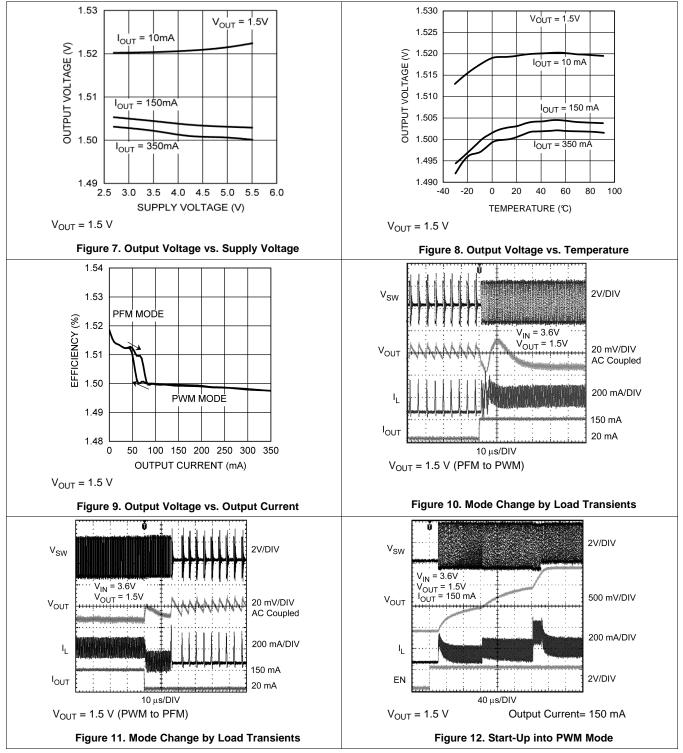

## **Typical Characteristics (continued)**

LM3673TL typical application (Figure 17), V<sub>IN</sub> = 3.6 V, V<sub>OUT</sub>= 1.5 V, T<sub>A</sub> = 25°C, unless otherwise noted.

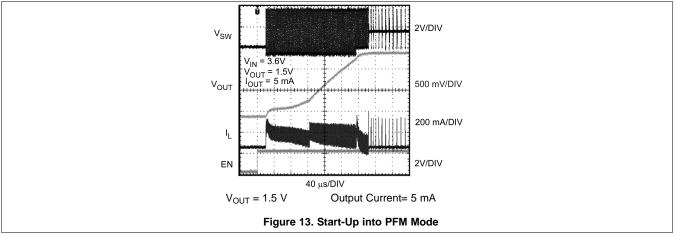

## **Typical Characteristics (continued)**

LM3673TL typical application (Figure 17),  $V_{IN}$  = 3.6 V,  $V_{OUT}$ = 1.5 V,  $T_A$  = 25°C, unless otherwise noted.

## 8 Detailed Description

## 8.1 Overview

The LM3673, a high-efficiency step-down DC-DC switching buck converter, delivers a constant voltage from a single Li-Ion battery and input voltage ranging from 2.7 V to 5.5 V to portable devices such as cell phones and PDAs. Using a voltage mode architecture with synchronous rectification, the LM3673 has the ability to deliver up to 350 mA depending on the input voltage, output voltage, ambient temperature and the inductor chosen.

There are three modes of operation depending on the current required: pulse width modulation (PWM), pulse frequency modulation (PFM), and shutdown. The device operates in PWM mode at load current of approximately 80 mA or higher. Lighter load current cause the device to automatically switch into PFM for reduced current consumption ( $I_Q = 16 \ \mu A$  typical) and a longer battery life. Shutdown mode turns off the device, offering the lowest current consumption ( $I_{SHUTDOWN} = 0.01 \ \mu A$  typical).

Additional features include soft-start, undervoltage protection, current overload protection, and thermal shutdown protection. As shown in Figure 17, only three external power components are required for implementation. The part uses an internal reference voltage of 0.5 V. It is recommended to keep the part in shutdown until the input voltage is 2.7 V or higher.

## 8.2 Functional Block Diagram

## 8.3 Feature Description

### 8.3.1 Circuit Operation

During the first portion of each switching cycle, the control block in the LM3673 turns on the internal PFET switch. This allows current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of  $(V_{IN} - V_{OUT}) / L$  by storing energy in a magnetic field.

During the second portion of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET synchronous rectifier on. The inductor draws current from ground through the NFET to the output filter capacitor and load, which ramps the inductor current down with a slope of  $-V_{OUT}/L$ .

The output filter stores charge when the inductor current is high, and releases it when inductor current is low, smoothing the voltage across the load.

The output voltage is regulated by modulating the PFET switch on time to control the average current sent to the load. The effect is identical to sending a duty-cycle modulated rectangular wave formed by the switch and synchronous rectifier at the SW pin to a low-pass filter formed by the inductor and output filter capacitor. The output voltage is equal to the average voltage at the SW pin.

#### 8.3.2 PWM Operation

During PWM operation the converter operates as a voltage-mode controller with input voltage feed forward. This allows the converter to achieve good load and line regulation. The DC gain of the power stage is proportional to the input voltage. To eliminate this dependence, feed forward inversely proportional to the input voltage is introduced.

While in PWM mode, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control power to the load. At the beginning of each clock cycle the PFET switch is turned on and the inductor current ramps up until the comparator trips and the control logic turns off the switch. The current limit comparator can also turn off the switch in case the current limit of the PFET is exceeded. Then the NFET switch is turned on and the inductor current ramps down. The next cycle is initiated by the clock turning off the NFET and turning on the PFET.

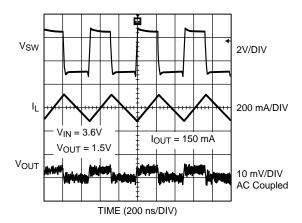

Figure 14. Typical PWM Operation

#### 8.3.3 Internal Synchronous Rectification

While in PWM mode, the LM3673 uses an internal NFET as a synchronous rectifier to reduce rectifier forward voltage drop and associated power loss. Synchronous rectification provides a significant improvement in efficiency whenever the output voltage is relatively low compared to the voltage drop across an ordinary rectifier diode.

### Feature Description (continued)

### 8.3.4 Current Limiting

A current limit feature allows the LM3673 to protect itself and external components during overload conditions. PWM mode implements current limiting using an internal comparator that trips at 750 mA (typical). If the output is shorted to ground the device enters a timed current limit mode where the NFET is turned on for a longer duration until the inductor current falls below a low threshold. This allows the inductor current more time to decay, thereby preventing runaway.

## 8.3.5 Soft Start

The LM3673 has a soft-start circuit that limits in-rush current during start-up. During start-up the switch current limit is increased in steps. Soft start is activated only if EN goes from logic low to logic high after  $V_{IN}$  reaches 2.7 V. Soft start is implemented by increasing switch current limit in steps of 70 mA, 140 mA, 280 mA, and 750 mA (typical switch current limit). The start-up time thereby depends on the output capacitor and load current. Typical start-up time with a 10-µF output capacitor and 150-mA load is 280 µs; with a 5-mA load start-up time is 240 µs.

## 8.3.6 Low Drop Out Operation (LDO)

The LM3673-ADJ can operate at 100% duty cycle (no switching; PMOS switch completely on) for LDO support of the output voltage. In this way the output voltage is controlled down to the lowest possible input voltage. When the device operates near 100% duty cycle, output voltage ripple is approximately 25 mV.

The minimum input voltage needed to support the output voltage is:

$$V_{\text{IN, MIN}} = I_{\text{LOAD}} \times (R_{\text{DSON, PFET}} + R_{\text{INDUCTOR}}) + V_{\text{OUT}}$$

where

- I<sub>LOAD:</sub> Load current

- R<sub>DSON, PFET</sub>: Drain-to-source resistance of PFET switch in the triode region

- R<sub>INDUCTOR</sub>: Inductor resistance

(1)

## 8.4 Device Functional Modes

### 8.4.1 **PFM** Operation

At very light load, the converter enters PFM mode and operates with reduced switching frequency and supply current to maintain high efficiency.

The part automatically transitions into PFM mode when either of two conditions occurs for a duration of 32 or more clock cycles:

- The NFET current reaches zero.

- The peak PMOS switch current drops below the I<sub>MODE</sub> level (typically I<sub>MODE</sub> < 30 mA + V<sub>IN</sub> / 42  $\Omega$ ).

Figure 15. Typical PFM Operation

## **Device Functional Modes (continued)**

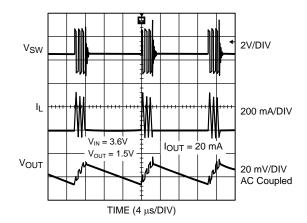

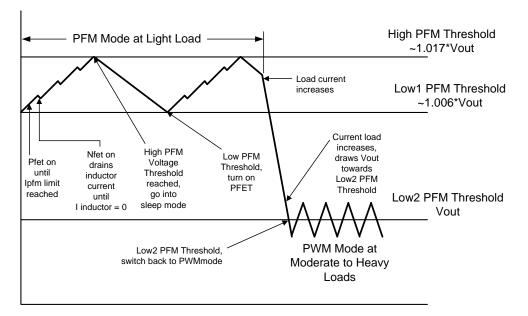

During PFM operation, the converter positions the output voltage slightly higher than the nominal output voltage during PWM operation, allowing additional headroom for voltage drop during a load transient from light to heavy load. The PFM comparators sense the output voltage via the FB pin and control the switching of the output FETs such that the output voltage ramps from approximately 0.6% to approximately 1.7% above the nominal PWM output voltage. If the output voltage is below the *high* PFM comparator threshold, the PMOS power switch is turned on. It remains on until the output voltage reaches the *high* PFM threshold or the peak current exceeds the  $I_{PFM}$  level set for PFM mode. The typical peak current in PFM mode is:  $I_{PFM} = 112 \text{ mA} + V_{IN} / 27 \Omega$ .

Once the PMOS power switch is turned off, the NMOS power switch is turned on until the inductor current ramps to zero. When the NMOS zero-current condition is detected, the NMOS power switch is turned off. If the output voltage is below the *high* PFM comparator threshold (see Figure 16), the PMOS switch is again turned on and the cycle is repeated until the output reaches the desired level. Once the output reaches the *high* PFM threshold, the NMOS switch is turned on briefly to ramp the inductor current to zero and then both output switches are turned off and the part enters an extremely low power mode. Quiescent supply current during this *sleep* mode is 16 µA (typical), which allows the device to achieve high efficiency under extremely light load conditions.

If the load current increases during PFM mode (see Figure 16) causing the output voltage to fall below the *Low 2* PFM threshold, the device automatically transitions into fixed-frequency PWM mode. When  $V_{IN} = 2.7$  V, the device transitions from PWM mode to PFM mode at approximately 35-mA output current and from PFM mode to PWM mode at approximately 85 mA. When  $V_{IN} = 3.6$  V, PWM-to-PFM transition happens at approximately 50 mA and PFM-to-PWM transition happens at approximately 100 mA. When  $V_{IN} = 4.5$  V, PWM-to-PFM transition happens at approximately 65 mA and PFM-to-PWM transition happens at approximately 115 mA.

Figure 16. Operation in PFM Mode and Transfer to PWM Mode

### 8.4.2 Shutdown Mode

Setting the EN input pin low (< 0.4 V) places the LM3673 in shutdown mode. During shutdown the PFET switch, NFET switch, reference, control, and bias circuitry of the LM3673 are turned off. Setting EN high (> 1 V) enables normal operation. Setting the EN pin low is recommended to turn off the LM3673 during system power up and undervoltage conditions when the supply is less than 2.7 V. Do not leave the EN pin floating.

#### LM3673 SNVS434M – JULY 2006–REVISED NOVEMBER 2016

## 9 Application and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The LM3673 is designed for powering low-voltage circuits from a single Li-Ion cell battery and input-voltage rails from 2.7 V to 5.5 V. The device is internally powered from the VIN pin, and the typical switching frequency is 2 MHz. The LM3673 is available in 1.2-V, 1.5-V, and 1.8-V options. An externally adjustable version is also available where the output voltage can be set with an external resistor divider to the FB pin.

## 9.2 Typical Applications

Figure 17. LM3673 Typical Application Circuit

Figure 18. LM3673-ADJ Typical Application Circuit

### 9.2.1 Design Requirements

For typical step-down DC-DC converter applications, use the parameters listed in Table 1.

#### **Table 1. Design Parameters**

| DESIGN PARAMETER      | EXAMPLE VALUE                     |  |

|-----------------------|-----------------------------------|--|

| Minimum input voltage | 2.7 V                             |  |

| Output voltage        | several fixed options; adjustable |  |

| Maximum load current  | 350 mA                            |  |

| Switching frequency   | 2 MHz (typical)                   |  |

## 9.2.2 Detailed Design Procedure

### 9.2.2.1 Output Voltage Selection for LM3673-ADJ

The output voltage of the adjustable device can be programmed through the resistor network connected from  $V_{OUT}$  to FB, then to GND.  $V_{OUT}$  is adjusted to make the voltage at FB equal to 0.5 V. The resistor from FB to GND (R2) must be 200 k $\Omega$  to keep the current drawn through this network well below the 16-µA quiescent current level (PFM mode) but large enough that it is not susceptible to noise. If R2 is 200 k $\Omega$ , and  $V_{FB}$  is 0.5 V, the current through the resistor feedback network is 2.5 µA. The output voltage of the adjustable device ranges from 1.1 V to 3.3 V.

The formula for output voltage selection is:

$$V_{OUT} = V_{FB} * \left(1 + \frac{R1}{R2}\right)$$

where

• V<sub>OUT</sub>: output voltage (V)

1

- V<sub>FB</sub> : feedback voltage = 0.5 V

- R1: feedback resistor from V<sub>OUT</sub> to FB

- R2: feedback resistor from FB to GND

For any output voltage greater than or equal to 1.1 V, a zero must be added around 45 kHz for stability. The formula for calculation of C1 is:

$$C1 = \frac{1}{(2 * \pi * R1 * 45 \text{ kHz})}$$

(3)

For output voltages higher than 2.5 V, a pole must be placed at 45 kHz as well. If the pole and zero are at the same frequency the formula for calculation of C2 is:

$$C2 = \frac{1}{(2 * \pi * R2 * 45 \text{ kHz})}$$

(4)

The formula for location of zero and pole frequency created by adding C1 and C2 is shown in Equation 5 and Equation 6. By adding C1, a zero as well as a higher frequency pole is introduced.

$$Fz = \frac{1}{(2 * \pi * R1 * C1)}$$

$$Fp = \frac{1}{2 * \pi * (R1 || R2) * (C1+C2)}$$

(5)

(6)

See Table 2.

(2)

| V <sub>OUT</sub> (V) | R1(kΩ) | R2 (kΩ) | C1 (pF) | C2 (pF) | L (µH) | C <sub>IN</sub> (μF) | C <sub>ΟUT</sub> (μF) |

|----------------------|--------|---------|---------|---------|--------|----------------------|-----------------------|

| 1.1                  | 240    | 200     | 15      | None    | 2.2    | 4.7                  | 10                    |

| 1.2                  | 280    | 200     | 12      | None    | 2.2    | 4.7                  | 10                    |

| 1.3                  | 320    | 200     | 12      | None    | 2.2    | 4.7                  | 10                    |

| 1.5                  | 357    | 178     | 10      | None    | 2.2    | 4.7                  | 10                    |

| 1.6                  | 442    | 200     | 8.2     | None    | 2.2    | 4.7                  | 10                    |

| 1.7                  | 432    | 178     | 8.2     | None    | 2.2    | 4.7                  | 10                    |

| 1.8                  | 464    | 178     | 8.2     | None    | 2.2    | 4.7                  | 10                    |

| 1.875                | 523    | 191     | 6.8     | None    | 2.2    | 4.7                  | 10                    |

| 2.5                  | 402    | 100     | 8.2     | None    | 2.2    | 4.7                  | 10                    |

| 2.8                  | 464    | 100     | 8.2     | 33      | 2.2    | 4.7                  | 10                    |

| 3.3                  | 562    | 100     | 6.8     | 33      | 2.2    | 4.7                  | 10                    |

## Table 2. LM3673-ADJ Configurations For Various V<sub>OUT</sub><sup>(1)</sup>

(1) Circuit of *Typical Application Circuit for ADJ Version*.

## 9.2.2.2 Inductor Selection

There are two main considerations when choosing an inductor; the inductor must not saturate, and the inductor current ripple must be small enough to achieve the desired output voltage ripple. Different saturation current rating specifications are followed by different manufacturers so attention must be given to details. Saturation current ratings are typically specified at 25°C. However, ratings at the maximum ambient temperature of application should be requested from the manufacturer. *The minimum value of inductance to ensure good performance is 1.76 \muH at I\_{LIM} (typical) DC current over the ambient temperature range. Shielded inductors radiate less noise and are preferred.*

There are two methods to choose the inductor saturation current rating.

### 9.2.2.2.1 Method 1

The saturation current must be greater than the sum of the maximum load current and the worst case average to peak inductor current. This can be written as:

$I_{SAT} > I_{OUTMAX} + I_{RIPPLE}$

where

$$I_{RIPPLE} = \left(\frac{V_{IN} - V_{OUT}}{2 * L}\right) * \left(\frac{V_{OUT}}{V_{IN}}\right) * \left(\frac{1}{f}\right)$$

where

- I<sub>RIPPLE</sub>: average to peak inductor current

- I<sub>OUTMAX</sub>: maximum load current (350 mA)

- V<sub>IN</sub>: maximum input voltage in application

- L : min inductor value including worst case tolerances (30% drop can be considered for Method 1)

- *f* : minimum switching frequency (1.6 MHz)

- V<sub>OUT</sub>: output voltage

### 9.2.2.2.2 Method 2

A more conservative and recommended approach is to choose an inductor that has a saturation current rating greater than the maximum current limit of 855 mA.

A 2.2- $\mu$ H inductor with a saturation current rating of at least 855 mA is recommended for most applications. Resistance of the inductor must be less than 0.3  $\Omega$  for good efficiency. Table 3 lists suggested inductors and suppliers. For low-cost applications, an unshielded bobbin inductor could be considered. For noise critical applications, a toroidal or shielded-bobbin inductor must be used. A good practice is to lay out the board with overlapping footprints of both types for design flexibility. This allows substitution of a low-noise shielded inductor, in the event that noise from low-cost bobbin models is unacceptable.

(7)

#### LM3673 SNVS434M-JULY 2006-REVISED NOVEMBER 2016

## 9.2.2.3 Input Capacitor Selection

A ceramic input capacitor of 4.7  $\mu$ F, 6.3 V is sufficient for most applications. Place the input capacitor as close as possible to the V<sub>IN</sub> pin of the device. A larger value may be used for improved input voltage filtering. Use X7R or X5R types; do not use Y5V. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0805 and 0603. *The minimum input capacitance to ensure good performance is 2.2 \muF at 3-V DC bias; 1.5 \muF at 5-V DC bias including tolerances and over ambient temperature range. The input filter capacitor supplies current to the PFET switch of the LM3673 in the first half of each cycle and reduces voltage ripple imposed on the input power source. The low ESR of a ceramic capacitor provides the best noise filtering of the input voltage spikes due to this rapidly changing current. Select a capacitor with sufficient ripple current rating. The input current ripple can be calculated as:*

$$I_{RMS} = I_{OUTMAX} * \sqrt{\frac{V_{OUT}}{V_{IN}}} * \left(1 - \frac{V_{OUT}}{V_{IN}} + \frac{r^2}{12}\right)$$

$$(V_{IN} - V_{OUT}) * V_{OUT}$$

$r = \frac{1}{L + f + I_{OUTMAX} + V_{IN}}$

The worst case is when  $V_{IN} = 2 * V_{OUT}$

|                   |                | ••                        |               |  |  |  |  |  |  |  |

|-------------------|----------------|---------------------------|---------------|--|--|--|--|--|--|--|

| MODEL             | VENDOR         | DIMENSIONS L × W × H (mm) | DCR (maximum) |  |  |  |  |  |  |  |

| COIL              |                |                           |               |  |  |  |  |  |  |  |

| BRL2518T2R2M      | Taiyo Yuden    | 2.5 × 1.8 × 1.2           | 135 mΩ        |  |  |  |  |  |  |  |

| DO3314-222MX      | Coilcraft      | 3.3 × 3.3 × 1.4           | 200 mΩ        |  |  |  |  |  |  |  |

| LPO3310-222MX     | Coilcraft      | 3.3 × 3.3 × 1             | 150 mΩ        |  |  |  |  |  |  |  |

| CDRH2D14-2R2      | Sumida         | 3.2 × 3.2 × 1.55          | 94 mΩ         |  |  |  |  |  |  |  |

|                   |                | CHIP                      |               |  |  |  |  |  |  |  |

| KSLI-2520101AG2R2 | Hitachi Metals | 2.5 × 2 × 1.0             | 115 mΩ        |  |  |  |  |  |  |  |

| LQM31PN2R2M00     | Murata         | 3.2 × 1.6 × 0.95          | 220 mΩ        |  |  |  |  |  |  |  |

| LQM2HPN2R2MJ0     | Murata         | 2.5 × 2 × 1.2             | 160 mΩ        |  |  |  |  |  |  |  |

## Table 3. Suggested Inductors and Their Suppliers

### 9.2.2.4 Output Capacitor Selection

A ceramic output capacitor of 10  $\mu$ F, 6.3 V is sufficient for most applications. Use X7R or X5R types; do not use Y5V. DC bias characteristics of ceramic capacitors must be considered when selecting case sizes like 0805 and 0603. DC bias characteristics vary from manufacturer to manufacturer and DC bias curves should be requested from them as part of the capacitor selection process.

The minimum output capacitance to ensure good performance is 5.75  $\mu$ F at 1.8-V DC bias including tolerances and over ambient temperature range. The output filter capacitor smoothes out current flow from the inductor to the load, helps maintain a steady output voltage during transient load changes and reduces output voltage ripple. These capacitors must be selected with sufficient capacitance and sufficiently low ESR to perform these functions.

The output voltage ripple is caused by the charging and discharging of the output capacitor and by the  $R_{ESR}$  and can be calculated as:

Voltage peak-to-peak ripple due to capacitance can be expressed as follows:

$$V_{PP-C} = \frac{I_{RIPPLE}}{4^* f^* C}$$

Voltage peak-to-peak ripple due to ESR can be expressed as follows:

$V_{PP-ESR} = (2 \times I_{RIPPLE}) \times R_{ESR}$

Because these two components are out of phase the root mean squared (RMS) value can be used to get an approximate value of peak-to-peak ripple.

(8)

www.ti.com

(9)

The peak-to-peak ripple voltage, rms value can be expressed as follow:

$$V_{\text{PP-RMS}} = \sqrt{V_{\text{PP-C}}^2 + V_{\text{PP-ESR}}^2}$$

(10)

The output voltage ripple is dependent on the inductor current ripple and the equivalent series resistance of the output capacitor ( $R_{ESR}$ ).

The R<sub>ESR</sub> is frequency dependent (as well as temperature dependent); make sure the value used for calculations is at the switching frequency of the device.

|                            |              | •           | ••             |                     |

|----------------------------|--------------|-------------|----------------|---------------------|

| MODEL                      | TYPE         | VENDOR      | VOLTAGE RATING | CASE SIZE inch (mm) |

| 4.7 μF for C <sub>IN</sub> |              |             |                |                     |

| C2012X5R0J475K             | Ceramic, X5R | TDK         | 6.3 V          | 0805 (2012)         |

| JMK212BJ475K               | Ceramic, X5R | Taiyo-Yuden | 6.3 V          | 0805 (2012)         |

| GRM21BR60J475K             | Ceramic, X5R | Murata      | 6.3 V          | 0805 (2012)         |

| C1608X5R0J475K             | Ceramic, X5R | TDK         | 6.3 V          | 0603 (1608)         |

| 10 μF for C <sub>OUT</sub> |              |             |                |                     |

| GRM21BR60J106K             | Ceramic, X5R | Murata      | 6.3 V          | 0805 (2012)         |

| JMK212BJ106K               | Ceramic, X5R | Taiyo-Yuden | 6.3 V          | 0805 (2012)         |

| C2012X5R0J106K             | Ceramic, X5R | TDK         | 6.3 V          | 0805 (2012)         |

| C1608X5R0J106K             | Ceramic, X5R | TDK         | 6.3 V          | 0603 (1608)         |

Table 4. Suggested Capacitors and Their Suppliers

## 9.2.3 Application Curves

## **10 Power Supply Recommendations**

The LM3673 requires a single supply input voltage. This voltage can range between 2.7 V to 5.5 V and must be able to supply enough current for a given application.

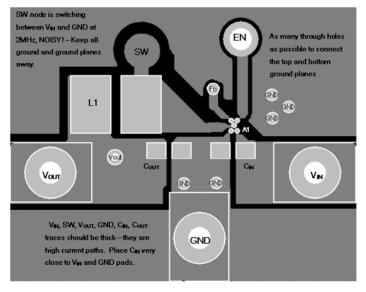

## 11 Layout

## 11.1 Layout Guidelines

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce, and resistive voltage loss in the traces. These can send erroneous signals to the DC-DC converter device, resulting in poor regulation or instability.

Good layout for the LM3673 can be implemented by following a few simple design rules below. Refer to Figure 28 for top layer board layout.

- 1. Place the LM3673, inductor and filter capacitors close together and make the traces short. The traces between these components carry relatively high switching currents and act as antennas. Following this rule reduces radiated noise. Special care must be given to place the input filter capacitor very close to the VIN and GND pins.

- 2. Arrange the components so that the switching current loops curl in the same direction. During the first half of each cycle, current flows from the input filter capacitor through the LM3673 and inductor to the output filter capacitor and back through ground, forming a current loop. In the second half of each cycle, current is pulled up from ground through the LM3673 by the inductor to the output filter capacitor and then back through ground forming a second current loop. Routing these loops so the current curls in the same direction prevents magnetic field reversal between the two half-cycles and reduces radiated noise.

- 3. Connect the ground pins of the LM3673 and filter capacitors together using generous component-side copper fill as a pseudo-ground plane. Then, connect this to the ground-plane (if one is used) with several vias. This reduces ground-plane noise by preventing the switching currents from circulating through the ground plane. It also reduces ground bounce at the LM3673 by giving it a low-impedance ground connection.

- 4. Use wide traces between the power components and for power connections to the DC-DC converter circuit. This reduces voltage errors caused by resistive losses across the traces.

- 5. Route noise sensitive traces, such as the voltage feedback path, away from noisy traces between the power components. The voltage feedback trace must remain close to the LM3673 circuit and must be direct, but routed opposite to noisy components. This reduces EMI radiated onto the own voltage feedback trace of the DC-DC converter. A good approach is to route the feedback trace on another layer and to have a ground plane between the top layer and layer on which the feedback trace is routed. For the adjustable device option, it is also best to have the feedback dividers on the bottom layer.

- 6. Place noise sensitive circuitry, such as radio IF blocks, away from the DC-DC converter, CMOS digital blocks and other noisy circuitry. Interference with noise-sensitive circuitry in the system can be reduced through distance.

In mobile phones, for example, a common practice is to place the DC-DC converter on one corner of the board, arrange the CMOS digital circuitry around it (because this also generates noise), and then place sensitive preamplifiers and IF stages on the diagonally opposing corner. Often, the sensitive circuitry is shielded with a metal pan and power to it is post-regulated to reduce conducted noise, using low-dropout linear regulators.

## 11.2 Layout Example

Figure 28. LM3673 DSBGA Top Layer Board Layout

## 11.3 DSBGA Package Assembly and Use

Use of the DSBGA package requires specialized board layout, precision mounting and careful re-flow techniques, as detailed in Texas Instruments *AN-1112 DSBGA Wafer Level Chip Scale Package*. Refer to the section *Surface Mount Technology (SMD) Assembly Considerations*. For best results in assembly, alignment ordinals on the PC board must be used to facilitate placement of the device. The pad style used with DSBGA package must be the NSMD (non-solder mask defined) type. This means that the solder-mask opening is larger than the pad size. This prevents a lip that otherwise forms if the solder-mask and pad overlap, from holding the device off the surface of the board and interfering with mounting. See SNVA009 for specific instructions how to do this. The 5-pin package used for LM3673 has 300-micron solder balls and requires 10.82 mils pads for mounting on the circuit board. The trace to each pad must enter the pad with a 90° entry angle to prevent debris from being caught in deep corners. Initially, the trace to each pad must be 7 mil wide, for a section approximately 7 mil long or longer, as a thermal relief. Then each trace must neck up or down to its optimal width. The important criteria is symmetry. This ensures the solder bumps on the LM3673 re-flow evenly and that the device solders level to the board. In particular, special attention must be paid to the pads for bumps A1 and A3, because VIN and GND are typically connected to large copper planes, inadequate thermal relief can result in late or inadequate re-flow of these bumps.

The DSBGA package is optimized for the smallest possible size in applications with red or infrared opaque cases. Because the DSBGA package lacks the plastic encapsulation characteristic of larger devices, it is vulnerable to light. Backside metallization and/or epoxy coating, along with front-side shading by the printed circuit board, reduce this sensitivity. However, the package has exposed die edges. In particular, DSBGA devices are sensitive to light, in the red and infrared range, shining on the package's exposed die edges.

TEXAS INSTRUMENTS

www.ti.com

## **12 Device and Documentation Support**

## 12.1 Device Support

#### 12.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

### **12.2 Documentation Support**

#### 12.2.1 Related Documentation

For further information, see the following:

AN-1112 DSBGA Wafer Level Chip Scale Package

### **12.3 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 12.4 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 12.5 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 12.6 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## **PACKAGING INFORMATION**

| Orderable Device   |        | Package Type | •       | Pins | •    |              | Lead finish/  | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|--------------------|--------|--------------|---------|------|------|--------------|---------------|--------------------|--------------|----------------|---------|

|                    | (1)    |              | Drawing |      | Qty  | (2)          | Ball material | (3)                |              | (4/5)          |         |

| LM3673TL-1.2/NOPB  | ACTIVE | DSBGA        | YZR     | 5    | 250  | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | 1              | Samples |

| LM3673TL-1.5/NOPB  | ACTIVE | DSBGA        | YZR     | 5    | 250  | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | Н              | Samples |

| LM3673TL-1.8/NOPB  | ACTIVE | DSBGA        | YZR     | 5    | 250  | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | F              | Samples |

| LM3673TL-ADJ/NOPB  | ACTIVE | DSBGA        | YZR     | 5    | 250  | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | R              | Samples |

| LM3673TLX-1.2/NOPB | ACTIVE | DSBGA        | YZR     | 5    | 3000 | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | 1              | Samples |

| LM3673TLX-1.8/NOPB | ACTIVE | DSBGA        | YZR     | 5    | 3000 | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | F              | Samples |

| LM3673TLX-ADJ/NOPB | ACTIVE | DSBGA        | YZR     | 5    | 3000 | RoHS & Green | SNAGCU        | Level-1-260C-UNLIM | -30 to 85    | R              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

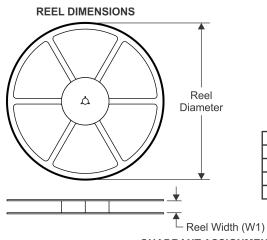

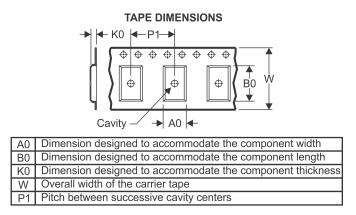

## TAPE AND REEL INFORMATION

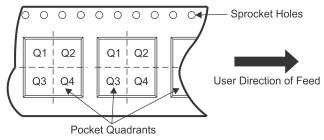

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| LM3673TL-1.2/NOPB           | DSBGA           | YZR                | 5 | 250  | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TL-1.5/NOPB           | DSBGA           | YZR                | 5 | 250  | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TL-1.8/NOPB           | DSBGA           | YZR                | 5 | 250  | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TL-ADJ/NOPB           | DSBGA           | YZR                | 5 | 250  | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TLX-1.2/NOPB          | DSBGA           | YZR                | 5 | 3000 | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TLX-1.8/NOPB          | DSBGA           | YZR                | 5 | 3000 | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

| LM3673TLX-ADJ/NOPB          | DSBGA           | YZR                | 5 | 3000 | 178.0                    | 8.4                      | 1.14       | 1.47       | 0.76       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

20-Jul-2019

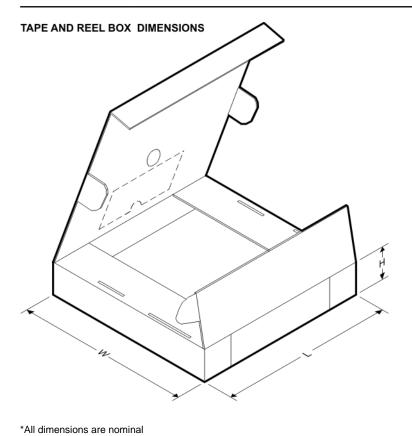

| *All dimensions are nominal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LM3673TL-1.2/NOPB           | DSBGA        | YZR             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LM3673TL-1.5/NOPB           | DSBGA        | YZR             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LM3673TL-1.8/NOPB           | DSBGA        | YZR             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LM3673TL-ADJ/NOPB           | DSBGA        | YZR             | 5    | 250  | 210.0       | 185.0      | 35.0        |

| LM3673TLX-1.2/NOPB          | DSBGA        | YZR             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LM3673TLX-1.8/NOPB          | DSBGA        | YZR             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

| LM3673TLX-ADJ/NOPB          | DSBGA        | YZR             | 5    | 3000 | 210.0       | 185.0      | 35.0        |

# YZR0005

B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated