#### Self powered digital input current limiter

# Features2 isolate

- 2 isolated channels device

- · No power supply needed

- · Digital input current limitation

- · Glitch filter for EMC robustness

- · High side/ Low side compatible

- · Input are reverse plugin compatible

- Direct opto-coupler or 3.3 V LVTTL output

- Operating temperature range from 30 °C to 125 °C

- QFN 2 x 4 16L 500 μm pitch

- Exceeds IEC 61000-4-2 level 4 standard:

- ±4 kV (air discharge)

- ±2 kV (contact discharge)

- IEC61131-2 type 3

- IEC 61508

#### **Applications**

Where current limitation is required in factory automation application:

- · Programmable logic controller

- · Remote input module

#### Description

The CLT03-2Q3 is a digital input current limiter which does not require external power supply and is powered through inputs. The product is housed in a QFN 2 x 4-16L and is high side, low side compatible and as well as reverse plugin compatible.

The CLT03-2Q3 can drive either opto-coupler or 3.3V LVTTL circuit.

# Product status link CLT03-2Q3

| Product summary       |             |  |

|-----------------------|-------------|--|

| Order code            | CLT03-2Q3   |  |

| Package               | QFN 2X4-16L |  |

| Packing Tape and reel |             |  |

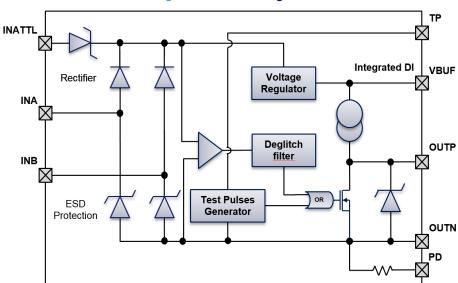

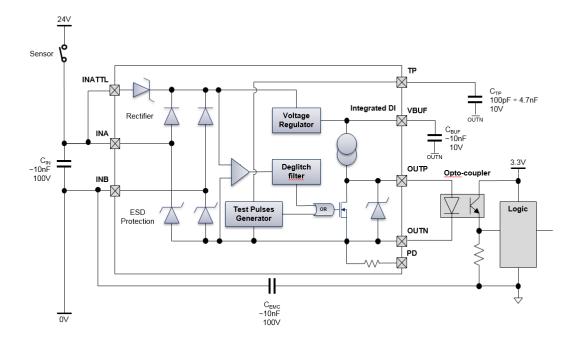

# 1 Circuit block diagram

Figure 1. One line diagram

# 1.1 I/O pin description

Table 1. Pins name, type and description

| Name              | Pin#      | Туре          | Description                                                        |

|-------------------|-----------|---------------|--------------------------------------------------------------------|

| INA1 / INA2       | 7/3       | Signal input  | Logic input with current limitation                                |

| INATTL1 / INATTL2 | 6/2       | Signal input  | Logic input with current limitation for non-isolated configuration |

| INB1 / INB2       | 8 / 4     | Signal input  | Logic input with current limitation                                |

| TP1 / TP2         | 9 / 14    | Test input    | Test pulse input for capacitor                                     |

| VBUF1 / VBUF2     | 10 / 15   | Power output  | Buffer capacitor                                                   |

| OUTN1             | 5 / TAB1  | Ground        | Logic output ground (channel 1 output ground)                      |

| OUTN2             | 13 / TAB2 | Ground        | Logic output ground (channel 2 output ground)                      |

| OUTP1 / OUTP2     | 11 / 16   | Signal output | Data output                                                        |

| PD1/PD2           | 12 / 1    | Ground        | Logic output ground with pull down resistor (non-isolated mode)    |

DS12302 - Rev 2 page 2/18

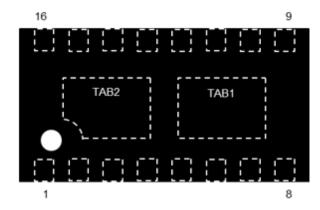

Figure 2. QFN 2x4-16L pinout (top view)

DS12302 - Rev 2 page 3/18

#### 2 Characteristics

Table 2. Absolute maximum ratings

| Symbol                 | Parameter name                                      | Value        | Unit            |    |

|------------------------|-----------------------------------------------------|--------------|-----------------|----|

| V <sub>PP</sub>        | Peak pulse voltage HBM                              |              | 2               | kV |

| V <sub>PP</sub> (1)(2) | Peak pulse voltage (pins INA, INATTL & INB), IEC 61 | 2            | kV              |    |

| V <sub>IN</sub>        | Maximum input voltage for 1 minute                  | -60 to 60    | V               |    |

| V <sub>ISO</sub>       | Isolation between channel 1 and 2                   | 230          | V <sub>AC</sub> |    |

| Tj                     | Maximum operating ambient temperature               | 175          | °C              |    |

| T <sub>STG</sub>       | Storage temperature range                           | -55 to + 150 | °C              |    |

<sup>1.</sup> See application schematic

Table 3. Electrical characteristics (-30 °C < T $_{\rm j}$  < +125 °C, unless otherwise specified) (values)

| Symbol             | Description                                                 | Name                                                              | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

|                    |                                                             | Input                                                             |      |      |      |      |

| I <sub>LIM</sub>   | Input current – On state                                    |                                                                   |      |      | 4    | mA   |

| $V_{TLH}$          | High to Low state input voltage                             | •                                                                 |      | 9.4  | 11   | V    |

| $V_{THL}$          | Low to High state input voltage                             | •                                                                 | 5    | 7.5  |      | V    |

| V <sub>HYST</sub>  | Input triggering voltage hystere                            | esis                                                              | 1.2  |      | 2.6  | V    |

| V <sub>FAULT</sub> | Fault mode threshold voltage                                |                                                                   | 30   | 40   |      | V    |

| I <sub>FAULT</sub> | Input current in fault region VIN                           | N > V <sub>FAULT</sub>                                            | 1    |      | 3    | mA   |

| t <sub>FAULT</sub> | Fault mode triggering latency a                             | after V <sub>IN</sub> > V <sub>FAULT</sub>                        |      | 25   |      | μs   |

|                    |                                                             | Timing parameters                                                 |      |      |      |      |

| f <sub>IN</sub>    | Input frequency                                             |                                                                   |      | 35   | kHz  |      |

| t <sub>PLH</sub>   | Input to output low to high propagation time <sup>(1)</sup> |                                                                   |      |      | 5    | μs   |

| t <sub>PHL</sub>   | Input to output high to low prop                            | pagation time (1)                                                 | 2    |      | 5    | μs   |

|                    |                                                             | Ouput                                                             |      |      |      |      |

|                    | On state                                                    | Isolated mode                                                     | 2    |      | 4    | mA   |

| I <sub>OUT</sub>   | Offstate                                                    | Non-isolated mode                                                 |      |      | 1    | mA   |

|                    | Off state                                                   | Isolated and non-isolated mode                                    | -10  |      | 10   | μA   |

| V <sub>OUT</sub>   | On state Isolated and non-isolated mode                     |                                                                   | 3    |      | 3.6  | V    |

| V OU I             | Off state                                                   | Isolated and non-isolated mode                                    | -3   |      | -0.4 | V    |

| R <sub>OUT</sub>   | OUTP to OUTN internal equiva                                | alent output resistance (V <sub>INA</sub> - V <sub>INB</sub> = 0) |      | 24   |      | kΩ   |

| R <sub>PD</sub>    | OUTN to PD internal pull down                               | n resistor                                                        | 2.85 |      | 4.25 | kΩ   |

<sup>1.</sup> See rise/fall time measurement section

DS12302 - Rev 2 page 4/18

<sup>2.</sup> Performance level depends on layout and environment

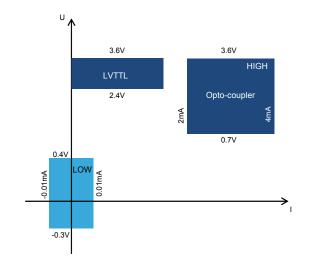

# 3 U-I operation description

OFF REGION

OFF REGION

OFF REGION

OFF REGION

OFF REGION

ON REGION

OFF REG

Figure 3. Input U-I operation

Figure 4. Output U-I operation

DS12302 - Rev 2 page 5/18

#### 4 Fault mode description

Fault mode is a working mode of CLT03-2Q3 occuring when input voltage is higher than 30 V minimum ( $V_{FAULT}$ ). In normal conditions, the system is not meant to operate in this area. However, the IEC 61508 requires that systems should survive up to 1 minute with voltages up to 60 V.

When  $V_{IN} > V_{FAULT}$ , the impacted channel enters into fault mode after a certain time defined as  $t_{FAULT}$ . When fault mode is activated, the input current limitation is reduced down to  $I_{FAULT}$ . In this mode, the channel output is not functional anymore.

CLT03-2Q3 guarantees fault mode conditions up to 1 minute according to IEC 61508 standard.

DS12302 - Rev 2 page 6/18

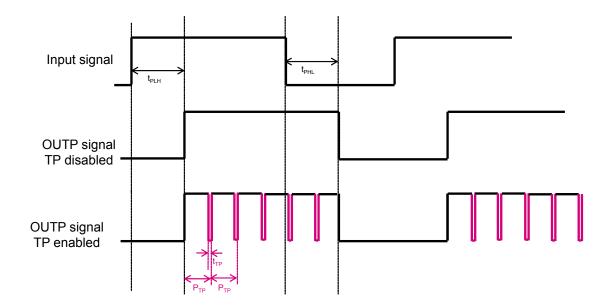

#### 5 Test pulse feature description

The built-in test pulse feature complies with the latest safety standards. Thus, it is possible to know on a regular basis that CLT03-2Q3 is still working properly.

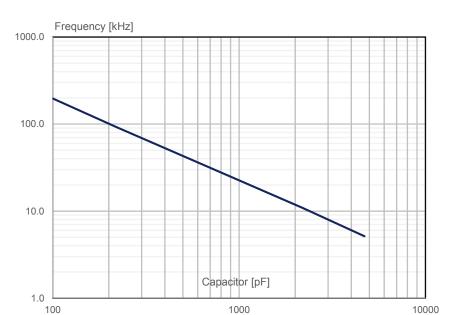

In order, to enable the Test Pulse feature a capacitor should be connected between TP and OUTN pins. When such a capacitor is connected, the OUTP value will be forced to low state every TP period ( $P_{TP}$ ) for a define test pulse width ( $t_{TP}$ ). TP period is equal to 256 times  $t_{TP}$ .

The frequency of the "Test Pulse low state" is managed through the capacitor value. In order to disable this feature, TP should be shorted to OUTN.

| Symbol          | Description                                                       | Min.                  | Тур. | Max. | Unit |

|-----------------|-------------------------------------------------------------------|-----------------------|------|------|------|

| f <sub>TP</sub> | PTest pulse frequency                                             | 4.1                   |      | 219  | kHz  |

| C <sub>TP</sub> | External capacitor range 100 4700                                 |                       |      |      | pF   |

| t <sub>TP</sub> | Test pulse width                                                  | 1/f <sub>TP</sub>     |      |      | ms   |

| P <sub>TP</sub> | Test pulse period                                                 | 256 x t <sub>TP</sub> |      |      |      |

| $\Delta f_{TP}$ | Test pulse frequency variation (out of capacitance variation) -60 |                       |      |      | %    |

Table 4. Test pulse parameters

DS12302 - Rev 2 page 7/18

Figure 6. f<sub>TP</sub> versus C<sub>TP</sub> value

DS12302 - Rev 2 page 8/18

# 6 Propagation time measurement description

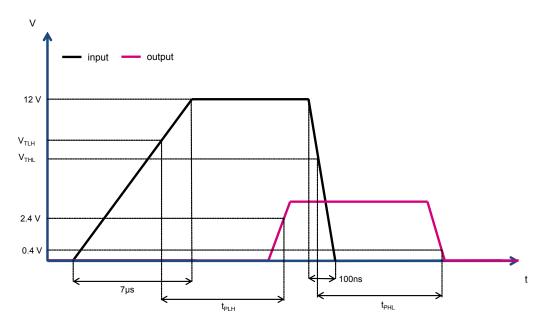

Figure 7. t<sub>PLH</sub> and t<sub>PHL</sub> test condition

Note:

for  $t_{PLH}$  and  $t_{PHL}$  measurement,  $V_{TLH}$  and  $V_{THL}$  should be determined for each sample. Timing measurement should be done with these sample specific  $V_{TLH}$  and  $V_{THL}$  thresholds.

DS12302 - Rev 2 page 9/18

# 7 Simplified application schematic

Table 5. Configuration compatibility of CLT03-2Q3

| Symbol       | High Side | Low Side |

|--------------|-----------|----------|

| Isolated     | OK        | OK       |

| Non-isolated | OK        | КО       |

Each circuit given in this section is given for 1 line only.

Figure 8. High side – isolated configuration

DS12302 - Rev 2 page 10/18

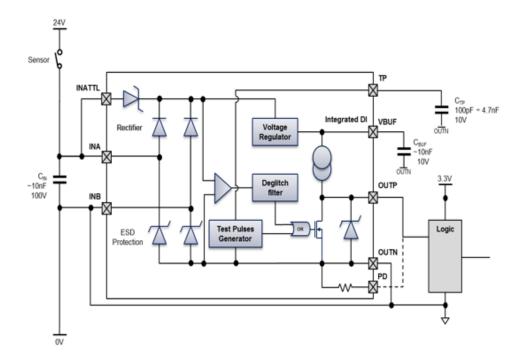

24V INATTL C<sub>TP</sub> 100pF ÷ 4.7nF 10V Integrated DI VBUF Voltage Regulator C<sub>BUF</sub> ~10nF 10V INA OUTN C<sub>IN</sub> ~10nF 100V Deglitch filter OUTP INB Test Pulses Generator OR Logic ESD Protection OUTN PD ╢ C<sub>EMC</sub> ~10nF 100V 0V

Figure 9. Low side – isolated configuration

Figure 10. High side – non-isolated configuration

Note: OUTP to PD connection is optional.

DS12302 - Rev 2 page 11/18

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

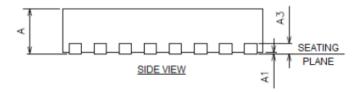

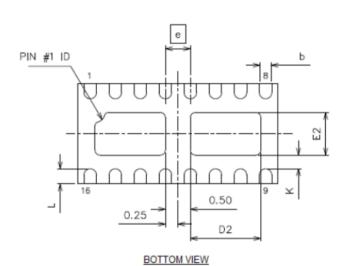

#### 8.1 QFN 2X4 -16 package information

PIN #1

INDEX AREA

TOP VIEW

Figure 11. QFN 2X4-16L package outline

DS12302 - Rev 2 page 12/18

Table 6. QFN 2X4-16L package mechanical data

|      |      |             |      | Dimensions |                       |        |

|------|------|-------------|------|------------|-----------------------|--------|

| Ref. |      | Millimeters |      |            | Inches <sup>(1)</sup> |        |

|      | Min. | Тур.        | Max. | Min.       | Тур.                  | Max.   |

| Α    | 0.80 | 0.90        | 1.00 | 0.0315     | 0.0354                | 0.0394 |

| A1   |      | 0.02        | 0.05 |            | 0.0008                | 0.0020 |

| A3   |      | 0.20        |      |            | 0.008                 |        |

| В    | 0.18 | 0.25        | 0.30 | 0.0071     | 0.0100                | 0.0118 |

| D    | 3.95 | 4.00        | 4.05 | 0.1555     | 0.1574                | 0.1594 |

| E    | 1.95 | 2.00        | 2.05 | 0.0768     | 0.0787                | 0.0807 |

| D2   | 1.25 | 1.40        | 1.51 | 0.0492     | 0.0551                | 0.0594 |

| E2   | 0.70 | 0.85        | 0.95 | 0.0276     | 0.0334                | 0.0374 |

| е    |      | 0.50        |      |            | 0.0197                |        |

| K    | 0.15 |             |      | 0.0059     |                       |        |

| L    | 0.20 | 0.30        | 0.40 | 0.0079     | 0.0118                | 0.0157 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

DS12302 - Rev 2 page 13/18

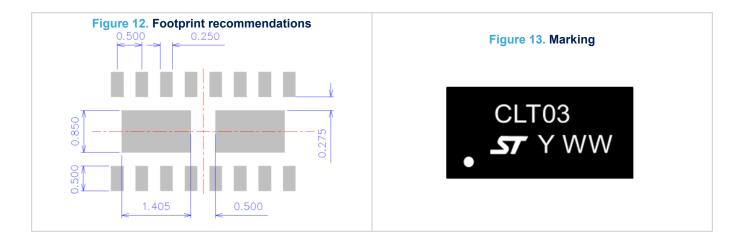

Figure 14. Tape and reel outline

Pocket dimensions are not on scale Pocket shape may vary depending on package

Table 7. Tape and reel mechanical data

|      | Dimensions  |      |      |  |  |

|------|-------------|------|------|--|--|

| Ref. | Millimeters |      |      |  |  |

|      | Min.        | Тур. | Max. |  |  |

| A    | 3.9         | 4    | 4.1  |  |  |

| A0   | 2.2         | 2.25 | 2.3  |  |  |

| A1   | 4.2         | 4.25 | 4.3  |  |  |

| В0   | 3.9         | 4    | 4.1  |  |  |

| ØD0  | 1.5         |      | 1.6  |  |  |

| ØD1  | 1           |      |      |  |  |

| F    | 1.65        | 1.75 | 1.85 |  |  |

| K    | 1.10        | 1.15 | 1.20 |  |  |

| P0   | 1.95        | 2    | 2.05 |  |  |

| W    | 11.9        | 12   | 12.3 |  |  |

page 14/18

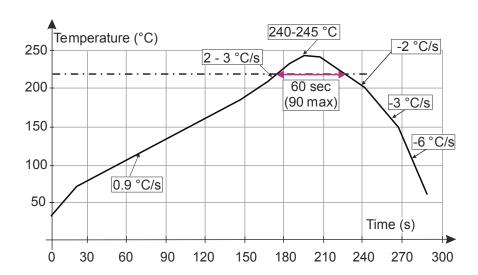

# 9 Reflow profile

Figure 15. ST ECOPACK® recommended soldering reflow profile for PCB mounting

Note: Minimize air convection currents in the reflow oven to avoid component movement.

Note: Maximum soldering profile corresponds to the latest IPC/JEDEC J-ST-020.

DS12302 - Rev 2 page 15/18

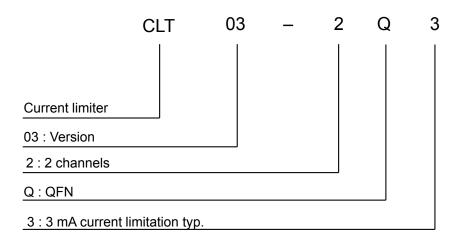

# 10 Ordering information

Figure 16. Ordering information scheme

**Table 8. Ordering information**

| Order code | Marking | Package         | Weight | Base qty. | Delivery mode |

|------------|---------|-----------------|--------|-----------|---------------|

| CLT03-2Q3  | CLT03   | QFN 2 x 4 – 16L | 20 mg  | 3000      | Tape and reel |

DS12302 - Rev 2 page 16/18

# **Revision history**

Table 9. Document revision history

| Date        | Revision | Changes                                   |

|-------------|----------|-------------------------------------------|

| 18-Dec-2017 | 1        | Initial release.                          |

| 11-Dec-2018 | 2        | Minor text change to improve readability. |

DS12302 - Rev 2 page 17/18

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

DS12302 - Rev 2 page 18/18