Qualcomm Technologies, Inc.

### WCD9335 Audio Codec

**Device Specification**

LM80-P2751-29 Rev. A February 8, 2018

> For additional information or to submit technical questions, go to: https://www.96boards.org/product/dragonboard820c/

Qualcomm Snapdragon and Qualcomm Snapdragon Voice Activation are products of Qualcomm Technologies, Inc. Other Qualcomm products referenced herein are products of Qualcomm Technologies, Inc. or its other subsidiaries.

DragonBoard, Qualcomm, and Snapdragon are trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other product and brand names may be trademarks or registered trademarks of their respective owners.

Use of this document is subject to the license set forth in Exhibit 1.

Qualcomm Technologies, Inc. 5775 Morehouse Drive San Diego, CA 92121 U.S.A.

© 2018 Qualcomm Technologies, Inc. All rights reserved.

# **Contents**

| 1 | Intr | oduction                                                                      | 7    |

|---|------|-------------------------------------------------------------------------------|------|

|   | 1.1  | Device description                                                            | 7    |

|   | 1.2  | Summary of key features                                                       | 7    |

|   | 1.3  | WCD9335 detailed functional block diagram                                     | 9    |

|   | 1.4  | Supply voltage summary                                                        | . 10 |

|   | 1.5  | Features                                                                      | . 10 |

|   | 1.6  | Terms and acronyms                                                            | . 12 |

| 2 | Pad  | definitions                                                                   | . 15 |

|   | 2.1  | I/O parameter definitions                                                     | . 16 |

|   | 2.2  | Pad descriptions                                                              | . 16 |

| 3 | Elec | ctrical specifications                                                        | . 21 |

|   | 3.1  | Absolute maximum ratings                                                      | . 21 |

|   | 3.2  | Operating conditions                                                          | . 22 |

|   | 3.3  | DC power characteristics                                                      | . 23 |

|   |      | 3.3.1 Peak current                                                            | . 23 |

|   | 3.4  | Digital logic characteristics                                                 | . 23 |

|   | 3.5  | Audio inputs and Tx processing                                                | . 23 |

|   |      | 3.5.1 Analog input through digital serial interface                           |      |

|   |      | 3.5.2 DMIC input through digital serial interface                             |      |

|   | 3.6  | Audio outputs and Rx processing                                               |      |

|   |      | 3.6.1 Digital serial interface through earpiece analog output                 |      |

|   |      | 3.6.2 Digital serial interface through HPH output                             |      |

|   |      | 3.6.3 Digital serial interface through stereo hi-fi differential line outputs |      |

|   |      | 3.6.4 Digital serial interface through single-ended line output               |      |

|   | 3.7  | Digital I/Os and digital processing                                           |      |

|   |      | 3.7.1 SLIMbus                                                                 | . 34 |

|   |      | 3.7.2 Inter-IC sound ( $I^2S$ )                                               | . 34 |

|   |      | 3.7.3 Inter-integrated circuit (I <sup>2</sup> C)                             | . 35 |

|   |      | 3.7.4 Digital microphone PDM interface                                        | . 36 |

|   |      | 3.7.5 Master clock (MCLK)                                                     | . 37 |

|   |      | 3.7.6 SoundWire                                                               | . 37 |

|   | 3.8  | Support circuits – analog                                                     | . 39 |

|   |     | 3.8.1      | Microphone bias                 | 39 |

|---|-----|------------|---------------------------------|----|

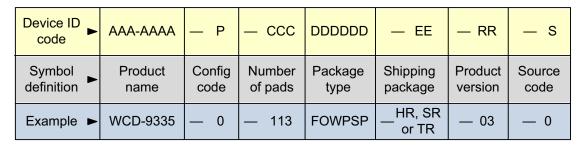

| 4 | Dev | rice mark  | king and ordering information   | 40 |

|   | 4.1 | Device of  | ordering information            | 42 |

|   |     | 4.1.1      | Specification-compliant devices | 42 |

| 5 | Car | rier, stor | rage, & handling information    | 43 |

|   | 5.1 |            |                                 |    |

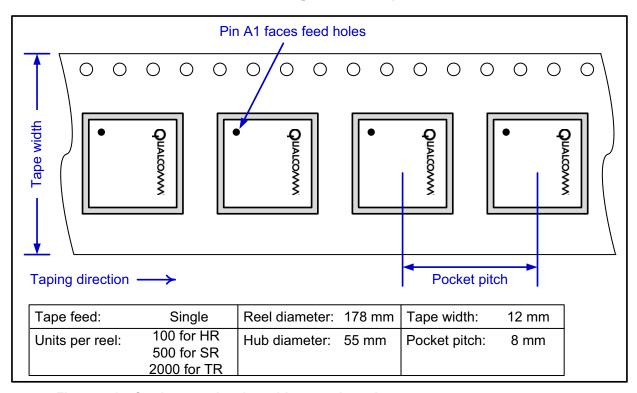

|   |     | 5.1.1      | Tape and reel information       | 43 |

|   | 5.2 |            |                                 |    |

|   |     | 5.2.1      | Bagged storage conditions       | 44 |

|   |     |            | Out-of-bag duration             |    |

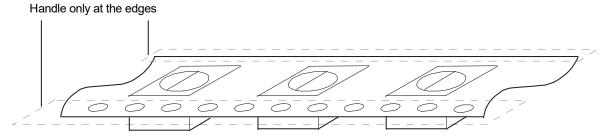

|   | 5.3 | Handling   | g                               | 44 |

|   |     | 5.3.1      | Baking                          | 44 |

|   |     | 5.3.2      | Electrostatic discharge         | 45 |

| 6 | PCE | 3 mounti   | ing guidelines                  | 46 |

|   | 6.1 | RoHS co    | ompliance                       | 46 |

| 7 | Dev | ice relial | bility                          | 47 |

|   | 7.1 |            | ty qualifications summary       |    |

|   |     |            | · · · ·                         |    |

### **Figures**

| Figure 1-1 | WCD9335 high-level block diagram                           | 8    |

|------------|------------------------------------------------------------|------|

| Figure 1-2 | WCD9335 detailed functional block diagram                  | 9    |

| Figure 2-1 | WCD9335 pad assignments (top view)                         | . 15 |

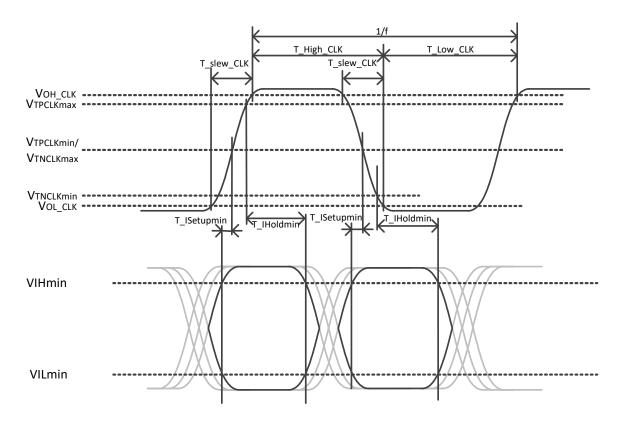

| Figure 3-1 | Received clock signal constraints                          | . 34 |

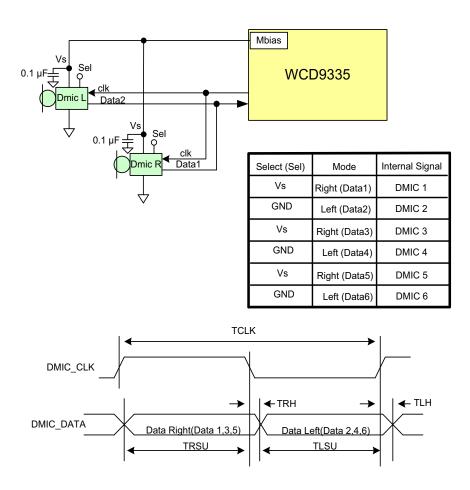

| Figure 3-2 | WCD9335 digital microphone PDM interface timing            | . 36 |

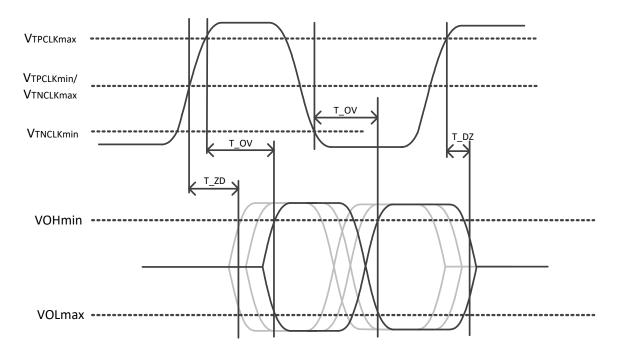

| Figure 3-3 | PHY timing – clock output/input and data input             | . 37 |

| Figure 3-4 | PHY timing – clock output/input and data input             | . 38 |

| Figure 4-1 | 113 FOWPSP (4.17 × 3.91 × 0.65 mm) package outline drawing | . 41 |

| Figure 4-2 | Device identification code                                 | . 42 |

| Figure 5-1 | Carrier tape drawing with part orientation                 | . 43 |

| Figure 5-2 | Tane handling                                              | 44   |

### **Tables**

| Table 1-1  | Summary of WCD9335 device features                                    | 10 |

|------------|-----------------------------------------------------------------------|----|

| Table 1-2  | Terms and acronyms                                                    | 12 |

| Table 2-1  | I/O description (pad type) parameters                                 | 16 |

| Table 2-2  | Pad descriptions – analog inputs                                      | 17 |

| Table 2-3  | Pad descriptions – analog outputs                                     | 17 |

| Table 2-4  | Pad descriptions – digital I/Os (other than host interfaces)          | 18 |

| Table 2-5  | Pad descriptions – host digital interfaces                            | 18 |

| Table 2-6  | Pad descriptions – support circuits                                   | 19 |

|            | Pad descriptions – do not connect pads                                |    |

|            | Pad descriptions – power supply pads                                  |    |

|            | Pad descriptions – ground pads                                        |    |

| Table 3-1  | Absolute maximum ratings                                              | 21 |

| Table 3-2  | Operating conditions                                                  | 22 |

| Table 3-3  | Power supply peak current                                             | 23 |

|            | Digital I/O characteristics                                           |    |

| Table 3-5  | Analog input through digital serial interface performance             | 24 |

| Table 3-6  | Digital microphone input through digital serial interface performance | 25 |

|            | Serial interface through mono EAR output                              |    |

|            | Serial interface through HPH output                                   |    |

|            | Serial interface through stereo-differential line outputs             |    |

|            | Serial interface through stereo line output                           |    |

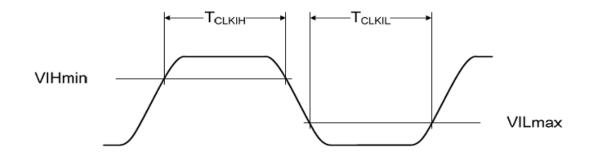

|            | Clock input timing requirements                                       |    |

|            | 2 Data output timing characteristics                                  |    |

| Table 3-13 | B Data input timing requirements                                      | 34 |

| Table 3-14 | 4 Supported I <sup>2</sup> S standards and exceptions                 | 34 |

| Table 3-15 | Master transmitter with data rate of 16 MHz                           | 35 |

| Table 3-16 | Slave receiver with clock rate of 16 MHz                              | 35 |

| Table 3-17 | 7 Supported I <sup>2</sup> C standards and exceptions                 | 35 |

| Table 3-18 | B Digital microphone timing                                           | 36 |

| Table 3-19 | Master clock (MCLK)                                                   | 37 |

| Table 3-20 | PHY timing parameters (1.8 V systems)                                 | 38 |

| Table 3-21 | Microphone bias performance                                           | 39 |

| Table 7-1  | Silicon reliability results                                           | 47 |

| Table 7-2  | Package reliability results                                           | 48 |

### **Revision history**

| Revision | Date          | Description     |

|----------|---------------|-----------------|

| Α        | February 2018 | Initial release |

### 1 Introduction

### 1.1 Device description

This document contains a description of the chipset capabilities. Not all features are available, nor are all features supported in the software.

**NOTE** Enabling some features may require additional licensing fees.

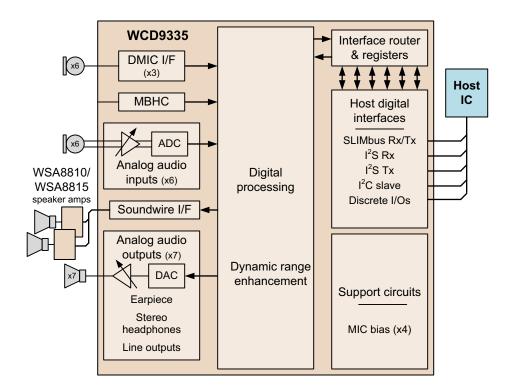

The WCD9335 is a stand-alone high fidelity (hi-fi) audio codec IC that supports the Qualcomm Technologies, Inc. (QTI) multimedia solutions, including the APQ8096SGE chipset. The key WCD9335 functions include the following:

- Serial low-power interchip media bus (SLIMbus) for access to all on-chip digital audio channels; inter-IC sound (I<sup>2</sup>S) accesses fewer paths, but maintains compatibility with earlier integrated circuits (ICs).

- SoundWire interface for driving WSA8810 or WSA8815 speaker amplifiers

- Six analog input ports and seven analog output ports

- Six audio analog-to-digital converters (ADCs) and seven digital-to-analog converters (DACs)

- Six digital microphone inputs (three clock/data pairs)

- Multibutton headset control (MBHC) for smart accessory detection

- Digital processing includes the following:

- □ Microphone activity detection (MAD) detecting audio, ultrasound, and beacon activity

- □ Qualcomm<sup>®</sup> Voice Activation subsystem

- □ Active noise cancellation (ANC)

- Integrated analog support reduces bill of materials (BOM) and area:

- $\Box$  Microphone bias outputs (x4)

### 1.2 Summary of key features

WCD9335 features are listed in Table 1-1.

- Lower cost, smaller footprint while enabling high-percentage digital content

- Ultra low-power voice activation engine for keyword detection and user identification

- Low-power, high-performance ultrasound support, including analog microphone (MIC) and line output

- Hi-fi audio recording and playback 109 dB ADC and 130 dB DAC signal-to-noise ratio (SNR)

- 32-bit/384 kHz, 44.1 kHz processing

- Supports external smart speaker amplifiers such as WSA8810/WSA8815 with 2-wire SoundWire signaling to provide configuration flexibility and reduce printed circuit board (PCB) design complexity.

- Class-H headphone amplifier 122 dB dynamic range and -105 dB THD+N

- MBHC, including an additional pad to support both tip and ground insertion/removal

- Ground reference pad for line outputs to improve signal integrity for docking stations.

- Only two external supplies are required; all other required voltages are generated by the WCD9335 support circuits.

- Highly integrated 4.17 × 3.91 mm fan out wafer-level picoscale package (FOWPSP)

See Section 1.5 for a complete list of the WCD9335 features.

Figure 1-1 WCD9335 high-level block diagram

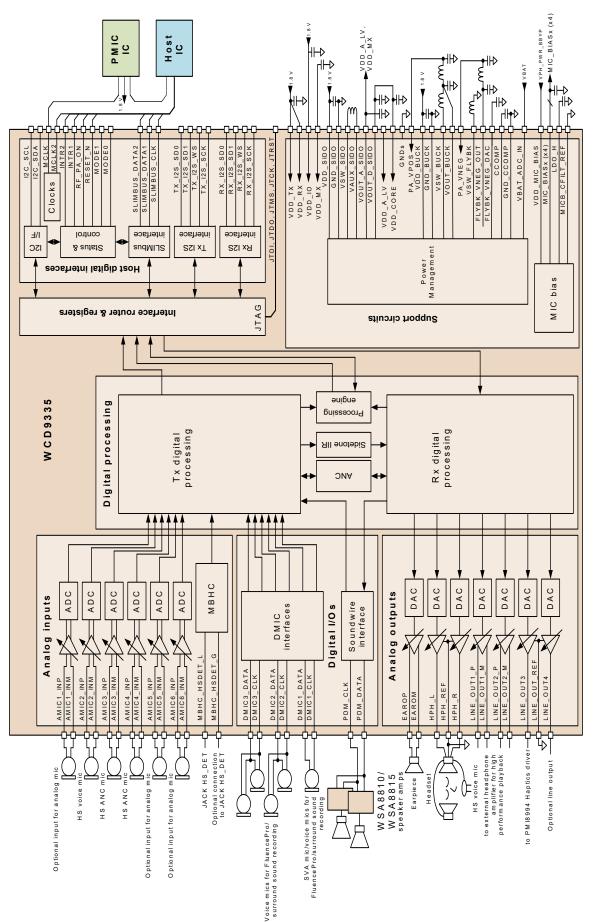

# 1.3 WCD9335 detailed functional block diagram

Figure 1-2 WCD9335 detailed functional block diagram

LM80-P2751-29 Rev. A

တ

### 1.4 Supply voltage summary

The following supplies are required:

- Primary phone power (VPH\_PWR)

- Regulated 1.8 V from power management

The on-chip circuits generate all other voltages required by the WCD9335.

### 1.5 Features

The features of the WCD9335 device are listed in Table 1-1.

Table 1-1 Summary of WCD9335 device features

| Feature                                      | WCD9335 capabilities                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System                                       |                                                                                                                                                                                                                                                                                                                                                                                             |

| Hi-fi audio                                  | <ul> <li>Recording path: 110 dB dynamic range and -103 dB THD + N</li> <li>Playback path: 130 dB dynamic range and -109 dB THD + N</li> </ul>                                                                                                                                                                                                                                               |

| Qualcomm Voice Activation subsystem          | <ul> <li>Microphone activity detection (MAD) to detect audio and beacon activity</li> <li>Codec processing engine (CPE) with 304 kB on-chip RAM</li> <li>Provides keyword detection and user identification in the codec with less than 0.85 mA power at battery (100% speech occupancy).</li> <li>Look-ahead buffer provides more consistent and coherent interaction to users.</li> </ul> |

| Digital I/Os                                 |                                                                                                                                                                                                                                                                                                                                                                                             |

| SLIMbus slave                                | <ul> <li>Two data lanes; 16 transmit (Tx) ports + 8 receive (Rx) ports + control</li> <li>Tx sample rates: 8, 16, 32, 48, 96, and 192 kHz</li> <li>Rx sample rates: 8, 16, 32, 44.1, 48, 96, 192, and 384 kHz</li> <li>Bit resolution: 12, 16, 20, 24, and 32</li> <li>Framer device to support framer handover to codec</li> </ul>                                                         |

| Two stereo master and slave I <sup>2</sup> S | <ul> <li>Isochronous mode</li> <li>Push/pull transport protocols</li> <li>Four Tx ports + four Rx ports</li> <li>Tx sample rates: 8, 16, 32, 48, 96, and 192 kHz</li> <li>Rx sample rates: 8, 16, 32, 44.1, 48, 96, and 192 kHz</li> <li>Bit resolution: 16 and 32</li> </ul>                                                                                                               |

| SoundWire interface to WSA8810/WSA8815       | ■ Multichannel, audio, and control use two lines (one clock and one data)                                                                                                                                                                                                                                                                                                                   |

| Digital microphone ports                     | ■ Six; three clock lines; nine supported frequencies from 600 kHz to 6.144 MHz                                                                                                                                                                                                                                                                                                              |

| Interrupts                                   | ■ Multiple hardware interrupts multiplexed behind two interrupt pads                                                                                                                                                                                                                                                                                                                        |

| Feature                   | WCD9335 capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Tx processing             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Analog audio input ports  | Six ports that support differential and single-ended configurations.  There are three operational modes:  Hi-fi  Programmable gain from 0–24 dB in 1.5 dB steps  0.9 µVrms input referred noise, 100 dB SNR, and -107 THD at 21 dB gain  Standard  Programmable gain from 0–30 dB in 1.5 dB steps  1.4 µVrms input referred noise, 96 dB SNR, and -102 THD at 21 dB gain  Ultra low power  Programmable gain from 0–30 dB in 1.5 dB steps  2.7 µVrms input referred noise, 90 dB SNR, and -95 THD at 21 dB gain  Capless inputs:  Input multiplexing allows routing any AMIC input to any decimator  Integrated IEC diodes on AMIC2_INP, AMIC3_INP, and AMIC4_INP |  |

| ADCs                      | ■ Six audio ADCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Concurrency               | ■ Nine concurrent Tx decimation paths to support voice and audio applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Digital controls          | <ul> <li>■ Gain: -84 dB to +40 dB in 0.5 dB increments</li> <li>■ DC blocking corner frequency: 4 Hz, 75 Hz, and 100 Hz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Decimation filters        | <ul> <li>Nine decimation filters for concurrent Tx paths</li> <li>Passband ripple: ± 0.005 dB</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Rx processing             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Analog audio output ports | <ul> <li>Seven – earpieces, stereo headphone, four line outputs (two differentials, two single-ended or four single-ended)</li> <li>Integrated IEC diodes on EAROP, EAROM, HPH_L, HPH_R, and HPH_REF pads</li> <li>Class-H differential earpiece output</li> <li>120 mW (typical) into 32 Ω; 150 mW (minimum) into 16 Ω or 10.67 Ω</li> <li>Class-H stereo single-ended headphone outputs; capless; 16 Ω or 32 Ω</li> <li>Two differentials and two single-ended line outputs</li> </ul>                                                                                                                                                                          |  |

| Digital audio to WSA      | ■ SoundWire interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| DACs                      | <ul> <li>Seven DACs and nine dedicated interpolators</li> <li>High-performance DACs for differential line outputs (to external headphone amplifiers)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Performance               | <ul> <li>■ Headphone: 1 Vrms; 122 dB dynamic range, -105 dB THD+N, and 16 µVpp click and pop in Class-H mode</li> <li>■ Line outputs: 2 Vrms; 130 dB dynamic range and -109 THD+N (differential)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Concurrency               | ■ Nine concurrent Rx paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Frequency response        | <ul> <li>High pass filter (HPF) cutoff of 0.48 Hz with 0.0025 dB droop at 20 Hz to meet Dolby requirements</li> <li>Nine interpolation filters with passband ripple of ±0.0025 dB (HPF disabled)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Mixing                    | <ul> <li>Digital mixing at the input of each DAC path</li> <li>Digital mixing on inputs to IIRs with independent gain control</li> <li>HD audio mixing path added to all interpolators</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Feature                       | WCD9335 capabilities                                                                                                                        |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Dynamic range enhancement     | ■ DRE provides Hi-Fi audio quality for headphone and line-output PAs                                                                        |

| Protection and suppression    | Overcurrent protection                                                                                                                      |

|                               | ■ Click-and-pop suppression                                                                                                                 |

| Multiple sample rates         | <ul> <li>Any path can use any of these sampling rates: 8, 16, 32, 44.1, 48, 96, 192, and<br/>384 kHz</li> </ul>                             |

| Concurrent PCM rates          | ■ Independent rates on each path to support voice and music concurrently                                                                    |

| Additional digital processing | and paths                                                                                                                                   |

| Active noise cancellation     | -                                                                                                                                           |

| Multibutton headset control   | Moisture detection                                                                                                                          |

| (MBHC)                        | <ul> <li>Mechanical plug insertion and removal detection on both tip and ground<br/>detection pad with pop noise reduction</li> </ul>       |

|                               | ■ Accessory plug type (3-pole, 4-pole - CTIA or OMTP, and 5-pole) detection                                                                 |

|                               | ■ Detection for up to eight buttons (send/end, volume, and play control)                                                                    |

|                               | ■ Headset impedance detection with ±5% from 3 $Ω$ up to 2 k $Ω$                                                                             |

| Sidetone paths and processing | All mixed channels operate at the same sample rate                                                                                          |

|                               | ■ No gain changes occur as a result of mixing channels                                                                                      |

|                               | ■ Five-stage IIR filters                                                                                                                    |

|                               | ■ Sample-rate converters                                                                                                                    |

|                               | ■ Echo cancellation (EC)                                                                                                                    |

| Clock circuits                | ■ Master clocks supported: 24.576, 19.2, 12.288, and 9.6 MHz (default)                                                                      |

| Support circuits              |                                                                                                                                             |

| Microphone biasing            | ■ Four voltage sources for powering analog and digital microphones                                                                          |

|                               | ■ Programmable from 1.0 V to 2.85 V                                                                                                         |

| SmartBoost                    | ■ Feedback signal to the companion WSA boost for efficient power control                                                                    |

| Feedback speaker protection   | <ul> <li>Receives I/V sense signals from companion WSA devices and transmits them to<br/>the audio processing in the APQ chipset</li> </ul> |

| Always-on power               | <ul> <li>Supports headset-insert/button-detect and Snapdragon Voice Activation while in<br/>low-power sleep mode</li> </ul>                 |

| Fabrication technology and p  | package                                                                                                                                     |

| Package                       | ■ Small, thermally efficient 113 FOWPSP; 4.17 × 3.91 × 0.65 mm; 0.35 mm pitch                                                               |

# 1.6 Terms and acronyms

Table 1-2 defines terms and acronyms commonly used throughout this document.

Table 1-2 Terms and acronyms

| Term or acronym | Definition                  |

|-----------------|-----------------------------|

| ADC             | Analog-to-digital converter |

| AMIC            | Analog microphone           |

| Term or acronym  | Definition                                            |

|------------------|-------------------------------------------------------|

| ВОМ              | Bill of materials                                     |

| BPF              | Band pass filter                                      |

| bps              | Bits per second                                       |

| CPE              | Codec processing engine                               |

| DAC              | Digital-to-analog converter                           |

| DMIC             | Digital microphone                                    |

| EC               | Echo cancellation                                     |

| ESD              | Electrostatic discharge                               |

| FOWPSP           | Fan out wafer-level picoscale package                 |

| FOWLP            | Fan out wafer level package                           |

| Hi-fi            | High fidelity                                         |

| HPF              | High pass filter                                      |

| HPH              | Headphone                                             |

| HR               | Hundred reel                                          |

| HV               | High voltage                                          |

| I <sup>2</sup> C | Interintegrated circuit                               |

| I <sup>2</sup> S | Inter-IC sound                                        |

| IEC              | International Electrotechnical Commission             |

| JTAG             | Joint Test Action Group (ANSI/ICEEE Std. 1149.1-1990) |

| LDO              | Low dropout (linear regulator)                        |

| LPF              | Low pass filter                                       |

| LV               | Low voltage                                           |

| MBHC             | Multibutton headset control                           |

| MGB              | Master bandgap (voltage reference)                    |

| MIC or mic       | Microphone                                            |

| MSL              | Moisture sensitivity level                            |

| NVM              | Nonvolatile memory                                    |

| OEM              | Original equipment manufacturer                       |

| OSR              | Oversampling ratio                                    |

| PA               | Power amplifier                                       |

| PCB              | Printed circuit board                                 |

| PDM              | Pulse density modulation                              |

| RoHS             | Restriction of hazardous substances                   |

| SIDO             | Single inductor dual output                           |

| SIMO             | Single inductor multiple outputs                      |

| SLIMbus          | Serial low-power interchip media bus                  |

| Term or acronym | Definition                                                                                              |

|-----------------|---------------------------------------------------------------------------------------------------------|

| SMPS            | Switched-mode power supply                                                                              |

| SMT             | Surface-mount technology                                                                                |

| SNR             | Signal-to-noise ratio                                                                                   |

| Sn/Ag/Cu        | Also known as SAC. Tin-silver-copper is a lead-free (Pb-free) alloy commonly used for electronic solder |

| SPKR            | Speaker                                                                                                 |

| SR              | Short reel                                                                                              |

| TR              | Tape and reel                                                                                           |

| WCD             | WSP codec device                                                                                        |

| WLP             | Wafer-level package                                                                                     |

| WSA             | WSP smart amplifier                                                                                     |

| WSP             | Wafer-scale package                                                                                     |

| XO              | Crystal oscillator                                                                                      |

# 2 Pad definitions

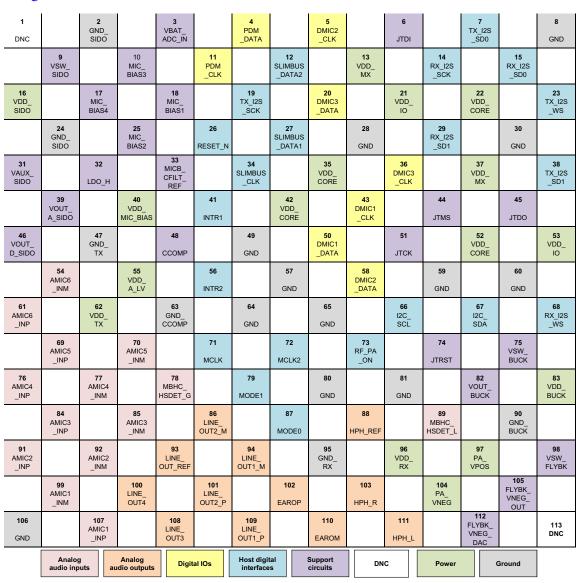

The WCD9335 is available in the 113 FOWPSP; a high-level view of its pad assignments is shown in Figure 2-1.

Figure 2-1 WCD9335 pad assignments (top view)

### 2.1 I/O parameter definitions

Table 2-1 I/O description (pad type) parameters

| Symbol                               | Description                           |  |

|--------------------------------------|---------------------------------------|--|

| Pad attribute                        |                                       |  |

| Al                                   | Analog input                          |  |

| AO                                   | Analog output                         |  |

| В                                    | Bidirectional digital with CMOS input |  |

| DI                                   | Digital input (CMOS)                  |  |

| DO                                   | Digital output (CMOS)                 |  |

| Z                                    | Z High-impedance (Hi-Z) output        |  |

| VDD_IO is used for digital I/O pads. |                                       |  |

### 2.2 Pad descriptions

Descriptions of all pads are presented in the following tables, organized by functional group:

| Table 2-2 | Analog inputs                             |

|-----------|-------------------------------------------|

| Table 2-3 | Analog outputs                            |

| Table 2-4 | Digital I/Os (other than host interfaces) |

| Table 2-5 | Host digital interfaces                   |

| Table 2-6 | Support circuits                          |

| Table 2-7 | Do not connect pads                       |

| Table 2-8 | Power supply pads                         |

| Table 2-9 | Ground pads                               |

Table 2-2 Pad descriptions – analog inputs

| Pad # | Pad name     | Pad type <sup>1</sup> | Functional description                                           |  |

|-------|--------------|-----------------------|------------------------------------------------------------------|--|

| 107   | AMIC1_INP    | Al                    | Analog microphone 1 input, differential plus                     |  |

| 99    | AMIC1_INM    | Al                    | nalog microphone 1 input, differential minus                     |  |

| 91    | AMIC2_INP    | Al                    | Analog microphone 2 input, differential plus                     |  |

| 92    | AMIC2_INM    | Al                    | Analog microphone 2 input, differential minus                    |  |

| 84    | AMIC3_INP    | Al                    | Analog microphone 3 input, differential plus                     |  |

| 85    | AMIC3_INM    | Al                    | Analog microphone 3 input, differential minus                    |  |

| 76    | AMIC4_INP    | Al                    | Analog microphone 4 input, differential plus                     |  |

| 77    | AMIC4_INM    | Al                    | Analog microphone 4 input, differential minus                    |  |

| 69    | AMIC5_INP    | Al                    | Analog microphone 5 input, differential plus                     |  |

| 70    | AMIC5_INM    | Al                    | Analog microphone 5 input, differential minus                    |  |

| 61    | AMIC6_INP    | Al                    | Analog microphone 6 input, differential plus                     |  |

| 54    | AMIC6_INM    | Al                    | Analog microphone 6 input, differential minus                    |  |

| 89    | MBHC_HSDET_L | Al                    | MBHC mechanical insertion/removal tip-detection pad              |  |

| 78    | MBHC_HSDET_G | Al                    | Secondary MBHC mechanical insertion/removal ground-detection pad |  |

<sup>1.</sup> See Table 2-1 for parameter and acronym definitions.

Table 2-3 Pad descriptions – analog outputs

| Pad # | Pad name     | Pad type <sup>1</sup> | Functional description                        |  |

|-------|--------------|-----------------------|-----------------------------------------------|--|

| 102   | EAROP        | AO                    | Earpiece amplifier output, differential plus  |  |

| 110   | EAROM        | AO                    | Earpiece amplifier output, differential minus |  |

| 111   | HPH_L        | AO                    | Headphone left output                         |  |

| 103   | HPH_R        | AO                    | Headphone right output                        |  |

| 88    | HPH_REF      | Al                    | Capless headphone ground reference of the PA  |  |

| 109   | LINE_OUT1_P  | AO                    | Audio line output 1, differential plus        |  |

| 94    | LINE_OUT1_M  | AO                    | Audio line output 1, differential minus       |  |

| 101   | LINE_OUT2_P  | AO                    | Audio line output 2, differential plus        |  |

| 86    | LINE_OUT2_M  | AO                    | Audio line output 2, differential minus       |  |

| 108   | LINE_OUT3    | AO                    | Audio line output 3, single-ended             |  |

| 100   | LINE_OUT4    | AO                    | Audio line output 4, single-ended             |  |

| 93    | LINE_OUT_REF | Al                    | Audio line outputs 3 and 4 ground reference   |  |

<sup>1.</sup> See Table 2-1 for parameter and acronym definitions.

Table 2-4 Pad descriptions – digital I/Os (other than host interfaces)

| Pad #     | Pad name                             | Pad type <sup>1</sup> | Functional description                                      |  |  |  |

|-----------|--------------------------------------|-----------------------|-------------------------------------------------------------|--|--|--|

| Digital m | Digital microphone (DMIC) interfaces |                       |                                                             |  |  |  |

| 50        | DMIC1_DATA                           | DI                    | Data for digital microphones 1 and 2                        |  |  |  |

| 43        | DMIC1_CLK                            | DO                    | Clock for digital microphones 1 and 2                       |  |  |  |

| 58        | DMIC2_DATA                           | DI                    | Data for digital microphones 3 and 4                        |  |  |  |

| 5         | DMIC2_CLK                            | DO                    | Clock for digital microphones 3 and 4                       |  |  |  |

| 20        | DMIC3_DATA                           | DI                    | Data for digital microphones 5 and 6                        |  |  |  |

| 36        | DMIC3_CLK                            | DO                    | Clock for digital microphones 5 and 6                       |  |  |  |

| SoundW    | ire port                             |                       |                                                             |  |  |  |

| 4         | PDM_DATA                             | В                     | SoundWire data for WSA8810/WSA8815 smart speaker amplifier  |  |  |  |

| 11        | PDM_CLK                              | DO                    | SoundWire clock for WSA8810/WSA8815 smart speaker amplifier |  |  |  |

<sup>1.</sup> See Table 2-1 for parameter and acronym definitions.

Table 2-5 Pad descriptions – host digital interfaces

| Pad #                  | Pad name                 | Pad type <sup>1</sup> | Functional description                            |  |

|------------------------|--------------------------|-----------------------|---------------------------------------------------|--|

| SLIMbus                | bidirectional audio      |                       |                                                   |  |

| 12                     | SLIMBUS_DATA2            | В                     | Bidirectional (Rx/Tx) SLIMbus data bit 2          |  |

| 27                     | SLIMBUS_DATA1            | В                     | Bidirectional (Rx/Tx) SLIMbus data bit 1          |  |

| 34                     | SLIMBUS_CLK              | В                     | Bidirectional (Rx/Tx) SLIMbus clock               |  |

| Interinte              | grated circuit (I2C) por | t                     |                                                   |  |

| 67                     | I2C_SDA                  | В                     | I <sup>2</sup> C serial data                      |  |

| 66                     | I2C_SCL                  | В                     | I <sup>2</sup> C serial clock                     |  |

| I <sup>2</sup> S bus - | - Rx direction           |                       |                                                   |  |

| 14                     | RX_I2S_SCK               | В                     | I <sup>2</sup> S bit clock, Rx direction          |  |

| 68                     | RX_I2S_WS                | В                     | I <sup>2</sup> S word select, Rx direction        |  |

| 29                     | RX_I2S_SD1               | DI                    | I <sup>2</sup> S serial data line 1, Rx direction |  |

| 15                     | RX_I2S_SD0               | DI                    | I <sup>2</sup> S serial data line 0, Rx direction |  |

| I <sup>2</sup> S bus - | Tx direction             |                       |                                                   |  |

| 19                     | TX_I2S_SCK               | В                     | I <sup>2</sup> S bit clock, Tx direction          |  |

| 23                     | TX_I2S_WS                | В                     | I <sup>2</sup> S word select, Tx direction        |  |

| 38                     | TX_I2S_SD1               | DO                    | I <sup>2</sup> S serial data line 1, Tx direction |  |

| 7                      | TX_I2S_SD0               | DO                    | I <sup>2</sup> S serial data line 0, Tx direction |  |

| Clock cir              | cuits                    |                       |                                                   |  |

| 71                     | MCLK                     | Al                    | Master clock input                                |  |

| 72                     | MCLK2                    | Al                    | Master clock input 2                              |  |

Table 2-5 Pad descriptions – host digital interfaces (cont.)

| Pad #                               | Pad name | Pad type <sup>1</sup> | Functional description                                               |  |

|-------------------------------------|----------|-----------------------|----------------------------------------------------------------------|--|

| Discrete status and control signals |          | nals                  |                                                                      |  |

| 26                                  | RESET_N  | DI                    | WCD9335 IC-level reset                                               |  |

| 73                                  | RF_PA_ON | DI                    | Indicates that GSM RF power amplifier is about to burst              |  |

| 41                                  | INTR1    | DO                    | Interrupt output 1                                                   |  |

| 56                                  | INTR2    | DO                    | Interrupt output 2                                                   |  |

| 87                                  | MODE0    | DI                    | Digital interface mode selection (SLIMbus or I <sup>2</sup> S) bit 0 |  |

| 79                                  | MODE1    | DI                    | Digital interface mode selection (SLIMbus or I <sup>2</sup> S) bit 1 |  |

<sup>1.</sup> See Table 2-1 for parameter and acronym definitions.

Table 2-6 Pad descriptions - support circuits

| Pad #     | Pad name                | Pad type 1 | Functional description                                    |

|-----------|-------------------------|------------|-----------------------------------------------------------|

| SIDO bu   | ck                      |            |                                                           |

| 9         | VSW_SIDO                | AI, AO     | SIDO buck switching node                                  |

| 31        | VAUX_SIDO               | AI, AO     | SIDO buck auxiliary voltage node                          |

| 39        | VOUT_A_SIDO             | AO         | SIDO output voltage for analog circuits                   |

| 46        | VOUT_D_SIDO             | AO         | SIDO output voltage for digital circuits                  |

| Buck SM   | IPS .                   |            |                                                           |

| 75        | VSW_BUCK                | AI, AO     | Buck SMPS switching node                                  |

| 82        | VOUT_BUCK               | AO         | Buck SMPS output node 1                                   |

| SIMO fly  | back                    |            |                                                           |

| 105       | FLYBK_VNEG_OUT          | AO         | Flyback SIMO negative output for PAs                      |

| 112       | FLYBK_VNEG_DAC          | AO         | Flyback SIMO negative output for DACs                     |

| 98        | VSW_FLYBK               | AI, AO     | Flyback SIMO switching node                               |

| Low-drop  | pout (LDO) linear regul | ator       |                                                           |

| 32        | LDO_H                   | AO         | Internal-circuitry LDO high-voltage output load capacitor |

| Micropho  | one bias voltage sourc  | es         |                                                           |

| 18        | MIC_BIAS1               | AO         | Microphone bias output voltage 1                          |

| 25        | MIC_BIAS2               | AO         | Microphone bias output voltage 2                          |

| 10        | MIC_BIAS3               | AO         | Microphone bias output voltage 3                          |

| 17        | MIC_BIAS4               | AO         | Microphone bias output voltage 4                          |

| 33        | MICB_CFILT_REF          | Al         | Microphone bias shared reference ground of the circuits   |

| Bandgap   | voltage reference dec   | oupling    |                                                           |

| 48        | CCOMP                   | AO         | Bandgap reference circuit compensation capacitor          |

| Battery v | oltage monitor          |            |                                                           |

| 3         | VBAT_ADC_IN             | Al         | Input to VBAT ADC                                         |

|           | 1                       | 1          | 1                                                         |

Table 2-6 Pad descriptions – support circuits (cont.)

| Pad #          | Pad name | Pad type <sup>1</sup> | Functional description |

|----------------|----------|-----------------------|------------------------|

| JTAG interface |          |                       |                        |

| 51             | JTCK     | DI                    | JTAG clock             |

| 6              | JTDI     | DI                    | JTAG data input        |

| 45             | JTDO     | DO                    | JTAG data output       |

| 44             | JTMS     | DI                    | JTAG mode select       |

| 74             | JTRST    | DI                    | JTAG reset             |

<sup>1.</sup> See Table 2-1 for parameter and acronym definitions.

Table 2-7 Pad descriptions – do not connect pads

| Pad #      | Pad name | e Functional description                                        |  |

|------------|----------|-----------------------------------------------------------------|--|

| 1, 113 DNC |          | Do not connect; connected internally, do not connect externally |  |

Table 2-8 Pad descriptions – power supply pads

| Pad #          | Pad name     | Functional description                         |

|----------------|--------------|------------------------------------------------|

| 104            | PA_VNEG      | Negative supply for PAs                        |

| 97             | PA_VPOS      | Positive supply for PAs                        |

| 55             | VDD_A_LV     | Power for analog low-voltage circuits          |

| 83             | VDD_BUCK     | Power for buck SMPS                            |

| 22, 35, 42, 52 | VDD_CORE     | Power for core digital circuits                |

| 13, 37         | VDD_MX       | Power for on-chip memory                       |

| 40             | VDD_MIC_BIAS | Power for the LDO and microphone bias circuits |

| 21, 53         | VDD_IO       | Power for digital I/O pads                     |

| 96             | VDD_RX       | Power for analog audio output (Rx) circuits    |

| 16             | VDD_SIDO     | Power for the SIDO buck                        |

| 62             | VDD_TX       | Power for analog audio input (Tx) circuits     |

Table 2-9 Pad descriptions – ground pads

| Pad #                                          | Pad name  | Functional description                      |

|------------------------------------------------|-----------|---------------------------------------------|

| 8, 28, 30, 49, 57, 59, 60, 64, 65, 80, 81, 106 | GND       | Ground                                      |

| 90                                             | GND_BUCK  | Ground for buck SMPS circuits               |

| 63                                             | GND_CCOMP | Ground for bandgap reference circuits       |

| 95                                             | GND_RX    | Ground for analog audio input (Rx) circuits |

| 2, 24                                          | GND_SIDO  | Ground for SIDO buck                        |

| 47                                             | GND_TX    | Ground for analog audio input (Tx) circuits |

# 3 Electrical specifications

### 3.1 Absolute maximum ratings

Absolute maximum ratings (Table 3-1) reflect the worst-case conditions that WCD9335 devices are exposed to during testing. They are limiting values to be considered individually when all other parameters are within their specified operating ranges. Functional operation and specification compliance at any absolute maximum condition, or after exposure to any of these conditions, are not guaranteed or implied. Exposure can shorten the life of the device.

Table 3-1 Absolute maximum ratings

| Parameter            | Description                                    | Minimum | Maximum | Units |

|----------------------|------------------------------------------------|---------|---------|-------|

| Power supply voltage | s                                              | "       |         |       |

| VDD_MIC_BIAS         | Power for the LDO and microphone bias circuits | -0.30   | 4.80    | V     |

| VDD_RX               | Power for analog audio output (Rx) circuits    | -0.30   | 2.16    | V     |

| VDD_TX               | Power for analog audio input (Tx) circuits     | -0.30   | 2.16    | V     |

| VDD_BUCK             | Power for buck SMPS                            | -0.30   | 2.16    | V     |

| VDD_SIDO             | Power for the SIDO buck                        | -0.30   | 2.16    | V     |

| VDD_IO               | Power for digital I/O pads                     | -0.30   | 2.16    | V     |

| VDD_A_LV             | Power for analog low-voltage circuits          | -0.30   | 1.30    | V     |

| VDD_MX               | Power for on-chip memory                       | -0.30   | 1.30    | V     |

| VDD_CORE             | Power for core digital circuits                | -0.30   | 1.30    | V     |

| Signal pads          |                                                |         | 1       |       |

| VIN_DIG              | Any digital input, nonpower                    | -0.30   | 2.15    | V     |

| VIN_ANA              | Any analog input, nonpower                     | -0.30   | 2.90    | V     |

| VBAT_ADC_IN          | Input to VBAT ADC                              | -0.30   | 4.80    | V     |

### 3.2 Operating conditions

Operating conditions include parameters that are under the control of the design team: power supply voltage, power distribution impedances, and thermal conditions (Table 3-2). The WCD9335 meets all performance specifications listed in Section through Section 3.7.6, when used within the operating conditions, unless otherwise noted in those sections (provided the absolute maximum ratings have never been exceeded).

Table 3-2 Operating conditions

| Parameter               | Description                                    | Minimum  | Тур  | Maximum | Units |

|-------------------------|------------------------------------------------|----------|------|---------|-------|

| Power supply voltage    | es                                             |          |      |         |       |

| VDD_MIC_BIAS            | Power for the LDO and microphone bias circuits | 3.15     | 3.80 | 4.60    | V     |

| VDD_RX                  | Power for analog audio output (Rx) circuits    | 1.70     | 1.80 | 1.90    | V     |

| VDD_TX                  | Power for analog audio input (Tx) circuits     | 1.70     | 1.80 | 1.90    | V     |

| VDD_BUCK                | Power for buck SMPS                            | 1.70     | 1.80 | 1.90    | V     |

| VDD_SIDO                | Power for the SIDO buck                        | 1.70     | 1.80 | 1.90    | V     |

| VDD_IO                  | Power for digital I/O pads                     | 1.70     | 1.80 | 1.90    | V     |

| Internally generated in | nput voltage                                   | 1        |      |         |       |

| VDD_A_LV                | Power for analog low-voltage circuits          | 1.0      | 1.10 | 1.21    | V     |

| VDD_MX                  | Power for on-chip memory                       | 1.0      | 1.10 | 1.21    | V     |

| VDD_CORE                | Power for core digital circuits                | 0.88     | 1.10 | 1.21    | V     |

| Signal pads             |                                                | 1        |      |         |       |

| VBAT_ADC_IN             | Input to VBAT ADC                              | 2.50     | 3.80 | 4.60    | V     |

| Thermal condition       |                                                | <u> </u> |      |         |       |

| Тс                      | Operating temperature (case)                   | -30      | _    | 85      | °C    |

### 3.3 DC power characteristics

### 3.3.1 Peak current

Table 3-3 Power supply peak current

| Parameter    | Conditions                                | Minimum | Тур | Maximum | Units |

|--------------|-------------------------------------------|---------|-----|---------|-------|

| VDD_MIC_BIAS | -                                         | _       | _   | 15      | mA    |

| VDD_RX       | -                                         | _       | -   | 25      | mA    |

| VDD_TX       | -                                         | -       | -   | 25      | mA    |

| VDD_BUCK     | -                                         | _       | _   | 650     | mA    |

| VDD_SIDO     | -                                         | -       | -   | 200     | mA    |

| VDD_IO       | Total for two pads                        | _       | _   | 10      | mA    |

| VDD_A_LV     | Included in VDD_SIDO                      | _       | _   | 15      | mA    |

| VDD_MX       | Included in VDD_SIDO, total for two pads  | _       | -   | 10      | mA    |

| VDD_CORE     | Included in VDD_SIDO, total for four pads | _       | _   | 40      | mA    |

### 3.4 Digital logic characteristics

Table 3-4 Digital I/O characteristics

|     | Parameter                 | Conditions | Minimum     | Тур | Maximum     | Units |

|-----|---------------------------|------------|-------------|-----|-------------|-------|

| VIH | High-level input voltage  | _          | 0.65 · VDDX | _   | 1.1 · VDDX  | V     |

| VIL | Low-level input voltage   | _          | 0           | _   | 0.35 · VDDX | V     |

| VOH | High-level output voltage | _          | 0.90 · VDDX | _   | VDDX        | V     |

| VOL | Low-level output voltage  | _          | 0           | _   | 0.10 · VDDX | V     |

| CIN | Digital input capacitance | _          | _           | _   | 5           | pF    |

### 3.5 Audio inputs and Tx processing

Unless otherwise stated:

- All Tx performance parameters are measured with 1.02 kHz sine wave input signal, differential or single-ended inputs, Fs = 48 kHz, 24-bit data, and MCLK = 9.6 MHz or 12.288 MHz.

- SNR is measured by taking the ratio of the output level with input signal level of 0 dBV and 1.02 kHz sine wave to the output level with inputs grounded over a bandwidth of 20 Hz–20 kHz.

### 3.5.1 Analog input through digital serial interface

Table 3-5 specifies the performance of the following Tx path: Any analog input  $\rightarrow$  pre-amp  $\rightarrow$  ADC  $\rightarrow$  digital serial interface.

**NOTE** Only hi-fi mode specification is listed. Lower power consumption modes are supported.

Table 3-5 Analog input through digital serial interface performance

| Parameter                       | Conditions                                                                                | Min | Тур  | Max | Units |  |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|--|--|--|

| Microphone amplifie             | Microphone amplifier gain = 0 dB (minimum gain)                                           |     |      |     |       |  |  |  |  |  |

| Input-referred noise            | A-weighted; inputs grounded; bandwidth 20 Hz–20 kHz                                       | _   | 3.3  | _   | μVrms |  |  |  |  |  |

| SNR                             | A-weighted                                                                                | _   | 109  | _   | dB    |  |  |  |  |  |

| THD + N ratio                   | Analog input = 0 dBV; bandwidth 20 Hz–20 kHz                                              | _   | -103 | _   | dB    |  |  |  |  |  |

|                                 | Analog input = -1 dBV; bandwidth 20 Hz–20 kHz                                             | -   | -98  | _   | dB    |  |  |  |  |  |

|                                 | Analog input = -60 dBV; bandwidth 20 Hz–20 kHz;<br>A-weighted                             | -   | -50  | _   | dB    |  |  |  |  |  |

| Microphone amplifie             | er gain = 21 dB (typical gain)                                                            |     |      |     |       |  |  |  |  |  |

| Input-referred noise            | A-weighted; inputs grounded; bandwidth 20 Hz–20 kHz                                       | _   | 0.9  | _   | μVrms |  |  |  |  |  |

| SNR                             | A-weighted                                                                                | -   | 100  | _   | dB    |  |  |  |  |  |

| THD + N ratio                   | Analog input = -21 dBV; bandwidth 20 Hz–20 kHz                                            | _   | -90  | _   | dB    |  |  |  |  |  |

|                                 | Analog input = -22 dBV; bandwidth 20 Hz–20 kHz                                            | -   | -90  | -   | dB    |  |  |  |  |  |

|                                 | Analog input = -81 dBV; bandwidth 20 Hz–20 kHz;<br>A-weighted                             | _   | -34  | -   | dB    |  |  |  |  |  |

| THD                             | Analog input = -22 dBV; bandwidth 20 Hz–20 kHz                                            | _   | -107 | _   | dB    |  |  |  |  |  |

| General requiremen              | ts                                                                                        |     |      |     |       |  |  |  |  |  |

| Absolute gain error             | Hi-fi mode                                                                                | _   | -0.1 | _   | dB    |  |  |  |  |  |

| Full scale input signal         | Measure differential input level that gives 0 dBFS output level; gain = 0 dB              | _   | 0.1  | -   | dBV   |  |  |  |  |  |

| Power supply rejection (VDD_TX) | 0 < f < 1 kHz; 100 mVpp sine wave imposed on the power supply; analog input = 0 Vrms      |     |      |     |       |  |  |  |  |  |

|                                 | Terminate inputs with 0 $\Omega$ ; gain = 0 dB                                            | _   | 113  | _   | dB    |  |  |  |  |  |

|                                 | 1 kHz < f < 5 kHz; 100 mVpp sine wave imposed on the power supply; analog input = 0 Vrms  |     |      |     |       |  |  |  |  |  |

|                                 | Terminate inputs with 0 $\Omega$ ; gain = 0 dB                                            | _   | 107  | _   | dB    |  |  |  |  |  |

|                                 | 5 kHz < f < 20 kHz; 100 mVpp sine wave imposed on the power supply; analog input = 0 Vrms |     |      |     |       |  |  |  |  |  |

|                                 | Terminate inputs with 0 Ω; gain = 0 dB                                                    | _   | 94   | _   | dB    |  |  |  |  |  |

| Input impedance                 | _                                                                                         | 1   | _    | _   | ΜΩ    |  |  |  |  |  |

| Input capacitance               | Analog pad                                                                                | _   | _    | 30  | pF    |  |  |  |  |  |

Table 3-5 Analog input through digital serial interface performance (cont.)

| Parameter                      | Conditions                                                                                                                                                                  | Min | Тур | Max | Units |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Rx-to-Tx crosstalk attenuation | Tx path measurement with -5 dBFS Rx path signal; separate Tx input and Rx output grounds                                                                                    | -   | 105 | _   | dB    |

| Interchannel isolation         | 20 < f < 20 kHz; one input terminated with 1 kΩ and the other input gets 1 kHz at -5 dBFS. Measure the digital output of the terminated channel; separate Tx inputs grounds | _   | 93  | -   | dB    |

### 3.5.2 DMIC input through digital serial interface

Table 3-6 specifies the performance of the following Tx path:

Any digital microphone input  $\rightarrow$  digital serial interface.

Table 3-6 Digital microphone input through digital serial interface performance

| Parameter                                                                                              | Conditions                                                                      | Minimum | Тур          | Maximum         | Units               |  |  |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------|--------------|-----------------|---------------------|--|--|--|

| Frequency response (from digital microphone input to SB/I <sup>2</sup> S PCM output, all sample rates) |                                                                                 |         |              |                 |                     |  |  |  |

| Frequency response                                                                                     | See Table 3-7 for the frequency respo<br>PCM output for all the sampling rates. |         | ital microph | one input to \$ | SB/I <sup>2</sup> S |  |  |  |

Table 3-6 Digital microphone input through digital serial interface performance (cont.)

| Parameter         | Conditions                                                                                                    | Minimum | Тур   | Maximum | Units |

|-------------------|---------------------------------------------------------------------------------------------------------------|---------|-------|---------|-------|

| Clock rate        | System clock = 9.6 MHz decimated output rates: 8 kHz, 16 kHz, 32 kHz, and 48 kHz                              | _       | 600   | -       | kHz   |

|                   | System clock = 9.6 MHz decimated output rates: 8 kHz, 16 kHz, 32 kHz, and 48 kHz                              | _       | 1.2   | _       | MHz   |

|                   | System clock = 9.6 MHz decimated output rates: 8 kHz, 16 kHz, 32 kHz, 48 kHz, 96 kHz, and 192 kHz             | _       | 2.4   | _       | MHz   |

|                   | System clock = 9.6 MHz decimated output rates: 8 kHz, 16 kHz, 32 kHz, 48 kHz, 96 kHz, and 192 kHz             | _       | 3.2   | -       | MHz   |

|                   | System clock = 9.6 MHz decimated output rates: 8 kHz, 16 kHz, 32 kHz, 48 kHz, 96 kHz, and 192 kHz             | _       | 4.8   | _       | MHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, and 48 kHz                     | _       | 768   | _       | kHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, and 48 kHz                     | _       | 1.536 | _       | MHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, 48 kHz, 96 kHz, and<br>192 kHz | _       | 2.048 | -       | MHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, 48 kHz, 96 kHz, and<br>192 kHz | _       | 3.072 | -       | MHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, 48 kHz, 96 kHz, and<br>192 kHz | -       | 4.096 | -       | MHz   |

|                   | System clock = 12.288 MHz<br>decimated output rates: 8 kHz,<br>16 kHz, 32 kHz, 48 kHz, 96 kHz, and<br>192 kHz | -       | 6.144 | _       | MHz   |

| Input capacitance | -                                                                                                             | _       | 1     | 5       | pF    |

| Board capacitance | _                                                                                                             | _       | 10    | 50      | pF    |

### 3.6 Audio outputs and Rx processing

Unless otherwise stated:

- All Rx performance parameters are measured with 1.02 kHz sine wave input signal, Fs = 48 kHz,

- 24-bit data and MCLK = 9.6 MHz or 12.288 MHz

- Receive noise is measured with no dither added to the input signal

### 3.6.1 Digital serial interface through earpiece analog output

Table 3-7 specifies the performance of the following Rx path: digital serial input  $\rightarrow$  mono DAC  $\rightarrow$  mono EAR output with 32  $\Omega$ , load unless otherwise specified.

Table 3-7 Serial interface through mono EAR output

| Parameter                     | Conditions                                                              | Minimum | Тур  | Maximum | Units |  |  |  |

|-------------------------------|-------------------------------------------------------------------------|---------|------|---------|-------|--|--|--|

| EAR output; 8/16 kHz; 16 bits |                                                                         |         |      |         |       |  |  |  |

| Receive noise                 | A-weighted; input = -999 dBFS, 6 dB gain mode                           | _       | 8.4  | _       | μVrms |  |  |  |

|                               | A-weighted; input = -999 dBFS, 0 dB gain mode                           | -       | 5    | _       | μVrms |  |  |  |

| SNR                           | Ratio of full-scale output to output noise level, A-weighted, 6 dB gain | _       | 107  | _       | dB    |  |  |  |

| THD + N ratio                 | PCMI = 0 dBFS, 20 Hz–20 kHz, 6 dB gain                                  | _       | -91  | _       | dB    |  |  |  |

|                               | PCMI = -1 dBFS, 20 Hz–20 kHz, 6 dB gain                                 | _       | -90  | _       | dB    |  |  |  |

|                               | PCMI = -60 dBFS, 20 Hz–20 kHz, 6 dB gain, A-weighted                    | -       | -38  | _       | dB    |  |  |  |

| EAR output; 48 kHz            | z; 16 bits                                                              |         |      |         |       |  |  |  |

| Receive noise                 | A-weighted; input = -999 dBFS, 6 dB gain mode                           | _       | 8.4  | _       | μVrms |  |  |  |

|                               | A-weighted; input = -999 dBFS, 0 dB gain mode                           | _       | 5    | -       | μVrms |  |  |  |

| SNR                           | Ratio of full-scale output to output noise level, A-weighted, 6 dB gain | _       | 107  | _       | dB    |  |  |  |

| THD + N ratio                 | PCMI = 0 dBFS, 20 Hz–20 kHz, 6 dB gain                                  | _       | -96  | _       | dB    |  |  |  |

|                               | PCMI = -1 dBFS, 20 Hz–20 kHz, 6 dB gain                                 | _       | -95  | _       | dB    |  |  |  |

|                               | PCMI = -60 dBFS, 20 Hz–20 kHz, 6 dB gain, A-weighted                    | _       | -40  | _       | dB    |  |  |  |

| Other characteristi           | cs                                                                      |         |      | 1       | I .   |  |  |  |

| Full-scale output             | Input = 0 dBFS, PA gain = 6 dB                                          | _       | 1.96 | _       | Vrms  |  |  |  |

| voltage                       | Input = 0 dBFS, PA gain = 0 dB                                          | _       | 0.99 | -       | Vrms  |  |  |  |