# **inter<sub>sil</sub>™**

## 82C55A

## CMOS Programmable Peripheral Interface

The Intersil 82C55A is a high performance CMOS version of the industry standard 8255A and is manufactured using a self-aligned silicon gate CMOS process (Scaled SAJI IV). It is a general purpose programmable I/O device which may be used with many different microprocessors. There are 24 I/O pins which may be individually programmed in 2 groups of 12 and used in 3 major modes of operation. The high performance and industry standard configuration of the 82C55A make it compatible with the 80C86, 80C88 and other microprocessors.

Static CMOS circuit design insures low operating power. TTL compatibility over the full military temperature range and bus hold circuitry eliminate the need for pull-up resistors. The Intersil advanced SAJI process results in performance equal to or greater than existing functionally equivalent products at a fraction of the power.

#### Features

- Pb-Free Plus Anneal Available (RoHS Compliant) (See Ordering Info)

- Pin Compatible with NMOS 8255A

- · 24 Programmable I/O Pins

- Fully TTL Compatible

- High Speed, No "Wait State" Operation with 5MHz and 8MHz 80C86 and 80C88

- · Direct Bit Set/Reset Capability

- · Enhanced Control Word Read Capability

- L7 Process

- 2.5mA Drive Capability on All I/O Ports

- Low Standby Power (ICCSB).....10μA

|                                                                                     | PART NU              | MBERS             |                 |                     |                      |             |

|-------------------------------------------------------------------------------------|----------------------|-------------------|-----------------|---------------------|----------------------|-------------|

| 5MHz                                                                                | PART<br>MARKING 8MHz |                   | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE              | PKG. DWG. # |

| CP82C55A-5<br>(No longer available,<br>recommended<br>replacement:<br>CP82C55A-5Z)  | CP82C55A-5           | CP82C55A          | CP82C55A        | 0 to +70            | 40 Ld PDIP           | E40.6       |

| CP82C55A-5Z (Note)                                                                  | CP82C55A-5Z          | CP82C55AZ (Note)  | CP82C55AZ       | 0 to +70            | 40 Ld PDIP (Pb-free) |             |

|                                                                                     |                      | IP82C55A          | IP82C55A        | -40 to +85          | 40 Ld PDIP           |             |

|                                                                                     |                      | IP82C55AZ (Note)  | IP82C55AZ       | -40 to +85          | 40 Ld PDIP (Pb-free) |             |

| CS82C55A-5*<br>(No longer available,<br>recommended<br>replacement:<br>CS82C55A-5Z) | CS82C55A-5           | CS82C55A*         | CS82C55A*       | 0 to +70            | 44 Ld PLCC           | N44.65      |

| CS82C55A-5Z* (Note)                                                                 | CS82C55A-5Z          | CS82C55AZ* (Note) | CS82C55AZ       | 0 to +70            | 44 Ld PLCC (Pb-free) |             |

| IS82C55A-5*                                                                         | IS82C55A-5           | IS82C55A*         | IS82C55A*       | -40 to +85          | 44 Ld PLCC           |             |

| IS82C55A-5Z* (Note)                                                                 | IS82C55A-5Z          | IS82C55AZ* (Note) | IS82C55AZ       | -40 to +85          | 44 Ld PLCC (Pb-free) |             |

|                                                                                     |                      | CQ82C55AZ (Note)  | CQ82C55AZ       | 0 to +70            | 44 Ld MQFP (Pb-free) | Q44.10x10   |

|                                                                                     |                      | IQ82C55AZ* (Note) | IQ82C55AZ       | -40 to +85          | 44 Ld MQFP (Pb-free) |             |

|                                                                                     |                      | ID82C55A          | ID82C55A        | -40 to +85          | 40 Ld CERDIP         | F40.6       |

|                                                                                     |                      | MD82C55A/B        | MD82C55A/B      | -55 to +125         |                      |             |

|                                                                                     |                      | 8406602QA         | 8406602QA       | SMD#                |                      |             |

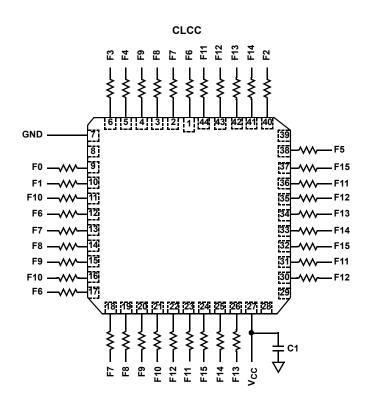

|                                                                                     |                      | 8406602XA         | 8406602XA       | SMD#                | 44 Ld CLCC           | J44.A       |

Ordering Information

\*Add "96" suffix to part number for tape and reel packaging.

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

FN2969 Rev 11.00 Dec 8, 2015

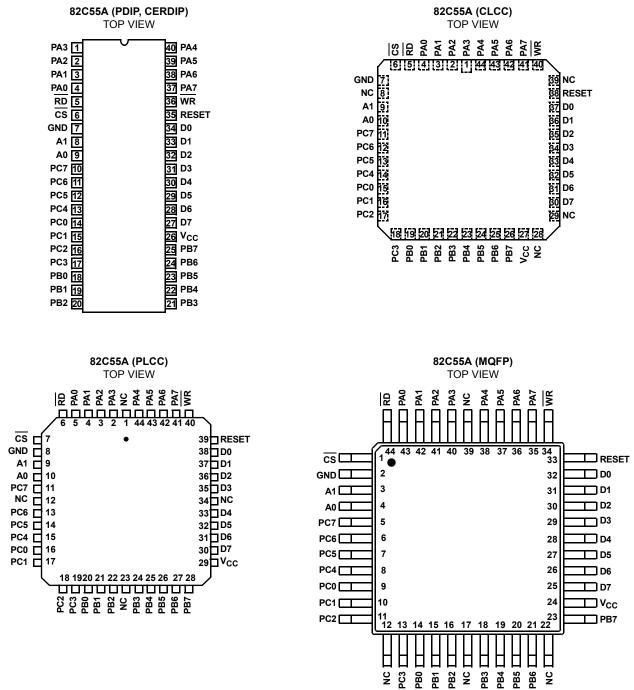

## Pinouts

| Pin Descrip | tion |

|-------------|------|

|-------------|------|

| SYMBOL          | TYPE | DESCRIPTION                                                                                                                                                                                                                                                               |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> |      | $V_{CC}$ : The +5V power supply pin. A 0.1 $\mu F$ capacitor between $V_{CC}$ and GND is recommended for decoupling.                                                                                                                                                      |

| GND             |      | GROUND                                                                                                                                                                                                                                                                    |

| D0-D7           | I/O  | DATA BUS: The Data Bus lines are bidirectional three-state pins connected to the system data bus.                                                                                                                                                                         |

| RESET           | I    | RESET: A high on this input clears the control register and all ports (A, B, C) are set to the input mode with the "Bus Hold" circuitry turned on.                                                                                                                        |

| CS              | I    | CHIP SELECT: Chip select is an active low input used to enable the 82C55A onto the Data Bus for CPU communications.                                                                                                                                                       |

| RD              | I    | READ: Read is an active low input control signal used by the CPU to read status information or data via the data bus.                                                                                                                                                     |

| WR              | I    | WRITE: Write is an active low input control signal used by the CPU to load control words and data into the 82C55A.                                                                                                                                                        |

| A0-A1           | I    | ADDRESS: These input signals, in conjunction with the $\overline{RD}$ and $\overline{WR}$ inputs, control the selection of one of the three ports or the control word register. A0 and A1 are normally connected to the least significant bits of the Address Bus A0, A1. |

| PA0-PA7         | I/O  | PORT A: 8-bit input and output port. Both bus hold high and bus hold low circuitry are present on this port.                                                                                                                                                              |

| PB0-PB7         | I/O  | PORT B: 8-bit input and output port. Bus hold high circuitry is present on this port.                                                                                                                                                                                     |

| PC0-PC7         | I/O  | PORT C: 8-bit input and output port. Bus hold circuitry is present on this port.                                                                                                                                                                                          |

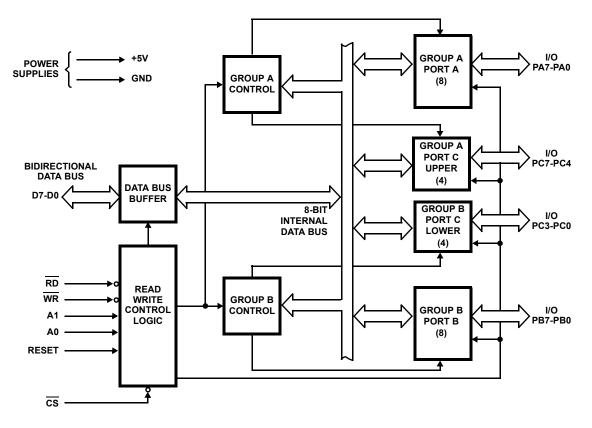

## Functional Diagram

## Functional Description

#### Data Bus Buffer

This three-state bidirectional 8-bit buffer is used to interface the 82C55A to the system data bus. Data is transmitted or received by the buffer upon execution of input or output instructions by the CPU. Control words and status information are also transferred through the data bus buffer.

#### Read/Write and Control Logic

The function of this block is to manage all of the internal and external transfers of both Data and Control or Status words. It accepts inputs from the CPU Address and Control busses and in turn, issues commands to both of the Control Groups.

(CS) Chip Select. A "low" on this input pin enables the communication between the 82C55A and the CPU.

**(RD)** Read. A "low" on this input pin enables 82C55A to send the data or status information to the CPU on the data bus. In essence, it allows the CPU to "read from" the 82C55A.

(WR) Write. A "low" on this input pin enables the CPU to write data or control words into the 82C55A.

(A0 and A1) Port Select 0 and Port Select 1. These input signals, in conjunction with the RD and WR inputs, control the selection of one of the three ports or the control word register. They are normally connected to the least significant bits of the address bus (A0 and A1).

| A1 | A0 | RD | WR | cs | INPUT OPERATION<br>(READ)           |

|----|----|----|----|----|-------------------------------------|

| 0  | 0  | 0  | 1  | 0  | Port A $\rightarrow$ Data Bus       |

| 0  | 1  | 0  | 1  | 0  | Port B $\rightarrow$ Data Bus       |

| 1  | 0  | 0  | 1  | 0  | Port C $\rightarrow$ Data Bus       |

| 1  | 1  | 0  | 1  | 0  | Control Word $\rightarrow$ Data Bus |

|    |    |    |    |    | OUTPUT OPERATION<br>(WRITE)         |

| 0  | 0  | 1  | 0  | 0  | Data Bus $\rightarrow$ Port A       |

| 0  | 1  | 1  | 0  | 0  | Data Bus $\rightarrow$ Port B       |

| 1  | 0  | 1  | 0  | 0  | Data Bus $\rightarrow$ Port C       |

| 1  | 1  | 1  | 0  | 0  | Data Bus $\rightarrow$ Control      |

|    |    |    |    |    | DISABLE FUNCTION                    |

| Х  | Х  | Х  | Х  | 1  | Data Bus $\rightarrow$ Three-State  |

| Х  | х  | 1  | 1  | 0  | Data Bus $\rightarrow$ Three-State  |

82C55A BASIC OPERATION

(**RESET**) Reset. A "high" on this input initializes the control register to 9Bh and all ports (A, B, C) are set to the input mode. "Bus hold" devices internal to the 82C55A will hold the I/O port inputs to a logic "1" state with a maximum hold current of  $400\mu$ A.

#### FIGURE 1. 82C55A BLOCK DIAGRAM. DATA BUS BUFFER, READ/WRITE, GROUP A & B CONTROL LOGIC FUNCTIONS

#### Group A and Group B Controls

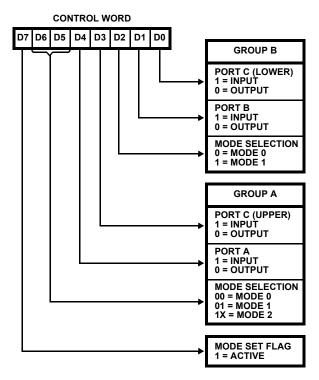

The functional configuration of each port is programmed by the systems software. In essence, the CPU "outputs" a control word to the 82C55A. The control word contains information such as "mode", "bit set", "bit reset", etc., that initializes the functional configuration of the 82C55A.

Each of the Control blocks (Group A and Group B) accepts "commands" from the Read/Write Control logic, receives "control words" from the internal data bus and issues the proper commands to its associated ports.

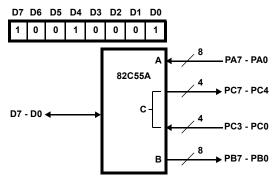

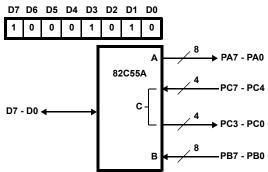

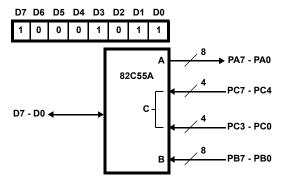

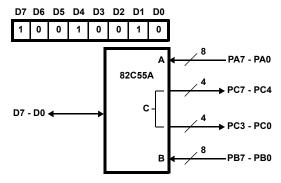

Control Group A - Port A and Port C upper (C7 - C4)

Control Group B - Port B and Port C lower (C3 - C0)

The control word register can be both written and read as shown in the "Basic Operation" table. Figure 4 shows the control word format for both Read and Write operations. When the control word is read, bit D7 will always be a logic "1", as this implies control word mode information.

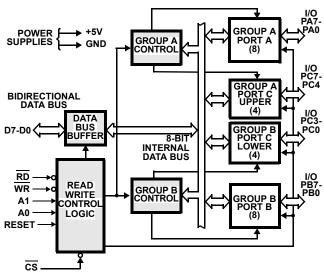

## Ports A, B, and C

The 82C55A contains three 8-bit ports (A, B, and C). All can be configured to a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 82C55A.

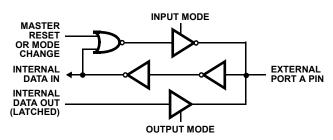

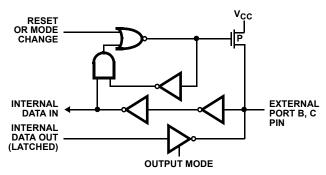

**Port A** One 8-bit data output latch/buffer and one 8-bit data input latch. Both "pull-up" and "pull-down" bus-hold devices are present on Port A. See Figure 2A.

**Port B** One 8-bit data input/output latch/buffer and one 8-bit data input buffer. See Figure 2B.

**Port C** One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input). This port can be divided into

two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal output and status signal inputs in conjunction with ports A and B. See Figure 2B.

FIGURE 2A. PORT A BUS-HOLD CONFIGURATION

FIGURE 2B. PORT B AND C BUS-HOLD CONFIGURATION

FIGURE 2. BUS-HOLD CONFIGURATION

## **Operational Description**

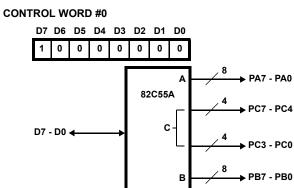

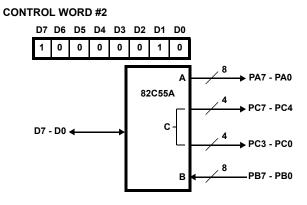

#### Mode Selection

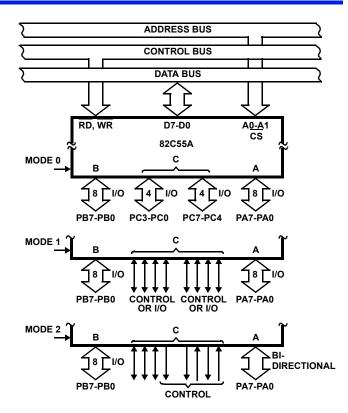

There are three basic modes of operation than can be selected by the system software:

- Mode 0 Basic Input/Output

- Mode 1 Strobed Input/Output

- Mode 2 Bidirectional Bus

When the reset input goes "high", all ports will be set to the input mode with all 24 port lines held at a logic "one" level by internal bus hold devices. After the reset is removed, the 82C55A can remain in the input mode with no additional initialization required. This eliminates the need to pull-up or pull-down resistors in all-CMOS designs. The control word register will contain 9Bh. During the execution of the system program, any of the other modes may be selected using a single output instruction. This allows a single 82C55A to service a variety of peripheral devices with a simple software maintenance routine. Any port programmed as an output port is initialized to all zeros when the control word is written.

FIGURE 3. BASIC MODE DEFINITIONS AND BUS INTERFACE

The modes for Port A and Port B can be separately defined, while Port C is divided into two portions as required by the Port A and Port B definitions. All of the output registers, including the status flip-flops, will be reset whenever the mode is changed. Modes may be combined so that their functional definition can be "tailored" to almost any I/O structure. For instance: Group B can be programmed in Mode 0 to monitor simple switch closings or display computational results, Group A could be programmed in Mode 1 to monitor a keyboard or tape reader on an interrupt-driven basis.

The mode definitions and possible mode combinations may seem confusing at first, but after a cursory review of the complete device operation a simple, logical I/O approach will surface. The design of the 82C55A has taken into account things such as efficient PC board layout, control signal definition vs. PC layout and complete functional flexibility to support almost any peripheral device with no external logic. Such design represents the maximum use of the available pins.

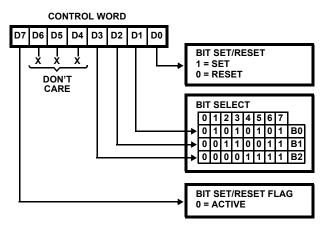

## Single Bit Set/Reset Feature (Figure 5)

Any of the eight bits of Port C can be Set or Reset using a single Output instruction. This feature reduces software requirements in control-based applications.

When Port C is being used as status/control for Port A or B, these bits can be set or reset by using the Bit Set/Reset operation just as if they were output ports.

FIGURE 5. BIT SET/RESET FORMAT

#### Interrupt Control Functions

When the 82C55A is programmed to operate in mode 1 or mode 2, control signals are provided that can be used as interrupt request inputs to the CPU. The interrupt request signals, generated from port C, can be inhibited or enabled by setting or resetting the associated INTE flip-flop, using the bit set/reset function of port C.

This function allows the programmer to enable or disable a CPU interrupt by a specific I/O device without affecting any other device in the interrupt structure.

#### INTE Flip-Flop Definition

(BIT-SET)-INTE is SET - Interrupt Enable

(BIT-RESET)-INTE is Reset - Interrupt Disable

NOTE: All Mask flip-flops are automatically reset during mode selection and device Reset.

## **Operating Modes**

**Mode 0** (Basic Input/Output). This functional configuration provides simple input and output operations for each of the three ports. No handshaking is required, data is simply written to or read from a specific port.

Mode 0 Basic Functional Definitions:

- Two 8-bit ports and two 4-bit ports

- · Any Port can be input or output

- · Outputs are latched

- · Inputs are not latched

- 16 different Input/Output configurations possible

| A B |    | GRO | UP A |        | GROUP B          |    |        |                  |

|-----|----|-----|------|--------|------------------|----|--------|------------------|

| D4  | D3 | D1  | D0   | PORT A | PORTC<br>(Upper) | #  | PORT B | PORTC<br>(Lower) |

| 0   | 0  | 0   | 0    | Output | Output           | 0  | Output | Output           |

| 0   | 0  | 0   | 1    | Output | Output           | 1  | Output | Input            |

| 0   | 0  | 1   | 0    | Output | Output           | 2  | Input  | Output           |

| 0   | 0  | 1   | 1    | Output | Output           | 3  | Input  | Input            |

| 0   | 1  | 0   | 0    | Output | Input            | 4  | Output | Output           |

| 0   | 1  | 0   | 1    | Output | Input            | 5  | Output | Input            |

| 0   | 1  | 1   | 0    | Output | Input            | 6  | Input  | Output           |

| 0   | 1  | 1   | 1    | Output | Input            | 7  | Input  | Input            |

| 1   | 0  | 0   | 0    | Input  | Output           | 8  | Output | Output           |

| 1   | 0  | 0   | 1    | Input  | Output           | 9  | Output | Input            |

| 1   | 0  | 1   | 0    | Input  | Output           | 10 | Input  | Output           |

| 1   | 0  | 1   | 1    | Input  | Output           | 11 | Input  | Input            |

| 1   | 1  | 0   | 0    | Input  | Input            | 12 | Output | Output           |

| 1   | 1  | 0   | 1    | Input  | Input            | 13 | Output | Input            |

| 1   | 1  | 1   | 0    | Input  | Input            | 14 | Input  | Output           |

| 1   | 1  | 1   | 1    | Input  | Input            | 15 | Input  | Input            |

#### MODE 0 PORT DEFINITION

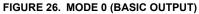

#### Mode 0 (Basic Input)

## Mode 0 (Basic Output)

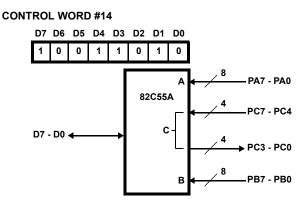

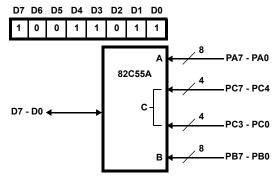

#### Mode 0 Configurations

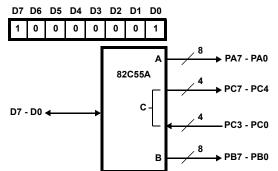

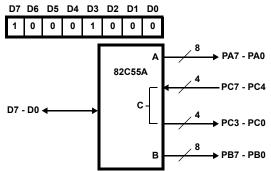

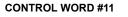

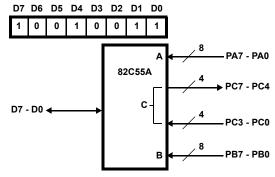

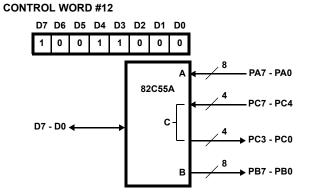

CONTROL WORD #1

**intersi**[

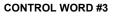

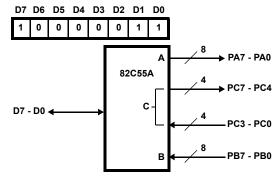

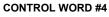

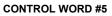

## Mode 0 Configurations (Continued)

CONTROL WORD #9

CONTROL WORD #6

CONTROL WORD #7

CONTROL WORD #10

intersil

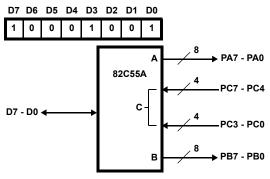

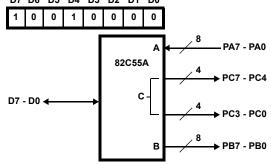

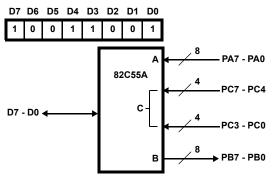

#### Mode 0 Configurations (Continued)

#### CONTROL WORD #13

#### CONTROL WORD #15

## **Operating Modes**

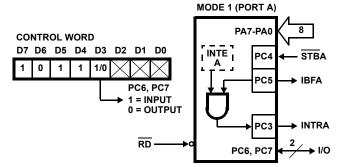

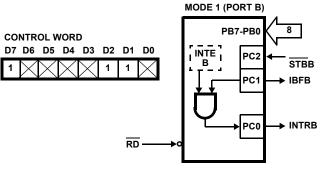

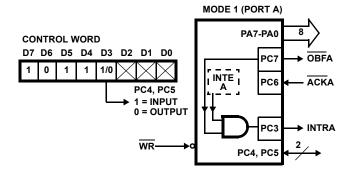

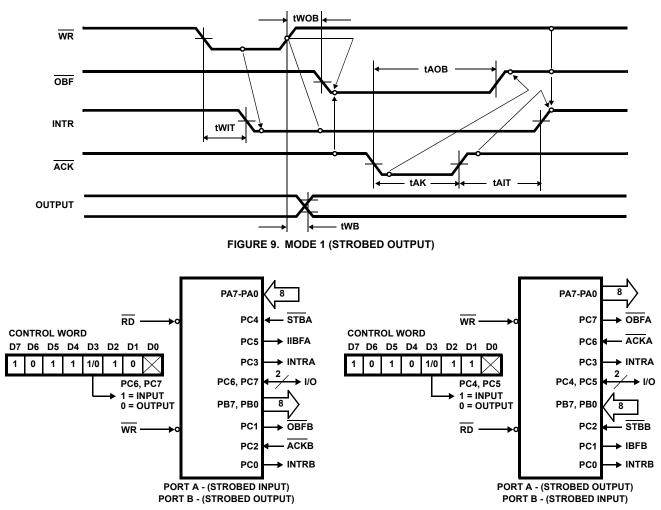

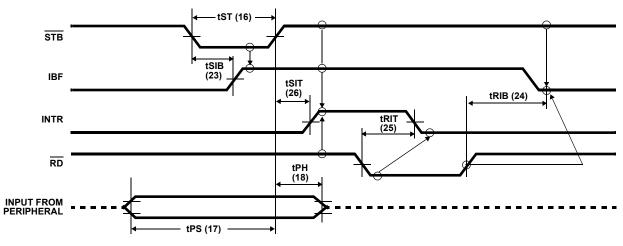

**Mode 1** - (Strobed Input/Output). This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or "hand shaking" signals. In mode 1, port A and port B use the lines on port C to generate or accept these "hand shaking" signals.

Mode 1 Basic Function Definitions:

- Two Groups (Group A and Group B)

- Each group contains one 8-bit port and one 4-bit control/data

port

- The 8-bit data port can be either input or output. Both inputs and outputs are latched.

- The 4-bit port is used for control and status of the 8-bit port.

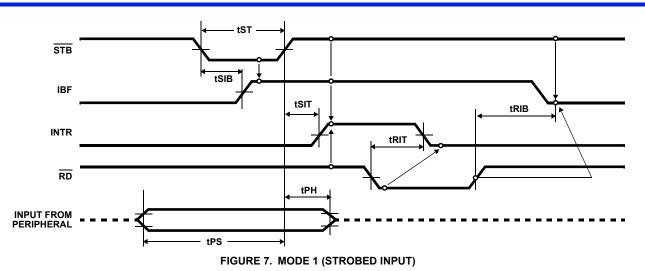

## Input Control Signal Definition

(Figures 6 and 7)

## STB (Strobe Input)

A "low" on this input loads data into the input latch.

## IBF (Input Buffer Full F/F)

A "high" on this output indicates that the data has been loaded into the input latch: in essence, an acknowledgment. IBF is set by  $\overline{\text{STB}}$  input being low and is reset by the rising edge of the  $\overline{\text{RD}}$  input.

FIGURE 6. MODE 1 INPUT

#### INTR (Interrupt Request)

A "high" on this output can be used to interrupt the CPU when an input device is requesting service. INTR is set by the condition: STB is a "one", IBF is a "one" and INTE is a "one". It is reset by the falling edge of RD. This procedure allows an input device to request service from the CPU by simply strobing its data into the port.

#### INTE A

Controlled by bit set/reset of PC4.

#### INTE B

Controlled by bit set/reset of PC2.

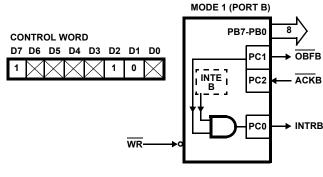

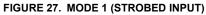

#### **Output Control Signal Definition**

(Figure 8 and 9)

**OBF** - (Output Buffer Full F/F). The  $\overline{\text{OBF}}$  output will go "low" to indicate that the CPU has written data out to the specified port. This does not mean valid data is sent out of the port at this time since  $\overline{\text{OBF}}$  can go true before data is available. Data is guaranteed valid at the rising edge of  $\overline{\text{OBF}}$ , (See Note 1). The  $\overline{\text{OBF}}$  F/F will be set by the rising edge of the  $\overline{\text{WR}}$  input and reset by  $\overline{\text{ACK}}$  input being low.

**ACK** - (Acknowledge Input). A "low" on this input informs the 82C55A that the data from Port A or Port B is ready to be accepted. In essence, a response from the peripheral device indicating that it is ready to accept data, (See Note 1).

**INTR** - (Interrupt Request). A "high" on this output can be used to interrupt the CPU when an output device has accepted data transmitted by the CPU. INTR is set when  $\overrightarrow{ACK}$  is a "one",  $\overrightarrow{OBF}$  is a "one" and INTE is a "one". It is reset by the falling edge of  $\overrightarrow{WR}$ .

#### INTE A

Controlled by Bit Set/Reset of PC6.

#### INTE B

Controlled by Bit Set/Reset of PC2.

NOTE:

To strobe data into the peripheral device, the user must operate the strobe line in a hand shaking mode. The user needs to send OBF to the peripheral device, generates an ACK from the peripheral device and then latch data into the peripheral device on the rising edge of OBF.

FIGURE 8. MODE 1 OUTPUT

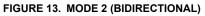

Combinations of Mode 1: Port A and Port B can be individually defined as input or output in Mode 1 to support a wide variety of strobed I/O applications. FIGURE 10. COMBINATIONS OF MODE 1

## **Operating Modes**

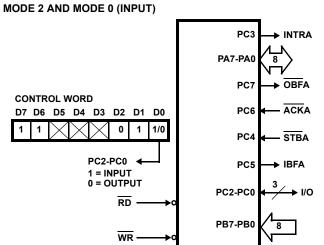

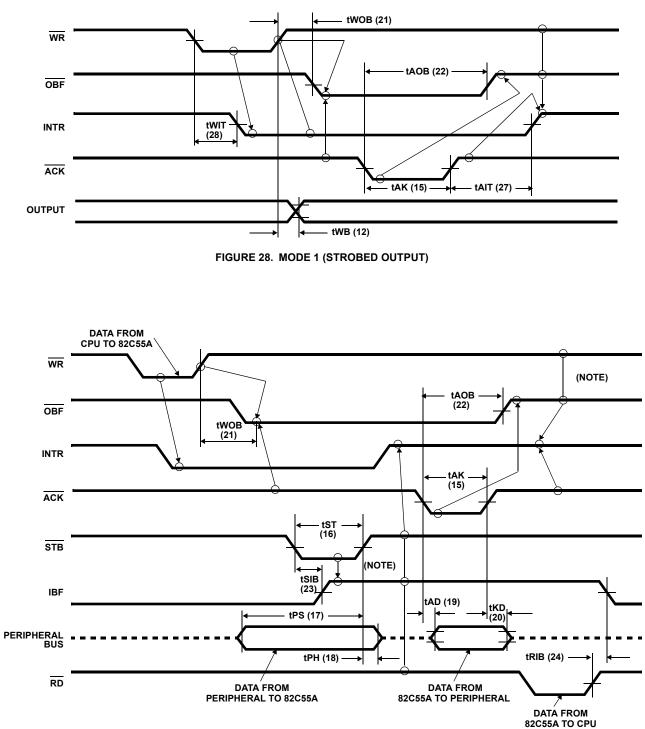

## Mode 2 (Strobed Bidirectional Bus I/O)

This functional configuration provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data (bidirectional bus I/O). "Hand shaking" signals are provided to maintain proper bus flow discipline similar to Mode 1. Interrupt generation and enable/disable functions are also available.

Mode 2 Basic Functional Definitions:

- · Used in Group A only

- One 8-bit, bidirectional bus Port (Port A) and a 5-bit control Port (Port C)

- · Both inputs and outputs are latched

- The 5-bit control port (Port C) is used for control and status for the 8-bit, bidirectional bus port (Port A)

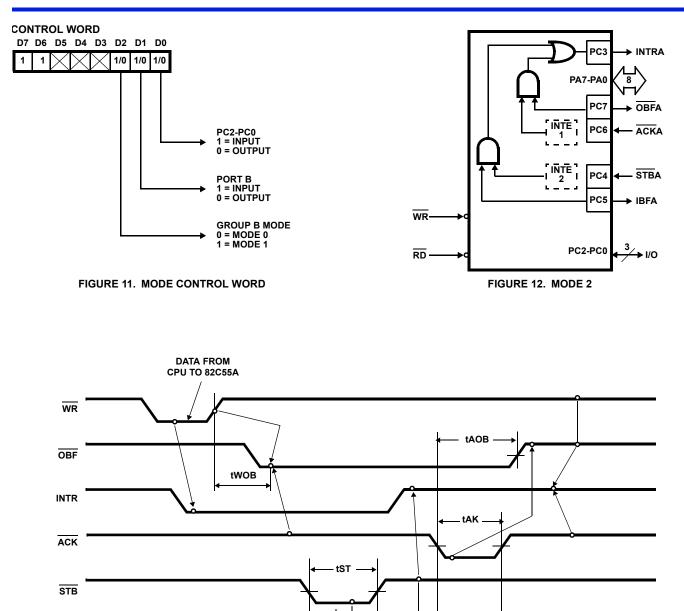

## Bidirectional Bus I/O Control Signal Definition

(Figures 11, 12, 13, 14)

**INTR** - (Interrupt Request). A high on this output can be used to interrupt the CPU for both input or output operations.

## **Output Operations**

**OBF** - (Output Buffer Full). The OBF output will go "low" to indicate that the CPU has written data out to port A.

**ACK** - (Acknowledge). A "low" on this input enables the threestate output buffer of port A to send out the data. Otherwise, the output buffer will be in the high impedance state.

**INTE 1** - (The INTE flip-flop associated with  $\overline{OBF}$ ). Controlled by bit set/reset of PC4.

#### Input Operations

**STB** - (Strobe Input). A "low" on this input loads data into the input latch.

**IBF** - (Input Buffer Full F/F). A "high" on this output indicates that data has been loaded into the input latch.

**INTE 2** - (The INTE flip-flop associated with IBF). Controlled by bit set/reset of PC4.

tPH

tAD

DATA FROM

82C55A TO PERIPHERAL

tKD

tRIB

DATA FROM 82C55A TO CPU

tSIB

tPS

DATA FROM

PERIPHERAL TO 82C55A

IBF

RD

PERIPHERAL BUS

intersil

INTRA

• OBFA

- ACKA

- STBA

IBFA

STBB

→ IBFB

INTRB

8

8

**FIGURE 14. MODE 2 COMBINATIONS**

|                   |                | MODE              | DEFINITION SUMM       | ARY                  |                                                  |                    |

|-------------------|----------------|-------------------|-----------------------|----------------------|--------------------------------------------------|--------------------|

|                   | MOI            | DE 0              | MO                    | DE 1                 | MODE 2                                           |                    |

|                   | IN             | OUT               | IN                    | OUT                  | GROUP A ONLY                                     | -                  |

| PA0<br>PA1        | ln<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           | $\underset{\longleftarrow}{\longleftrightarrow}$ |                    |

| PA2<br>PA3        | ln<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           | $\stackrel{\longleftarrow}{\longleftarrow}$      |                    |

| PA4<br>PA5        | In<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           | $\stackrel{\longleftarrow}{\longleftarrow}$      |                    |

| PA6<br>PA7        | In<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           | $\stackrel{\longleftarrow}{\longleftarrow}$      |                    |

| PB0<br>PB1        | In<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           |                                                  | <b>ן</b>           |

| PB2<br>PB3        | In<br>In       | Out<br>Out        | In<br>In              | Out                  |                                                  | Mode 0             |

| PB4<br>PB5        | In<br>In       | Out               | In<br>In              | Out<br>Out           |                                                  | ≻or Mode 1<br>Only |

| PB6<br>PB7        | In<br>In       | Out<br>Out        | In<br>In              | Out<br>Out           |                                                  |                    |

| PC0<br>PC1        | In<br>In       | Out<br>Out        | INTRB<br>IBFB         | INTRB<br>OBFB        | I/O<br>I/O                                       |                    |

| PC2<br>PC3<br>PC4 | In<br>In<br>In | Out<br>Out<br>Out | STBB<br>INTRA<br>STBA | ACKB<br>INTRA<br>I/O | I/O<br>INTRA<br>STBA                             |                    |

| PC4<br>PC5<br>PC6 | In<br>In       | Out<br>Out        | IBFA<br>I/O           | 1/0<br>ACKA          | IBFA<br>ACKA                                     |                    |

| PC7               | In             | Out               | I/O                   | OBFA                 | OBFA                                             |                    |

#### Special Mode Combination Considerations

There are several combinations of modes possible. For any combination, some or all of Port C lines are used for control or status. The remaining bits are either inputs or outputs as defined by a "Set Mode" command.

During a read of Port C, the state of all the Port C lines, except the  $\overrightarrow{ACK}$  and  $\overrightarrow{STB}$  lines, will be placed on the data bus. In place of the  $\overrightarrow{ACK}$  and  $\overrightarrow{STB}$  line states, flag status will appear on the data bus in the PC2, PC4, and PC6 bit positions as illustrated by Figure 17.

Through a "Write Port C" command, only the Port C pins programmed as outputs in a Mode 0 group can be written. No other pins can be affected by a "Write Port C" command, nor can the interrupt enable flags be accessed. To write to any Port C output programmed as an output in Mode 1 group or to change an interrupt enable flag, the "Set/Reset Port C Bit" command must be used.

With a "Set/Reset Port C Bit" command, any Port C line programmed as an output (including IBF and OBF) can be written, or an interrupt enable flag can be either set or reset. Port C lines programmed as inputs, including ACK and STB lines, associated with Port C are not affected by a "Set/Reset Port C Bit" command. Writing to the corresponding Port C bit positions of the ACK and STB lines with the "Set Reset Port C Bit" command will affect the Group A and Group B interrupt enable flags, as illustrated in Figure 17.

## Current Drive Capability

Any output on Port A, B or C can sink or source 2.5mA. This feature allows the 82C55A to directly drive Darlington type drivers and high-voltage displays that require such sink or source current.

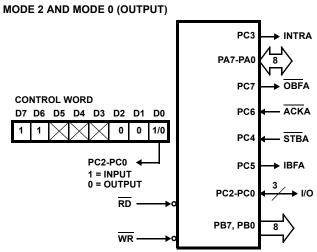

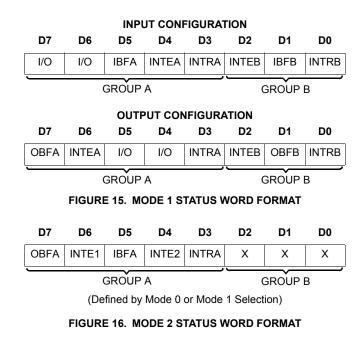

#### Reading Port C Status (Figures 15 and 16)

In Mode 0, Port C transfers data to or from the peripheral device. When the 82C55A is programmed to function in Modes

1 or 2, Port C generates or accepts "hand shaking" signals with the peripheral device. Reading the contents of Port C allows the programmer to test or verify the "status" of each peripheral device and change the program flow accordingly.

There is not a special instruction to read the status information from Port C. A normal read operation of Port C is executed to perform this function.

| INTERRUPT<br>ENABLE FLAG | POSITION | ALTERNATE PORT C<br>PIN SIGNAL (MODE)          |

|--------------------------|----------|------------------------------------------------|

| INTE B                   | PC2      | ACKB (Output Mode 1)<br>or STBB (Input Mode 1) |

| INTE A2                  | PC4      | STBA (Input Mode 1 or Mode 2)                  |

| INTE A1                  | PC6      | ACKA (Output Mode 1 or<br>Mode 2)              |

FIGURE 17. INTERRUPT ENABLE FLAGS IN MODES 1 AND 2

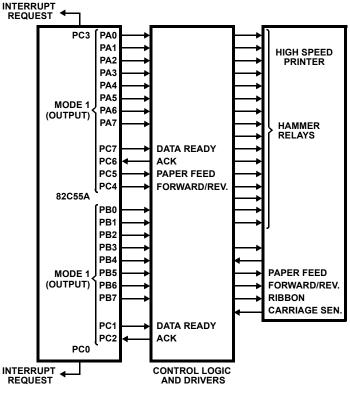

## Applications of the 82C55A

The 82C55A is a very powerful tool for interfacing peripheral equipment to the microcomputer system. It represents the optimum use of available pins and is flexible enough to interface almost any I/O device without the need for additional external logic.

Each peripheral device in a microcomputer system usually has a "service routine" associated with it. The routine manages the software interface between the device and the CPU. The functional definition of the 82C55A is programmed by the I/O service routine and becomes an extension of the system software. By examining the I/O devices interface characteristics for both data transfer and timing, and matching this information to the examples and tables in the detailed operational description, a control word can easily be developed to initialize the 82C55A to exactly "fit" the application. Figures 18 through 24 present a few examples of typical applications of the 82C55A.

FIGURE 18. PRINTER INTERFACE

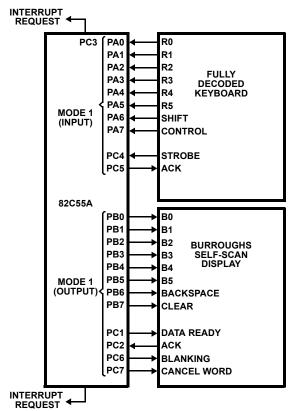

FIGURE 19. KEYBOARD AND DISPLAY INTERFACE

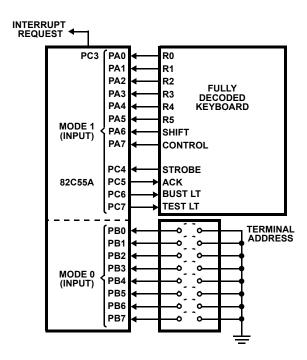

FIGURE 20. KEYBOARD AND TERMINAL ADDRESS INTERFACE

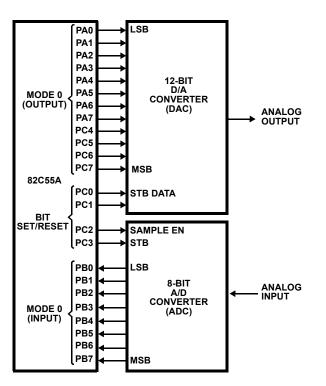

FIGURE 21. DIGITAL TO ANALOG, ANALOG TO DIGITAL

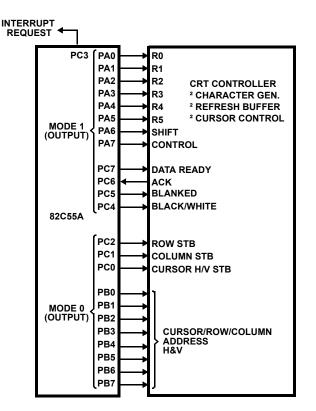

FIGURE 22. BASIC CRT CONTROLLER INTERFACE

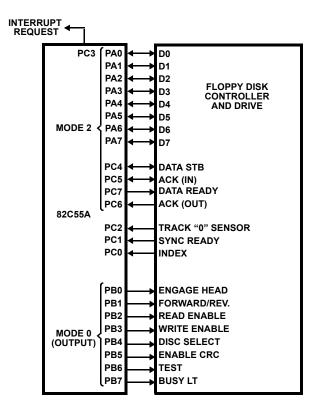

FIGURE 23. BASIC FLOPPY DISC INTERFACE

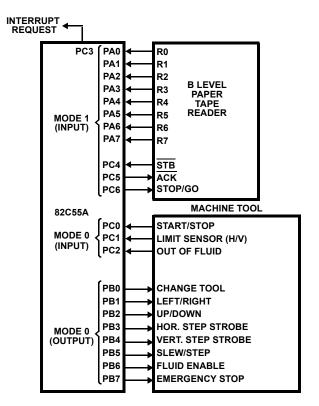

FIGURE 24. MACHINE TOOL CONTROLLER INTERFACE

## intersil

#### **Absolute Maximum Ratings** T<sub>A</sub> = +25°C

| Supply Voltage               | +8.0V                             |

|------------------------------|-----------------------------------|

| Input, Output or I/O Voltage | GND-0.5V to V <sub>CC</sub> +0.5V |

| ESD Classification           | Class 1                           |

#### **Operating Conditions**

| Voltage Range+4.5V to 5.5V  |

|-----------------------------|

| Operating Temperature Range |

| CX82C55A                    |

| IX82C55A40°C to 85°C        |

| MX82C55A55°C to 125°C       |

|                             |

#### **Die Characteristics**

#### Thermal Information

| Thermal Resistance (Typical, Note 1)   | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|----------------------------------------|----------------------|------------------------|

| CERDIP Package                         | 50                   | 10                     |

| CLCC Package                           | 65                   | 14                     |

| PDIP Package                           | 50                   | N/A                    |

| PLCC Package                           | 55                   | N/A                    |

| MQFP Package                           | 62                   | N/A                    |

| Maximum Storage Temperature Range      | 65°                  | °C to +150°C           |

| Maximum Junction Temperature           |                      |                        |

| CDIP Packages                          |                      | +175°C                 |

| PDIP Packages                          |                      | +150°C                 |

| Maximum Lead Temperature (Soldering 10 | Os)                  | +300°C                 |

| (PLCC and MQFP Lead Tips Only)         |                      |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### SYMBOL **TEST CONDITIONS** PARAMETER MIN MAX UNITS VIH Logical One Input Voltage 2.0 V 2.2 VIL Logical Zero Input Voltage -0.8 V VOH V Logical One Output Voltage $I_{OH} = -2.5 mA$ , 3.0 \_ $I_{OH} = -100 \mu A$ V<sub>CC</sub> -0.4 Logical Zero Output Voltage I<sub>OL</sub> +2.5mA V VOL -0.4 VIN = V<sub>CC</sub> or GND, RD, CS, A1, A0, RESET, WR Input Leakage Current -1.0 I<sub>I</sub> +1.0μΑ 10 I/O Pin Leakage Current VO = V<sub>CC</sub> or GND, D0 - D7 -10 +10 μΑ VO = 3.0V. Ports A, B, C IBHH **Bus Hold High Current** T<sub>A</sub> = -55°C -50 -450 μΑ T<sub>A</sub> = +128°C -50 -400 μΑ IBHL **Bus Hold Low Current** VO = 1.0V. Port A ONLY $T_A = -55^{\circ}C$ 50 450 μA T<sub>A</sub> = +128°C μΑ 50 400 Ports A, B, C. Test Condition 3 IDAR **Darlington Drive Current** -2.5 Note 2.4 mΑ **ICCSB** V<sub>CC</sub> = 5.5V, V<sub>IN</sub> = V<sub>CC</sub> or GND. Output Open μA Standby Power Supply Current -10 ICCOP **Operating Power Supply Current** $T_A = +25^{\circ}C$ , $V_{CC} = 5.0V$ , Typical (See Note 3) 1 mA/MHz \_

#### Electrical Specifications V<sub>CC</sub> = 5.0V ±10%; T<sub>A</sub> = Operating Temperature Range

NOTES:

2. No internal current limiting exists on Port Outputs. A resistor must be added externally to limit the current.

3. ICCOP = 1mA/MHz of Peripheral Read/Write cycle time. (Example: 1.0µs I/O Read/Write cycle time = 1mA).

4. Tested as V<sub>OH</sub> at -2.5mA.

#### **Capacitance** T<sub>A</sub> = +25°C

| SYMBOL | PARAMETER         | TYPICAL | UNITS | TEST CONDITIONS                                 |

|--------|-------------------|---------|-------|-------------------------------------------------|

| CIN    | Input Capacitance | 10      | pF    | FREQ = 1MHz, All Measurements are referenced to |

| CI/O   | I/O Capacitance   | 20      | pF    | device GND                                      |

#### 82C55A

## $\label{eq:constraint} \textbf{AC Electrical Specifications} \quad V_{CC} \texttt{=} \texttt{+}5V \pm \texttt{10\%}, \texttt{GND} \texttt{=} \texttt{0V}; \texttt{T}_{A} \texttt{=} \texttt{Operating Temperature Range}$

|             |                                 | 82C55A-5 82C55A |     |     | TEST |       |            |

|-------------|---------------------------------|-----------------|-----|-----|------|-------|------------|

| SYMBOL      | PARAMETER                       | MIN             | MAX | MIN | MAX  | UNITS | CONDITIONS |

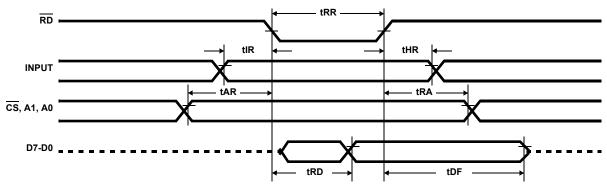

| READ TIMING |                                 |                 |     |     |      |       | 1          |

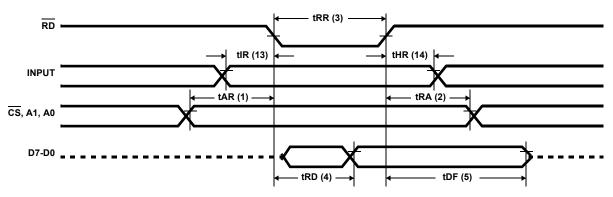

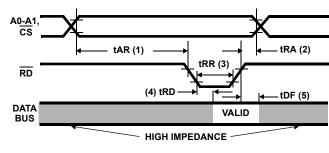

| (1) tAR     | Address Stable Before RD        | 0               | -   | 0   | -    | ns    |            |

| (2) tRA     | Address Stable After RD         | 0               | -   | 0   | -    | ns    |            |

| (3) tRR     | RD Pulse Width                  | 250             | -   | 150 | -    | ns    |            |

| (4) tRD     | Data Valid From RD              | -               | 200 | -   | 120  | ns    | 1          |

| (5) tDF     | Data Float After RD             | 10              | 75  | 10  | 75   | ns    | 2          |

| (6) tRV     | Time Between RDs and/or WRs     | 300             | -   | 300 | -    | ns    |            |

|             | 3                               |                 |     |     |      |       |            |

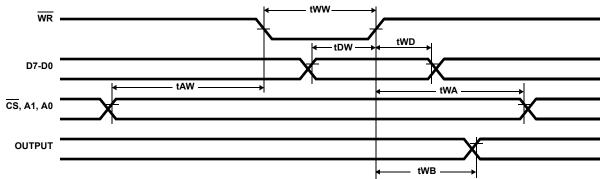

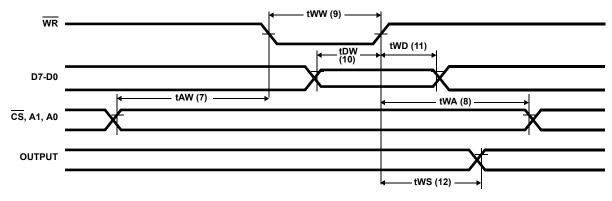

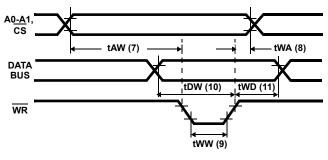

| (7) tAW     | Address Stable Before WR        | 0               | -   | 0   | -    | ns    |            |

| (8) tWA     | Address Stable After WR         | 20              | -   | 20  | -    | ns    |            |

| (9) tWW     | WR Pulse Width                  | 100             | -   | 100 | -    | ns    |            |

| (10) tDW    | Data Valid to WR High           | 100             | -   | 100 | -    | ns    |            |

| (11) tWD    | Data Valid After WR High        | 30              | -   | 30  | -    | ns    |            |

| OTHER TIMIN | G                               | I               | 1   | 1   | I    |       |            |

| (12) tWB    | WR = 1 to Output                | -               | 350 | -   | 350  | ns    | 1          |

| (13) tIR    | Peripheral Data Before RD       | 0               | -   | 0   | -    | ns    |            |

| (14) tHR    | Peripheral Data After RD        | 0               | -   | 0   | -    | ns    |            |

| (15) tAK    | ACK Pulse Width                 | 200             | -   | 200 | -    | ns    |            |

| (16) tST    | STB Pulse Width                 | 100             | -   | 100 | -    | ns    |            |

| (17) tPS    | Peripheral Data Before STB High | 20              | -   | 20  | -    | ns    |            |

| (18) tPH    | Peripheral Data After STB High  | 50              | -   | 50  | -    | ns    |            |

| (19) tAD    | ACK = 0 to Output               | -               | 175 | -   | 175  | ns    | 1          |

| (20) tKD    | ACK = 1 to Output Float         | 20              | 250 | 20  | 250  | ns    | 2          |

| (21) tWOB   | $\overline{WR}$ = 1 to OBF = 0  | -               | 150 | -   | 150  | ns    | 1          |

| (22) tAOB   | ACK = 0 to OBF = 1              | -               | 150 | -   | 150  | ns    | 1          |

| (23) tSIB   | STB = 0 to IBF = 1              | -               | 150 | -   | 150  | ns    | 1          |

| (24) tRIB   | $\overline{RD} = 1$ to IBF = 0  | -               | 150 | -   | 150  | ns    | 1          |

| (25) tRIT   | $\overline{RD} = 0$ to INTR = 0 | -               | 200 | -   | 200  | ns    | 1          |

| (26) tSIT   | STB = 1 to INTR = 1             | -               | 150 | -   | 150  | ns    | 1          |

| (27) tAIT   | ACK = 1 to INTR = 1             | -               | 150 | -   | 150  | ns    | 1          |

| (28) tWIT   | $\overline{WR} = 0$ to INTR = 0 | -               | 200 | -   | 200  | ns    | 1          |

| (29) tRES   | Reset Pulse Width               | 500             | -   | 500 | -    | ns    | 1, (Note)  |

NOTE: Period of initial Reset pulse after power-on must be at least 50µsec. Subsequent Reset pulses may be 500ns minimum.

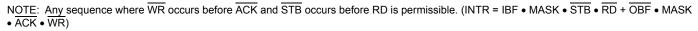

## **Timing Waveforms**

## Timing Waveforms (Continued)

FIGURE 29. MODE 2 (BIDIRECTIONAL)

NOTE: Any sequence where  $\overline{WR}$  occurs before  $\overline{ACK}$  and  $\overline{STB}$  occurs before  $\overline{RD}$  is permissible. (INTR = IBF •  $\overline{MASK}$  •  $\overline{STB}$  •  $\overline{RD}$  +  $\overline{OBF}$  •  $\overline{MASK}$  •  $\overline{ACK}$  •  $\overline{WR}$ )

## Timing Waveforms (Continued)

FIGURE 30. WRITE TIMING

FIGURE 31. READ TIMING

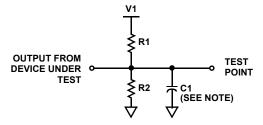

## AC Test Circuit

NOTE: Includes STRAY and JIG Capacitance

## AC Testing Input, Output Waveforms

| INPUT      | OUTPUT |

|------------|--------|

| VIH + 0.4V | VOH    |

| 1.5V       | 1.5V   |

| VIL - 0.4V | VOI    |

AC Testing: All AC Parameters tested as per test circuits. Input RISE and FALL times are driven at 1ns/V.

#### TEST CONDITION DEFINITION TABLE

| TEST CONDITION | V1              | R1   | R2    | C1    |

|----------------|-----------------|------|-------|-------|

| 1              | 1.7V            | 523Ω | Open  | 150pF |

| 2              | V <sub>CC</sub> | 2kΩ  | 1.7kΩ | 50pF  |

| 3              | 1.5V            | 750Ω | Open  | 50pF  |

## intersil

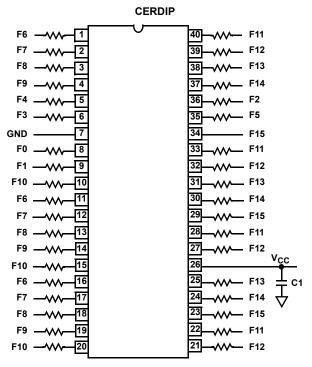

## **Burn-In Circuits**

NOTES:

1. V<sub>CC</sub> =  $5.5V \pm 0.5V$

- 2. VIH =  $4.5V\pm10\%$

- 3. VIL = -0.2V to 0.4V

4. GND = 0V

#### NOTES:

- 1. C1 =  $0.01 \mu$ F minimum

- 2. All resistors are  $47k\Omega\pm5\%$

- 3. f0 = 100kHz  $\pm$  10%

- 4. f1 = f0  $\div$  2; f2 = f1  $\div$  2; . . . ; f15 = f14  $\div$  2

## intersil

## **Die Characteristics**

#### **METALLIZATION:**

Type: Silicon - Aluminum Thickness: 11kÅ  $\pm$ 1kÅ

## Metallization Mask Layout

## GLASSIVATION:

Type: SiO<sub>2</sub> Thickness: 8kÅ *±*1kÅ

82C55A RD PA2 PA3 PA4 PA5 PA6 PA7 WR PA0 PA1 Hio HP TLOTADD DEI TDDTDT∂TL cs RESET D0 GND D1 A1 D2 A0 D3 PC7 D4 PC6 D5 PC5 D6 PC4 D7 VCC GN PC0  $v_{cc}$ PC1 **96**() 8 PC2 PC3 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE             | REVISION  | CHANGE                                                                                                                             |

|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------|

| December 8, 2015 | FN2969.11 | <ul> <li>Ordering Information Table on page 1.</li> <li>Added Revision History.</li> <li>Added About Intersil Verbiage.</li> </ul> |

## About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <u>www.intersil.com</u>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support

© Copyright Intersil Americas LLC 1998-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <u>www.intersil.com/en/support/qualandreliability.html</u>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

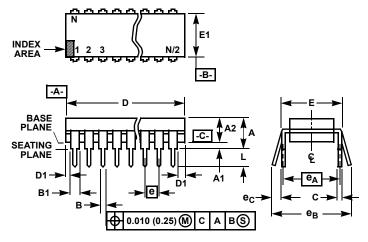

## Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- 1. Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- 6. E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C- .

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

#### **E40.6** (JEDEC MS-011-AC ISSUE B) 40 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES MILLIMETERS |       |       |       |       |

|----------------|--------------------|-------|-------|-------|-------|

| SYMBOL         | MIN                | MAX   | MIN   | MAX   | NOTES |

| А              | -                  | 0.250 | -     | 6.35  | 4     |

| A1             | 0.015              | -     | 0.39  | -     | 4     |

| A2             | 0.125              | 0.195 | 3.18  | 4.95  | -     |

| В              | 0.014              | 0.022 | 0.356 | 0.558 | -     |

| B1             | 0.030              | 0.070 | 0.77  | 1.77  | 8     |

| С              | 0.008              | 0.015 | 0.204 | 0.381 | -     |

| D              | 1.980              | 2.095 | 50.3  | 53.2  | 5     |

| D1             | 0.005              | -     | 0.13  | -     | 5     |

| Е              | 0.600              | 0.625 | 15.24 | 15.87 | 6     |

| E1             | 0.485              | 0.580 | 12.32 | 14.73 | 5     |

| е              | 0.100 BSC          |       | 2.54  | BSC   | -     |

| e <sub>A</sub> | 0.600 BSC          |       | 15.24 | BSC   | 6     |

| e <sub>B</sub> | -                  | 0.700 | -     | 17.78 | 7     |

| L              | 0.115              | 0.200 | 2.93  | 5.08  | 4     |

| Ν              | 4                  | 0     | 4     | 0     | 9     |

Rev. 0 12/93

## intersil

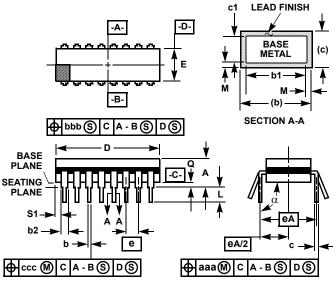

## Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

NOTES:

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- 2. The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- 3. Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

#### **F40.6** MIL-STD-1835 GDIP1-T40 (D-5, CONFIGURATION A) 40 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INCHES MILLIMETERS |                  |                 |                  |       |

|--------|--------------------|------------------|-----------------|------------------|-------|

| SYMBOL | MIN                | MAX              | MIN MAX         |                  | NOTES |

| А      | -                  | 0.225            | -               | 5.72             | -     |

| b      | 0.014              | 0.026            | 0.36            | 0.66             | 2     |

| b1     | 0.014              | 0.023            | 0.36            | 0.58             | 3     |

| b2     | 0.045              | 0.065            | 1.14            | 1.65             | -     |

| b3     | 0.023              | 0.045            | 0.58            | 1.14             | 4     |

| с      | 0.008              | 0.018            | 0.20            | 0.46             | 2     |

| c1     | 0.008              | 0.015            | 0.20            | 0.38             | 3     |

| D      | -                  | 2.096            | -               | 53.24            | 5     |

| E      | 0.510              | 0.620            | 12.95           | 15.75            | 5     |

| е      | 0.100 BSC          |                  | 2.54 BSC        |                  | -     |

| eA     | 0.600 BSC          |                  | 15.24 BSC       |                  | -     |

| eA/2   | 0.300              | BSC              | 7.62 BSC        |                  | -     |

| L      | 0.125              | 0.200            | 3.18            | 5.08             | -     |

| Q      | 0.015              | 0.070            | 0.38            | 1.78             | 6     |

| S1     | 0.005              | -                | 0.13            | -                | 7     |

| α      | 90 <sup>0</sup>    | 105 <sup>0</sup> | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |

| aaa    | -                  | 0.015            | -               | 0.38             | -     |

| bbb    | -                  | 0.030            | -               | 0.76             | -     |

| ссс    | -                  | 0.010            | -               | 0.25             | -     |

| М      | -                  | 0.0015           | -               | 0.038            | 2, 3  |

| Ν      | 4                  | 0                | 4               | 40               | 8     |

Rev. 0 4/94

## inter<sub>si</sub>[

## Ceramic Leadless Chip Carrier Packages (CLCC)

#### J44.A MIL-STD-1835 CQCC1-N44 (C-5) 44 PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE

|        | INCHES    |       | MILLI     | MILLIMETERS |       |  |

|--------|-----------|-------|-----------|-------------|-------|--|

| SYMBOL | MIN       | MAX   | MIN       | MAX         | NOTES |  |

| А      | 0.064     | 0.120 | 1.63      | 3.05        | 6, 7  |  |

| A1     | 0.054     | 0.088 | 1.37      | 2.24        | -     |  |

| В      | 0.033     | 0.039 | 0.84      | 0.99        | 4     |  |

| B1     | 0.022     | 0.028 | 0.56      | 0.71        | 2, 4  |  |

| B2     | 0.072     | REF   | 1.83      | B REF       | -     |  |

| B3     | 0.006     | 0.022 | 0.15      | 0.56        | -     |  |

| D      | 0.640     | 0.662 | 16.26     | 16.81       | -     |  |

| D1     | 0.500     | BSC   | 12.7      | 0 BSC       | -     |  |

| D2     | 0.250     | BSC   | 6.35      | 5 BSC       | -     |  |

| D3     | -         | 0.662 | -         | 16.81       | 2     |  |

| Е      | 0.640     | 0.662 | 16.26     | 16.81       | -     |  |

| E1     | 0.500 BSC |       | 12.70 BSC |             | -     |  |

| E2     | 0.250 BSC |       | 6.35 BSC  |             | -     |  |

| E3     | -         | 0.662 | -         | 16.81       | 2     |  |

| е      | 0.050 BSC |       | 1.27 BSC  |             | -     |  |

| e1     | 0.015     | -     | 0.38      | -           | 2     |  |

| h      | 0.040     | REF   | 1.02 REF  |             | 5     |  |

| j      | 0.020     | REF   | 0.51      | I REF       | 5     |  |

| L      | 0.045     | 0.055 | 1.14      | 1.40        | -     |  |

| L1     | 0.045     | 0.055 | 1.14      | 1.40        | -     |  |

| L2     | 0.075     | 0.095 | 1.90      | 2.41        | -     |  |

| L3     | 0.003     | 0.015 | 0.08      | 0.38        | -     |  |

| ND     | 1         | 1     | 11        |             | 3     |  |

| NE     | 1         | 1     |           | 11          | 3     |  |

| Ν      | 4         | 4     | 44        |             | 3     |  |

NOTES:

- 1. Metallized castellations shall be connected to plane 1 terminals and extend toward plane 2 across at least two layers of ceramic or completely across all of the ceramic layers to make electrical connection with the optional plane 2 terminals.

- 2. Unless otherwise specified, a minimum clearance of 0.015 inch (0.38mm) shall be maintained between all metallized features (e.g., lid, castellations, terminals, thermal pads, etc.)

- Symbol "N" is the maximum number of terminals. Symbols "ND" and "NE" are the number of terminals along the sides of length "D" and "E", respectively.

- 4. The required plane 1 terminals and optional plane 2 terminals (if used) shall be electrically connected.

- 5. The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown on the drawing.

- 6. Chip carriers shall be constructed of a minimum of two ceramic layers.

- 7. Dimension "A" controls the overall package thickness. The maximum "A" dimension is package height before being solder dipped.

- 8. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 9. Controlling dimension: INCH.

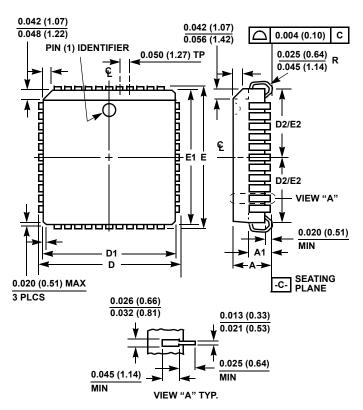

## Plastic Leaded Chip Carrier Packages (PLCC)

#### N44.65 (JEDEC MS-018AC ISSUE A) 44 LEAD PLASTIC LEADED CHIP CARRIER PACKAGE

|        | INCHES |       | MILLIMETERS |       |       |

|--------|--------|-------|-------------|-------|-------|

| SYMBOL | MIN    | MAX   | MIN         | MAX   | NOTES |

| A      | 0.165  | 0.180 | 4.20        | 4.57  | -     |

| A1     | 0.090  | 0.120 | 2.29        | 3.04  | -     |

| D      | 0.685  | 0.695 | 17.40       | 17.65 | -     |

| D1     | 0.650  | 0.656 | 16.51       | 16.66 | 3     |

| D2     | 0.291  | 0.319 | 7.40        | 8.10  | 4, 5  |

| E      | 0.685  | 0.695 | 17.40       | 17.65 | -     |

| E1     | 0.650  | 0.656 | 16.51       | 16.66 | 3     |

| E2     | 0.291  | 0.319 | 7.40        | 8.10  | 4, 5  |

| Ν      | 44     |       |             | 44    | 6     |

Rev. 2 11/97

#### NOTES:

- 1. Controlling dimension: INCH. Converted millimeter dimensions are not necessarily exact.

- 2. Dimensions and tolerancing per ANSI Y14.5M-1982.

- 3. Dimensions D1 and E1 do not include mold protrusions. Allowable mold protrusion is 0.010 inch (0.25mm) per side. Dimensions D1 and E1 include mold mismatch and are measured at the extreme material condition at the body parting line.

- 4. To be measured at seating plane -C- contact point.

- 5. Centerline to be determined where center leads exit plastic body.

- 6. "N" is the number of terminal positions.

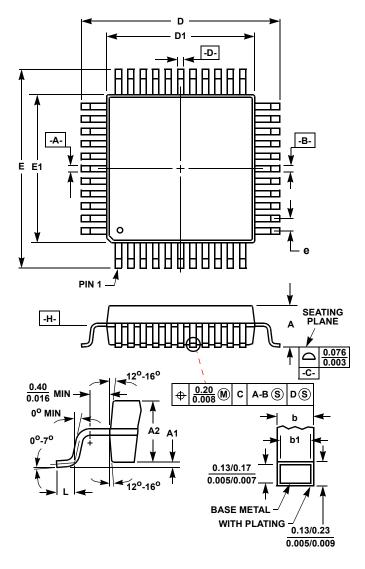

## Metric Plastic Quad Flatpack Packages (MQFP)

#### Q44.10x10 (JEDEC MS-022AB ISSUE B) 44 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

|            | INCHES |       | INCHES MILLIMETERS |       |             |

|------------|--------|-------|--------------------|-------|-------------|

| SYMBOL     | MIN    | MAX   | MIN                | MAX   | NOTES       |

| А          | -      | 0.096 | -                  | 2.45  | -           |

| A1         | 0.004  | 0.010 | 0.10               | 0.25  | -           |

| A2         | 0.077  | 0.083 | 1.95               | 2.10  | -           |

| b          | 0.012  | 0.018 | 0.30               | 0.45  | 6           |

| b1         | 0.012  | 0.016 | 0.30               | 0.40  | -           |

| D          | 0.515  | 0.524 | 13.08              | 13.32 | 3           |

| D1         | 0.389  | 0.399 | 9.88               | 10.12 | 4, 5        |

| E          | 0.516  | 0.523 | 13.10              | 13.30 | 3           |

| E1         | 0.390  | 0.398 | 9.90               | 10.10 | 4, 5        |

| L          | 0.029  | 0.040 | 0.73               | 1.03  | -           |

| Ν          | 44     |       |                    | 44    | 7           |

| е          | 0.032  | BSC   | 0.80 BSC           |       | -           |

| Rev. 2 4/9 |        |       |                    |       | Rev. 2 4/99 |

#### NOTES:

- 1. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 2. All dimensions and tolerances per ANSI Y14.5M-1982.

- 3. Dimensions D and E to be determined at seating plane -C-

- Dimensions D1 and E1 to be determined at datum plane

-H -Image: A state of the sta

- 5. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25mm (0.010 inch) per side.

- 6. Dimension b does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total.

- 7. "N" is the number of terminal positions.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

**Renesas Electronics:**

<u>CP82C55A</u> <u>CS82C55A</u> <u>ID82C55A</u> <u>IP82C55A</u> <u>IS82C55A</u> <u>IS82C55A-5</u> <u>CP82C55A-5Z</u> <u>CP82C55AZ</u> <u>CQ82C55AZ</u> <u>CS82C55A-5Z</u> <u>CS82C55A-5Z96</u> <u>CS82C55AZ</u> <u>CS82C55AZ96</u> <u>IP82C55AZ</u> <u>IQ82C55AZ</u> <u>IQ82C55AZ96</u> <u>IS82C55A-5Z96</u> <u>IS82C55AZ96</u> <u>IS82C55A</u> <u>I</u>