##

## **RS-485/RS-422** Transceivers with Preemphasis for High-Speed, Long-Distance Communication

## **General Description**

The MAX3291/MAX3292 high-speed RS-485/RS-422 transceivers feature driver preemphasis circuitry, which extends the distance and increases the data rate of reliable communication by reducing intersymbol interference (ISI) caused by long cables. The MAX3291 is programmable for data rates of 5Mbps to 10Mbps, while the MAX3292 is programmable for data rates up to 10Mbps by using a single external resistor.

The MAX3291/MAX3292 are full-duplex devices that operate from a single +5V supply and offer a low-current shutdown mode that reduces supply current to 100nA. They feature driver output short-circuit current limiting and a fail-safe receiver input that guarantees a logic-high output if the input is open circuit. A 1/4-unitload receiver input impedance allows up to 128 transceivers on the bus.

Applications

Long-Distance, High-Speed RS-485/RS-422 Communications

Telecommunications

Industrial-Control Local Area Networks

#### \_Features

- Preemphasis Increases the Distance and Data Rate of Reliable RS-485/RS-422 Communication

- Data Rate

Optimized for 5Mbps to 10Mbps (MAX3291)

Programmable up to 10Mbps (MAX3292)

- + 100nA Low-Current Shutdown Mode

- + Allow Up to 128 Transceivers on the Bus

- ♦ -7V to +12V Common-Mode Input Voltage Range

- Pin-Compatible with '75180, MAX489, MAX491 MAX3080, MAX3083, MAX3086, MAX1482

#### \_Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE    |

|------------|----------------|----------------|

| MAX3291CSD | 0°C to +70°C   | 14 SO          |

| MAX3291CPD | 0°C to +70°C   | 14 Plastic DIP |

| MAX3291ESD | -40°C to +85°C | 14 SO          |

| MAX3291EPD | -40°C to +85°C | 14 Plastic DIP |

| MAX3292CSD | 0°C to +70°C   | 14 SO          |

| MAX3292CPD | 0°C to +70°C   | 14 Plastic DIP |

| MAX3292ESD | -40°C to +85°C | 14 SO          |

| MAX3292EPD | -40°C to +85°C | 14 Plastic DIP |

Pin Configuration appears at end of data sheet.

#### M/IXI/M

Maxim Integrated Products 1

*For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.*

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> , V <sub>CCD</sub> )+6V<br>Control Input Voltage (RE, DE, PEE, |

|------------------------------------------------------------------------------------------------|

| PSET, DI)0.3V to (V <sub>CC</sub> + 0.3V)                                                      |

| Driver Output Voltage (Y, Z)7.5V to +12.5V                                                     |

| Receiver Input Voltage (A, B)7.5V to +12.5V                                                    |

| Receiver Output Voltage (RO)0.3V to (V <sub>CC</sub> + 0.3V)                                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                          |

| 14-Pin SO (derate 8.7mW/°C above +70°C)695mW                                                   |

| 14-Pin Plastic DIP (derate 10.0mW/°C above +70°C)800mW                                         |

| Operating Temperature Ranges        |                |

|-------------------------------------|----------------|

| MAX329_C_ D                         | 0°C to +70°C   |

| MAX329_E_ D                         | 40°C to +85°C  |

| Storage Temperature Range           | 65°C to +160°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(Typical Operating Circuit, V<sub>CC</sub> = +5V ±5%, RPSET = 0 (MAX3292), V<sub>CC</sub> = V<sub>CCD</sub> (MAX3292), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at V<sub>CC</sub> = +5V and T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                                                          | SYMBOL                                | CONDITIONS                                                                 |                                              | MIN  | TYP                 | MAX         | UNITS |

|------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|------|---------------------|-------------|-------|

| DRIVER                                                                             |                                       |                                                                            |                                              |      |                     |             |       |

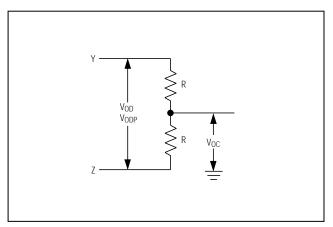

| Differential Driver Output                                                         | Vod                                   | Figure 1                                                                   | R = 27Ω<br>No load (Note 2)                  | 1.5  |                     | 5.0<br>5.25 | V     |

| Differential Driver Output with<br>Preemphasis                                     | VODP                                  | R = 27Ω                                                                    |                                              | 2.4  |                     |             | V     |

| Differential Driver<br>Preemphasis Ratio                                           | DPER                                  | Figure 1, R = $27\Omega$ (Note                                             | 23)                                          | 1.65 | 2.0                 | 2.35        | V     |

| Change in Magnitude of<br>Differential Output Voltage<br>(Normal and Preemphasis)  | $\Delta V_{OD}$ ,<br>$\Delta V_{ODP}$ | Figure 1, R = $27\Omega$ (Note                                             | 2 4)                                         |      |                     | 0.2         | V     |

| Driver Common-Mode Output<br>Voltage (Normal and<br>Preemphasis)                   | V <sub>OC</sub>                       | Figure 1, R = $27\Omega$                                                   |                                              |      | V <sub>CC</sub> / 2 | 3           | V     |

| Change in Magnitude of<br>Common-Mode Voltage<br>(Normal and Preemphasis)          | ΔV <sub>OC</sub>                      | Figure 1, R = $27\Omega$ (Note 5)                                          |                                              |      |                     | 0.3         | V     |

| Change in Magnitude of<br>Common-Mode Output<br>Voltage (Normal to<br>Preemphasis) | ΔV <sub>NP</sub>                      | Figure 1, R = $27\Omega$                                                   |                                              |      | 50                  |             | mV    |

| Input High Voltage                                                                 | VIH                                   | DE, DI, RE                                                                 |                                              | 2.4  |                     |             | V     |

| input high voltage                                                                 | VIH                                   | PEE 3.7                                                                    | 3.75                                         |      |                     | v           |       |

| Input Low Voltage                                                                  | VIL                                   | DE, DI, RE, PEE                                                            |                                              |      |                     | 0.8         | V     |

| Input Current                                                                      | lin                                   | DE, DI, RE                                                                 |                                              |      |                     | ±2          | μΑ    |

| PEE Input Current (MAX3291)                                                        | IPEE                                  |                                                                            |                                              | -15  | -30                 | -45         | μA    |

| PSET Input Current (MAX3292)                                                       | IPSET                                 | VPSET = VCC                                                                |                                              |      | 70                  | 110         | μA    |

| Output Leakage (Y and Z)                                                           | IO                                    | $\begin{array}{l} DE = GND, \\ V_{CC} = GND \text{ or } 5.25V \end{array}$ | $V_{Y} = V_{Z} = +12V$ $V_{Y} = V_{Z} = -7V$ |      |                     | 25<br>-25   | μA    |

| Driver Short-Circuit Output<br>Current                                             | IOSD                                  | $-7V \le V_{OUT} \le +12V$ (Note 6)                                        |                                              | ±30  |                     | ±250        | mA    |

M/X/M

### DC ELECTRICAL CHARACTERISTICS (continued)

(Typical Operating Circuit,  $V_{CC} = +5V \pm 5\%$ , RPSET = 0 (MAX3292),  $V_{CC} = V_{CCD}$  (MAX3292), TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at  $V_{CC} = +5V$  and T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                                                                              |                 | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------|-----------------|------|-----|------|-------|

| RECEIVER                                   |                   |                                                                                                         |                 |      |     |      |       |

| Input Current (A and B)                    |                   | DE = GND,                                                                                               | $V_{IN} = +12V$ |      |     | 250  |       |

| input current (A and B)                    | IA, B             | $V_{CC} = GND \text{ or } 5.25V$                                                                        | $V_{IN} = -7V$  |      |     | -150 | μΑ    |

| Receiver Differential<br>Threshold Voltage | V <sub>TH</sub>   | $-7V \le V_{CM} \le +12V$                                                                               |                 | -200 |     | 200  | mV    |

| Receiver Input Hysteresis                  | $\Delta V_{TH}$   | $V_A = V_B = 0$                                                                                         |                 |      | 35  |      | mV    |

| Receiver Output High Voltage               | Voh               | $I_O = -4mA$ , $V_A - V_B = V_{TH}$                                                                     |                 | 3.5  |     |      | V     |

| Receiver Output Low Voltage                | Vol               | $I_O = 4mA$ , $V_A - V_B = -V_{TH}$                                                                     |                 |      |     | 0.4  | V     |

| Three-State Output Current at Receiver     | lozr              | $0 \le V_0 \le V_{CC}$                                                                                  |                 |      | 0.1 | ±1   | μA    |

| Receiver Input Resistance                  | RIN               | $-7V \le V_{CM} \le +12V$                                                                               |                 | 48   |     |      | kΩ    |

| Receiver Output Short-Circuit<br>Current   | IOSR              | $0 \le V_{RO} \le V_{CC}$                                                                               |                 | ±15  |     | ±95  | mA    |

| SUPPLY CURRENT                             |                   |                                                                                                         |                 | -    |     |      |       |

| No-Load Supply Current                     | ICC + ICCD        | $\overline{\text{RE}}$ = GND, DE = V <sub>CC</sub>                                                      |                 |      | 2.0 | 3.0  | mA    |

| Supply Current in Shutdown<br>Mode         | I <sub>SHDN</sub> | $\overline{RE} = V_{CC}$ , DE = GND, V <sub>Y</sub> = V <sub>Z</sub> = 0 to V <sub>CC</sub> or floating |                 |      | 0.1 | 1    | μΑ    |

### SWITCHING CHARACTERISTICS

(Typical Operating Circuit,  $V_{CC} = +5V \pm 5\%$ ,  $R_{PSET} = 0$  (MAX3292),  $V_{CC} = V_{CCD}$  (MAX3292),  $T_A = +25^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                                 | SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CONE                                                                                 | DITIONS                                   | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|-----|------|-----|-------|

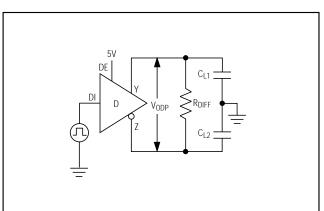

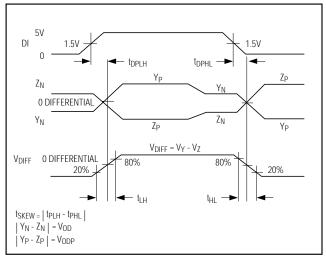

| Driver Propagation Delay                                                  | tdplh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figures 3 and 5, RDIFF                                                               | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,  |     | 41   | 65  | ns    |

|                                                                           | t dphl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $C_{L1} = C_{L2} = 50 pF$                                                            |                                           |     | 44   | 65  | 113   |

| Driver Differential Output                                                | t <sub>HL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figures 3 and 5, RDIFF                                                               | = 54Ω,                                    |     | 12   |     | ns    |

| Rise or Fall Time                                                         | tlh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $C_{L1} = C_{L2} = 50 pF$                                                            | $C_{L1} = C_{L2} = 50 \text{pF}$          |     | 12   |     | 115   |

| Driver Preemphasis Interval                                               | terms is the figures in the figures the figures is the figures in the figures | 0                                                                                    | MAX3291/MAX3292,<br>R <sub>PSET</sub> = 0 | 80  | 100  | 120 | ns    |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MAX3292,<br>R <sub>PSET</sub> = 523k $\Omega$                                        | 0.75                                      | 1   | 1.25 | μs  |       |

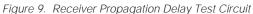

| Preemphasis Voltage Level to<br>Normal Voltage Level Delay                | t <sub>PTND</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figures 3 and 10, $R_{DIFF} = 54\Omega$ ,<br>$C_{L1} = C_{L2} = 50pF$                |                                           |     | 30   |     | ns    |

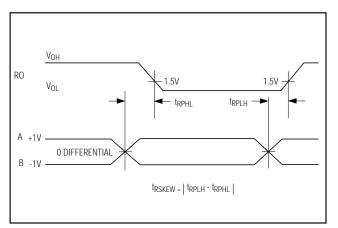

| Differential Driver Output<br>Skew  t <sub>DPLH</sub> - t <sub>DPHL</sub> | t <sub>DSKEW</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figures 3 and 5, $R_{DIFF} = 54\Omega$ ,<br>C <sub>L1</sub> = C <sub>L2</sub> = 50pF |                                           |     | 3    | 8   | ns    |

| Maximum Data Rate                                                         | fMAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                      |                                           | 10  |      |     | Mbps  |

## SWITCHING CHARACTERISTICS (continued)

(Typical Operating Circuit,  $V_{CC} = +5V \pm 5\%$ ,  $R_{PSET} = 0$  (MAX3292),  $V_{CC} = V_{CCD}$  (MAX3292),  $T_A = +25^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +5V$  and  $T_A = +25^{\circ}C$ .)

| PARAMETER                                                      | SYMBOL            | CONDITIONS                                                                         | MIN | TYP  | MAX  | UNITS |

|----------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------|-----|------|------|-------|

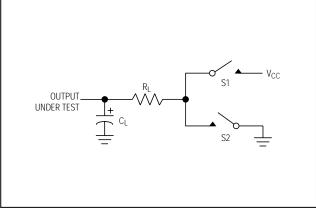

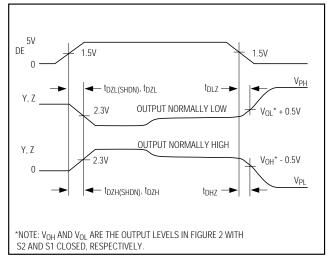

| Driver Enable to Output High                                   | t <sub>DZH</sub>  | Figures 2 and 6, S2 closed, R <sub>L</sub> = 500 $\Omega$ , C <sub>L</sub> = 100pF |     | 72   | 105  | ns    |

| Driver Enable to Output Low                                    | t <sub>DZL</sub>  | Figures 2 and 6, S1 closed, RL = 500 $\Omega$ , CL = 100pF                         |     | 55   | 105  | ns    |

| Driver Disable Time from Low                                   | t <sub>DLZ</sub>  | Figures 2 and 6, S1 closed, RL = 500 $\Omega$ , CL = 15pF                          |     | 53   | 100  | ns    |

| Driver Disable Time from High                                  | tdhz              | Figures 2 and 6, S2 closed, RL = 500 $\Omega$ , CL = 15pF                          |     | 71   | 100  | ns    |

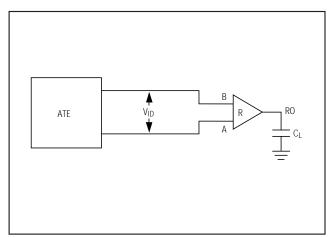

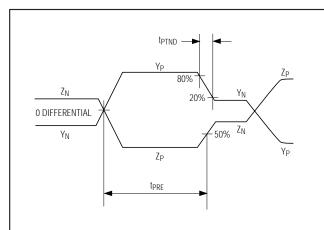

| Receiver Propagation Delay                                     | t <sub>RPLH</sub> | Figures 7 and 9, $C_L = 50pF$ , $V_{ID} = 2V$ ,                                    |     | 49   | 85   | ns    |

| Receiver Propagation Delay                                     | <b>t</b> RPHL     | $V_{CM} = 0$                                                                       |     | 52   | 85   | 115   |

| Receiver Output Skew<br> t <sub>RPLH</sub> - t <sub>RPHL</sub> | <b>t</b> RSKEW    | Figures 7 and 9, $C_L = 100 pF$                                                    |     | 3    |      | ns    |

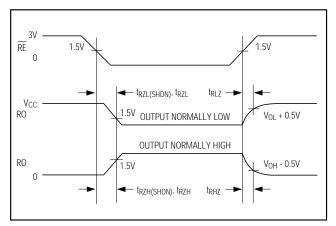

| Receiver Enable to Output<br>Low                               | t <sub>RZL</sub>  | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 100pF$ , S1 closed                      |     | 43   | 55   | ns    |

| Receiver Enable to Output<br>High                              | t <sub>RZH</sub>  | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 100pF$ , S2 closed                      | 3   | 43   | 55   | ns    |

| Receiver Disable Time from Low                                 | t <sub>RLZ</sub>  | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 15pF$ , S1 closed                       |     | 25   | 45   | ns    |

| Receiver Disable Time from<br>High                             | t <sub>RHZ</sub>  | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 15pF$ , S2 closed                       |     | 25   | 45   | ns    |

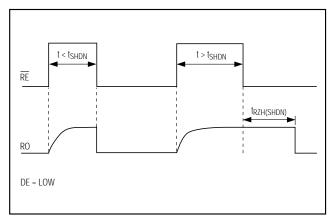

| Time to Shutdown                                               | <b>t</b> SHDN     | Figures 4 and 11 (Note 7)                                                          | 50  | 160  | 500  | ns    |

| Driver Enable from Shutdown<br>to Output High                  | tdzh(shdn)        | Figures 2 and 6, $R_L = 500\Omega$ , $C_L = 100pF$ , S2 closed                     |     | 6000 | 8750 | ns    |

| Driver Enable from Shutdown to Output Low                      | tDZL(SHDN)        | Figures 2 and 6, RL = 500 $\Omega$ , CL = 100pF, S1 closed                         |     | 6000 | 8750 | ns    |

| Receiver Enable from<br>Shutdown to Output High                | trzh(ShDN)        | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 100pF$ , S2 closed                      |     | 850  | 1500 | ns    |

| Receiver Enable from<br>Shutdown to Output Low                 | trzl(SHDN)        | Figures 2 and 8, $R_L = 1k\Omega$ , $C_L = 100pF$ , S1 closed                      |     | 30   | 1500 | ns    |

Note 1: All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to device ground unless otherwise noted.

Note 2: Guaranteed by design.

Note 3: DPER is defined as  $(V_{ODP} / V_{OD})$ .

Note 4: ΔV<sub>ODP</sub> and ΔV<sub>OC</sub> are the changes in V<sub>DD</sub> and V<sub>OC</sub>, respectively, when the DI input changes. This specification reflects constant operating conditions. When operating conditions shift, the maximum value may be momentarily exceeded.

**Note 5:**  $\Delta V_{ODP}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the DI input changes state.

Note 6: Maximum current level applies to peak current just prior to foldback-current limiting; minimum current level applies during current limiting.

**Note 7:** Shutdown is enabled by bringing  $\overline{RE}$  high and DE low. If the enable inputs are in this state for less than 50ns, the device is guaranteed not to enter shutdown. If the enable inputs are in this state for at least 500ns, the device is guaranteed to have entered shutdown. Time to shutdown for the device (t<sub>SHDN</sub>) is measured by monitoring R0 as in Figure 4.

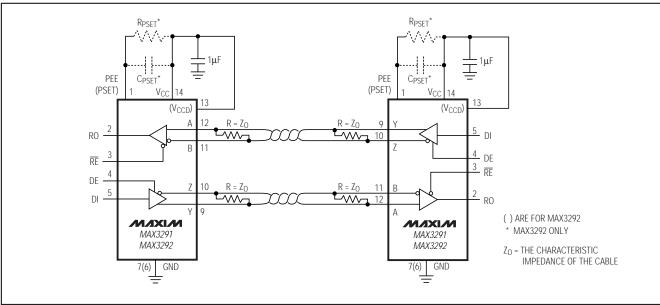

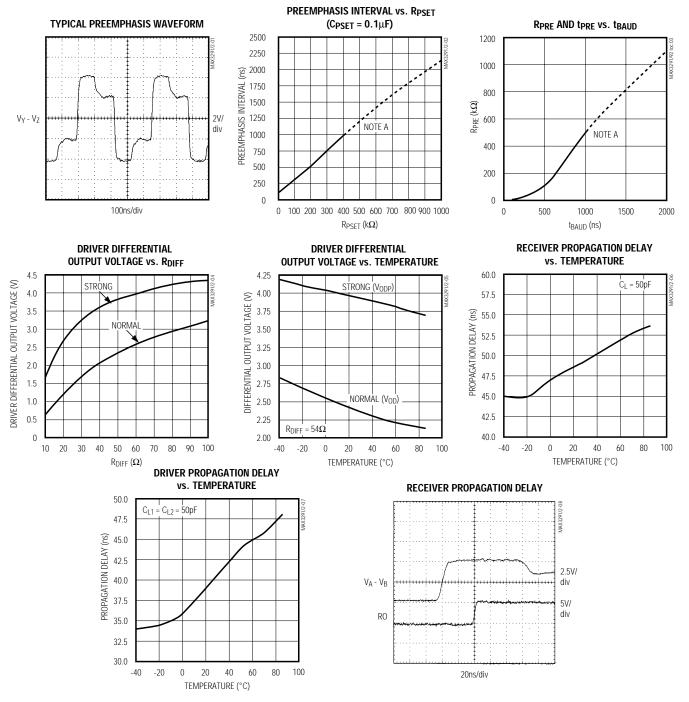

**Typical Operating Characteristics**

#### $(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

**Note A:** Dotted line represents region in which preemphasis may not work in systems with excessive power-supply noise. See *Preemphasis at Low Data Rates.*

# MAX3291/MAX3292

OUTPUT LOW VOLTAGE (V)

Typical Operating Characteristics (continued)

OUTPUT HIGH VOLTAGE (V)

M/X/M

TEMPERATURE (°C)

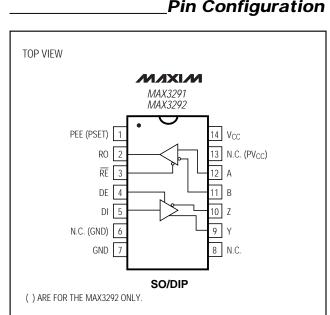

## Pin Description

| PIN      |      | NAME | FUNCTION                                                                                                                                                                                                                                                            |  |  |  |

|----------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX3291  |      |      | FUNCTION                                                                                                                                                                                                                                                            |  |  |  |

| 1        |      | PEE  | Preemphasis Enable Input. To enable preemphasis, leave PEE unconnected, connect to $V_{CC}$ , or drive high. To enable strong-level-drive only mode, connect PEE to GND or drive low.                                                                               |  |  |  |

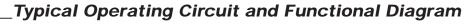

| _        | 1    | PSET | Preemphasis Set Input. Sets the preemphasis interval. Connect a resistor (R <sub>PSET</sub> ) in paral-<br>lel with a capacitor (C <sub>PSET</sub> ) from PSET to V <sub>CC</sub> to set the preemphasis interval. See <i>Typical</i><br><i>Operating Circuit</i> . |  |  |  |

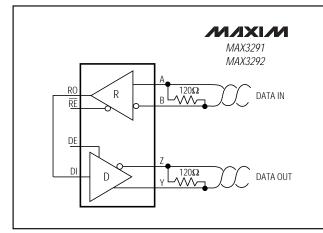

| 2        | 2    | RO   | Receiver Output. When $\overline{RE}$ is low and if A - B $\ge$ 200mV, RO is high; if A - B $\le$ -200mV, RO is low.                                                                                                                                                |  |  |  |

| 3        | 3    | RE   | Receiver Output Enable. Drive $\overline{\text{RE}}$ low to enable RO; RO is high impedance when $\overline{\text{RE}}$ is high. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode.                                                     |  |  |  |

| 4        | 4    | DE   | Driver Output Enable. Drive DE high to enable the driver outputs. These outputs are high impedance when DE is low. Drive $\overline{\text{RE}}$ high and DE low to enter low-power shutdown mode.                                                                   |  |  |  |

| 5        | 5    | DI   | Driver Input. With DE high, a low on DI forces the noninverting output low and the inverting output high. Similarly, a high on DI forces the noninverting output high and the inverting output low.                                                                 |  |  |  |

| 6, 8, 13 | 8    | N.C. | No Connection. Not internally connected.                                                                                                                                                                                                                            |  |  |  |

| 7        | 6, 7 | GND  | Ground                                                                                                                                                                                                                                                              |  |  |  |

| 9        | 9    | Y    | Noninverting Driver Output                                                                                                                                                                                                                                          |  |  |  |

| 10       | 10   | Z    | Inverting Driver Output                                                                                                                                                                                                                                             |  |  |  |

| 11       | 11   | В    | Inverting Receiver Input                                                                                                                                                                                                                                            |  |  |  |

| 12       | 12   | A    | Noninverting Receiver Input                                                                                                                                                                                                                                         |  |  |  |

|          | 13   | VCCD | Connect to V <sub>CC</sub>                                                                                                                                                                                                                                          |  |  |  |

| 14       | 14   | Vcc  | Positive Supply: +4.75V $\leq$ V <sub>CC</sub> $\leq$ +5.25V                                                                                                                                                                                                        |  |  |  |

Figure 1. Driver DC Test Load

Figure 2. Driver or Receiver Enable/Disable Timing Test Load

Figure 3. Driver Timing Test Circuit

Figure 5. Driver Propagation Delays

Figure 7. Receiver Propagation Delays

Figure 4. Shutdown Timing Diagram

Figure 6. Driver Enable and Disable Times

Figure 8. Receiver Enable and Disable Times

M/XI/M

Figure 10. Preemphasis Timing

Figure 11. Time-to-Shutdown Test Circuit

#### **Function Tables**

| TRANSMITTING |        |      |                        |        |  |  |  |

|--------------|--------|------|------------------------|--------|--|--|--|

|              | INPUTS | OUTI | PUTS                   |        |  |  |  |

| RE           | DE     | DI   | Z                      | Y      |  |  |  |

| Х            | 1      | 1    | 0                      | 1      |  |  |  |

| Х            | 1      | 0    | 1                      | 0      |  |  |  |

| 0            | 0      | Х    | High-Z                 | High-Z |  |  |  |

| 1            | 0      | Х    | High-Z and<br>SHUTDOWN |        |  |  |  |

| RECEIVING |        |         |                        |  |  |  |  |

|-----------|--------|---------|------------------------|--|--|--|--|

|           | INPUTS |         |                        |  |  |  |  |

| RE        | DE     | A-B     | RO                     |  |  |  |  |

| 0         | Х      | ≥ 0.2V  | 1                      |  |  |  |  |

| 0         | Х      | ≤ -0.2V | 0                      |  |  |  |  |

| 0         | Х      | Open    | 1                      |  |  |  |  |

| 1         | 1      | Х       | High-Z                 |  |  |  |  |

| 1         | 0      | Х       | High-Z and<br>SHUTDOWN |  |  |  |  |

X = Don't care

Z = High impedance

SHUTDOWN = Low-power shutdown; driver and receiver outputs are high impedance.

9

MAX3291/MAX3292

## Detailed Description

The MAX3291/MAX3292 high-speed RS-485/RS-422 transceivers feature driver preemphasis circuitry, which extends the distance and increases the data rate of reliable communication by reducing intersymbol interference (ISI) caused by long cables. The MAX3291 is programmable for data rates of 5Mbps to 10Mbps, while the MAX3292 is programmable for data rates up to 10Mbps by using a single external resistor.

The MAX3291/MAX3292 are full-duplex devices that operate from a single +5V supply and offer a low-current shutdown mode that reduces supply current to 100nA. They feature driver output short-circuit current limiting and a fail-safe receiver input that guarantees a logic-high output if the input is open circuit. A 1/4-unitload receiver input impedance allows up to 128 transceivers on the bus.

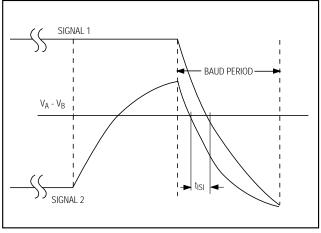

Inter-symbol interference (ISI) causes significant problems for UARTs if the total RS-485/RS-422 signal jitter becomes 10% or more of the baud period. ISI is caused by the effect of the cable's RC time constant on different bit patterns. If a series of ones is transmitted, followed by a zero, the transmission-line voltage rises to a high value at the end of the string of ones (signal 1 in Figure 12). As the signal moves towards the zero state, it takes longer to reach the zero-crossing, because its starting voltage is farther from the zero crossing. On the other hand, if the data pattern has a string of zeros followed by a one and then another zero, the one-to-zero transition starts from a voltage that is much closer to the zero-crossing ( $V_A - V_B = 0$ ) and it takes much less time for the signal to reach the zerocrossing (signal 2 in Figure 12). In other words, the propagation delay depends upon the previous bit pattern. This is inter-symbol interference (ISI).

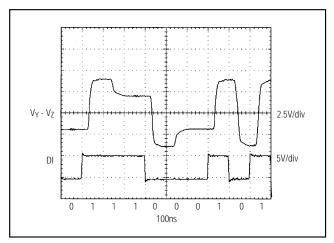

Preemphasis reduces ISI by increasing the signal amplitude at every transition edge for about one baud period, counteracting the effects of the cable (see the section Setting the Preemphasis Interval). Figure 13 shows a typical preemphasis waveform optimized for data rates between 5Mbps and 10Mbps. When DI changes from a logic low to a logic high, the differential output switches to a strong high. At the end of the preemphasis interval, the strong high returns to a normal high level. Both levels meet RS-485/RS-422 specifications, and the strong levels are typically 1.9 times larger than the normal levels. If DI switches back to a logic low before the end of the preemphasis interval, the differential output switches directly from the strong high to the strong low. Similarly, this explanation applies when DI transitions from high to low.

Figure 12. Inter-Symbol Interference among Two Data Patterns: Signal 1 = 11111110, Signal 2 = 00000010

Figure 13. Typical Preemphasis Waveform with a 100ns Preemphasis Interval

## Applications Information

#### Data Rate vs. Cable Length

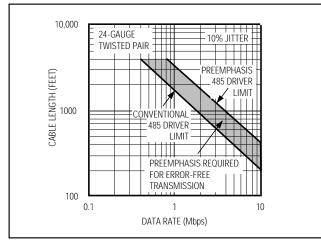

In general, preemphasis allows either double the distance for a fixed data rate or double the data rate for a fixed existing cable distance over existing RS-485 transceivers that do not feature preemphasis. Figure 14 shows that the MAX3291/MAX3292 transmits approximately twice as far at the same data rate or twice as fast at the same cable length as a conventional RS-485 transceiver without preemphasis for 10% jitter.

#### Setting the Preemphasis Interval

The MAX3291 has an internal fixed preemphasis interval of 100ns. Use the MAX3291 for existing designs requiring industry-standard '75180 pin-compatibility at data rates of 5Mbps to 10Mbps.

The MAX3292 has a resistor-programmable preemphasis interval for more flexibility. For data rates less than 1Mbps, use the following equation to calculate RPSET (the preemphasis setting resistor):

where  $t_{BAUD}$  = one baud period in ns.

For example, a baud rate of 500kbps produces a baud period of  $2\mu s$  ( $2\mu s = 2000ns$ ).

$\begin{array}{l} {\sf R}_{\sf PSET} = 580 \; (t_{\sf BAUD} \; \text{--} \; 100) \\ {\sf R}_{\sf PSET} = 580 \; (2000 \; \text{--} \; 100) = 1.1 \\ {\sf M}\Omega \end{array}$

For data rates of 1Mbps to 10Mbps, use the following equation to calculate  $\mathsf{R}_{\mathsf{PSET}}$ :

$R_{PSET} = 580 (t_{BAUD} - 100)(t_{BAUD} / 1000)$

where  $t_{BAUD}$  = one baud period in ns.

For example, a baud rate of 1Mbps produces a baud period of  $1\mu$ s ( $1\mu$ s = 1000ns).

$R_{PSET} = 580 (1000 - 100)(1000 / 1000) = 522k\Omega$  (closest standard value is 523kΩ)

Set the preemphasis interval by connecting the RPSET resistor from PSET to V<sub>CC</sub>. Use a 0.1 $\mu$ F bypass capacitor (CPSET) from PSET to V<sub>CC</sub>. If PSET is connected directly to V<sub>CC</sub> (RPSET = 0), the preemphasis interval reverts to the nominal 100ns value.

Figure 14. Preemphasis Driver Performance Compared to a Conventional Driver Without Preemphasis at 10% Jitter

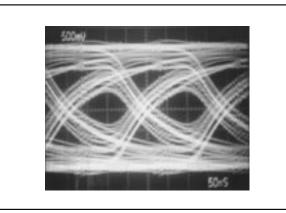

#### One simple method to quickly determine your circuit configuration is to view an eye diagram. An eye diagram is a scope photo (voltage vs. time) showing the transitions of a pseudo-random bit string displaying at least one bit interval. Use an eye diagram to quickly calculate the total jitter of a circuit configuration. Jitter is the total time variation at the zero-volt differential crossing, and percent jitter is expressed as a percentage of one baud period, tBAUD. Figures 15 and 16 show typical eye diagrams for a non-preemphasis device and the MAX3291/MAX3292. ISI and jitter are often used interchangeably; however, they are not exactly the same thing. ISI usually makes up the majority of the jitter, but asymmetrical high and low driver output voltage levels and time skews of non-ideal transceivers (driver and receiver) also contribute to jitter.

Figure 15. Eye Diagram of a Typical RS-485 Transceiver Without Preemphasis, while Driving 1000 feet of Cable at 5Mbps

Figure 16. Eye Diagram of the MAX3292 with a Preemphasis Interval of 175ns, while Driving 1000 feet of Cable at 5Mbps

Eye Diagrams

% Jitter = (total jitter / tBAUD) • 100

When the total amount of time skew becomes 10% or more of the baud period, the data error rate can increase sharply.

#### 128 Transceivers on the Bus

The standard RS-485 receiver input impedance is  $12k\Omega$  (one unit load), and the standard driver can drive up to 32 unit loads. The MAX3291/MAX3292 transceivers have a 1/4-unit-load receiver input impedance (48k $\Omega$ ), allowing up to 128 transceivers to be connected in parallel on one communication line. Any combination of these devices and/or other RS-485 transceivers with a total of 32 unit-loads or less can be connected to the line.

#### Low-Power Shutdown Mode

Initiate low-power shutdown mode by bringing  $\overline{\text{RE}}$  high and DE low. In shutdown the MAX3291/MAX3292 typically draw only 1µA of supply current.

Simultaneously driving  $\overline{RE}$  and DE is allowed; the parts are guaranteed not to enter shutdown if  $\overline{RE}$  is high and DE is low for less than 80ns. If the inputs are in this state for at least 300ns, the parts are guaranteed to enter shutdown.

Enable times tz<sub>H</sub> and tz<sub>L</sub> in the *Switching Characteris*tics tables correspond to when the part is not in the lowpower shutdown state. Enable times tz<sub>H</sub>(SHDN) and tz<sub>L</sub>(SHDN) assume the parts are shut down. It takes drivers and receivers longer to activate from the lowpower shutdown mode (tz<sub>H</sub>(SHDN), tz<sub>L</sub>(SHDN)) than from the driver/receiver disable mode (tz<sub>H</sub>, tz<sub>L</sub>).

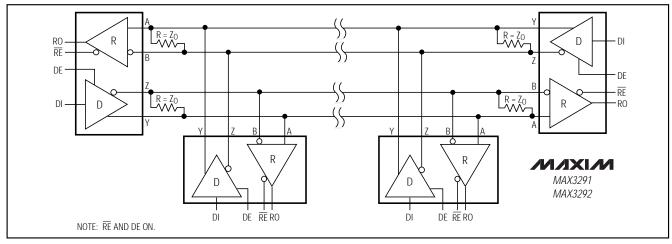

For line lengths greater than what one MAX3291/ MAX3292 can drive, use the repeater application shown in Figure 17.

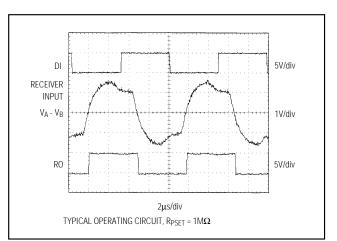

Figure 18 shows the system differential voltage for the MAX3292 driving 4000 feet of 26AWG twisted-pair wire into two  $120\Omega$  termination loads.

#### **Line Termination**

The MAX3291/MAX3292 are targeted for applications requiring the best combination of long cable length and lowest bit-error rate. In order to achieve this combination, the cable system must be set up with care. There are three basic steps:

- 1) The cable should only have two ends (no tree configuration with long branches), which are terminated with a simple resistor termination whose value is the cable's characteristic impedance (Zo). Avoid terminations anywhere else along the cable. This ensures that there are no reflections at the end of the cable, and that all transmitters (whether they are located at the ends of the cable or somewhere along the length) see the same impedance, equal to  $Z_0 / 2$ .

- 2) Make all branches or stubs short enough so that twice the propagation delay along the stub (down and back) is significantly less than one baud period (around 15% or less). This ensures that the reflections from the end of the stub (which are unavoidable, since the stubs are not terminated) settle in much less than a baud period. If the application requires a branch much longer than this, use a repeater (see the *Line Repeater* section).

Figure 17. Line-Repeater Application

3) Don't overload the cable with too many receivers. Even though the MAX3291/MAX3292 receives present only 1/4-unit load, placing 128 receivers on the cable will attenuate the signal if spaced out along the cable and, in addition, cause reflections if clumped in one spot. The MAX3291/MAX3292 successfully drive the cables to correct RS-485/RS-422 levels with 128 receivers, but the preemphasis effect is significantly diminished.

The MAX3291/ MAX3292 are centered for a load impedance of  $54\Omega$ , which corresponds to the parallel combination of the cable impedance and termination resistors. If your cable impedance deviates somewhat from this value, you still get the preemphasis effect (although the ideal preemphasis time, tPRE, may need adjustment). However, if your cable impedance is significantly different, the preemphasis ratio DPER changes, resulting in significantly less preemphasis. Determine the preemphasis ratio versus load by referring to the Driver Differential Output Voltage vs. R<sub>DIFF</sub> graph in the *Typical Operating Characteristics*. Read the strong and normal levels from the graph (remember that the horizontal units are half your cable impedance) and divide the two numbers to get DPER (DPER = VSTRONG / VNORMAL = VODP / VOD). Figures 19 and 20 show typical network application circuits with proper termination.

#### Preemphasis at Low Data Rates (MAX3292)

At low data rates (<1Msps), preemphasis operation is not guaranteed because it is highly dependent on the system power-supply noise. Minimize this noise by increasing bypass capacitance and using a power supply with a fast transient response.

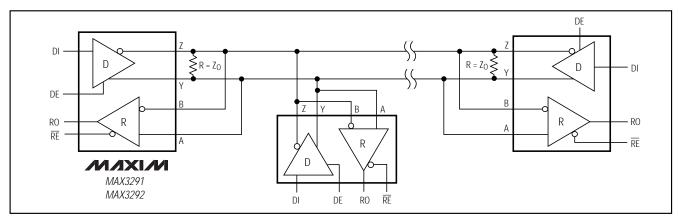

Figure 19. Typical Half-Duplex RS-485 Network

Figure 20. Typical Full-Duplex RS-485 Network

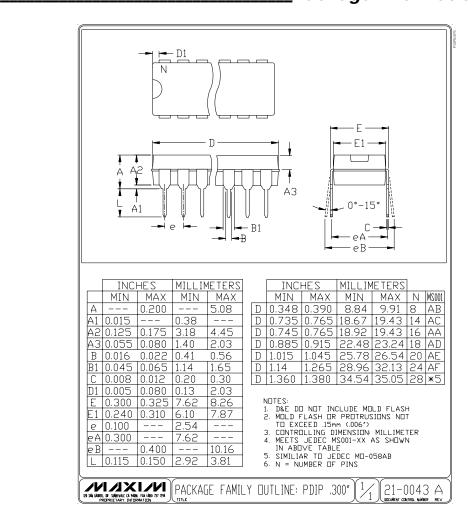

Pin Configuration

Chip Information

TRANSISTOR COUNT: 2280 SUBSTRATE CONNECTED TO GND

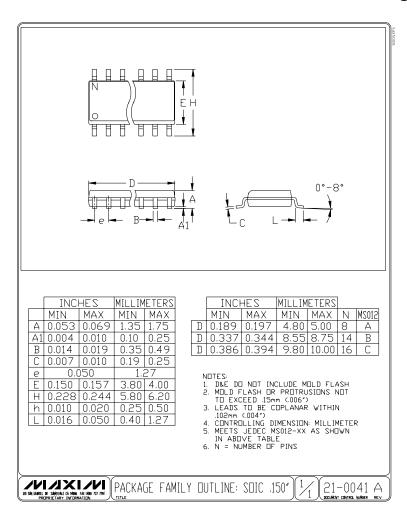

\_Package Information

\_Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1999 Maxim Integrated Products

16

Printed USA

is a registered trademark of Maxim Integrated Products.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX3291EPD+ MAX3292ESD+ MAX3291CPD+ MAX3291CSD+ MAX3291CSD+T MAX3291ESD+ MAX3291ESD+T MAX3292CPD+ MAX3292CSD+ MAX3292CSD+T MAX3292EPD+ MAX3292ESD+T