**Data Sheet**

### **FEATURES**

Programmable microphone bias (5 V to 9 V) with diagnostics Four 10 V rms capable direct-coupled differential inputs **On-chip PLL for master clock** Low EMI design 109 dB ADC dynamic range -95 dB THD + N Selectable digital high-pass filter 24-bit ADC with 8 kHz to 192 kHz sample rates Digital volume control with autoramp function I<sup>2</sup>C/SPI control Software-controllable clickless mute Software power-down Right justified, left justified, I<sup>2</sup>S justified, and TDM modes Master and slave operation modes 40-lead LFCSP package **Qualified for automotive applications**

#### APPLICATIONS

Automotive audio systems Active noise cancellation system

# **Quad ADC with Diagnostics**

# ADAU1977

#### **GENERAL DESCRIPTION**

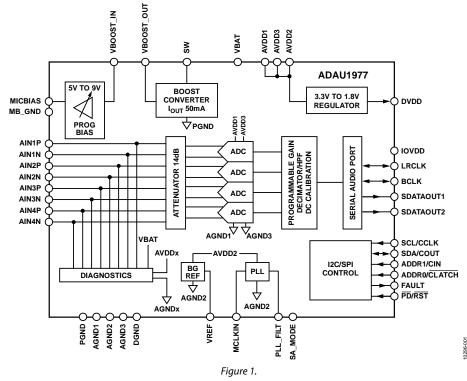

The ADAU1977 incorporates four high performance analog-todigital converters (ADCs) with direct-coupled inputs capable of 10 V rms. The ADC uses multibit sigma-delta ( $\Sigma$ - $\Delta$ ) architecture with continuous time front end for low EMI. The ADCs can be connected to the electret microphone (ECM) directly and provide the bias for powering the microphone. Built-in diagnostic circuitry detects faults on input lines and includes comprehensive diagnostics for faults on microphone inputs. The faults reported are short to battery, short to microphone bias, short to ground, short between positive and negative input pins, and open input terminals. In addition, each diagnostic fault is available as an IRQ flag for ease in system design. An I<sup>2</sup>C/SPI control port is also included. The ADAU1977 uses only a single 3.3 V supply. The part internally generates the microphone bias voltage. The microphone bias is programmable in a few steps from 5 V to 9 V. The low power architecture reduces the power consumption. An on-chip PLL can derive the master clock from an external clock input or frame clock (sample rate clock). When fed with a frame clock, the PLL eliminates the need for a separate high frequency master clock in the system. The ADAU1977 is available in a 40-lead LFCSP package.

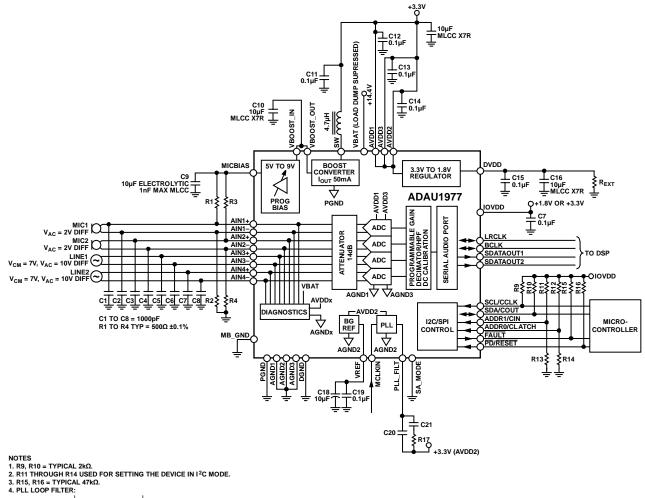

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. C

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Functional Block Diagram 1                    |

| Revision History                              |

| Specifications                                |

| Analog Performance Specifications             |

| Diagnostic and Fault Specifications           |

| Digital Input/Output Specifications6          |

| Power Supply Specifications                   |

| Digital Filters Specifications7               |

| Timing Specifications                         |

| Absolute Maximum Ratings10                    |

| Thermal Resistance10                          |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

| Typical Performance Characteristics           |

| Theory of Operation15                         |

| Overview15                                    |

| Power Supply and Voltage Reference15          |

| Power-On Reset Sequence15                     |

| PLL and Clock16                               |

| DC-to-DC Boost Converter17                    |

| Microphone Bias                               |

| Analog Inputs18                               |

| ADC                                           |

| ADC Summing Modes                             |

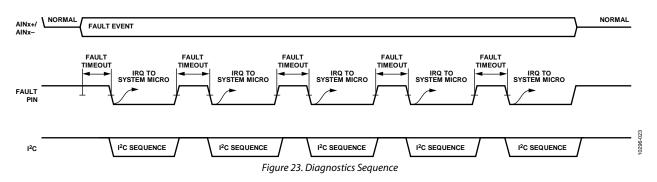

| Diagnostics                                   |

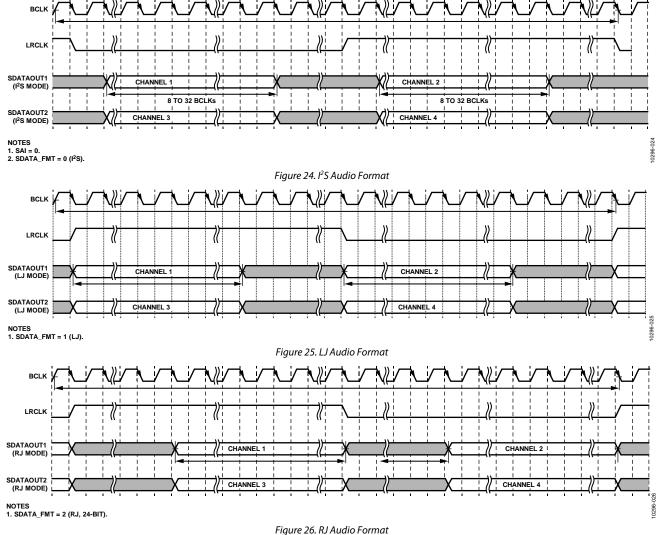

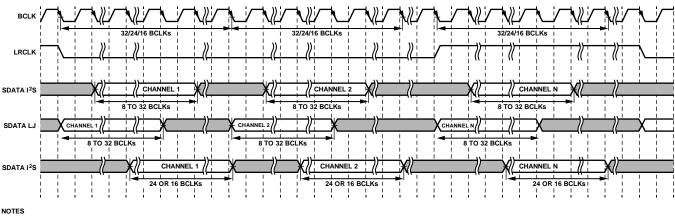

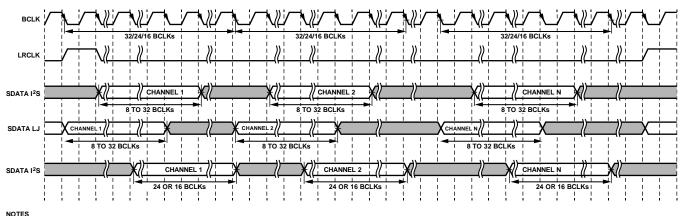

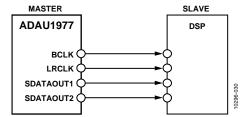

| Serial Audio Data Output Ports—Data Format    |

| Control Ports                                 |

| I <sup>2</sup> C Mode                         |

| SPI Mode                                      |

| Register Summary                              |

| Register Details                                                                                                                                                                                                                         | 37                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Master Power and Soft Reset Register                                                                                                                                                                                                     | 37                               |

| PLL Control Register                                                                                                                                                                                                                     | 38                               |

| DC-to-DC Boost Converter Control Register                                                                                                                                                                                                | 39                               |

| MICBIAS and Boost Control Register                                                                                                                                                                                                       | 40                               |

| Block Power Control and Serial Port Control Register                                                                                                                                                                                     | 41                               |

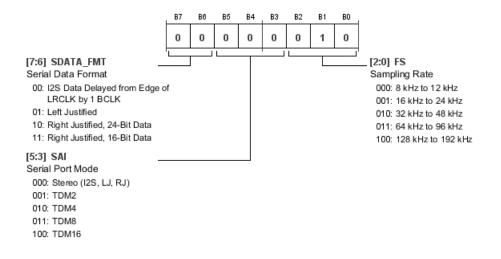

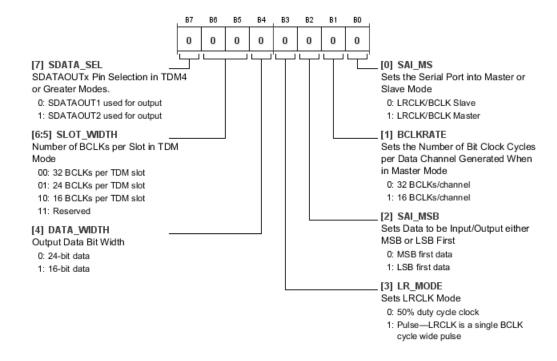

| Serial Port Control Register1                                                                                                                                                                                                            | 42                               |

| Serial Port Control Register2                                                                                                                                                                                                            | 43                               |

| Channel Mapping for Output Serial Ports Register                                                                                                                                                                                         | 44                               |

| Channel Mapping for Output Serial Ports Register                                                                                                                                                                                         | 46                               |

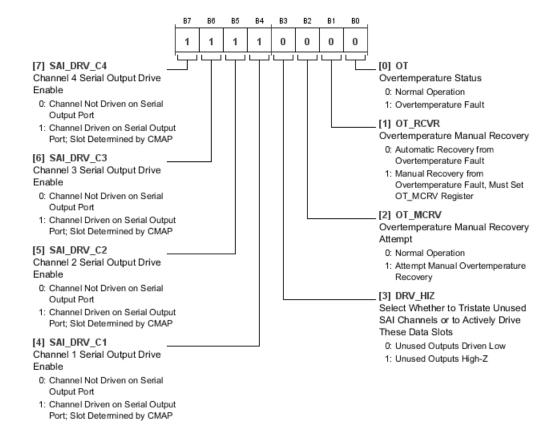

| Serial Output Drive and Overtemperature Protection<br>Control Register                                                                                                                                                                   | 48                               |

| Post ADC Gain Channel 1 Control Register                                                                                                                                                                                                 | 49                               |

| Post ADC Gain Channel 2 Control Register                                                                                                                                                                                                 | 50                               |

| Post ADC Gain Channel 3 Control Register                                                                                                                                                                                                 | 51                               |

| Post ADC Gain Channel 4 Control Register                                                                                                                                                                                                 | 52                               |

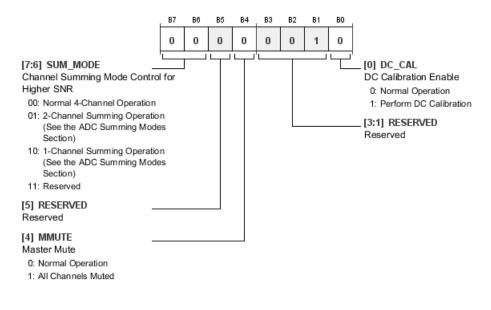

| High-Pass Filter and DC Offset Control Register and<br>Master Mute                                                                                                                                                                       | 53                               |

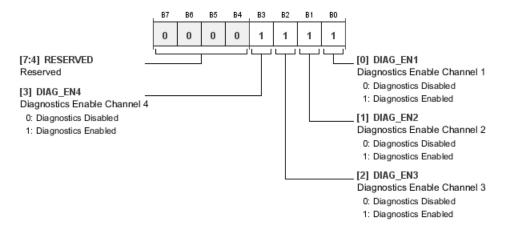

| Diagnostics Control Register                                                                                                                                                                                                             | 54                               |

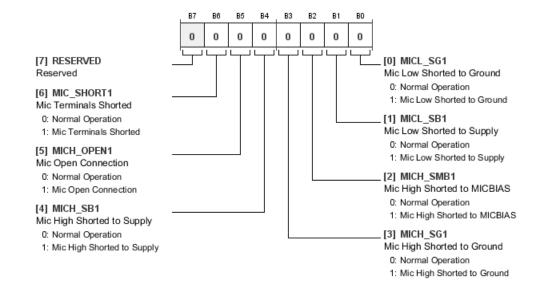

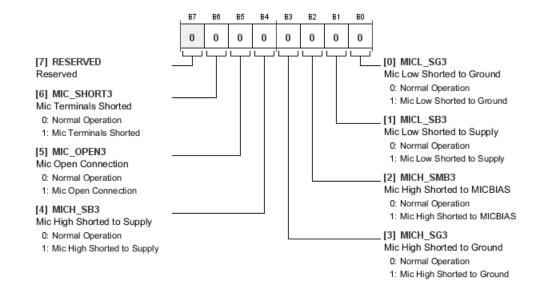

| Diagnostics Report Register Channel 1                                                                                                                                                                                                    | 55                               |

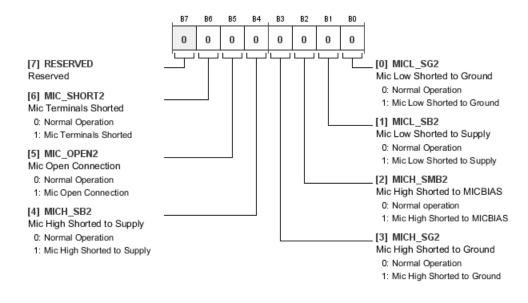

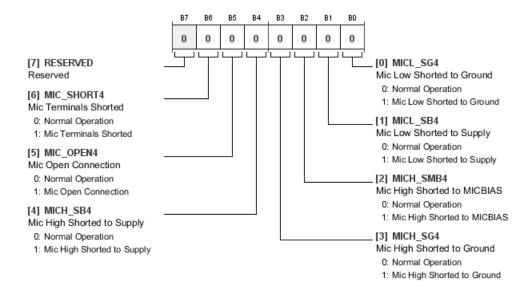

| Diagnostics Report Register Channel 2                                                                                                                                                                                                    |                                  |

| Diagnostics Report Register Channel 3                                                                                                                                                                                                    | 57                               |

| Diagnostics Report Register Channel 4                                                                                                                                                                                                    | 58                               |

|                                                                                                                                                                                                                                          | 59                               |

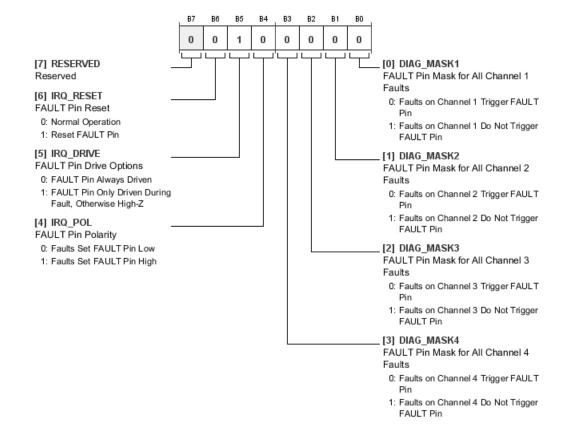

| Diagnostics Interrupt Pin Control Register 1                                                                                                                                                                                             | 60                               |

| Diagnostics Interrupt Pin Control Register 1<br>Diagnostics Interrupt Pin Control Register 2                                                                                                                                             |                                  |

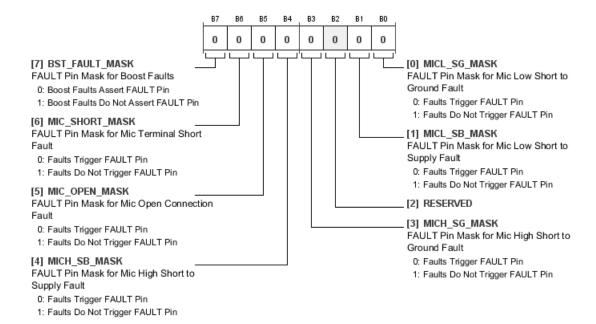

|                                                                                                                                                                                                                                          |                                  |

| Diagnostics Interrupt Pin Control Register 2                                                                                                                                                                                             | 61                               |

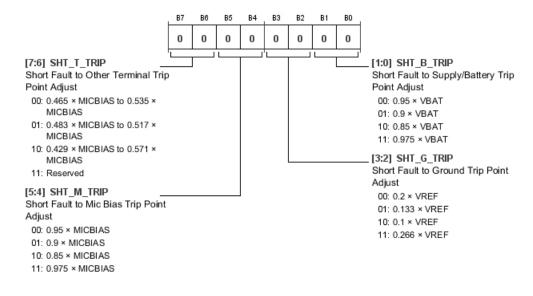

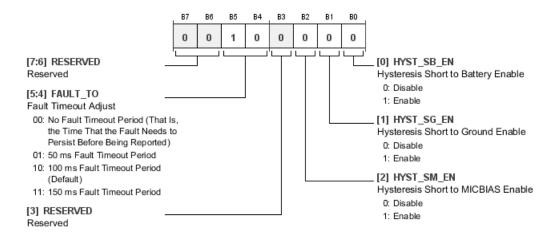

| Diagnostics Interrupt Pin Control Register 2<br>Diagnostics Adjustments Register 1                                                                                                                                                       | 61<br>62                         |

| Diagnostics Interrupt Pin Control Register 2<br>Diagnostics Adjustments Register 1<br>Diagnostics Adjustments Register 2                                                                                                                 | 61<br>62<br>63                   |

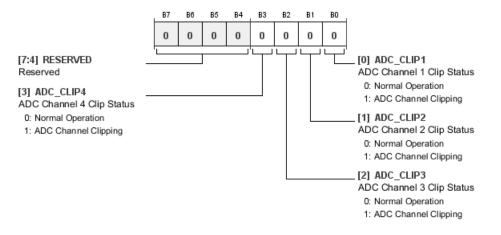

| Diagnostics Interrupt Pin Control Register 2<br>Diagnostics Adjustments Register 1<br>Diagnostics Adjustments Register 2<br>ADC Clipping Status Register                                                                                 | 61<br>62<br>63<br>64             |

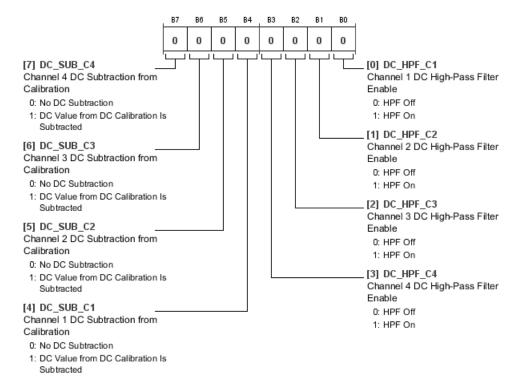

| Diagnostics Interrupt Pin Control Register 2<br>Diagnostics Adjustments Register 1<br>Diagnostics Adjustments Register 2<br>ADC Clipping Status Register<br>Digital DC High-Pass Filter and Calibration Register                         | 61<br>62<br>63<br>64<br>65       |

| Diagnostics Interrupt Pin Control Register 2<br>Diagnostics Adjustments Register 1<br>Diagnostics Adjustments Register 2<br>ADC Clipping Status Register<br>Digital DC High-Pass Filter and Calibration Register<br>Applications Circuit | 61<br>62<br>63<br>64<br>65<br>66 |

### **REVISION HISTORY**

### 1/14—Rev. B to Rev. C

| Change to Features Section                               |

|----------------------------------------------------------|

| Change to Dynamic Range (A-Weighted) Parameter, Table 14 |

| Change to Figure 913                                     |

| Change to Figure 36                                      |

| Change to Figure 4665                                    |

#### 9/13—Rev. A to Rev. B

| Changes to Figure 1            | 1  |

|--------------------------------|----|

| Moved Revision History Section | 3  |

| Changes to Figure 14           | 16 |

| Changes to Figure 46           | 65 |

|                                |    |

#### 3/13-Rev. 0 to Rev. A

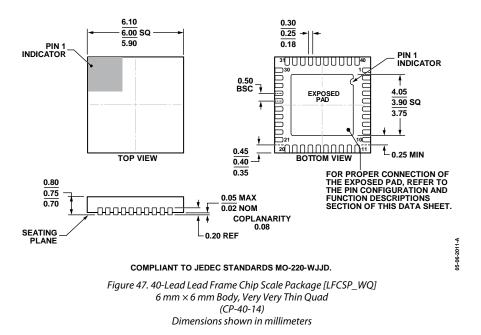

| Changed CP-40-9 to CP-40-14Universal                        |

|-------------------------------------------------------------|

| Changes to Hysteresis AINxP and AINxN Shorted Together      |

| Parameter, Table 2                                          |

| Changes to Thermal Resistance Section and Table 89          |

| Changes to SPI Mode Section                                 |

| Changes to Channel Mapping for Output Serial Ports Register |

| Section and Table 34                                        |

| Changes to Figure 46                                        |

| Changes to Ordering Guide                                   |

| 1/13—Revision 0: Initial Version                            |

## **SPECIFICATIONS**

Performance of all channels is identical, exclusive of the interchannel gain mismatch and interchannel phase deviation specifications. AVDDx/IOVDD = 3.3 V; DVDD (internally generated) = 1.8 V; VBAT = 14.4 V;  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C, unless otherwise noted; master clock = 12.288 MHz (48 kHz fs, 256 × fs mode); input sample rate = 48 kHz; measurement bandwidth = 20 Hz to 20 kHz; word width = 24 bits; load capacitance (digital output) = 20 pF; load current (digital output) =  $\pm 1$  mA; digital input voltage high = 2.0 V; digital input voltage low = 0.8 V.

### ANALOG PERFORMANCE SPECIFICATIONS

| Table 1.                                          | 1                                                                                                          |      |       |      |         |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|-------|------|---------|

| Parameter                                         | Test Conditions/Comments                                                                                   | Min  | Тур   | Мах  | Unit    |

| LINE INPUT APPLICATION                            | See Figure 46                                                                                              |      |       |      |         |

| Full-Scale Differential Input Voltage             | DC-coupled, $V_{CM}$ at AINxP/AINxN = 7 V                                                                  |      | 10    |      | V rms   |

| Full-Scale Single-Ended Input Voltage             | DC-coupled, $V_{CM}$ at AINxP/AINxN = 7 V                                                                  |      | 5     |      | V rms   |

| MICROPHONE INPUT APPLICATION                      | See Figure 46, MICBIAS = 8.5 V                                                                             |      |       |      |         |

| Differential Input Voltage                        | DC-coupled, $V_{CM}$ at AINxP = 5.66 V, AINxN = 2.83 V                                                     |      | 2     |      | V rms   |

| QUASI DC INPUT                                    |                                                                                                            |      |       |      |         |

| Single-Ended Input Voltage                        |                                                                                                            |      | 5     |      | V peak  |

| Input Common-Mode Voltage                         | V <sub>CM</sub> at AINxP/AINxN pins                                                                        | 0    |       | 8    | V dc    |

| Peak Input Voltage                                | V <sub>CM</sub> + V ac peak at AINxP/AINxN pins                                                            | 0    |       | 14   | V       |

| MICROPHONE BIAS                                   |                                                                                                            |      |       |      |         |

| Output Voltage                                    | Programmable from 5 V to 9 V in steps of 0.5 V; the output voltage is within the specified load regulation | 5    |       | 9    | V       |

| Load Regulation                                   | From no load to maximum load of 25 mA at 5 V                                                               | -1   | +0.2  | +1   | %       |

|                                                   | From no load to maximum load of 45 mA at 9 V                                                               | -1   | +0.3  | +1   | %       |

| Output Current                                    | At MICBIAS = 5 V                                                                                           |      |       | 25   | mA      |

|                                                   | At MICBIAS = $9 V$                                                                                         |      |       | 45   | mA      |

| Output Noise                                      | 20 Hz to 20 kHz, MICBIAS = 5 V                                                                             |      | 22    | 32   | μV rms  |

|                                                   | 20 Hz to 20 kHz, MICBIAS = 9 V                                                                             |      | 35    | 54   | μV rms  |

| Power Supply Rejection Ratio (PSRR)               | 350 mV rms, 1 kHz ripple on VBOOST_IN at 10 V                                                              |      | 60    |      | dB      |

| Interchannel Isolation at MICBIAS Pin             | Referred to full scale at 1 kHz                                                                            |      | 60    |      | dB      |

| Start-Up Time                                     | With $C_{LOAD} = 1 \text{ nF}$                                                                             |      | 40    |      | ms      |

| BOOST CONVERTER                                   |                                                                                                            |      |       |      |         |

| Input Voltage                                     |                                                                                                            | 2.97 | 3.3   | 3.63 | V       |

| Input Current                                     | $L = 4.7 \mu\text{H}$ , $f_{\text{SW}} = 1.536 \text{MHz}$ , MICBIAS = 9 V at 45 mA load                   |      | 195   |      | mA      |

|                                                   | $L = 2.2 \ \mu\text{H}$ , $f_{\text{SW}} = 3.072 \ \text{MHz}$ , MICBIAS = 9 V at 45 mA load               |      | 220   |      | mA      |

| Output Current                                    | MICBIAS = 5 V                                                                                              |      | 50    |      | mA      |

|                                                   | MICBIAS = 9 V                                                                                              |      | 88    |      | mA      |

| Load Regulation                                   | From no load to maximum load of 50 mA at MICBIAS<br>= 5 V                                                  | -1   |       | +1   | %       |

|                                                   | From no load to maximum load of 88 mA at MICBIAS<br>= 9 V                                                  | -1   |       | +1   | %       |

| Input Overcurrent Threshold                       |                                                                                                            |      | 900   |      | mA peak |

| Switching Frequency                               | $f_s = 48 \text{ kHz L} = 2.2 \mu \text{H}$                                                                |      | 3.072 |      | MHz     |

|                                                   | $f_s = 48 \text{ kHz}, L = 4.7 \mu \text{H}$                                                               |      | 1.536 |      | MHz     |

| External Load Capacitor at VBOOST_OUT Pin         |                                                                                                            | 4.7  | 10    | 22   | μF      |

| ANALOG-TO-DIGITAL CONVERTERS                      |                                                                                                            |      |       |      |         |

| Input Resistance                                  |                                                                                                            |      |       |      |         |

| Differential                                      | Between AINxP and AINxN                                                                                    |      | 50    |      | kΩ      |

| Single-Ended (Rin <sub>1977</sub> )               | Between AINxP and AINxN                                                                                    |      | 25    |      | kΩ      |

| ADC Resolution                                    |                                                                                                            |      | 24    |      | Bits    |

| Dynamic Range (A-Weighted) <sup>1</sup>           | Input = 1 kHz, –60 dBFS                                                                                    |      |       |      |         |

| Line Input                                        | Referred to full-scale differential input = 10 V rms                                                       | 103  | 109   |      | dB      |

| Microphone Input                                  | Referred to full-scale differential input = 2 V rms                                                        |      | 95    |      | dB      |

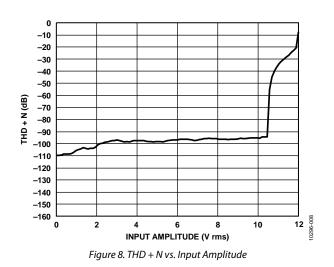

| Total Harmonic Distortion Plus Noise<br>(THD + N) | Input = 1 kHz, $-1$ dBFS (0 dBFS = 10 V rms input)                                                         |      | -95   | -89  | dB      |

| Parameter                           | Test Conditions/Comments           |         |      |       | Unit    |

|-------------------------------------|------------------------------------|---------|------|-------|---------|

| Digital Gain Post ADC               | Gain step size = 0.375 dB          | -35.625 |      | +60   | dB      |

| Gain Error                          |                                    | -10     |      | +10   | %       |

| Interchannel Gain Mismatch          |                                    | -0.25   |      | +0.25 | dB      |

| Gain Drift                          |                                    |         | 0.6  |       | ppm/°C  |

| Common-Mode Rejection Ratio (CMRR)  | 1 V rms, 1 kHz                     |         | 60   |       | dB      |

|                                     | 1 V rms, 20 kHz                    |         | 56   |       | dB      |

| Power Supply Rejection Ratio (PSRR) | 100 mV rms, 1 kHz on AVDDx = 3.3 V |         | 70   |       | dB      |

| Interchannel Isolation              |                                    |         | 100  |       | dB      |

| Interchannel Phase Deviation        |                                    |         | 0    |       | Degrees |

| REFERENCE                           |                                    |         |      |       |         |

| Internal Reference Voltage          | VREF pin                           | 1.47    | 1.50 | 1.54  | V       |

| Output Impedance                    |                                    |         | 20   |       | kΩ      |

| ADC SERIAL PORT                     |                                    |         |      |       |         |

| Output Sample Rate                  |                                    | 8       |      | 192   | kHz     |

$^{\scriptscriptstyle 1}$  For  $f_{\scriptscriptstyle S}$  ranging from 44.1 kHz to 192 kHz.

### DIAGNOSTIC AND FAULT SPECIFICATIONS

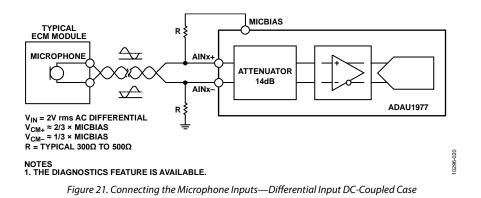

Applicable to differential microphone input using MICBIAS on AINxP and AINxN pins.

#### Table 2.

| Parameter                                                 | Test Conditions/<br>Comments                                                                                                              | Min                    | Тур                        | Max                       | Unit |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|---------------------------|------|

| INPUT VOLTAGE THRESHOLDS FOR FAULT DETECTION <sup>1</sup> |                                                                                                                                           |                        |                            |                           |      |

| Hysteresis AINxP or AINxN Shorted to VBAT                 | SHT_B_TRIP = 10                                                                                                                           | $0.79 \times VBAT$     | $0.85 \times VBAT$         | $0.86 \times VBAT$        | V    |

|                                                           | SHT_B_TRIP = 01                                                                                                                           | $0.84 \times VBAT$     | $0.9 \times VBAT$          | $0.91 \times VBAT$        | V    |

|                                                           | $SHT_B_TRIP = 00$                                                                                                                         | $0.89 \times VBAT$     | $0.95 \times VBAT$         | $0.96 \times VBAT$        | V    |

|                                                           | SHT_B_TRIP = 11                                                                                                                           | $0.93 \times VBAT$     | $0.975 \times VBAT$        | $0.99 \times VBAT$        | V    |

| Hysteresis AINxP and AINxN Shorted Together               | SHT_T_TRIP = 00                                                                                                                           | $MICBIAS(0.5\pm0.015)$ | MICBIAS(0.5 ± 0.035)       | MICBIAS(0.5 ± 0.047)      | v    |

|                                                           | SHT_T_TRIP = 01                                                                                                                           | $MICBIAS(0.5\pm0.001)$ | MICBIAS(0.5 ± 0.017)       | MICBIAS(0.5 ± 0.03)       | v    |

|                                                           | SHT_T_TRIP = 10                                                                                                                           | $MICBIAS(0.5\pm0.05)$  | MICBIAS(0.5 ± 0.071)       | MICBIAS(0.5 ± 0.08)       | v    |

| Hysteresis AINxP or AINxN Shorted to Ground               | $SHT_G_TRIP = 10$                                                                                                                         | $0.04 \times VREF$     | $0.1 \times \text{VREF}$   | 0.13 × VREF               | V    |

|                                                           | $SHT_G_TRIP = 01$                                                                                                                         | $0.08 \times VREF$     | $0.133 \times VREF$        | $0.16 \times \text{VREF}$ | V    |

|                                                           | $SHT_G_TRIP = 00$                                                                                                                         | $0.12 \times VREF$     | $0.2 \times \text{VREF}$   | $0.22 \times VREF$        | V    |

|                                                           | $SHT_G_TRIP = 11$                                                                                                                         | $0.19 \times VREF$     | $0.266 \times \text{VREF}$ | $0.28 \times \text{VREF}$ | V    |

| Hysteresis AINxP Shorted to MICBIAS                       | SHT_M_TRIP = 10                                                                                                                           | $0.82 \times MICBIAS$  | $0.85 \times MICBIAS$      | $0.89 \times MICBIAS$     | V    |

|                                                           | SHT_M_TRIP = 01                                                                                                                           | $0.87 \times MICBIAS$  | $0.9 \times MICBIAS$       | $0.94 \times MICBIAS$     | V    |

|                                                           | SHT_M_TRIP = 00                                                                                                                           | $0.92 \times MICBIAS$  | $0.95 \times MICBIAS$      | $1.0 \times MICBIAS$      | V    |

|                                                           | SHT_M_TRIP = 11                                                                                                                           | $0.95 \times MICBIAS$  | $0.975 \times MICBIAS$     | $1.0 \times MICBIAS$      | V    |

| Hysteresis AINxP or AINxN Open Circuit <sup>2</sup>       | Refer to the<br>AINXP shorted to<br>MICBIAS and the<br>AINXN shorted<br>to ground<br>specifications for<br>upper and lower<br>thresholds. |                        |                            |                           |      |

| FAULT DURATION                                            | Programmable                                                                                                                              | 10                     | 100                        | 150                       | ms   |

<sup>1</sup> The threshold limits are tested with VREF = 1.5 V, MICBIAS = 5 V to 8.5 V, and VBAT = 11 V to 18 V set using an external source. When VBAT ≤ MICBIAS, a short to VBAT cannot be distinguished from a short to MICBIAS, and reporting a short to VBAT fault takes precedence over a short to MICBIAS fault.

<sup>2</sup> The AINxP open terminal fault cannot be distinguished from the AINxN open terminal fault because the voltage at the AINxP and AINxN pins remain at MICBIAS and ground, respectively, when either of these two terminals becomes open circuit.

### DIGITAL INPUT/OUTPUT SPECIFICATIONS

#### Table 3.

| Parameter                                    | Test Conditions/Comments | Min                | Max                | Unit |

|----------------------------------------------|--------------------------|--------------------|--------------------|------|

| INPUT                                        |                          |                    |                    |      |

| High Level Input Voltage (V <sub>IH</sub> )  |                          | $0.7 \times IOVDD$ |                    | V    |

| Low Level Input Voltage (VIL)                |                          |                    | $0.3 \times IOVDD$ | V    |

| Input Leakage Current                        |                          |                    | ±10                | μΑ   |

| Input Capacitance                            |                          |                    | 5                  | рF   |

| OUTPUT                                       |                          |                    |                    |      |

| High Level Output Voltage (V <sub>он</sub> ) | I <sub>он</sub> = 1 mA   | IOVDD - 0.60       |                    | V    |

| Low Level Output Voltage (VoL)               | $I_{OL} = 1 \text{ mA}$  |                    | 0.4                | V    |

#### **POWER SUPPLY SPECIFICATIONS**

$L = 4.7 \ \mu$ H, AVDDx = 3.3 V, DVDD = 1.8 V, IOVDD = 3.3 V, f<sub>s</sub> = 48 kHz (master mode), unless otherwise noted.

Table 4.

| Parameter                | Test Conditions/Comments                          | Min Typ |      | Max  | Unit |  |

|--------------------------|---------------------------------------------------|---------|------|------|------|--|

| DVDD                     | On-chip LDO                                       | 1.62    | 1.8  | 1.98 | V    |  |

| AVDDx                    |                                                   | 3.0     | 3.3  | 3.6  | V    |  |

| IOVDD                    |                                                   | 1.62    | 3.3  | 3.6  | V    |  |

| VBAT <sup>1</sup>        |                                                   |         | 14.4 | 18   | v    |  |

| IOVDD Current            | Master clock = $256 f_s$                          |         |      |      |      |  |

| Normal Operation         | fs = 48 kHz                                       |         | 450  |      | μΑ   |  |

|                          | $f_s = 96 \text{ kHz}$                            |         | 880  |      | μΑ   |  |

|                          | f <sub>s</sub> = 192 kHz                          |         | 1.75 |      | mA   |  |

| Power-Down               | $f_s = 48$ kHz to 192 kHz                         |         | 20   |      | μΑ   |  |

| AVDDx Current            |                                                   |         |      |      |      |  |

| Normal Operation         | Boost off, 4-channel ADC, DVDD internal           |         | 14   |      | mA   |  |

|                          | Boost on, 4-channel ADC, DVDD internal            |         | 14.5 |      | mA   |  |

|                          | Boost off, 4-channel ADC, DVDD external           | 9.6     |      |      | mA   |  |

|                          | Boost on, 4-channel ADC, DVDD external            | 10.1    |      |      | mA   |  |

| Power-Down               |                                                   |         | 270  |      | μΑ   |  |

| Boost Converter Current  |                                                   |         |      |      |      |  |

| Normal Operation         | Boost on, 4-channel ADC, MICBIAS = 8.5 V, no load |         | 34   |      | mA   |  |

|                          | Boost on, 4-channel ADC, MICBIAS = 8.5 V, 42 mA   | mA 168  |      |      | mA   |  |

| Power-Down               |                                                   | 180     |      |      |      |  |

| DVDD Current             |                                                   |         |      |      |      |  |

| Normal Operation         | DVDD external = 1.8 V                             |         | 4.5  |      | mA   |  |

| Power-Down               |                                                   |         | 65   |      | μA   |  |

| VBAT Current             | VBAT = 14.4 V                                     |         |      |      |      |  |

| Normal Operation         |                                                   |         | 575  | 625  | μA   |  |

| Power-Down               |                                                   |         | 575  | 625  | μA   |  |

| POWER DISSIPATION        |                                                   |         |      |      |      |  |

| Normal Operation         | Master clock = 256 fs, 48 kHz                     |         |      |      |      |  |

| AVDDx                    | DVDD internal, MICBIAS = 8.5 V at 42 mA load      |         | 265  |      | mW   |  |

| Power-Down, All Supplies | PD/RST pin held low                               |         | 9    |      | mW   |  |

<sup>1</sup> When VBAT ≤ MICBIAS, a short to VBAT cannot be distinguished from a short to MICBIAS, and reporting a short to VBAT fault takes precedence over a short to MICBIAS fault.

### DIGITAL FILTERS SPECIFICATIONS

### Table 5.

| Parameter             | Mode                                     | Factor              | Min | Тур    | Max | Unit |  |

|-----------------------|------------------------------------------|---------------------|-----|--------|-----|------|--|

| ADC DECIMATION FILTER | All modes, typical at $f_s = 48$ kHz     |                     |     |        |     |      |  |

| Pass Band             |                                          | 0.4375 × fs 21      |     |        |     |      |  |

| Pass-Band Ripple      |                                          |                     |     | ±0.015 |     | dB   |  |

| Transition Band       |                                          | $0.5 \times f_s$    |     | 24     |     | kHz  |  |

| Stop Band             |                                          | $0.5625 \times f_s$ |     | 27     |     | kHz  |  |

| Stop-Band Attenuation |                                          | 79                  |     |        |     |      |  |

| Group Delay           | $f_s = 8 \text{ kHz to } 96 \text{ kHz}$ | 22.9844/fs          |     | 479    |     | μs   |  |

|                       | $f_s = 192 \text{ kHz}$                  |                     |     | 35     |     | μs   |  |

| HIGH-PASS FILTER      | All modes, typical at 48 kHz             |                     |     |        |     |      |  |

| Cutoff Frequency      | At –3 dB point                           |                     |     | 0.9375 |     | Hz   |  |

| Phase Deviation       | At 20 Hz 10                              |                     |     |        |     |      |  |

| Settling Time         |                                          |                     |     |        |     |      |  |

| ADC DIGITAL GAIN      | All modes                                | All modes 0 60      |     |        |     |      |  |

| Gain Step Size        | 0.375                                    |                     |     |        |     |      |  |

### Table 6.

|                           | Lim    | nit at |      |                                                                                                     |

|---------------------------|--------|--------|------|-----------------------------------------------------------------------------------------------------|

| Parameter                 | Min    | Max    | Unit | Description                                                                                         |

| INPUT MASTER CLOCK (MCLK) |        |        |      |                                                                                                     |

| Duty Cycle                | 40     | 60     | %    | MCLKIN duty cycle; MCLKIN at 256 $\times$ fs, 384 $\times$ fs, 512 $\times$ fs, and 768 $\times$ fs |

| f <sub>MCLK</sub>         | See Ta | ble 10 | MHz  | MCLKIN frequency, PLL in MCLK mode                                                                  |

| RESET                     |        |        |      |                                                                                                     |

| Reset Pulse               | 15     |        | ns   | RST low                                                                                             |

| PLL                       |        |        |      |                                                                                                     |

| Lock Time                 |        | 10     | ms   |                                                                                                     |

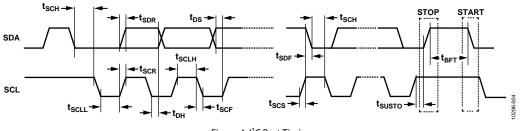

| I <sup>2</sup> C PORT     |        |        |      |                                                                                                     |

| f <sub>SCL</sub>          |        | 400    | kHz  | SCL frequency                                                                                       |

| tsclh                     | 0.6    |        | μs   | SCL high                                                                                            |

| tscll                     | 1.3    |        | μs   | SCL low                                                                                             |

| tscs                      | 0.6    |        | μs   | Setup time; relevant for repeated start condition                                                   |

| tscн                      | 0.6    |        | μs   | Hold time; after this period of time, the first clock pulse is generated                            |

| t <sub>DS</sub>           | 100    |        | ns   | Data setup time                                                                                     |

| t <sub>DH</sub>           | 0      |        |      | Data hold time                                                                                      |

| tscr                      |        | 300    | ns   | SCL rise time                                                                                       |

| t <sub>SCF</sub>          |        | 300    | ns   | SCL fall time                                                                                       |

| t <sub>sdr</sub>          |        | 300    | ns   | SDA rise time                                                                                       |

| t <sub>SDF</sub>          |        | 300    | ns   | SDA fall time                                                                                       |

| tBFT                      | 1.3    |        | μs   | Bus-free time; time between stop and start                                                          |

| tsusto                    | 0.6    |        | μs   | Setup time for stop condition                                                                       |

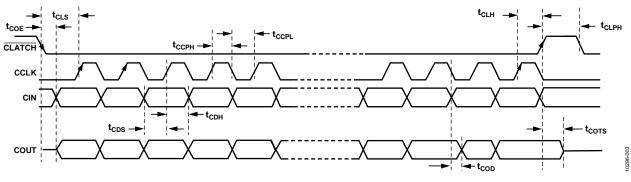

| SPI PORT                  |        |        |      |                                                                                                     |

| tссрн                     | 35     |        | ns   | CCLK high                                                                                           |

| tccpl                     | 35     |        | ns   | CCLK low                                                                                            |

| fcclк                     |        | 10     | MHz  | CCLK frequency                                                                                      |

| tcds                      | 10     |        | ns   | CIN setup to CCLK rising                                                                            |

| tcdh                      | 10     |        | ns   | CIN hold from CCLK rising                                                                           |

| tcls                      | 10     |        | ns   | CLATCH setup to CCLK rising                                                                         |

| t <sub>clH</sub>          | 40     |        | ns   | CLATCH hold from CCLK rising                                                                        |

| t <sub>clph</sub>         | 10     |        | ns   | CLATCH high                                                                                         |

| t <sub>COE</sub>          |        | 30     | ns   | COUT enable from CLATCH falling                                                                     |

| t <sub>COD</sub>          |        | 30     | ns   | COUT delay from CCLK falling                                                                        |

| tcots                     |        | 30     | ns   | COUT tristate from CLATCH rising                                                                    |

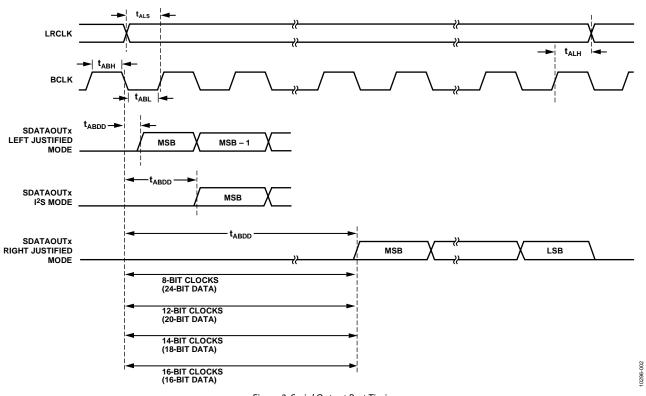

| ADC SERIAL PORT           |        | -      |      |                                                                                                     |

| t <sub>авн</sub>          | 10     |        | ns   | BCLK high, slave mode                                                                               |

| t <sub>ABL</sub>          | 10     |        | ns   | BCLK low, slave mode                                                                                |

| t <sub>ALS</sub>          | 10     |        | ns   | LRCLK setup to BCLK rising, slave mode                                                              |

| t <sub>ALH</sub>          | 5      |        | ns   | LRCLK hold from BCLK rising, slave mode                                                             |

| tabd                      | -      | 18     | ns   | SDATAOUTx delay from BCLK falling                                                                   |

## Data Sheet

ADAU1977

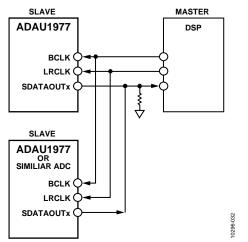

Figure 2. Serial Output Port Timing

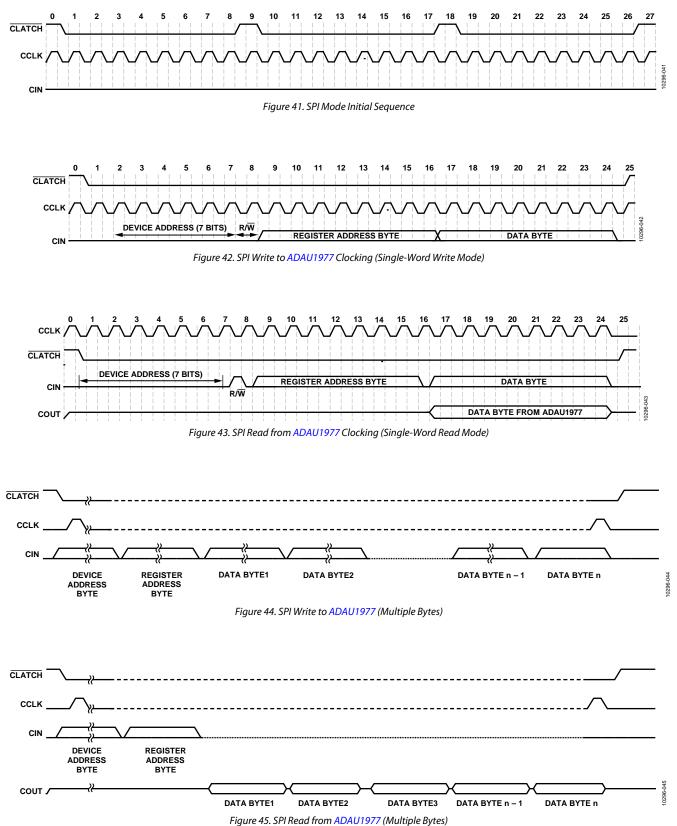

Figure 3. SPI Port Timing

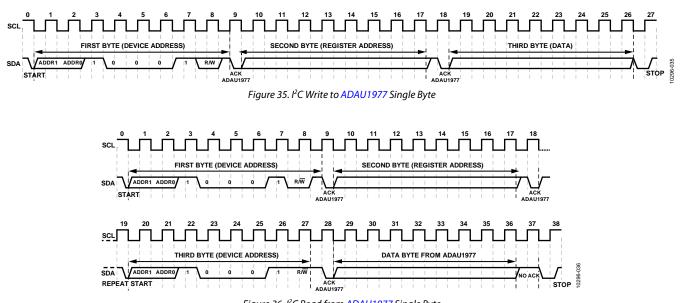

Figure 4. I<sup>2</sup>C Port Timing

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| Parameter                              | Rating            |

|----------------------------------------|-------------------|

| Analog Supply (AVDDx)                  | –0.3 V to +3.63 V |

| Digital Supply                         |                   |

| DVDD                                   | –0.3 V to +1.98 V |

| IOVDD                                  | –0.3 V to +3.63 V |

| Input Current (Except Supply Pins)     | ±20 mA            |

| Analog Input Voltage (AINx, VBAT Pins) | –0.3 V to +18 V   |

| Digital Input Voltage (Signal Pins)    | –0.3 V to +3.63 V |

| Operating Temperature Range (Ambient)  | -40°C to +105°C   |

| Junction Temperature Range             | -40°C to +125°C   |

| Storage Temperature Range              | –65°C to +150°C   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  represents thermal resistance, junction-to-ambient, and  $\theta_{JC}$  represents the thermal resistance, junction-to-case. All characteristics are for a standard JEDEC board per JESD51.

#### Table 8. Thermal Resistance

| Package Type  | θ <sub>JA</sub> | θ」   | Unit |

|---------------|-----------------|------|------|

| 40-Lead LFCSP | 32.8            | 1.93 | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

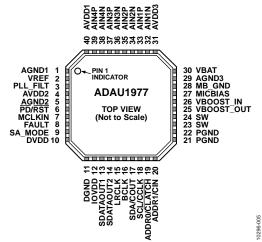

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES 1. THE EXPOSED PAD MUST BE CONNECTED TO THE GROUND PLANE ON THE PCB.

Figure 5. Pin Configuration, 40-Lead LFCSP

| Table 9. P | in Function Descri | ptions              |                                                                                                                                                  |

|------------|--------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.    | Mnemonic           | In/Out <sup>1</sup> | Description                                                                                                                                      |

| 1          | AGND1              | Р                   | Analog Ground.                                                                                                                                   |

| 2          | VREF               | 0                   | Voltage Reference. Decouple this pin to AGNDx with 10 $\mu$ F  100 nF capacitors.                                                                |

| 3          | PLL_FILT           | 0                   | PLL Loop Filter. Return this pin to AVDDx using recommended loop filter components.                                                              |

| 4          | AVDD2              | Р                   | Analog Power Supply. Connect this pin to analog 3.3 V supply.                                                                                    |

| 5          | AGND2              | Р                   | Analog Ground.                                                                                                                                   |

| 6          | PD/RST             | I                   | Power-Down Reset (Active Low).                                                                                                                   |

| 7          | MCLKIN             | 1                   | Master Clock Input.                                                                                                                              |

| 8          | FAULT              | 0                   | Fault Output. Programmable logic output.                                                                                                         |

| 9          | SA_MODE            | 1                   | Standalone Mode. Connect this pin to IOVDD using a 10 k $\Omega$ pull-up resistor for standalone mode.                                           |

| 10         | DVDD               | 0                   | 1.8 V Digital Power Supply Output. Decouple this pin to DGND with a 0.1 µF capacitor.                                                            |

| 11         | DGND               | Р                   | Digital Ground.                                                                                                                                  |

| 12         | IOVDD              | Р                   | Digital Input and Output Power Supply. Connect this pin to a supply in the range of 1.8 V to 3.3 V.                                              |

| 13         | SDATAOUT1          | 0                   | ADC Serial Data Output Pair 1.                                                                                                                   |

| 14         | SDATAOUT2          | 0                   | ADC Serial Data Output Pair 2.                                                                                                                   |

| 15         | LRCLK              | I/O                 | Frame Clock for the ADC Serial Port.                                                                                                             |

| 16         | BCLK               | I/O                 | Bit Clock for the ADC Serial Port.                                                                                                               |

| 17         | SDA/COUT           | I/O                 | Serial Data Output I <sup>2</sup> C/Control Data Output (SPI).                                                                                   |

| 18         | SCL/CCLK           | 1                   | Serial Clock Input I <sup>2</sup> C/Control Clock Input (SPI).                                                                                   |

| 19         | ADDR0/CLATCH       | I                   | Chip Address Bit 0 Setting I <sup>2</sup> C/Chip Select Input for Control Data (SPI).                                                            |

| 20         | ADDR1/CIN          | 1                   | Chip Address Bit 1 Setting I <sup>2</sup> C/Control Data Input (SPI).                                                                            |

| 21         | PGND               | Р                   | Power Ground Boost Converter.                                                                                                                    |

| 22         | PGND               | Р                   | Power Ground Boost Converter.                                                                                                                    |

| 23         | SW                 | 1                   | Inductor Switching Terminal.                                                                                                                     |

| 24         | SW                 | 1                   | Inductor Switching Terminal.                                                                                                                     |

| 25         | VBOOST_OUT         | 0                   | Boost Converter Output. Decouple this pin to PGND with a 10 $\mu$ F capacitor.                                                                   |

| 26         | VBOOST_IN          | 1                   | MICBIAS Regulator Input. Connect this pin to VBOOST_OUT (Pin 25).                                                                                |

| 27         | MICBIAS            | 0                   | Microphone Bias Output. Decouple this pin to AGNDx using a 10 $\mu$ F capacitor.                                                                 |

| 28         | MB_GND             | Р                   | Analog Return Ground for the Microphone Bias Regulator. Connect this pin directly to AGNDx for best noise performance.                           |

| 29         | AGND3              | Р                   | Analog Ground.                                                                                                                                   |

| 30         | VBAT               | 1                   | Voltage Sense for Diagnostics. Connect this pin to a load dump suppressed battery voltage. Decouple this to AGNDx using a 0.1 $\mu F$ capacitor. |

| Pin No. | Mnemonic | In/Out <sup>1</sup> | Description                                                                                            |

|---------|----------|---------------------|--------------------------------------------------------------------------------------------------------|

| 31      | AVDD3    | Р                   | Analog Power Supply. Connect this pin to an analog 3.3 V supply.                                       |

| 32      | AIN1N    | 1                   | Analog Input Channel 1 Inverting Input.                                                                |

| 33      | AIN1P    | 1                   | Analog Input Channel 1 Noninverting Input.                                                             |

| 34      | AIN2N    | 1                   | Analog Input Channel 2 Inverting Input.                                                                |

| 35      | AIN2P    | 1                   | Analog Input Channel 2 Noninverting Input.                                                             |

| 36      | AIN3N    | 1                   | Analog Input Channel 3 Inverting Input.                                                                |

| 37      | AIN3P    | 1                   | Analog Input Channel 3 Noninverting Input.                                                             |

| 38      | AIN4N    | 1                   | Analog Input Channel 4 Inverting Input.                                                                |

| 39      | AIN4P    | 1                   | Analog Input Channel 4 Noninverting Input.                                                             |

| 40      | AVDD1    | Р                   | Analog Power Supply. Connect this pin to an analog 3.3 V supply.                                       |

|         | EP       |                     | Exposed Pad. The exposed pad must be connected to the ground plane on the printed circuit board (PCB). |

$^{1}$  I = input, O = output, I/O = input/output, and P = power.

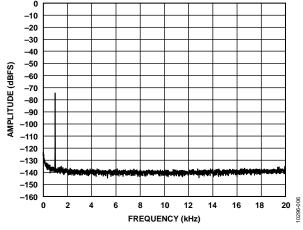

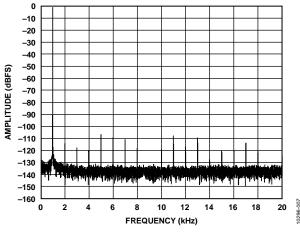

## **TYPICAL PERFORMANCE CHARACTERISTICS**

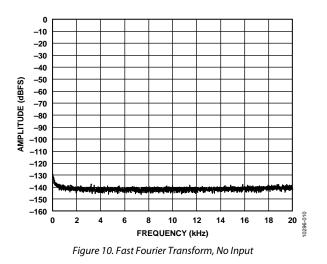

Figure 6. Fast Fourier Transform, 2 mV Differential Input at  $f_s = 48$  kHz

Figure 7. Fast Fourier Transform, -1 dBFS Differential Input

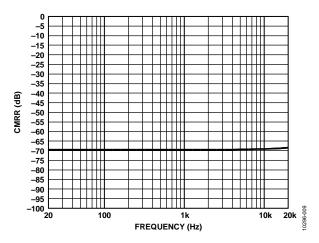

Figure 9. CMRR Differential Input, Referenced to 1 V Differential Input

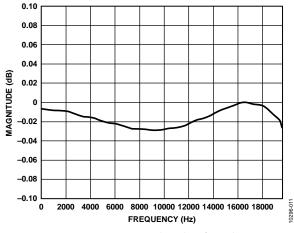

Figure 11. ADC Pass-Band Ripple at  $f_s = 48 \text{ kHz}$

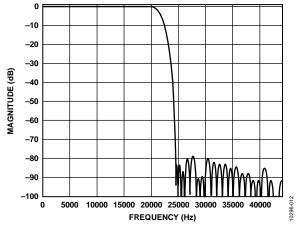

Figure 12. ADC Filter Stop-Band Response at  $f_s = 48 \text{ kHz}$

## THEORY OF OPERATION overview

The ADAU1977 incorporates four high performance ADCs with an integrated boost converter for microphone bias, the associated microphone diagnostics for fault detection, and a phase-locked loop circuit for generating the necessary on-chip clock signals.

### POWER SUPPLY AND VOLTAGE REFERENCE

The ADAU1977 requires a single 3.3 V power supply. Separate power supply input pins are provided for the analog and boost converter. These pins should be decoupled to AGND with 100 nF ceramic chip capacitors placed as close as possible to the pins to minimize noise pickup. A bulk aluminum electrolytic capacitor of at least 10  $\mu$ F must be provided on the same PCB as the ADC. It is important that the analog supply be as clean as possible for best performance.

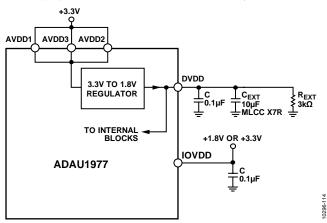

The supply voltage for the digital core (DVDD) is generated using an internal low dropout regulator. The typical DVDD output is 1.8 V and must be decoupled using a 100 nF ceramic capacitor and a 10  $\mu$ F capacitor. Place the 100 nF ceramic capacitor as close as possible to the DVDD pin.

The voltage reference for the analog blocks is generated internally and output at the VREF pin (Pin 2). The typical voltage at the pin is 1.5 V with an AVDDx of 3.3 V.

All digital inputs are compatible with TTL and CMOS levels. All outputs are driven from the IOVDD supply. The IOVDD can be in the range of 1.8 V to 3.3 V. The IOVDD pin must be decoupled with a 100 nF capacitor placed as close to the IOVDD pin as possible. It is recommended to connect the AGND, DGND, PGND, and exposed pad to a single GND plane on the PCB for best performance.

The ADC internal voltage reference is output from the VREF pin and should be decoupled using a 100 nF ceramic capacitor in parallel with a 10  $\mu$ F capacitor. The VREF pin has limited current capability. The voltage reference is used as a reference to the ADC; therefore, it is recommended not to draw current from this pin for external circuits. When using this reference, use a noninverting amplifier buffer to provide a reference to other circuits in the application.

In reset mode, the VREF pin is disabled to save power and is enabled only when the  $\overrightarrow{\text{RST}}$  pin is pulled high.

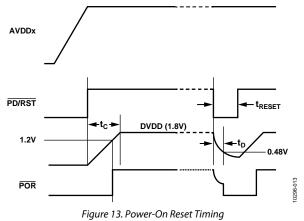

### **POWER-ON RESET SEQUENCE**

The ADAU1977 requires that a single 3.3 V power supply be provided externally at the AVDDx pin. The part internally generates DVDD (1.8 V), which is used for the digital core of the ADC. The DVDD supply output pin (Pin 10) is provided to connect the decoupling capacitors to DGND. The typical recommended values for the decoupling capacitors are 100 nF in parallel with 10  $\mu$ F. During a reset, the DVDD regulator is disabled to reduce power consumption. After the PD/RST pin (Pin 6) is pulled high, the part enables the DVDD regulator. However, the internal ADC and digital core reset is controlled by the internal  $\overrightarrow{POR}$  signal (power-on reset) circuit, which monitors the DVDD level. Therefore, the device does not come out of a reset until DVDD reaches 1.2 V and the  $\overrightarrow{POR}$  signal is released. The DVDD settling time depends on the charge-up time for the external capacitors and on the AVDDx ramp-up time.

The internal POR circuit is provided with hysteresis to ensure that a reset of the part is not initiated by an instantaneous glitch on DVDD. The typical trip points are 1.2 V with  $\overline{\text{RST}}$  high and 0.6 V (±20%) with  $\overline{\text{RST}}$  low. This ensures that the core is not reset until the DVDD level falls below the 0.6 V trip point.

As soon as the  $\overline{PD/RST}$  pin is pulled high, the internal regulator starts charging up the  $C_{EXT}$  on the DVDD pin. The DVDD chargeup time is based on the output resistance of the regulator and the external decoupling capacitor. The time constant can be calculated as

$t_C = R_{OUT} \times C_{EXT} (R_{OUT} = 20 \ \Omega \text{ typical})$

For example, if  $C_{EXT}$  is 10  $\mu F,$  then  $t_{\rm C}$  is 200  $\mu s$  and is the time to reach the DVDD voltage, within 63.6%.

The POR circuit releases an internal reset of the core when DVDD reaches 1.2 V (see Figure 13). Therefore, it is recommended to wait for at least the  $t_{\rm C}$  period to elapse before sending I<sup>2</sup>C or SPI control signals.

When applying a hardware reset to the part by pulling the  $\overline{PD/RST}$  pin (Pin 6) low and then high, there are certain time restrictions. During the  $\overline{RST}$  low pulse period, the DVDD starts discharging. The discharge time constant is decided by the internal resistance of the regulator and C<sub>EXT</sub>. The time required for DVDD to fall from 1.8 V to 0.48 V (0.6 V – 20%) can be estimated using the following equation:

$$t_D = 1.32 \times R_{INT} \times C_{EXT}$$

where  $R_{INT} = 64 \text{ k}\Omega$  typical. ( $R_{INT}$  can vary due to process by ±20%.) For example, if  $C_{EXT}$  is 10 µF, then  $t_D$  is 0.845 sec. Depending on  $C_{EXT}$ ,  $t_D$  may vary and in turn decide the minimum hold period for the  $\overline{RST}$  pulse. The  $\overline{RST}$  pulse must be held low for the  $t_D$  time period to initialize the core properly.

The required  $\overline{RST}$  low pulse period can be reduced by adding a resistor across  $C_{EXT}$ . The new t<sub>D</sub> value can then be calculated as

$$t_D = 1.32 \times R_{EQ} \times C_{EXT}$$

where  $R_{EQ} = 64 \text{ k}\Omega || R_{EXT}$ .

The resistor ensures that DVDD not only discharges quickly during a reset or an AVDDx power loss but also resets the internal blocks correctly. Note that some power loss in this resistor is to be expected because the resistor constantly draws current from DVDD. The typical value for  $C_{EXT}$  is 10 µF and for  $R_{EXT}$  is 3 k $\Omega$ . This results in a time constant of

$t_D = 1.32 \times R_{EQ} \times C_{EXT} = 37.8 \text{ ms}$

where  $R_{EQ} = 2.866 \text{ k}\Omega (64 \text{ k}\Omega \parallel 3 \text{ k}\Omega)$ .

Using this equation at a set  $C_{EXT}$  value, the  $R_{EXT}$  can be calculated for a desired  $\overline{RST}$  pulse period.

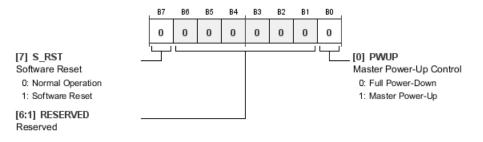

There is also a software reset register (S\_RST, Bit 7 of Register 0x00) available that can be used to reset the part, but it must be noted that during an AVDDx power loss, the software reset may not ensure proper initialization because DVDD may not be stable.

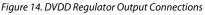

#### PLL AND CLOCK

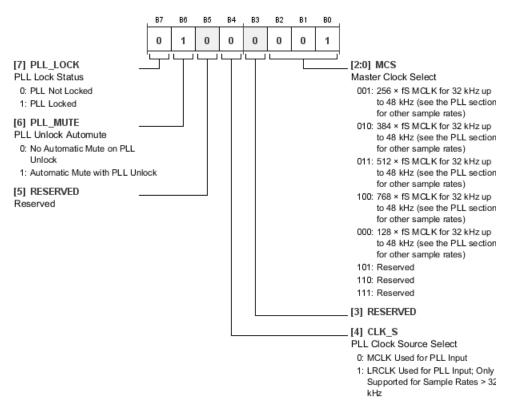

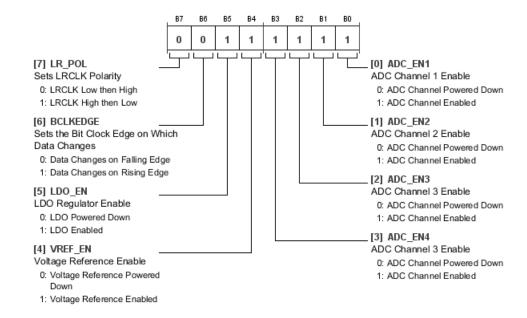

The ADAU1977 has a built-in analog PLL to provide a jitterfree master clock to the internal ADC. The PLL must be programmed for the appropriate input clock frequency. The PLL Control Register 0x01 is used for setting the PLL.

The CLK\_S bit (Bit 4) of Register 0x01 is used for setting the clock source for the PLL. The clock source can be either the MCLKIN pin or the LRCLK pin (slave mode). In LRCLK mode, the PLL can support sample rates between 32 kHz and 192 kHz.

In MCLK input mode, the MCS bits (Bits[2:0] of Register 0x01) must be set to the desired input clock frequency for the MCLKIN pin. Table 10 shows the input MCLK required for the most common sample rates and the MCS bit settings.

The PLL\_LOCK bit (Bit 7) of Register 0x01 indicates the lock status of the PLL. It is recommended that after initial power-up the PLL lock status be read to ensure that the PLL outputs the correct frequency before unmuting the audio outputs.

Table 10. Required Input MCLK for Common Sample Rates

| Table 10. Required input MCER for Common Sample Rates |          |                         |                  |

|-------------------------------------------------------|----------|-------------------------|------------------|

| MCS                                                   |          | Frequency Multi-        | MCLKIN Frequency |

| (Bits[2:0])                                           | fs (kHz) | plication Ratio         | (MHz)            |

| 000                                                   | 32       | 128 × fs                | 4.096            |

| 001                                                   | 32       | <b>256</b> × <b>f</b> s | 8.192            |

| 010                                                   | 32       | <b>384 × f</b> s        | 12.288           |

| 011                                                   | 32       | 512 × fs                | 16.384           |

| 100                                                   | 32       | <b>768 × f</b> s        | 24.576           |

| 000                                                   | 44.1     | 128 × fs                | 5.6448           |

| 001                                                   | 44.1     | <b>256</b> × fs         | 11.2896          |

| 010                                                   | 44.1     | $384 \times f_s$        | 16.9344          |

| 011                                                   | 44.1     | $512 \times f_s$        | 22.5792          |

| 100                                                   | 44.1     | $768 \times f_s$        | 33.8688          |

| 000                                                   | 48       | $128 \times f_s$        | 6.144            |

| 001                                                   | 48       | $256 \times f_s$        | 12.288           |

| 010                                                   | 48       | $384 \times f_s$        | 18.432           |

| 011                                                   | 48       | $512 \times f_s$        | 24.576           |

| 100                                                   | 48       | <b>768</b> × <b>f</b> s | 36.864           |

| 000                                                   | 96       | $64 \times f_s$         | 6.144            |

| 001                                                   | 96       | $128 \times f_s$        | 12.288           |

| 010                                                   | 96       | $192 \times f_s$        | 18.432           |

| 011                                                   | 96       | <b>256</b> × fs         | 24.576           |

| 100                                                   | 96       | $384 \times f_s$        | 36.864           |

| 000                                                   | 192      | $32 \times f_s$         | 6.144            |

| 001                                                   | 192      | $64 \times f_s$         | 12.288           |

| 010                                                   | 192      | $96 \times f_s$         | 18.432           |

| 011                                                   | 192      | 128 × fs                | 24.576           |

| 100                                                   | 192      | 192 × fs                | 36.864           |

The PLL can accept the audio frame clock (sample rate clock) as input, but the serial port must be configured as a slave and the frame clock must be fed to the part from the master. It is strongly recommended that the PLL be disabled, reprogrammed with the new setting, and then reenabled. A lock bit is provided that can be polled via the I<sup>2</sup>C to check whether the PLL has acquired lock.

The PLL requires an external filter, which is connected at the PLL\_FILT pin (Pin 3). The recommended PLL filter circuit for MCLK or LRCLK mode is shown in Figure 15. Using NPO capacitors is recommended for temperature stability. Place the filter components close to the device for best performance.

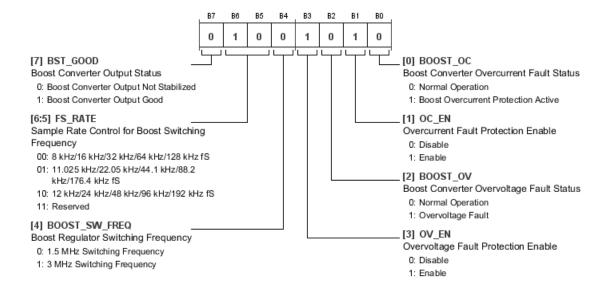

### **DC-TO-DC BOOST CONVERTER**

The boost converter generates a supply voltage for the microphone bias circuit from a fixed 3.3 V supply. The boost converter output voltage is programmable using Register 0x03. The boost converter output voltage is approximately 1 V above the set microphone bias voltage. The boost converter uses the clock from the PLL, and the switching frequency is dependent on the sample rate of the ADC. The FS\_RATE bits (Bits[6:5] of Register 0x02) must be set to the desired sample rate. The boost converter switching frequency can be selected to be 1.5 MHz or 3 MHz using Bit 4 of Register 0x02. For the 1.5 MHz switching frequency, the recommended value for the inductor is 4.7  $\mu$ H, whereas for the 3 MHz switching frequency, the recommended value for the inductor is 2.2  $\mu$ H.

Table 11 lists the typical switching frequency based on the sample rates.

#### **Capacitor Selection**

The boost converter output is available at the VBOOST\_OUT pin (Pin 25) and must be decoupled to PGND using a 10  $\mu$ F ceramic capacitor to remove the ripple at the switching frequency. The capacitor must have low ESR and good temperature stability. The MLCC X7R/NPO dielectric type with 25 V is recommended. Care must be taken to place this capacitor as close as possible to the VBOOST\_OUT pin (Pin 25).

|                        |                              | Boost Converter Switching Frequency |                          |

|------------------------|------------------------------|-------------------------------------|--------------------------|

| Base Sample Rate (kHz) | Sample Rates (kHz)           | Inductor = 2.2 µH                   | Inductor = 4.7 μH        |

| 32                     | 8/16/32/64                   | $(1024/12) \times f_{s}$            | $(1024/22) \times f_{s}$ |

| 44.1                   | 11.025/22.05/44.1/88.2/176.4 | (1024/16) × fs                      | (1024/30) × fs           |

| 48                     | 12/24/48/96/192              | (1024/16) × fs                      | $(1024/32) \times f_{s}$ |

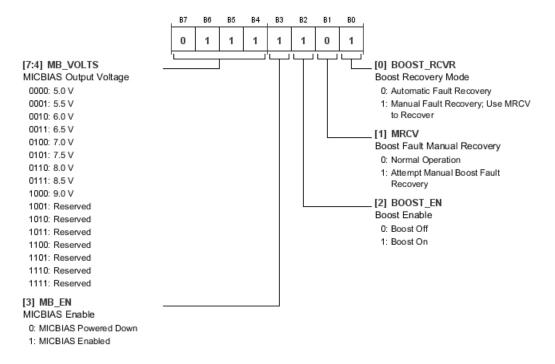

#### **MICROPHONE BIAS**

The microphone bias is generated by the input voltage at the VBOOST\_IN pin (Pin 26) via a linear regulator to ensure low noise performance and to reject the high frequency noise from the boost converter. If the internal boost converter output is used, the VBOOST\_OUT pin (Pin 25) must be connected to the VBOOST\_IN pin (Pin 26). If an external supply is used for the microphone bias, the supply can be fed at the VBOOST\_IN pin (Pin 26); in this case, leave the VBOOST\_OUT pin (Pin 25) open. The microphone bias voltage is programmable from 5 V to 9 V by using the MB\_VOLTS bits (Bits[7:4] of Register 0x03). The microphone bias output voltage is available at the MICBIAS pin (Pin 27). This pin can be decoupled to AGND using a maximum of up to a 10  $\mu$ F capacitor with an ESR of at least 1  $\Omega$ . For higher value capacitors, especially those above 1 nF, the ESR of the capacitor should be  $\geq 1 \Omega$  to ensure the stability of the microphone bias regulator. Register 0x03 can be used to enable the microphone bias. Table 11 lists the switching frequency of the boost converter based on the inductor value and common sample rates.

#### **ANALOG INPUTS**

The ADAU1977 has four differential analog inputs. The ADCs can accommodate both dc- and ac-coupled input signals.

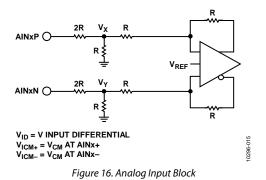

The block diagram shown in Figure 16 represents the typical input circuit.

In most audio applications, the dc content of the signal is removed by using a coupling capacitor. However, the ADAU1977 consists of a unique input structure that allows direct coupling of the input signal, eliminating the need for using a large coupling capacitor at the input. Each input has a fixed 14 dB attenuator connected to AGND for accommodating a 10 V rms differential input. The typical input resistance is approximately 26 k $\Omega$  from each input to AGND.

In dc-coupled applications, if the  $V_{CM}$  at AINxP and AINxN is the same, the dc content in the ADC output is close to 0. If the input pins are presented with different common-mode dc levels, the difference between the two levels appears at the ADC output and can be removed by enabling the high-pass filter.

The high-pass filter has a 1.4 Hz, 6 dB per octave cutoff at a 48 kHz sample rate. The cutoff frequency scales directly with the sample frequency. However, care is required in dc-coupled applications to ensure that the common-mode dc voltage does not exceed the specified limit. The common-mode loop can accommodate a common-mode dc voltage from 0 V to 7 V. The input required for the full-scale ADC output (0 dBFS) is typically 10 V rms differential.

#### Line Inputs

This section describes some of the possible ways to connect the ADAU1977 for line level inputs.

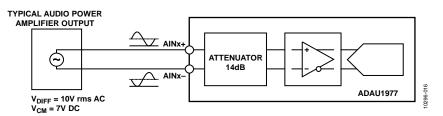

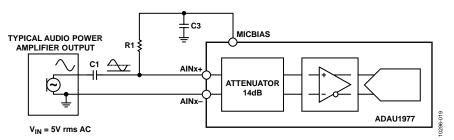

#### Line Input Balanced or Differential Input DC-Coupled Case

For example, in the case of a typical power amplifier for an automobile, the output can swing around 10 V rms differential with approximately 7.2 V common-mode dc input voltage (assuming a 14.4 V battery and bridge-tied load connection). The signal at each input pin has a 5 V rms or 14.14 V p-p signal swing. With a common-mode dc voltage of 7.2 V, the signal can swing between (7.2 V + 7.07 V) = +14.27 V p-p and (7 V - 7.07 V) = 0.13 V at each input. Therefore, this results in approximately a 28.54 V p-p differential signal swing and measures around -0.16 dBFS (ac only with dc high-pass filter) at the ADC output. See Figure 17.

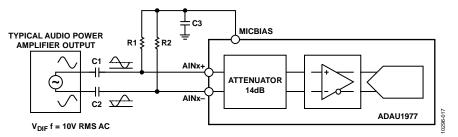

#### Line Input Balanced or Differential Input AC-Coupled Case

For an amplifier output case with ac coupling, refer to Figure 18 for information about connecting the line level inputs to the ADAU1977. In this case, the AINxP/AINxN pins must be pulled up to the required common-mode level using the resistors on MICBIAS. The  $V_{CM}$  must be such that the input never swings below a ground. In other words, if the input signal is 14 V p-p, the  $V_{CM}$  must be around 14 V/2 = 7 V to ensure that the signal never swings below a ground. The microphone bias can provide the required clean reference for generating the  $V_{CM}$ .

The R1 value can be calculated as follows:

$R1 = Rin_{1977} (MB - V_{CM})/V_{CM}$

where:

$V_{CM}$  is the peak-to-peak input swing divided by 2.  $MB=8.5~{\rm V}.$

Rin1977 is the single-ended input resistance (see Table 1).

However, in this case the equivalent input resistance of AINxP/ AINxN is reduced and can be calculated as R1 || Rin<sub>1977</sub>.

Input Resistance =  $R1 \times Rin_{1977}/(R1 + Rin_{1977})$

where *Rin*<sub>1977</sub> is the single-ended value from Table 1.

The C1 and C2 values can be determined for the required low frequency cutoff using the following equation:

*C1* or *C2* =  $1/(2 \times \pi \times f_C \times Input Resistance)$

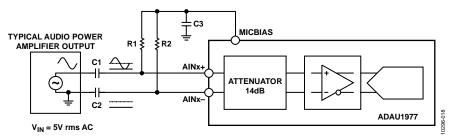

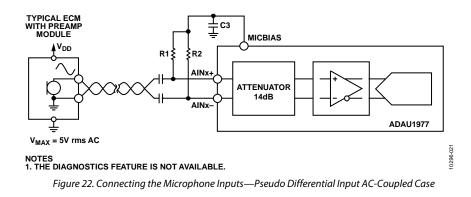

# Line Input Unbalanced or Single-Ended Pseudo Differential AC-Coupled Case

For a single-ended application, the signal swing is reduced by half because only one input is used for the signal, and the other input is connected to 0 V. As a result, the input signal capability is reduced to 5 V rms in a single-ended application. With a common-mode dc voltage of 7.2 V, the signal can swing between (7.2 V + 7.07 V)= +14.27 V p-p and (7.2 V - 7 V) = 0.13 V. Therefore, this results in approximately a 14.14 V p-p differential signal swing and measures around -6.16 dBFS (ac only with dc high-pass filter) at the ADC output. See Figure 19.

The values of the resistors (R1/R2) and capacitors (C1/C2) are similar to those for the balanced ac-coupled case described in the Line Input Balanced or Differential Input AC-Coupled Case section.

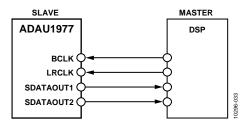

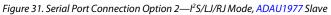

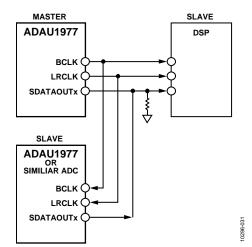

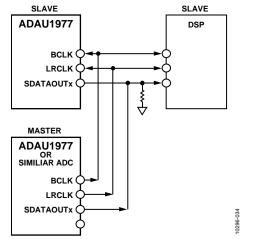

#### Line Input Unbalanced or Single-Ended AC-Coupled Case