# ANALOG DEVICES

# 1.6 GHz Clock Distribution IC, Dividers, Delay Adjust, Two Outputs

### **Data Sheet**

### **FEATURES**

1.6 GHz differential clock input

2 programmable dividers

Divide-by in range from1 to 32

Phase select for coarse delay adjust

1.6 GHz LVPECL clock output

Additive output jitter 225 fs rms

800 MHz/250 MHz LVDS/CMOS clock output

Additive output jitter 300 fs rms/290 fs rms

Time delays up to 10 ns

Device configured with 4-level logic pins

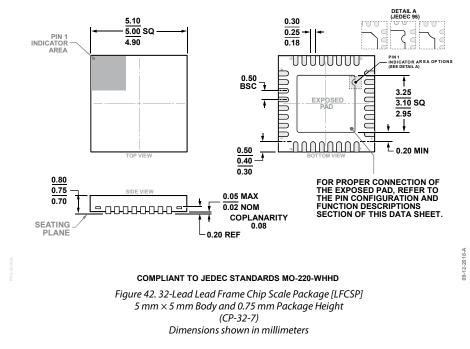

Space-saving, 32-lead LFCSP

### **APPLICATIONS**

Low jitter, low phase noise clock distribution Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceivers High performance instrumentation Broadband infrastructure ATE

### **GENERAL DESCRIPTION**

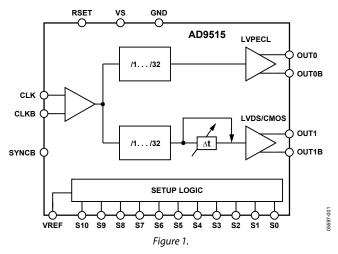

The AD9515 features a two-output clock distribution IC in a design that emphasizes low jitter and phase noise to maximize data converter performance. Other applications with demanding phase noise and jitter requirements also benefit from this part.

There are two independent clock outputs. One output is LVPECL, while the other output can be set to either LVDS or CMOS levels. The LVPECL output operates to 1.6 GHz. The other output operates to 800 MHz in LVDS mode and to 250 MHz in CMOS mode.

Each output has a programmable divider that can be set to divide by a selected set of integers ranging from 1 to 32. The phase of one clock output relative to the other clock output can be set by means of a divider phase select function that serves as a coarse timing adjustment.

### FUNCTIONAL BLOCK DIAGRAM

AD9515

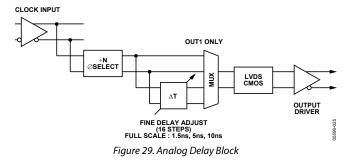

The LVDS/CMOS output features a delay element with three selectable full-scale delay values (1.5 ns, 5 ns, and 10 ns), each with 16 steps of fine adjustment.

The AD9515 does not require an external controller for operation or setup. The device is programmed by means of 11 pins (S0 to S10) using 4-level logic. The programming pins are internally biased to  $\frac{1}{3}$  Vs. The VREF pin provides a level of  $\frac{2}{3}$  Vs. Vs (3.3 V) and GND (0 V) provide the other two logic levels.

The AD9515 is ideally suited for data converter clocking applications where maximum converter performance is achieved by encode signals with subpicosecond jitter.

The AD9515 is available in a 32-lead LFCSP and operates from a single 3.3 V supply. The temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Rev. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

© 2005–2020 Analog Devices, Inc. All rights reserved.

## TABLE OF CONTENTS

| Features 1                                  |

|---------------------------------------------|

| Applications 1                              |

| Functional Block Diagram 1                  |

| General Description                         |

| Revision History                            |

| Specifications                              |

| Clock Input 3                               |

| Clock Outputs                               |

| Timing Characteristics 4                    |

| Clock Output Phase Noise5                   |

| Clock Output Additive Time Jitter 8         |

| SYNCB, VREF, and Setup Pins9                |

| Power                                       |

| Timing Diagrams11                           |

| Absolute Maximum Ratings 12                 |

| Thermal Characteristics12                   |

| ESD Caution12                               |

| Pin Configuration and Function Descriptions |

| Terminology14                               |

| Typical Performance Characteristics15       |

| Functional Description                      |

| Overall                                     |

| CLK, CLKB—Differential Clock Input18        |

|   | Synchronization                                                  | 18 |

|---|------------------------------------------------------------------|----|

|   | R <sub>SET</sub> Resistor                                        | 19 |

|   | VREF                                                             | 19 |

|   | Setup Configuration                                              | 19 |

| P | rogramming                                                       | 20 |

|   | Divider Phase Offset                                             | 22 |

|   | Delay Block                                                      | 22 |

|   | Outputs                                                          | 23 |

|   | Power Supply                                                     | 23 |

|   | Power Management                                                 | 24 |

| A | pplications                                                      | 25 |

|   | Using the AD9515 Outputs for ADC Clock Applications              | 25 |

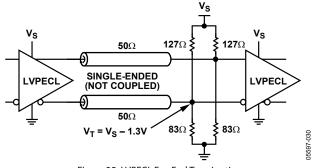

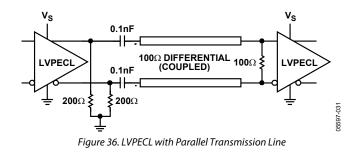

|   | LVPECL Clock Distribution                                        | 25 |

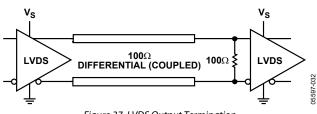

|   | LVDS Clock Distribution                                          | 26 |

|   | CMOS Clock Distribution                                          | 26 |

|   | Setup Pins (S0 to S10)                                           | 26 |

|   | Power and Grounding Considerations and Power Supply<br>Rejection | 26 |

|   | Phase Noise and Jitter Measurement Setups                        | 27 |

| 0 | Outline Dimensions                                               | 28 |

|   | Ordering Guide                                                   | 28 |

### **REVISION HISTORY**

| 9/2020—Rev. A to Rev. B                           |          |

|---------------------------------------------------|----------|

| Changed CP-32-2 to CP-32-7 Th                     | roughout |

| Changes to Pin Configuration Section and Figure 6 | 13       |

| Deleted Figure 7; Renumbered Sequentially         | 13       |

| Updated Outline Dimensions                        |          |

| Changes to Ordering Guide                         |          |

### 4/2012—Rev. 0 to Rev. A

| Changes to Table 9         | 13 |

|----------------------------|----|

| Updated Outline Dimensions | 28 |

| Changes to Ordering Guide  | 28 |

7/2005—Revision 0: Initial Version

## **SPECIFICATIONS**

Typical (typ) is given for  $V_s = 3.3 \text{ V} \pm 5\%$ ,  $T_A = 25^{\circ}\text{C}$ ,  $R_{\text{SET}} = 4.12 \text{ k}\Omega$ , LVPECL swing = 790 mV, unless otherwise noted. Minimum (min) and maximum (max) values are given over full  $V_s$  and  $T_A$  (-40°C to +85°C) variation.

### **CLOCK INPUT**

| Parameter                                  | Min | Тур | Мах | Unit   | Test Conditions/Comments                      |

|--------------------------------------------|-----|-----|-----|--------|-----------------------------------------------|

| CLOCK INPUT (CLK)                          |     |     |     |        |                                               |

| Input Frequency <sup>1</sup>               | 0   |     | 1.6 | GHz    |                                               |

| Input Sensitivity <sup>1</sup>             |     | 150 |     | mV p-p |                                               |

| Input Common-Mode Voltage, V <sub>CM</sub> | 1.5 | 1.6 | 1.7 | V      | Self-biased; enables ac coupling              |

| Input Common-Mode Range, V <sub>CMR</sub>  | 1.3 |     | 1.8 | V      | With 200 mV p-p signal applied; dc-coupled    |

| Input Sensitivity, Single-Ended            |     | 150 |     | mV p-p | CLK ac-coupled; CLKB ac-bypassed to RF ground |

| Input Resistance                           | 4.0 | 4.8 | 5.6 | kΩ     | Self-biased                                   |

| Input Capacitance                          |     | 2   |     | pF     |                                               |

<sup>1</sup>A slew rate of 1 V/ns is required to meet jitter, phase noise, and propagation delay specifications.

### **CLOCK OUTPUTS**

### Table 2.

| Parameter                                                  | Min       | Тур            | Мах            | Unit | Test Conditions/Comments                          |

|------------------------------------------------------------|-----------|----------------|----------------|------|---------------------------------------------------|

| LVPECL CLOCK OUTPUT                                        |           |                |                |      | Termination = 50 $\Omega$ to V <sub>s</sub> – 2 V |

| (OUT0) Differential                                        |           |                |                |      |                                                   |

| Output Frequency                                           | 0         |                | 1.6            | GHz  |                                                   |

| Output High Voltage (V <sub>он</sub> )                     | Vs - 1.1  | $V_{s} - 0.96$ | $V_{s} - 0.82$ | V    |                                                   |

| Output Low Voltage (Vol)                                   | Vs - 1.90 | Vs – 1.76      | Vs – 1.52      | V    |                                                   |

| Output Differential Voltage ( $V_{OD}$ )                   | 640       | 790            | 960            | mV   |                                                   |

| LVDS CLOCK OUTPUT                                          |           |                |                |      | Termination = 100 $\Omega$ differential           |

| (OUT1) Differential                                        |           |                |                |      |                                                   |

| Output Frequency                                           | 0         |                | 800            | MHz  |                                                   |

| Differential Output Voltage (V <sub>OD</sub> )             | 250       | 350            | 450            | mV   |                                                   |

| Delta V <sub>OD</sub>                                      |           |                | 30             | mV   |                                                   |

| Output Offset Voltage (Vos)                                | 1.125     | 1.23           | 1.375          | V    |                                                   |

| Delta Vos                                                  |           |                | 25             | mV   |                                                   |

| Short-Circuit Current (I <sub>SA</sub> , I <sub>SB</sub> ) |           | 14             | 24             | mA   | Output shorted to GND                             |

| CMOS CLOCK OUTPUT                                          |           |                |                |      | Single-ended measurements; termination open       |

| (OUT1) Single-Ended                                        |           |                |                |      | Complementary output on (OUT1B)                   |

| Output Frequency                                           | 0         |                | 250            | MHz  | With 5 pF load                                    |

| Output Voltage High (Vон)                                  | Vs - 0.1  |                |                | V    | @ 1 mA load                                       |

| Output Voltage Low (Vol)                                   |           |                | 0.1            | V    | @ 1 mA load                                       |

### TIMING CHARACTERISTICS

CLK input slew rate = 1 V/ns or greater.

### Table 3.

| Parameter                                                        | Min  | Тур   | Мах  | Unit  | Test Conditions/Comments                          |

|------------------------------------------------------------------|------|-------|------|-------|---------------------------------------------------|

| LVPECL                                                           |      |       |      |       | Termination = 50 $\Omega$ to V <sub>s</sub> – 2 V |

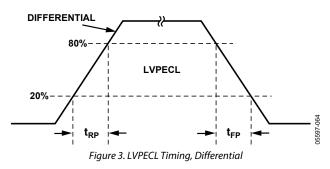

| Output Rise Time, t <sub>RP</sub>                                |      | 60    | 100  | ps    | 20% to 80%, measured differentially               |

| Output Fall Time, t <sub>FP</sub>                                |      | 60    | 100  | ps    | 80% to 20%, measured differentially               |

| PROPAGATION DELAY, tPECL, CLK-TO-LVPECL OUT                      |      |       |      |       |                                                   |

| Divide = 1                                                       | 355  | 480   | 635  | ps    |                                                   |

| Divide = 2 - 32                                                  | 395  | 530   | 710  | ps    |                                                   |

| Variation with Temperature                                       |      | 0.5   |      | ps/°C |                                                   |

| OUTPUT SKEW, LVPECL OUTPUT                                       |      |       |      |       |                                                   |

| LVPECL OUT Across Multiple Parts, t <sub>SKP_AB3</sub> 1         |      |       | 125  | ps    |                                                   |

| LVDS                                                             |      |       |      |       | Termination = $100 \Omega$ differential           |

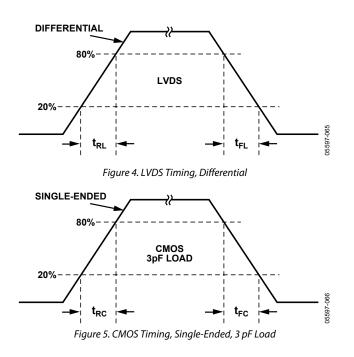

| Output Rise Time, t <sub>RL</sub>                                |      | 200   | 350  | ps    | 20% to 80%, measured differentially               |

| Output Fall Time, t <sub>FL</sub>                                |      | 210   | 350  | ps    | 80% to 20%, measured differentially               |

| PROPAGATION DELAY, t <sub>LVDS</sub> , CLK-TO-LVDS OUT           |      |       |      | -     | Delay off on OUT4                                 |

| OUT3 to OUT4                                                     |      |       |      |       |                                                   |

| Divide = 1                                                       | 1.00 | 1.25  | 1.55 | ns    |                                                   |

| Divide = 2 - 32                                                  | 1.05 | 1.30  | 1.60 | ns    |                                                   |

| Variation with Temperature                                       |      | 0.9   |      | ps/°C |                                                   |

| OUTPUT SKEW, LVDS OUTPUT                                         |      |       |      |       | Delay off on OUT4                                 |

| LVDS OUT Across Multiple Parts, tskv_AB <sup>1</sup>             |      |       | 230  | ps    |                                                   |

| CMOS                                                             |      |       |      | -     | B outputs are inverted; termination = open        |

| Output Rise Time, t <sub>RC</sub>                                |      | 650   | 865  | ps    | 20% to 80%; C <sub>LOAD</sub> = 3 pF              |

| Output Fall Time, t <sub>FC</sub>                                |      | 650   | 990  | ps    | 80% to 20%; C <sub>LOAD</sub> = 3 pF              |

| PROPAGATION DELAY, t <sub>CMOS</sub> , CLK-TO-CMOS OUT           |      |       |      | -     | Delay off on OUT4                                 |

| Divide = 1                                                       | 1.10 | 1.45  | 1.75 | ns    |                                                   |

| Divide = 2 – 32                                                  | 1.15 | 1.50  | 1.80 | ns    |                                                   |

| Variation with Temperature                                       |      | 1     |      | ps/°C |                                                   |

| OUTPUT SKEW, CMOS OUTPUT                                         |      |       |      | -     | Delay off on OUT4                                 |

| CMOS OUT Across Multiple Parts, t <sub>SKC_AB</sub> <sup>1</sup> |      |       | 300  | ps    |                                                   |

| LVPECL-TO-LVDS OUT                                               |      |       |      |       | Everything the same; different logic type         |

| Output Delay, t <sub>SKP_V</sub>                                 | 700  | 970   | 1150 | ps    | LVPECL to LVDS on same part                       |

| LVPECL-TO-CMOS OUT                                               |      |       |      |       | Everything the same; different logic type         |

| Output Delay, t <sub>skP_C</sub>                                 | 0.88 | 1.14  | 1.43 | ns    | LVPECL to CMOS on same part                       |

| DELAY ADJUST (OUT2; LVDS AND CMOS)                               |      |       |      |       |                                                   |

| S0 = 1/3                                                         |      |       |      |       |                                                   |

| Zero Scale Delay Time <sup>2</sup>                               |      | 0.34  |      | ns    |                                                   |

| Zero Scale Variation with Temperature                            |      | 0.20  |      | ps/°C |                                                   |

| Full Scale Time Delay <sup>2</sup>                               |      | 1.7   |      | ns    |                                                   |

| Full Scale Variation with Temperature                            |      | -0.38 |      | ps/°C |                                                   |

| S0 = 2/3                                                         |      |       |      |       |                                                   |

| Zero Scale Delay Time <sup>2</sup>                               |      | 0.45  |      | ns    |                                                   |

| Zero Scale Variation with Temperature                            |      | 0.31  |      | ps/°C |                                                   |

| Full Scale Time Delay <sup>2</sup>                               |      | 5.9   |      | ns    |                                                   |

| Full Scale Variation with Temperature                            |      | -1.3  |      | ps/°C |                                                   |

AD9515

| Parameter                             | Min | Тур  | Max | Unit  | Test Conditions/Comments |

|---------------------------------------|-----|------|-----|-------|--------------------------|

| S0 = 1                                |     |      |     |       |                          |

| Zero Scale Delay Time <sup>2</sup>    |     | 0.56 |     | ns    |                          |

| Zero Scale Variation with Temperature |     | 0.47 |     | ps/°C |                          |

| Full Scale Time Delay <sup>2</sup>    |     | 11.4 |     | ns    |                          |

| Full Scale Variation with Temperature |     | -5   |     | ps/°C |                          |

| Linearity, DNL                        |     | 0.2  |     | LSB   |                          |

| Linearity, INL                        |     | 0.2  |     | LSB   |                          |

<sup>1</sup> This is the difference between any two similar delay paths across multiple devices operating at the same voltage and temperature. <sup>2</sup> Incremental delay; does not include propagation delay.

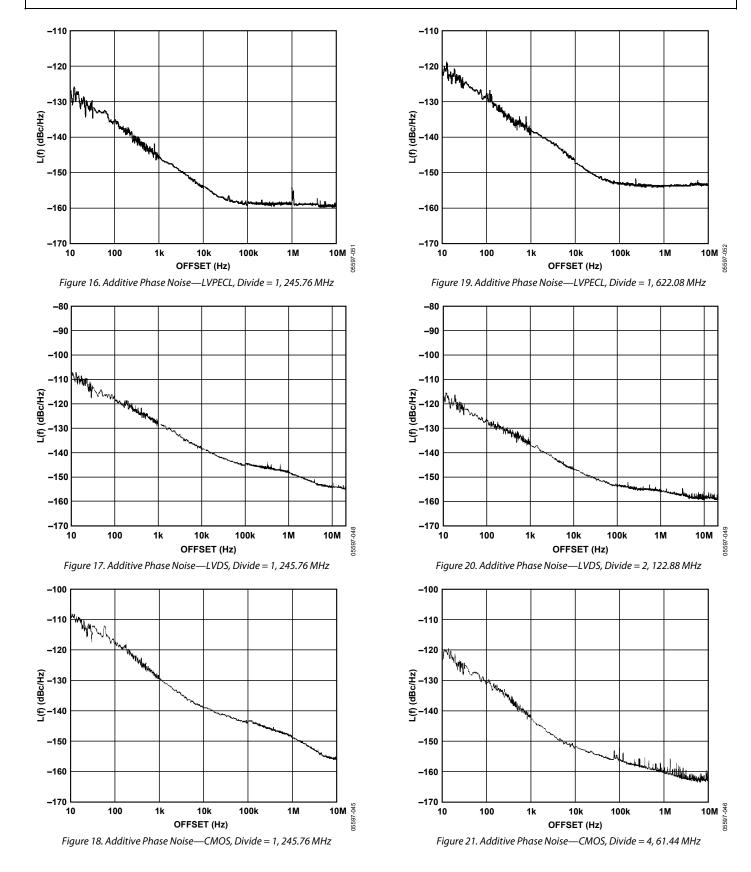

### **CLOCK OUTPUT PHASE NOISE**

CLK input slew rate = 1 V/ns or greater.

| Parameter                          | Min | Тур  | Max | Unit   | Test Conditions/Comments |

|------------------------------------|-----|------|-----|--------|--------------------------|

| CLK-TO-LVPECL ADDITIVE PHASE NOISE |     |      |     |        |                          |

| CLK = 622.08 MHz, OUT = 622.08 MHz |     |      |     |        |                          |

| Divide = 1                         |     |      |     |        |                          |

| @ 10 Hz Offset                     |     | -125 |     | dBc/Hz |                          |

| @ 100 Hz Offset                    |     | -132 |     | dBc/Hz |                          |

| @ 1 kHz Offset                     |     | -140 |     | dBc/Hz |                          |

| @ 10 kHz Offset                    |     | -148 |     | dBc/Hz |                          |

| @ 100 kHz Offset                   |     | -153 |     | dBc/Hz |                          |

| >1 MHz Offset                      |     | -154 |     | dBc/Hz |                          |

| CLK = 622.08 MHz, OUT = 155.52 MHz |     |      |     |        |                          |

| Divide = 4                         |     |      |     |        |                          |

| @ 10 Hz Offset                     |     | -128 |     | dBc/Hz |                          |

| @ 100 Hz Offset                    |     | -140 |     | dBc/Hz |                          |

| @ 1 kHz Offset                     |     | -148 |     | dBc/Hz |                          |

| @ 10 kHz Offset                    |     | -155 |     | dBc/Hz |                          |

| @ 100 kHz Offset                   |     | -161 |     | dBc/Hz |                          |

| >1 MHz Offset                      |     | -161 |     | dBc/Hz |                          |

| CLK = 622.08 MHz, OUT = 38.88 MHz  |     |      |     |        |                          |

| Divide = 16                        |     |      |     |        |                          |

| @ 10 Hz Offset                     |     | -135 |     | dBc/Hz |                          |

| @ 100 Hz Offset                    |     | -145 |     | dBc/Hz |                          |

| @ 1 kHz Offset                     |     | -158 |     | dBc/Hz |                          |

| @ 10 kHz Offset                    |     | -165 |     | dBc/Hz |                          |

| @ 100 kHz Offset                   |     | -165 |     | dBc/Hz |                          |

| >1 MHz Offset                      |     | -166 |     | dBc/Hz |                          |

| CLK = 491.52 MHz, OUT = 61.44 MHz  |     |      |     |        |                          |

| Divide = 8                         |     |      |     |        |                          |

| @ 10 Hz Offset                     |     | -131 |     | dBc/Hz |                          |

| @ 100 Hz Offset                    |     | -142 |     | dBc/Hz |                          |

| @ 1 kHz Offset                     |     | -153 |     | dBc/Hz |                          |

| @ 10 kHz Offset                    |     | -160 |     | dBc/Hz |                          |

| @ 100 kHz Offset                   |     | -165 |     | dBc/Hz |                          |

| > 1 MHz Offset                     |     | -165 |     | dBc/Hz |                          |

## AD9515

| Parameter                          | Min Typ | Max Unit | Test Conditions/Comments |

|------------------------------------|---------|----------|--------------------------|

| CLK = 491.52 MHz, OUT = 245.76 MHz |         |          |                          |

| Divide = 2                         |         |          |                          |

| @ 10 Hz Offset                     | -125    | dBc/Hz   |                          |

| @ 100 Hz Offset                    | -132    | dBc/Hz   |                          |

| @ 1 kHz Offset                     | -140    | dBc/Hz   |                          |

| @ 10 kHz Offset                    | -151    | dBc/Hz   |                          |

| @ 100 kHz Offset                   | -157    | dBc/Hz   |                          |

| >1 MHz Offset                      | -158    | dBc/Hz   |                          |

| CLK = 245.76 MHz, OUT = 61.44 MHz  |         |          |                          |

| Divide = 4                         |         |          |                          |

| @ 10 Hz Offset                     | -138    | dBc/Hz   |                          |

| @ 100 Hz Offset                    | -144    | dBc/Hz   |                          |

| @ 1 kHz Offset                     | -154    | dBc/Hz   |                          |

| @ 10 kHz Offset                    | -163    | dBc/Hz   |                          |

| @ 100 kHz Offset                   | -164    | dBc/Hz   |                          |

| >1 MHz Offset                      | -165    | dBc/Hz   |                          |

| CLK-TO-LVDS ADDITIVE PHASE NOISE   |         |          |                          |

| CLK = 622.08 MHz, OUT= 622.08 MHz  |         |          |                          |

| Divide = 1                         |         |          |                          |

| @ 10 Hz Offset                     | -100    | dBc/Hz   |                          |

| @ 100 Hz Offset                    | -110    | dBc/Hz   |                          |

| @ 1 kHz Offset                     | -118    | dBc/Hz   |                          |

| @ 10 kHz Offset                    | -129    | dBc/Hz   |                          |

| @ 100 kHz Offset                   | -135    | dBc/Hz   |                          |

| @ 1 MHz Offset                     | -140    | dBc/Hz   |                          |

| >10 MHz Offset                     | -148    | dBc/Hz   |                          |

| CLK = 622.08 MHz, OUT = 155.52 MHz |         |          |                          |

| Divide = 4                         |         |          |                          |

| @ 10 Hz Offset                     | -112    | dBc/Hz   |                          |

| @ 100 Hz Offset                    | -122    | dBc/Hz   |                          |

| @ 1 kHz Offset                     | -132    | dBc/Hz   |                          |

| @ 10 kHz Offset                    | -142    | dBc/Hz   |                          |

| @ 100 kHz Offset                   | -148    | dBc/Hz   |                          |

| @ 1 MHz Offset                     | -152    | dBc/Hz   |                          |

| >10 MHz Offset                     | -155    | dBc/Hz   |                          |

| CLK = 491.52 MHz, OUT = 245.76 MHz |         |          |                          |

| Divide = 2                         |         |          |                          |

| @ 10 Hz Offset                     | -108    | dBc/Hz   |                          |

| @ 100 Hz Offset                    | -118    | dBc/Hz   |                          |

| @ 1 kHz Offset                     | -128    | dBc/Hz   |                          |

| @ 10 kHz Offset                    | -138    | dBc/Hz   |                          |

| @ 100 kHz Offset                   | -145    | dBc/Hz   |                          |

| @ 1 MHz Offset                     | -148    | dBc/Hz   |                          |

| >10 MHz Offset                     | -154    | dBc/Hz   |                          |

| Parameter                          | Min | Тур          | Max | Unit   | <b>Test Conditions/Comments</b> |

|------------------------------------|-----|--------------|-----|--------|---------------------------------|

| CLK = 491.52 MHz, OUT = 122.88 MHz |     |              |     |        |                                 |

| Divide = 4                         |     |              |     |        |                                 |

| @ 10 Hz Offset                     |     | -118         |     | dBc/Hz |                                 |

| @ 100 Hz Offset                    |     | -129         |     | dBc/Hz |                                 |

| @ 1 kHz Offset                     |     | -136         |     | dBc/Hz |                                 |

| @ 10 kHz Offset                    |     | -147         |     | dBc/Hz |                                 |

| @ 100 kHz Offset                   |     | -153         |     | dBc/Hz |                                 |

| @ 1 MHz Offset                     |     | -156         |     | dBc/Hz |                                 |

| >10 MHz Offset                     |     | -158         |     | dBc/Hz |                                 |

| CLK = 245.76 MHz, OUT = 245.76 MHz |     |              |     |        |                                 |

| Divide = 1                         |     |              |     |        |                                 |

| @ 10 Hz Offset                     |     | -108         |     | dBc/Hz |                                 |

| @ 100 Hz Offset                    |     | -118         |     | dBc/Hz |                                 |

| @ 1 kHz Offset                     |     | -128         |     | dBc/Hz |                                 |

| @ 10 kHz Offset                    |     | -138         |     | dBc/Hz |                                 |

| @ 100 kHz Offset                   |     | -145         |     | dBc/Hz |                                 |

| @ 1 MHz Offset                     |     | -148         |     | dBc/Hz |                                 |

| >10 MHz Offset                     |     | -155         |     | dBc/Hz |                                 |

| CLK = 245.76 MHz, OUT = 122.88 MHz |     |              |     |        |                                 |

| Divide = 2                         |     |              |     |        |                                 |

| @ 10 Hz Offset                     |     | -118         |     | dBc/Hz |                                 |

| @ 100 Hz Offset                    |     | -127         |     | dBc/Hz |                                 |

| @ 1 kHz Offset                     |     | -137         |     | dBc/Hz |                                 |

| @ 10 kHz Offset                    |     | -147         |     | dBc/Hz |                                 |

| @ 100 kHz Offset                   |     | -154         |     | dBc/Hz |                                 |

| @ 1 MHz Offset                     |     | -156         |     | dBc/Hz |                                 |

| >10 MHz Offset                     |     | -158         |     | dBc/Hz |                                 |

| LK-TO-CMOS ADDITIVE PHASE NOISE    |     |              |     |        |                                 |

| CLK = 245.76 MHz, OUT = 245.76 MHz |     |              |     |        |                                 |

| Divide = 1                         |     |              |     |        |                                 |

| @ 10 Hz Offset                     |     | -110         |     | dBc/Hz |                                 |

| @ 100 Hz Offset                    |     | -121         |     | dBc/Hz |                                 |

| @ 1 kHz Offset                     |     | -130         |     | dBc/Hz |                                 |

| @ 10 kHz Offset                    |     | -140         |     | dBc/Hz |                                 |

| @ 100 kHz Offset                   |     | -145         |     | dBc/Hz |                                 |

| @ 1 MHz Offset                     |     | -149         |     | dBc/Hz |                                 |

| >10 MHz Offset                     |     | -156         |     | dBc/Hz |                                 |

| CLK = 245.76 MHz, OUT = 61.44 MHz  |     |              |     |        |                                 |

| Divide = 4                         |     |              |     |        |                                 |

| @ 10 Hz Offset                     |     | -125         |     | dBc/Hz |                                 |

| @ 100 Hz Offset                    |     | -132         |     | dBc/Hz |                                 |

| @ 1 kHz Offset                     |     | -143         |     | dBc/Hz |                                 |

| @ 10 kHz Offset                    |     | -152         |     | dBc/Hz |                                 |

| @ 100 kHz Offset                   |     | -152         |     | dBc/Hz |                                 |

| @ 1 MHz Offset                     |     | -158<br>-160 |     | dBc/Hz |                                 |

| >10 MHz Offset                     |     | -162         |     | dBc/Hz |                                 |

## AD9515

| Parameter                            | Min Typ | Мах | Unit   | Test Conditions/Comments |

|--------------------------------------|---------|-----|--------|--------------------------|

| CLK = 78.6432 MHz, OUT = 78.6432 MHz |         |     |        |                          |

| Divide = 1                           |         |     |        |                          |

| @ 10 Hz Offset                       | -122    |     | dBc/Hz |                          |

| @ 100 Hz Offset                      | -132    |     | dBc/Hz |                          |

| @ 1 kHz Offset                       | -140    |     | dBc/Hz |                          |

| @ 10 kHz Offset                      | -150    |     | dBc/Hz |                          |

| @ 100 kHz Offset                     | -155    |     | dBc/Hz |                          |

| @ 1 MHz Offset                       | -158    |     | dBc/Hz |                          |

| >10 MHz Offset                       | -160    |     | dBc/Hz |                          |

| CLK = 78.6432 MHz, OUT = 39.3216 MHz |         |     |        |                          |

| Divide = 2                           |         |     |        |                          |

| @ 10 Hz Offset                       | -128    |     | dBc/Hz |                          |

| @ 100 Hz Offset                      | -136    |     | dBc/Hz |                          |

| @ 1 kHz Offset                       | -146    |     | dBc/Hz |                          |

| @ 10 kHz Offset                      | -155    |     | dBc/Hz |                          |

| @ 100 kHz Offset                     | –161    |     | dBc/Hz |                          |

| >1 MHz Offset                        | -162    |     | dBc/Hz |                          |

### CLOCK OUTPUT ADDITIVE TIME JITTER

| Table 5.                           |        |       |        |                                   |  |  |

|------------------------------------|--------|-------|--------|-----------------------------------|--|--|

| Parameter                          | Min Ty | o Max | Unit   | Test Conditions/Comments          |  |  |

| LVPECL OUTPUT ADDITIVE TIME JITTER |        |       |        |                                   |  |  |

| CLK = 622.08 MHz                   | 40     |       | fs rms | BW = 12 kHz – 20 MHz (OC-12)      |  |  |

| LVPECL (OUT0) = 622.08 MHz         |        |       |        | OUT1 off                          |  |  |

| Divide = 1                         |        |       |        |                                   |  |  |

| CLK = 622.08 MHz                   | 55     |       | fs rms | BW = 12 kHz – 20 MHz (OC-3)       |  |  |

| LVPECL (OUT0) = 155.52 MHz         |        |       |        | OUT1 off                          |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| CLK = 400 MHz                      | 215    | i     | fs rms | Calculated from SNR of ADC method |  |  |

| LVPECL (OUT0) = 100 MHz            |        |       |        | OUT1 off                          |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| CLK = 400 MHz                      | 215    | ;     | fs rms | Calculated from SNR of ADC method |  |  |

| LVPECL (OUT0) = 100 MHz            |        |       |        |                                   |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| LVDS (OUT1) = 100 MHz              |        |       |        | Interferer                        |  |  |

| CLK = 400 MHz                      | 225    | ;     | fs rms | Calculated from SNR of ADC method |  |  |

| LVPECL (OUT0) = 100 MHz            |        |       |        |                                   |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| LVDS (OUT1) = 50 MHz               |        |       |        | Interferer                        |  |  |

| CLK = 400  MHz                     | 230    | )     | fs rms | Calculated from SNR of ADC method |  |  |

| LVPECL (OUT0) = 100 MHz            |        |       |        |                                   |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| CMOS (OUT1) = 50 MHz               |        |       |        | Interferer                        |  |  |

| LVDS OUTPUT ADDITIVE TIME JITTER   |        |       |        | Delay off                         |  |  |

| CLK = 400 MHz                      | 300    | )     | fs rms | Calculated from SNR of ADC method |  |  |

| LVDS (OUT1) = 100 MHz              |        |       |        | OUT0 off                          |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| CLK = 400 MHz                      | 350    | )     | fs rms | Calculated from SNR of ADC method |  |  |

| LVDS (OUT1) = 100 MHz              |        |       |        | OUT0 off                          |  |  |

| Divide = 4                         |        |       |        |                                   |  |  |

| LVPECL (OUT0)= 50 MHz              |        |       |        | Interferer                        |  |  |

| Parameter                                     | Min | Тур  | Max | Unit   | Test Conditions/Comments                                 |

|-----------------------------------------------|-----|------|-----|--------|----------------------------------------------------------|

| CMOS OUTPUT ADDITIVE TIME JITTER              |     |      |     |        | Delay off                                                |

| CLK = 400 MHz                                 |     | 290  |     | fs rms | Calculated from SNR of ADC method                        |

| CMOS (OUT1) = 100 MHz                         |     |      |     |        |                                                          |

| Divide = 4                                    |     |      |     |        |                                                          |

| CLK = 400 MHz                                 |     | 315  |     | fs rms | Calculated from SNR of ADC method                        |

| CMOS (OUT1) = 100 MHz                         |     |      |     |        |                                                          |

| Divide = 4                                    |     |      |     |        |                                                          |

| LVPECL (OUT0) = $50 \text{ MHz}$              |     |      |     |        | Interferer                                               |

| DELAY BLOCK ADDITIVE TIME JITTER <sup>1</sup> |     |      |     |        | 100 MHz output; incremental additive jitter <sup>1</sup> |

| Delay FS = 1.5 ns Fine Adj. 00000             |     | 0.71 |     | ps rms |                                                          |

| Delay FS = 1.5 ns Fine Adj. 11111             |     | 1.2  |     | ps rms |                                                          |

| Delay FS = 5 ns Fine Adj. 00000               |     | 1.3  |     | ps rms |                                                          |

| Delay FS = 5 ns Fine Adj. 11111               |     | 2.7  |     | ps rms |                                                          |

| Delay FS = 10 ns Fine Adj. 00000              |     | 2.0  |     | ps rms |                                                          |

| Delay FS = 10 ns Fine Adj. 11111              |     | 2.8  |     | ps rms |                                                          |

<sup>1</sup> This value is incremental. That is, it is in addition to the jitter of the LVDS or CMOS output without the delay. To estimate the total jitter, the LVDS or CMOS output jitter should be added to this value using the root sum of the squares (RSS) method.

### SYNCB, VREF, AND SETUP PINS

| Table 6.       | Table 6.       |     |         |      |                                          |  |  |  |  |  |

|----------------|----------------|-----|---------|------|------------------------------------------|--|--|--|--|--|

| Parameter      | Min            | Тур | Max     | Unit | Test Conditions/Comments                 |  |  |  |  |  |

| SYNCB          |                |     |         |      |                                          |  |  |  |  |  |

| Logic High     | 2.7            |     |         | V    |                                          |  |  |  |  |  |

| Logic Low      |                |     | 0.40    | V    |                                          |  |  |  |  |  |

| Capacitance    |                | 2   |         | pF   |                                          |  |  |  |  |  |

| VREF           |                |     |         |      |                                          |  |  |  |  |  |

| Output Voltage | 0.62 Vs        |     | 0.76 Vs | V    | Minimum – maximum from 0 mA to 1 mA load |  |  |  |  |  |

| S0 TO S10      |                |     |         |      |                                          |  |  |  |  |  |

| Levels         |                |     |         |      |                                          |  |  |  |  |  |

| 0              |                |     | 0.1 Vs  | V    |                                          |  |  |  |  |  |

| 1/3            | 0.2 Vs         |     | 0.45 Vs | V    |                                          |  |  |  |  |  |

| 2/3            | 0.55 Vs        |     | 0.8 Vs  | V    |                                          |  |  |  |  |  |

| 1              | <b>0.9 V</b> s |     |         | V    |                                          |  |  |  |  |  |

## AD9515

### POWER

Table 7.

| Parameter                                       | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                       |

|-------------------------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------|

| POWER-ON SYNCHRONIZATION <sup>1</sup>           |     |     | 35  | ms   | See the Power-On SYNC section.                                                                                                 |

| $V_{\text{S}}$ Transit Time from 2.2 V to 3.1 V |     |     |     |      |                                                                                                                                |

| POWER DISSIPATION                               | 215 | 285 | 380 | mW   | Both outputs on. LVPECL (divide = 2), LVDS (divide = 2). No clock.<br>Does not include power dissipated in external resistors. |

|                                                 | 300 | 370 | 465 | mW   | Both outputs on. LVPECL (divide = 2), CMOS (divide = 2);<br>at 62.5 MHz out (5 pF load).                                       |

|                                                 | 330 | 405 | 510 | mW   | Both outputs on. LVPECL, CMOS (divide = 2);                                                                                    |

|                                                 |     |     |     |      | at 125 MHz out (5 pF load).                                                                                                    |

| POWER DELTA                                     |     |     |     |      |                                                                                                                                |

| Divider (Divide = $2$ to Divide = $1$ )         | 15  | 30  | 45  | mW   | For each divider. No clock.                                                                                                    |

| LVPECL Output                                   | 65  | 90  | 125 | mW   | For each output. No clock.                                                                                                     |

| LVDS Output                                     | 20  | 50  | 85  | mW   | No clock.                                                                                                                      |

| CMOS Output (Static)                            | 30  | 40  | 50  | mW   | No clock.                                                                                                                      |

| CMOS Output (@ 62.5 MHz)                        | 80  | 110 | 140 | mW   | Single-ended. At 62.5 MHz out with 5 pF load.                                                                                  |

| CMOS Output (@ 125 MHz)                         | 110 | 150 | 190 | mW   | Single-ended. At 125 MHz out with 5 pF load.                                                                                   |

| Delay Block                                     | 30  | 45  | 65  | mW   | Off to 1.5 ns fs, delay word = 60; output clocking at 62.5 MHz.                                                                |

<sup>1</sup> This is the rise time of the V<sub>s</sub> supply that is required to ensure that a synchronization of the outputs occurs on power-up. The critical factor is the time it takes the V<sub>s</sub> to transition the range from 2.2 V to 3.1 V. If the rise time is too slow, the outputs will not be synchronized.

## TIMING DIAGRAMS

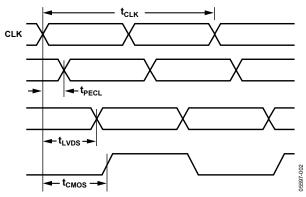

Figure 2. CLK/CLKB to Clock Output Timing, Divide = 1 Mode

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 8.

|                                   | With<br>Respect |      |               |      |

|-----------------------------------|-----------------|------|---------------|------|

| Parameter or Pin                  | to .            | Min  | Max           | Unit |

| VS                                | GND             | -0.3 | +3.6          | ٧    |

| RSET                              | GND             | -0.3 | Vs + 0.3      | V    |

| CLK, CLKB                         | GND             | -0.3 | $V_{s} + 0.3$ | V    |

| CLK                               | CLKB            | -1.2 | +1.2          | V    |

| OUT0, OUT0B, OUT1, OUT1B          | GND             | -0.3 | $V_{s} + 0.3$ | V    |

| Junction Temperature <sup>1</sup> |                 |      | 150           | °C   |

| Storage Temperature               |                 | -65  | +150          | °C   |

| Lead Temperature (10 sec)         |                 |      | 300           | °C   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS<sup>2</sup>

#### **Thermal Resistance**

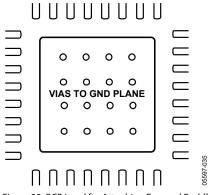

32-Lead LFCSP<sup>3</sup>

$\theta_{IA} = 36.6^{\circ}C/W$

<sup>1</sup> See Thermal Characteristics for  $\theta_{JA}$ .

<sup>2</sup> Thermal impedance measurements were taken on a 4-layer board in still air in accordance with EIA/JESD51-7.

<sup>3</sup> The external pad of this package must be soldered to adequate copper land on board.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

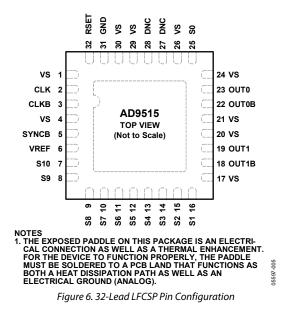

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 9. Pin Function Descriptions**

| Pin No.                                    | Mnemonic  | Description                                                                        |

|--------------------------------------------|-----------|------------------------------------------------------------------------------------|

| 1, 4, 17, 20, 21, 24, 26, 29, 30           | VS        | Power Supply (3.3 V).                                                              |

| 2                                          | CLK       | Clock Input.                                                                       |

| 3                                          | CLKB      | Complementary Clock Input. Used in conjunction with CLK.                           |

| 5                                          | SYNCB     | Used to Synchronize the Outputs; Active Low Signal.                                |

| 6                                          | VREF      | Provides 2/3 V₅ Reference Voltage for Use with Programming Pins S0 to S10.         |

| 25, 16, 15, 14, 13, 12, 11, 10, 9,<br>8, 7 | S0 to S10 | Programming Pins. These pins determine the operation of the AD9515; 4-state logic. |

| 18                                         | OUT1B     | Complementary LVDS/Inverted CMOS Output. Includes a delay block.                   |

| 19                                         | OUT1      | LVDS/CMOS Output. Includes a delay block.                                          |

| 22                                         | OUT0B     | Complementary LVPECL Output.                                                       |

| 23                                         | OUT0      | LVPECL Output.                                                                     |

| 27, 28                                     | DNC       | Do Not Connect.                                                                    |

| 31, Exposed Paddle                         | GND       | Ground. The exposed paddle on the back of the chip is also GND.                    |

| 32                                         | RSET      | Current Sets Resistor to Ground. Nominal value = $4.12 \text{ k}\Omega$ .          |

## TERMINOLOGY

### Phase Jitter and Phase Noise

An ideal sine wave can be thought of as having a continuous and even progression of phase with time from 0 to 360 degrees for each cycle. Actual signals, however, display a certain amount of variation from ideal phase progression over time. This phenomenon is called phase jitter. Although there are many causes that can contribute to phase jitter, one major component is due to random noise that is characterized statistically as being Gaussian (normal) in distribution.

This phase jitter leads to a spreading out of the energy of the sine wave in the frequency domain, producing a continuous power spectrum. This power spectrum is usually reported as a series of values whose units are dBc/Hz at a given offset in frequency from the sine wave (carrier). The value is a ratio (expressed in dB) of the power contained within a 1 Hz bandwidth with respect to the power at the carrier frequency. For each measurement, the offset from the carrier frequency is also given.

It is also meaningful to integrate the total power contained within some interval of offset frequencies (for example, 10 kHz to 10 MHz). This is called the integrated phase noise over that frequency offset interval and can be readily related to the time jitter due to the phase noise within that offset frequency interval.

Phase noise has a detrimental effect on the performance of ADCs, DACs, and RF mixers. It lowers the achievable dynamic range of the converters and mixers, although they are affected in somewhat different ways.

### **Time Jitter**

Phase noise is a frequency domain phenomenon. In the time domain, the same effect is exhibited as time jitter. When observing a sine wave, the time of successive zero crossings is seen to vary. For a square wave, the time jitter is seen as a displacement of the edges from their ideal (regular) times of occurrence. In both cases, the variations in timing from the ideal are the time jitter. Since these variations are random in nature, the time jitter is specified in units of seconds root mean square (rms) or 1 sigma of the Gaussian distribution.

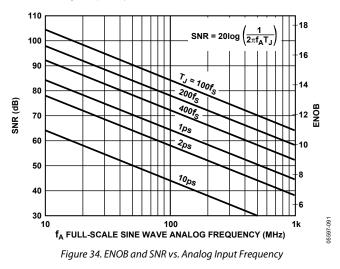

Time jitter that occurs on a sampling clock for a DAC or an ADC decreases the SNR and dynamic range of the converter. A sampling clock with the lowest possible jitter provides the highest performance from a given converter.

### **Additive Phase Noise**

It is the amount of phase noise that is attributable to the device or subsystem being measured. The phase noise of any external oscillators or clock sources has been subtracted. This makes it possible to predict the degree to which the device affects the total system phase noise when used in conjunction with the various oscillators and clock sources, each of which contribute their own phase noise to the total. In many cases, the phase noise of one element dominates the system phase noise.

### Additive Time Jitter

It is the amount of time jitter that is attributable to the device or subsystem being measured. The time jitter of any external oscillators or clock sources has been subtracted. This makes it possible to predict the degree to which the device will affect the total system time jitter when used in conjunction with the various oscillators and clock sources, each of which contribute their own time jitter to the total. In many cases, the time jitter of the external oscillators and clock sources dominates the system time jitter.

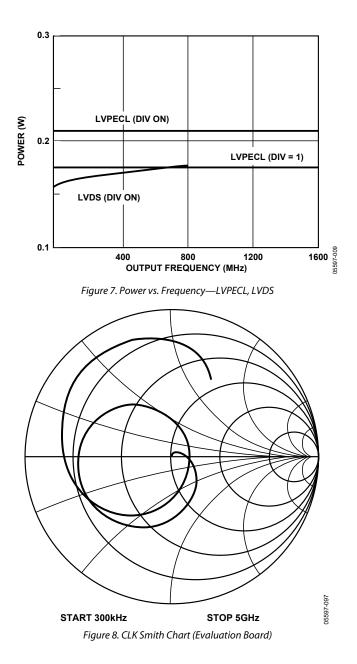

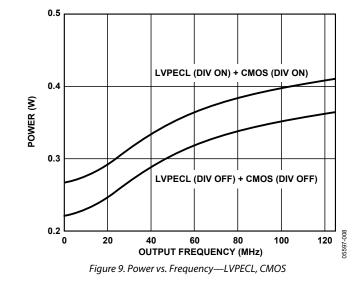

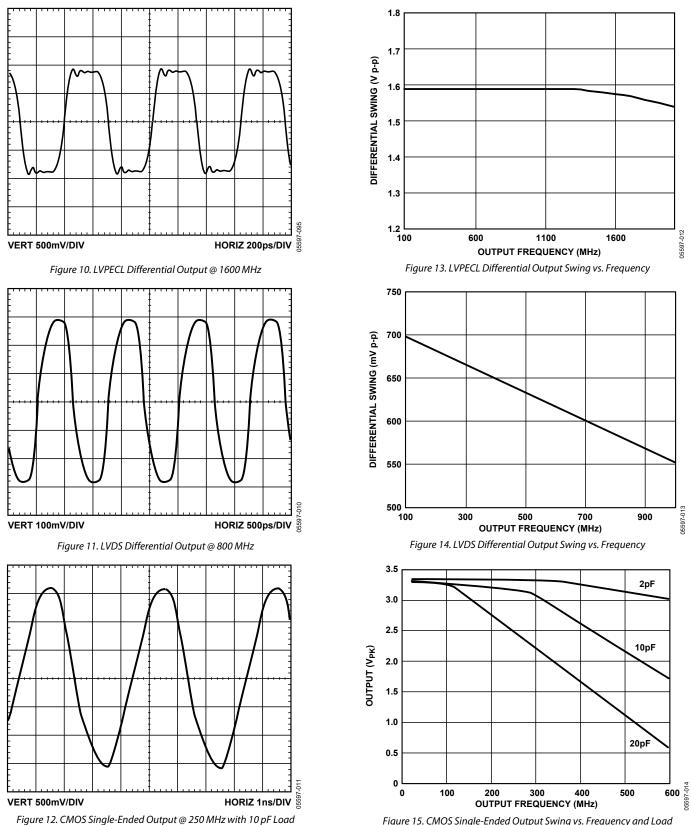

## **TYPICAL PERFORMANCE CHARACTERISTICS**

## AD9515

Figure 15. CMOS Single-Ended Output Swing vs. Frequency and Load

### FUNCTIONAL DESCRIPTION overall

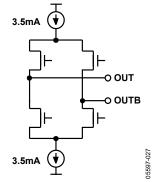

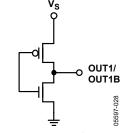

The AD9515 provides for the distribution of its input clock on one or both of its outputs. OUT0 is an LVPECL output. OUT1 can be set to either LVDS or CMOS logic levels. Each output has its own divider that can be set for a divide ratio selected from a list of integer values from 1 (bypassed) to 32.

OUT1 includes an analog delay block that can be set to add an additional delay of 1.5 ns, 5 ns, or 10 ns full scale, each with 16 levels of fine adjustment.

### CLK, CLKB—DIFFERENTIAL CLOCK INPUT

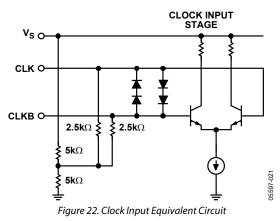

The CLK and CLKB pins are differential clock input pins. This input works up to 1600 MHz. The jitter performance is degraded by a slew rate below 1 V/ns. The input level should be between approximately 150 mV p-p to no more than 2 V p-p. Anything greater can result in turning on the protection diodes on the input pins.

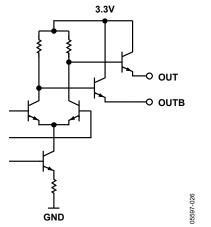

See Figure 22 for the CLK equivalent input circuit. This input is fully differential and self-biased. The signal should be ac-coupled using capacitors. If a single-ended input must be used, this can be accommodated by ac coupling to one side of the differential input only. The other side of the input should be bypassed to a quiet ac ground by a capacitor.

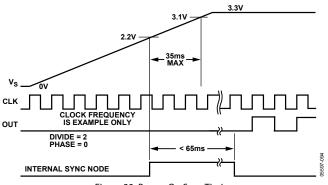

### SYNCHRONIZATION Power-On SYNC

A power-on sync (POS) is issued when the V<sub>s</sub> power supply is turned on to ensure that the outputs start in synchronization. The power-on sync works only if the V<sub>s</sub> power supply transitions the region from 2.2 V to 3.1 V within 35 ms. The POS can occur up to 65 ms after V<sub>s</sub> crosses 2.2 V. Only outputs which are not divide = 1 are synchronized.

Figure 23. Power-On Sync Timing

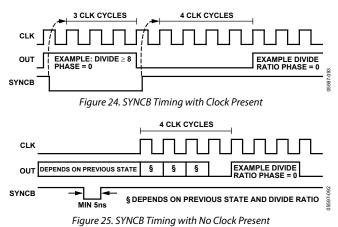

### SYNCB

If the setup configuration of the AD9515 is changed during operation, the outputs can become unsynchronized. The outputs can be re-synchronized to each other at any time. Synchronization occurs when the SYNCB pin is pulled low and released. The clock outputs (except where divide = 1) are forced into a fixed state (determined by the divide and phase settings) and held there in a static condition, until the SYNCB pin is returned to high. Upon release of the SYNCB pin, after four cycles of the clock signal at CLK, all outputs continue clocking in synchronicity (except where divide = 1).

When divide = 1 for an output, that output is not affected by SYNCB.

The outputs of the AD9515 can be synchronized by using the SYNCB pin. Synchronization aligns the phases of the clock outputs, respecting any phase offset that has been set on an output's divider.

Figure 26. SYNCB Equivalent Input Circuit

Synchronization is initiated by pulling the SYNCB pin low for a minimum of 5 ns. The input clock does not have to be present at the time the command is issued. The synchronization occurs after four input clock cycles.

The synchronization applies to clock outputs:

- that are not turned OFF

- where the divider is not divide = 1 (divider bypassed)

An output with its divider set to divide = 1 (divider bypassed) is always synchronized with the input clock, with a propagation delay.

The SYNCB pin must be pulled up for normal operation. Do not let the SYNCB pin float.

### **R**SET RESISTOR

The internal bias currents of the AD9515 are set by the  $R_{\text{SET}}$  resistor. This resistor should be as close as possible to the value given as a condition in the Specifications section ( $R_{\text{SET}} = 4.12 \text{ k}\Omega$ ). This is a standard 1% resistor value and should be readily obtainable. The bias currents set by this resistor determine the logic levels and operating conditions of the internal blocks of the AD9515. The performance figures given in the Specifications section assume that this resistor value is used for  $R_{\text{SET}}$ .

### VREF

The VREF pin provides a voltage level of  $\frac{2}{3}$  V<sub>s</sub>. This voltage is one of the four logic levels used by the setup pins (S0 to S10). These pins set the operation of the AD9515. The VREF pin provides sufficient drive capability to drive as many of the setup pins as necessary, up to all on a single part. The VREF pin should be used for no other purpose.

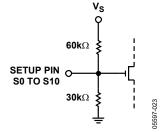

### SETUP CONFIGURATION

The specific operation of the AD9515 is set by the logic levels applied to the setup pins (S10 to S0). These pins use four-state logic. The logic levels used are  $V_s$  and GND, plus  $\frac{1}{3}$   $V_s$  and  $\frac{2}{3}$   $V_s$ . The  $\frac{1}{3}$   $V_s$  level is provided by the internal self-biasing on each of the setup pins (S10 to S0). This is the level seen by a setup pin that is left not connected (NC). The  $\frac{2}{3}$   $V_s$  level is

provided by the VREF pin. All setup pins requiring the  $\frac{2}{3}V_s$  level must be tied to the VREF pin.

Figure 27. Setup Pin (S0 to S10) Equivalent Circuit

The AD9515 operation is determined by the combination of logic levels present at the setup pins. The setup configurations for the AD9515 are shown in Table 10 to Table 15. The four logic levels are referred to as 0,  $\frac{1}{3}$ ,  $\frac{2}{3}$ , and 1. These numbers represent the fraction of the Vs voltage that defines the logic levels. See the setup pin thresholds in Table 6.

The meaning of some of the setup pins depends on the logic level set on other pins. For example, the effect of the S9/S10 pair of pins depends on the state of S8. S8 selects whether the phase value selected by S9/S10 affects either OUT0 or OUT1. In addition, if OUT1 is selected to have its phase controlled, the effect further depends on the state of S0. If S = 0, the delay block for OUT1 is bypassed, and the logic levels on S9/S10 set the phase value of the OUT1 divider. However, if S0  $\neq$  0, then the full-scale delay for OUT1 is set by the logic level on S0, and S9/S10 set the delay block fine delay (fraction of full scale).

Additionally, if a nonzero phase value is selected by S2/S3/S4 (for OUT0) or S5/S6/S7 (for OUT1), this phase overrides the phase value selected by S9/S10. This allows a phase delay to be selected on OUT0 while also selecting a time delay on OUT1.

S1 selects the logic level of each output. OUT0 is LVPECL. The LVPECL output differential voltage ( $V_{OD}$ ) can be selected from two levels: 400 mV or 780 mV. OUT1 can be set to either LVDS or CMOS levels.

OUT0 can be turned off (powered down) by setting S2/S3/S4 to 0/1/0. OUT1 can be turned off by setting S5/S6/S7 to 0/1/0.

Do not set \$2/\$3/\$4/\$5/\$6/\$7 to 1/1/1/1/1.

## PROGRAMMING

### Table 10. S0—OUT1 Delay Full Scale

| S0  | Delay    |

|-----|----------|

| 0   | Bypassed |

| 1/3 | 1.5 ns   |

| 2/3 | 5 ns     |

| 1   | 10 ns    |

| Table 11. S1—Output Logic Configuration |               |      |  |  |  |  |  |

|-----------------------------------------|---------------|------|--|--|--|--|--|

| <b>S</b> 1                              | OUT0          | OUT1 |  |  |  |  |  |

| 0                                       | LVPECL 790 mV | LVDS |  |  |  |  |  |

| 1/3                                     | LVPECL 400 mV | LVDS |  |  |  |  |  |

| 2/3                                     | LVPECL 790 mV | CMOS |  |  |  |  |  |

| 1                                       | LVPECL 400 mV | CMOS |  |  |  |  |  |

### Table 12. S2, S3, and S4—OUT0

| S2  | S3  | S4  | OUT0                              | OUT0  |

|-----|-----|-----|-----------------------------------|-------|

| 52  | 55  | 54  | Divide (Duty Cycle <sup>1</sup> ) | Phase |

| 0   | 0   | 0   | 1                                 | 0     |

| 1/3 | 0   | 0   | 2 (50%)                           | 0     |

| 2/3 | 0   | 0   | 3 (33%)                           | 0     |

| 1   | 0   | 0   | 4 (50%)                           | 0     |

| 0   | 1/3 | 0   | 5 (40%)                           | 0     |

| 1/3 | 1/3 | 0   | 6 (50%)                           | 0     |

| 2/3 | 1/3 | 0   | 7 (43%)                           | 0     |

| 1   | 1/3 | 0   | 8 (50%)                           | 0     |

| 0   | 2/3 | 0   | 9 (44%)                           | 0     |

| 1/3 | 2/3 | 0   | 10 (50%)                          | 0     |

| 2/3 | 2/3 | 0   | 11 (45%)                          | 0     |

| 1   | 2/3 | 0   | 12 (50%)                          | 0     |

| 0   | 1   | 0   | OUT0 OFF                          |       |

| 1/3 | 1   | 0   | 14 (50%)                          | 0     |

| 2/3 | 1   | 0   | 15 (47%)                          | 0     |

| 1   | 1   | 0   | 16 (50%)                          | 0     |

| 0   | 0   | 1/3 | 17 (47%)                          | 0     |

| 1/3 | 0   | 1/3 | 18 (50%)                          | 0     |

| 2/3 | 0   | 1/3 | 19 (47%)                          | 0     |

| 1   | 0   | 1/3 | 20 (50%)                          | 0     |

| 0   | 1/3 | 1/3 | 21 (48%)                          | 0     |

| 1/3 | 1/3 | 1/3 | 22 (50%)                          | 0     |

| 2/3 | 1/3 | 1/3 | 23 (48%)                          | 0     |

| 1   | 1/3 | 1/3 | 24 (50%)                          | 0     |

| 0   | 2/3 | 1/3 | 25 (48%)                          | 0     |

| 62  | 62         | 64         | 01170                                     | 0.1170        |

|-----|------------|------------|-------------------------------------------|---------------|

| S2  | <b>S</b> 3 | <b>S</b> 4 | OUT0<br>Divide (Duty Cycle <sup>1</sup> ) | OUT0<br>Phase |

| 1/3 | 2/3        | 1/3        | 26 (50%)                                  | 0             |

| 2/3 | 2/3        | 1/3        | 27 (48%)                                  | 0             |

| 1   | 2/3        | 1/3        | 28 (50%)                                  | 0             |

| 0   | 1          | 1/3        | 29 (48%)                                  | 0             |

| 1/3 | 1          | 1/3        | 30 (50%)                                  | 0             |

| 2/3 | 1          | 1/3        | 31 (48%)                                  | 0             |

| 1   | 1          | 1/3        | 32 (50%)                                  | 0             |

| 0   | 0          | 2/3        | 2 (50%)                                   | 1             |

| 1/3 | 0          | 2/3        | 4 (50%)                                   | 1             |

| 2/3 | 0          | 2/3        | 4 (50%)                                   | 2             |

| 1   | 0          | 2/3        | 4 (50%)                                   | 3             |

| 0   | 1/3        | 2/3        | 8 (50%)                                   | 1             |

| 1/3 | 1/3        | 2/3        | 8 (50%)                                   | 2             |

| 2/3 | 1/3        | 2/3        | 8 (50%)                                   | 3             |

| 1   | 1/3        | 2/3        | 8 (50%)                                   | 4             |

| 0   | 2/3        | 2/3        | 8 (50%)                                   | 5             |

| 1/3 | 2/3        | 2/3        | 8 (50%)                                   | 6             |

| 2/3 | 2/3        | 2/3        | 8 (50%)                                   | 7             |

| 1   | 2/3        | 2/3        | 16 (50%)                                  | 1             |

| 0   | 1          | 2/3        | 16 (50%)                                  | 2             |

| 1/3 | 1          | 2/3        | 16 (50%)                                  | 3             |

| 2/3 | 1          | 2/3        | 16 (50%)                                  | 4             |

| 1   | 1          | 2/3        | 16 (50%)                                  | 5             |

| 0   | 0          | 1          | 16 (50%)                                  | 6             |

| 1/3 | 0          | 1          | 16 (50%)                                  | 7             |

| 2/3 | 0          | 1          | 16 (50%)                                  | 8             |

| 1   | 0          | 1          | 16 (50%)                                  | 9             |

| 0   | 1/3        | 1          | 16 (50%)                                  | 10            |

| 1/3 | 1/3        | 1          | 16 (50%)                                  | 11            |

| 2/3 | 1/3        | 1          | 16 (50%)                                  | 12            |

| 1   | 1/3        | 1          | 16 (50%)                                  | 13            |

| 0   | 2/3        | 1          | 16 (50%)                                  | 14            |

| 1/3 | 2/3        | 1          | 16 (50%)                                  | 15            |

| 2/3 | 2/3        | 1          | 32 (50%)                                  | 1             |

| 1   | 2/3        | 1          | 32 (50%)                                  | 2             |

| 0   | 1          | 1          | 32 (50%)                                  | 3             |

| 1/3 | 1          | 1          | 32 (50%)                                  | 4             |

| 2/3 | 1          | 1          | 32 (50%)                                  | 5             |

| 1   | 1          | 1          | Do not use                                |               |

<sup>1</sup> Duty cycle is the clock signal high time divided by the total period.

### Table 13. S5, S6, and S7—OUT1

|     | 15. 55, 5 | 1   | 5/_0011                                   |               |

|-----|-----------|-----|-------------------------------------------|---------------|

| S5  | <b>S6</b> | S7  | OUT1<br>Divide (Duty Cycle <sup>1</sup> ) | OUT1<br>Phase |

| 0   | 0         | 0   | 1                                         | 0             |

| 1/3 | 0         | 0   | 2 (50%)                                   | 0             |

| 2/3 | 0         | 0   | 3 (33%)                                   | 0             |

| 1   | 0         | 0   | 4 (50%)                                   | 0             |

| 0   | 1/3       | 0   | 5 (40%)                                   | 0             |

| 1/3 | 1/3       | 0   | 6 (50%)                                   | 0             |

| 2/3 | 1/3       | 0   | 7 (43%)                                   | 0             |

| 1   | 1/3       | 0   | 8 (50%)                                   | 0             |

| 0   | 2/3       | 0   | 9 (44%)                                   | 0             |

| 1/3 | 2/3       | 0   | 10 (50%)                                  | 0             |

| 2/3 | 2/3       | 0   | 11 (45%)                                  | 0             |

| 1   | 2/3       | 0   | 12 (50%)                                  | 0             |

| 0   | 1         | 0   | OUT1 OFF                                  |               |

| 1/3 | 1         | 0   | 14 (50%)                                  | 0             |

| 2/3 | 1         | 0   | 15 (47%)                                  | 0             |

| 1   | 1         | 0   | 16 (50%)                                  | 0             |

| 0   | 0         | 1/3 | 17 (47%)                                  | 0             |

| 1/3 | 0         | 1/3 | 18 (50%)                                  | 0             |

| 2/3 | 0         | 1/3 | 19 (47%)                                  | 0             |

| 1   | 0         | 1/3 | 20 (50%)                                  | 0             |

| 0   | 1/3       | 1/3 | 21 (48%)                                  | 0             |

| 1/3 | 1/3       | 1/3 | 22 (50%)                                  | 0             |

| 2/3 | 1/3       | 1/3 | 23 (48%)                                  | 0             |

| 1   | 1/3       | 1/3 | 24 (50%)                                  | 0             |

| 0   | 2/3       | 1/3 | 25 (48%)                                  | 0             |

| 1/3 | 2/3       | 1/3 | 26 (50%)                                  | 0             |

| 2/3 | 2/3       | 1/3 | 27 (48%)                                  | 0             |

| 1   | 2/3       | 1/3 | 28 (50%)                                  | 0             |

| 0   | 1         | 1/3 | 29 (48%)                                  | 0             |

| 1/3 | 1         | 1/3 | 30 (50%)                                  | 0             |

| 2/3 | 1         | 1/3 | 31 (48%)                                  | 0             |

| 1   | 1         | 1/3 | 32 (50%)                                  | 0             |

| 0   | 0         | 2/3 | 2 (50%)                                   | 1             |

| 1/3 | 0         | 2/3 | 4 (50%)                                   | 1             |

| 2/3 | 0         | 2/3 | 4 (50%)                                   | 2             |

| 1   | 0         | 2/3 | 4 (50%)                                   | 3             |

| 0   | 1/3       | 2/3 | 8 (50%)                                   | 1             |

| 1/3 | 1/3       | 2/3 | 8 (50%)                                   | 2             |

| 2/3 | 1/3       | 2/3 | 8 (50%)                                   | 3             |

| 1   | 1/3       | 2/3 | 8 (50%)                                   | 4             |

| 0   | 2/3       | 2/3 | 8 (50%)                                   | 5             |

| 1/3 | 2/3       | 2/3 | 8 (50%)                                   | 6             |

| 2/3 | 2/3       | 2/3 | 8 (50%)                                   | 7             |

| 1   | 2/3       | 2/3 | 16 (50%)                                  | 1             |

| 0   | 1         | 2/3 | 16 (50%)                                  | 2             |

| 1/3 | 1         | 2/3 | 16 (50%)                                  | 3             |

| 2/3 | 1         | 2/3 | 16 (50%)                                  | 4             |

| 1   | 1         | 2/3 | 16 (50%)                                  | 5             |

| 0   | 0         | 1   | 16 (50%)                                  | 6             |

| 0   | Ū         |     | 10 (30 /0)                                | 5             |

| S5  | <b>S6</b> | S7 | OUT1<br>Divide (Duty Cycle <sup>1</sup> ) | OUT1<br>Phase |

|-----|-----------|----|-------------------------------------------|---------------|

| 1/3 | 0         | 1  | 16 (50%)                                  | 7             |

| 2/3 | 0         | 1  | 16 (50%)                                  | 8             |

| 1   | 0         | 1  | 16 (50%)                                  | 9             |

| 0   | 1/3       | 1  | 16 (50%)                                  | 10            |

| 1/3 | 1/3       | 1  | 16 (50%)                                  | 11            |

| 2/3 | 1/3       | 1  | 16 (50%)                                  | 12            |

| 1   | 1/3       | 1  | 16 (50%)                                  | 13            |

| 0   | 2/3       | 1  | 16 (50%)                                  | 14            |

| 1/3 | 2/3       | 1  | 16 (50%)                                  | 15            |

| 2/3 | 2/3       | 1  | 32 (50%)                                  | 1             |

| 1   | 2/3       | 1  | 32 (50%)                                  | 2             |

| 0   | 1         | 1  | 32 (50%)                                  | 3             |

| 1/3 | 1         | 1  | 32 (50%)                                  | 4             |

| 2/3 | 1         | 1  | 32 (50%)                                  | 5             |

| 1   | 1         | 1  | Do not use                                |               |

<sup>1</sup> Duty cycle is the clock signal high time divided by the total period.

# Table 14. S8—OUT0/OUT1 Phase (Delay) Select (Used with S9 to S10)

| <b>S8</b> | OUT0               | OUT1 (Delay if S0 ≠ 0)     |

|-----------|--------------------|----------------------------|

| 0         | No Phase           | Phase (Delay)              |

| 1/3       | Phase              | No Phase                   |

| 2/3       | No Phase           | Phase (Delay) (Start High) |

| 1         | Phase (Start High) | No Phase                   |

#### Table 15. S9 and S10

|     |     | OUT0 or OUT1 Phase<br>(Depends on S8) | OUT1 Delay (S0 ≠ 0)<br>(Depends on S8) |

|-----|-----|---------------------------------------|----------------------------------------|

| S9  | S10 | Phase <sup>1</sup>                    | Fine Delay                             |

| 0   | 0   | 0                                     | 0                                      |

| 1/3 | 0   | 1                                     | 1/16                                   |

| 2/3 | 0   | 2                                     | 1/8                                    |

| 1   | 0   | 3                                     | 3/16                                   |

| 0   | 1/3 | 4                                     | 1/4                                    |

| 1/3 | 1/3 | 5                                     | 5/16                                   |

| 2/3 | 1/3 | 6                                     | 3/8                                    |

| 1   | 1/3 | 7                                     | 7/16                                   |

| 0   | 2/3 | 8                                     | 1/2                                    |

| 1/3 | 2/3 | 9                                     | 9/16                                   |

| 2/3 | 2/3 | 10                                    | 5/8                                    |

| 1   | 2/3 | 11                                    | 11/16                                  |

| 0   | 1   | 12                                    | 3/4                                    |

| 1/3 | 1   | 13                                    | 13/16                                  |

| 2/3 | 1   | 14                                    | 7/8                                    |

| 1   | 1   | 15                                    | 15/16                                  |

$^{1}$  A phase > 0 in Table 12 or overrides the phase in Table 15.

### **DIVIDER PHASE OFFSET**

The phase offset of OUT0 and OUT1 can be selected (see Table 12 to Table 15). This allows the relative phase of OUT0 and OUT1 to be set.

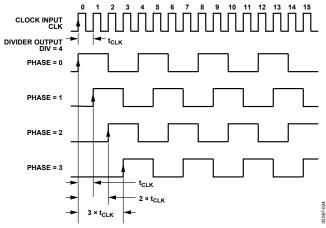

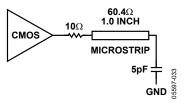

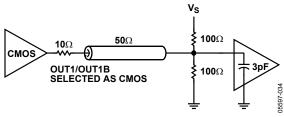

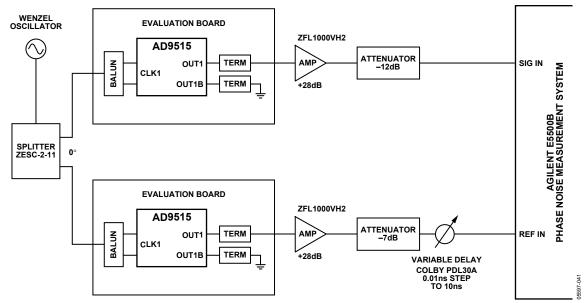

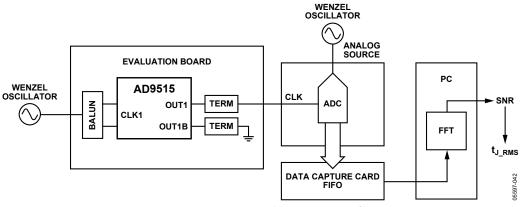

After a SYNC operation (see the Synchronization section), the phase offset word of each divider determines the number of input clock (CLK) cycles to wait before initiating a clock output edge. By giving each divider a different phase offset, output-to-output delays can be set in increments of the fast clock period,  $t_{\rm CLK}$ .