# Pb Free RoHS

# 3.2mm x 2.5mm Ceramic SMD Package Oscillator, CMOS

**ISM97 Series**

#### **Product Features:**

- Low Jitter, Non-PLL Based Output

- Compatible with Lead free Processing

- Pb-free, Halogen-free, and Antimony-free

- RoHS and REACH compliant

#### **Typical Applications:**

- Fibre Channel

- Server & Storage

- Sonet / SDH

- 802.11 / WiFi • T1/E1, T3/E3

- System Clock

| Frequency Range             | 1.000MHz to 156.250MHz                                                                          |                                                                                                                                                                                     |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Frequency Stability         | ±10ppm Maximum ±15ppm Maximum ±20ppm Maximum ±25ppm Maximum ±50ppm Maximum ±100ppm Maximum      | Inclusive of Calibration Tolerance at 25°C,<br>Frequency Stability over Operating Temperature<br>Range, Supply Voltage Change, Output Load<br>Change, and First Year Aging at 25°C. |  |  |

| Operating Temperature Range | 0°C to +70°C, -10°C to +60°C, -10°C to +70°C, -20°C to +70°C, -30°C to +75°C, or -40°C to +85°C |                                                                                                                                                                                     |  |  |

| Supply Voltage (Vdd)        | 1.8V, 2.5V, 2.7V, 3.0V, 3.3V, 1.62V - 3.63V                                                     | ±5%                                                                                                                                                                                 |  |  |

| Input Current               | 20mA Maximum                                                                                    |                                                                                                                                                                                     |  |  |

| Output Logic Type           | CMOS                                                                                            |                                                                                                                                                                                     |  |  |

| Output Drive Capability     | 15pF Maximum<br>30pF Maximum                                                                    |                                                                                                                                                                                     |  |  |

| Aging                       | ±3ppm/year Maximum                                                                              | at +25°C                                                                                                                                                                            |  |  |

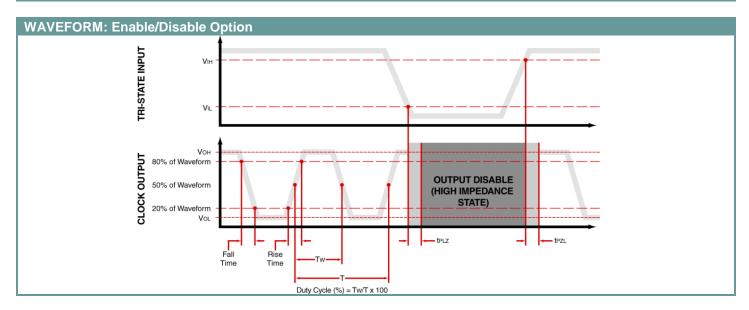

| Duty Cycle                  | 50 ±5(%) or 50 ±10(%)                                                                           | Measured at 50% of waveform                                                                                                                                                         |  |  |

| Rise / Fall Time            | 6nSec Maximum                                                                                   | Measured from 20% to 80% of waveform                                                                                                                                                |  |  |

| Output Voltage Logic High   | 90% of Vdd Minimum                                                                              |                                                                                                                                                                                     |  |  |

| Output Voltage Logic Low    | 10% of Vdd Maximum                                                                              |                                                                                                                                                                                     |  |  |

| Pin 1 Connection            | Tri-State (High Impedance)                                                                      |                                                                                                                                                                                     |  |  |

| Input Voltage Logic High    | 70% of Vdd Minimum or No Connect to Enable Output                                               |                                                                                                                                                                                     |  |  |

| Input Voltage Logic Low     | 30% of Vdd Maximum to Disable Output (High Impedance)                                           |                                                                                                                                                                                     |  |  |

| Standby Current             | 10μA Maximum                                                                                    | Disabled Output, High Impedance                                                                                                                                                     |  |  |

| Startup Time                | 10mSec Maximum                                                                                  |                                                                                                                                                                                     |  |  |

| RMS Phase Jitter            | 1pSec Maximum                                                                                   | 12kHz to 20MHz offset frequency                                                                                                                                                     |  |  |

| Period Jitter (RMS)         | 5pSec Maximum                                                                                   | 20k adjacent periods                                                                                                                                                                |  |  |

| Period Jitter (pk-pk)       | 50pSec Maximum                                                                                  | 100k adjacent periods                                                                                                                                                               |  |  |

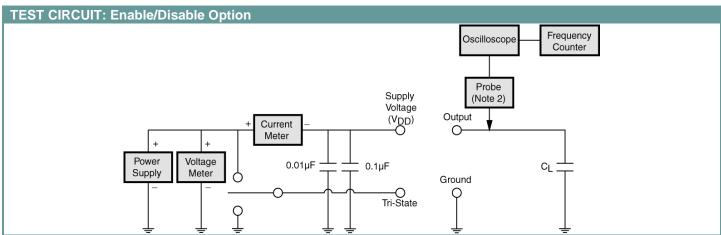

A 0.1μF bypass capacitor is recommended between Vdd (pad 4) and GND (pad 2) to minimize power supply noise.

| ABSOLUTE MAXIMUM LIMITS                                                                                                                            |                        |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|--|--|--|

| Storage Temperature Range                                                                                                                          | -55°C to +125°C        |  |  |  |  |

| Supply Voltage Range                                                                                                                               | -0.3Vdc to Vdd +0.3Vdc |  |  |  |  |

| Electrostatic Discharge                                                                                                                            | 2000V Maximum          |  |  |  |  |

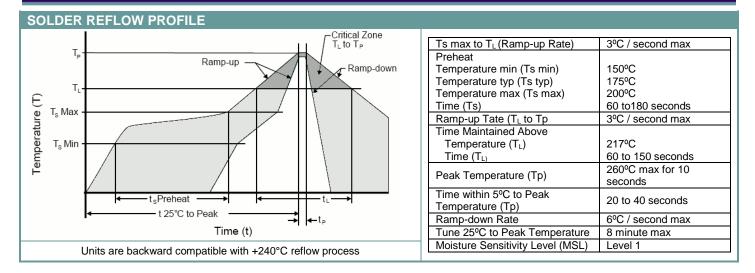

| Solder Temperature                                                                                                                                 | 260°C Maximum          |  |  |  |  |

| Junction Temperature                                                                                                                               | 150°C Maximum          |  |  |  |  |

| NOTE: If the post is used by and shoots to require up vetices, it was a source interval destruction. The post obsuid by used upday the recommended |                        |  |  |  |  |

**NOTE:** If the part is used beyond absolute maximum ratings, it may cause internal destruction. The part should be used under the recommended operating conditions or the reliability of this part may be damaged if those conditions are exceeded.

### 3.2mm x 2.5mm Ceramic SMD Package Oscillator, CMOS

#### **ISM97 Series**

| ENVIRONMENTAL SPECIFICATIONS |                          |  |  |  |  |

|------------------------------|--------------------------|--|--|--|--|

| Mechanical Shock             | MIL-STD-202, Method 213  |  |  |  |  |

| Mechanical Vibration         | MIL-STD-202, Method 204  |  |  |  |  |

| Resistance to Soldering Heat | MIL-STD-202, Method 210  |  |  |  |  |

| Solderability                | J-STD-002                |  |  |  |  |

| Gross Leak                   | MIL-STD-883, Method 1014 |  |  |  |  |

| Fine Leak                    | MIL-STD-883, Method 1014 |  |  |  |  |

| Moisture Sensitivity Level   | MSL 1 (+260°C)           |  |  |  |  |

| PART   | NUMBER GUIDE      |                                |               |                         |                        |                     |             |

|--------|-------------------|--------------------------------|---------------|-------------------------|------------------------|---------------------|-------------|

| Series | Supply<br>Voltage | Operating<br>Temperature Range | Duty<br>Cycle | Output Drive Capability | Frequency<br>Stability | Pin 1<br>Connection | Frequency   |

| ISM97- | 3 = 3.3V          | 1 = 0°C to +70°C               | 5 = 50 ±5%    | 1 = 15pF                | $E = \pm 10ppm$        | H = Tri-State       | -25.000 MHz |

|        | 7 = 3.0V          | 8 = -10°C to +60°C             | 6 = 50 ±10%   | 6 = 30pF                | $D = \pm 15ppm$        | O = N/C             |             |

|        | 2 = 2.7V          | 6 = -10°C to +70°C             |               |                         | $F = \pm 20ppm$        |                     |             |

|        | 6 = 2.5V          | 3 = -20°C to +70°C             |               |                         | $A = \pm 25ppm$        |                     |             |

|        | 1 = 1.8V          | 4 = -30°C to +75°C             |               |                         | $B = \pm 50ppm$        |                     |             |

|        | 8 = 1.62V - 3.63V | 2 = -40°C to +85°C             |               |                         | C = ±100ppm            |                     |             |

#### Sample Part Number: ISM97-3251BH-20.000 MHz

• Not all Frequency Stability options are available at all frequencies and Operating Temperature Ranges.

NOTES: • Not all Output Drive Capability options are available at all frequencies.

• Not all Supply Voltage options are available at all frequencies.

• Please consult with Sales Department any other parameters or options.

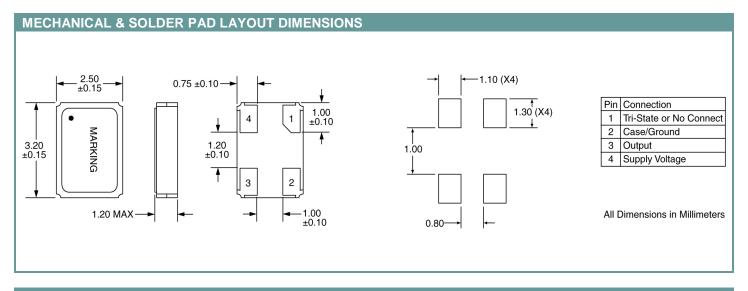

#### **MARKING**

Line 1: ILSI, Date Code (YWW)

Line 2: Frequency

Pin 1 Dot

# **PACKAGE INFORMATION**

**Termination** = e4 (Au over Ni over W base metallization)

**Terminal Plating Thickness:**

Gold (0.3µm to 1.0µm), Nickel (1.27µm to 8.89µm)

# Pb Free RoHS

# 3.2mm x 2.5mm Ceramic SMD Package Oscillator, CMOS

# Pb Free RoHS

# 3.2mm x 2.5mm Ceramic SMD Package Oscillator, CMOS

**ISM97 Series**

#### PROPRIETARY AND CONFIDENTIAL

THIS DOCUMENT CONTAINS PROPRIETARY INFORMATION, AND SUCH INFORMATION MAY NOT BE DISCLOSED TO OTHERS FOR ANY PURPOSE NOR USED FOR MANUFACTURING PURPOSES WITHOUT WRITTEN PERMISSION FROM ILSI America.