# **General Description**

The MAX6978 serial-interfaced LED driver provides eight open-drain, constant-current sinking LED driver outputs rated at 5.5V. The MAX6978 operates from a 3V to 5.5V supply. The MAX6978 supply and the LEDs' supply can power up in any order. The constant-current outputs are programmed together to up to 55mA using a single external resistor. The MAX6978 operates with a 25Mb, industry-standard, 4-wire serial interface.

The MAX6978 includes circuitry that automatically detects open-circuit LEDs. Fault status is loaded into the serial-interface shift register when LE goes high and is automatically shifted out on DOUT when the next data transmission is shifted in.

The MAX6978 includes a fail-safe feature for safetyrelated applications, which blanks the display if the serial interface fails. If the serial interface becomes inactive for more than 1s, all driver output latches are automatically cleared. This turns off all LEDs connected to the outputs. The shift register data is not disturbed. The outputs remain off until the driver output latches are updated with data turning them on, so recovery is automatic if the transmission failure is temporary. The watchdog function requires no software change to the application driving the MAX6978.

The MAX6978 uses the industry-standard shift-registerplus-latch-type serial interface. The driver accepts data shifted into an 8-bit shift register using data input DIN and clock input CLK. Input data appears at the output DOUT eight clock cycles later to allow cascading of multiple MAX6978s. The latch-enable input LE loads the 8 bits of shift-register data into an 8-bit output latch to set which LEDs are on and which are off. The outputenable input  $\overline{OE}$  gates all eight outputs on and off, and is fast enough to be used as a PWM input for LED intensity control.

The MAX6978 is one of a family of 12 shift-register-pluslatch-type LED drivers. The family includes 8-port and 16-port types, with 5.5V- or 36V-rated LED outputs, with and without open-circuit LED detection and watchdog. All versions operate from a 3V to 5.5V supply, and are specified over the -40°C to +125°C temperature range.

> Variable Message Signs Marquee Displays Point-of-Order Signs Traffic Signs Gaming Features Architectural Lighting

## \_Features

- ♦ 25Mb Industry-Standard 4-Wire Serial Interface at 5V

- ♦ 3V to 5.5V Logic Supply

- ♦ 8 Constant-Current LED Outputs Rated at 5.5V

- Up to 55mA Continuous Current per Output

- Output Current Programmed by Single Resistor

- ♦ 3% Current Matching Between Outputs

- 6% Current Matching Between ICs

- Watchdog Clears Display if Interface Fails

- Reports Open-Circuit LED Faults

- ♦ -40°C to +125°C Temperature Range

# **Ordering Information**

| TEMP RANGE      |                 |

|-----------------|-----------------|

| I LIVIF HANGE   | PIN-PACKAGE     |

| -40°C to +125°C | 16 TSSOP-EP*    |

| -40°C to +125°C | 16 PDIP         |

| -40°C to +125°C | 16 SSOP         |

|                 | -40°C to +125°C |

\*EP = Exposed pad.

Typical Application Circuit and Selector Guide appear at end of data sheet.

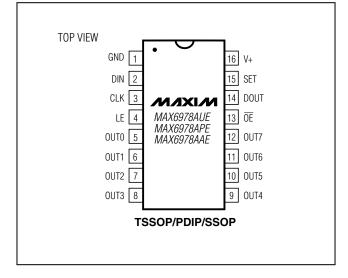

# **Pin Configuration**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

**Applications**

## **ABSOLUTE MAXIMUM RATINGS**

Voltage (with respect to GND)

| V+                    | 0.3V to +6V         |

|-----------------------|---------------------|

| OUT                   |                     |

| DIN, CLK, LE, OE, SET | 0.3V to (V+ + 0.3V) |

| DOUT Current          |                     |

| OUT Sink Current      | 60mA                |

| Total GND Current     |                     |

|                       |                     |

| Continuous Power Dissipation ( $T_A = +70^\circ$ | C)             |

|--------------------------------------------------|----------------|

| 16-Pin SSOP (derate 7.1mW/°C above -             | +70°C)571mW    |

| 16-Pin PDIP (derate 10.5mW/°C above              | +70°C)842mW    |

| 16-Pin TSSOP (derate 21.3mW/°C over              |                |

| $T_A = +70^{\circ}C)$                            | 1702mW         |

| Operating Temperature Range                      | 40°C to +125°C |

| Junction Temperature                             | +150°C         |

| Storage Temperature Range                        |                |

| Lead Temperature (soldering, 10s)                | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(*Typical Operating Circuit*, V + = 3V to 5.5V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at V + = 5V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                                                                             | SYMBOL                | CONDITIONS                                                                        | MIN          | ТҮР | МАХ    | UNITS |

|-------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------|--------------|-----|--------|-------|

| Operating Supply Voltage                                                                              | V+                    |                                                                                   | 3.0          |     | 5.5    | V     |

| Output Voltage                                                                                        | Vout                  |                                                                                   |              |     | 5.5    | V     |

| Standby Current<br>(Interface Idle, All Output Ports<br>High Impedance, $R_{SET}$ = 360 $\Omega$ )    | I+                    | All logic inputs at V+ or GND, DOUT unloaded                                      |              | 4.5 | 5.6    | mA    |

| Standby Current<br>(Interface Running, All Output<br>Ports High Impedance,<br>$R_{SET} = 360\Omega$ ) | ۱+                    | $f_{CLK} = 5MHz$ , $\overline{OE} = V+$ , DIN and LE = V+ or GND, DOUT unloaded   |              | 4.7 | 6      | mA    |

| Supply Current<br>(Interface Idle, All Output Ports<br>Active Low, $R_{SET}$ = 360 $\Omega$ )         | I <sub>+</sub>        | All logic inputs at V+ or GND,<br>DOUT unloaded                                   |              | 10  | 25     | mA    |

| Input High Voltage<br>DIN, CLK, LE, OE                                                                | VIH                   |                                                                                   | 0.7 V+       |     |        | V     |

| Input Low Voltage<br>DIN, CLK, LE, OE                                                                 | VIL                   |                                                                                   |              |     | 0.3 V+ | V     |

| Hysteresis Voltage<br>DIN, CLK, LE, OE                                                                | ΔVI                   |                                                                                   |              | 0.8 |        | V     |

| Input Leakage Current<br>DIN, CLK, LE, OE                                                             | l <sub>IH</sub> , lı∟ |                                                                                   | -1           |     | +1     | μA    |

| Output-High Voltage DOUT                                                                              | Voh                   | ISOURCE = 4mA                                                                     | V+<br>- 0.5V |     |        | V     |

| Output Low Voltage                                                                                    | V <sub>OL</sub>       | I <sub>SINK</sub> = 4mA                                                           |              |     | 0.5    | V     |

| Output Current<br>OUT_                                                                                | IOUT                  | V+ = 3V to 5.5V, V <sub>OUT</sub> = 0.8V to 2.5V, R <sub>SET</sub> = 360 $\Omega$ | 42           | 50  | 56     | mA    |

| Output Leakage Current OUT_                                                                           | ILEAK                 | $\overline{OE} = V+, V_{OUT} = V+$                                                |              |     | 1      | μA    |

| Watchdog Timeout                                                                                      | t <sub>WD</sub>       |                                                                                   |              | 1   |        | S     |

# **5V TIMING CHARACTERISTICS**

(*Typical Operating Circuit*, V + = 4.5V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL                            | CONDITIONS                           | MIN | ТҮР | MAX | UNITS |

|------------------------------------------------|-----------------------------------|--------------------------------------|-----|-----|-----|-------|

| CLK Clock Period                               | tCP                               |                                      | 40  |     |     | ns    |

| CLK Pulse-Width High                           | tсн                               |                                      | 19  |     |     | ns    |

| CLK Pulse-Width Low                            | tCL                               |                                      | 19  |     |     | ns    |

| DIN Setup Time                                 | tDS                               |                                      | 4   |     |     | ns    |

| DIN Hold Time                                  | tDH                               |                                      | 8   |     |     | ns    |

| DOUT Propagation Delay                         | tDO                               |                                      | 12  |     | 32  | ns    |

| DOUT Rise and Fall Time                        | t <sub>DR</sub> , t <sub>DF</sub> | C <sub>DOUT</sub> = 10pF, 20% to 80% |     |     | 10  | ns    |

| LE Pulse-Width High                            | tLW                               |                                      | 20  |     |     | ns    |

| LE Pulse Width (Fault-Detection<br>Data Valid) | tLF                               |                                      | 20  |     |     | ns    |

| LE Setup Time                                  | tLS                               |                                      | 10  |     |     | ns    |

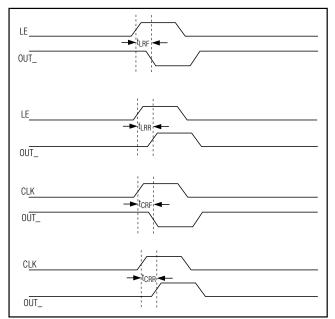

| LE Rising to OUT_ Rising Delay                 | t <sub>LRR</sub>                  | (Note 2)                             |     |     | 100 | ns    |

| LE Rising to OUT_ Falling Delay                | tLRF                              | (Note 2)                             |     |     | 280 | ns    |

| CLK Rising to OUT_ Rising Delay                | tCRR                              | (Note 2)                             |     |     | 100 | ns    |

| CLK Rising to OUT_ Falling Delay               | tCRF                              | (Note 2)                             |     |     | 310 | ns    |

| OE Rising to OUT_ Rising Delay                 | t <u>oe</u> h                     |                                      |     |     | 100 | ns    |

| OE Falling to OUT_ Falling Delay               | toel                              |                                      |     |     | 300 | ns    |

| LED Output OUT_ Turn-On Fall<br>Time           | tf                                | 80% to 20%                           |     |     | 200 | ns    |

| LED Output OUT_ Turn-Off Rise<br>Time          | tr                                | 20% to 80%                           |     |     | 120 | ns    |

# **3.3V TIMING CHARACTERISTICS**

(Typical Operating Circuit, V+ = 3V to 5.5V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                                      | SYMBOL               | CONDITIONS                           | MIN | ТҮР | MAX | UNITS |

|------------------------------------------------|----------------------|--------------------------------------|-----|-----|-----|-------|

| CLK Clock Period                               | tCP                  |                                      | 52  |     |     | ns    |

| CLK Pulse-Width High                           | tсн                  |                                      | 24  |     |     | ns    |

| CLK Pulse-Width Low                            | tCL                  |                                      | 24  |     |     | ns    |

| DIN Setup Time                                 | tDS                  |                                      | 4   |     |     | ns    |

| DIN Hold Time                                  | t <sub>DH</sub>      |                                      | 8   |     |     | ns    |

| DOUT Propagation Delay                         | tdo                  |                                      | 12  |     | 48  | ns    |

| DOUT Rise and Fall Time                        |                      | C <sub>DOUT</sub> = 10pF, 20% to 80% |     |     | 10  | ns    |

| LE Pulse-Width High                            | tLW                  |                                      | 20  |     |     | ns    |

| LE Pulse Width (Fault-Detection<br>Data Valid) | tLW                  |                                      | 20  |     |     | ns    |

| LE Setup Time                                  | tLS                  |                                      | 15  |     |     | ns    |

| LE Rising to OUT_ Rising Delay                 |                      |                                      |     |     | 100 | ns    |

| LE Rising to OUT_ Falling Delay                |                      |                                      |     |     | 310 | ns    |

| CLK Rising to OUT_ Rising Delay                |                      |                                      |     |     | 100 | ns    |

| CLK Rising to OUT_ Falling Delay               |                      |                                      |     |     | 330 | ns    |

| OE Rising to OUT_ Rising Delay                 | t <u>oe</u> h        |                                      |     |     | 100 | ns    |

| OE Falling to OUT_ Falling Delay               | <b>t</b> <u>o</u> EL |                                      |     |     | 330 | ns    |

| LED Output OUT_ Turn-On Fall<br>Time           | tf                   | 80% to 20%                           |     |     | 200 | ns    |

| LED Output OUT_ Turn-Off Rise<br>Time          | tr                   | 20% to 80%                           |     |     | 120 | ns    |

**Note 1:** All parameters tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design. **Note 2:** See Figure 3.

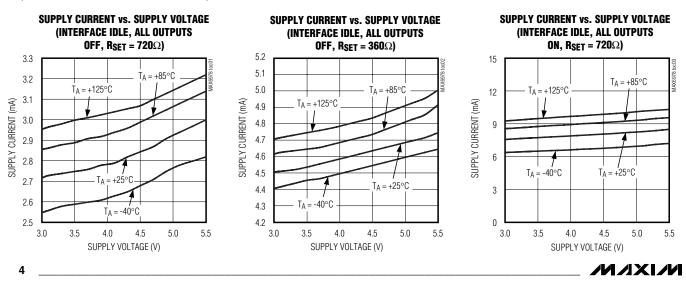

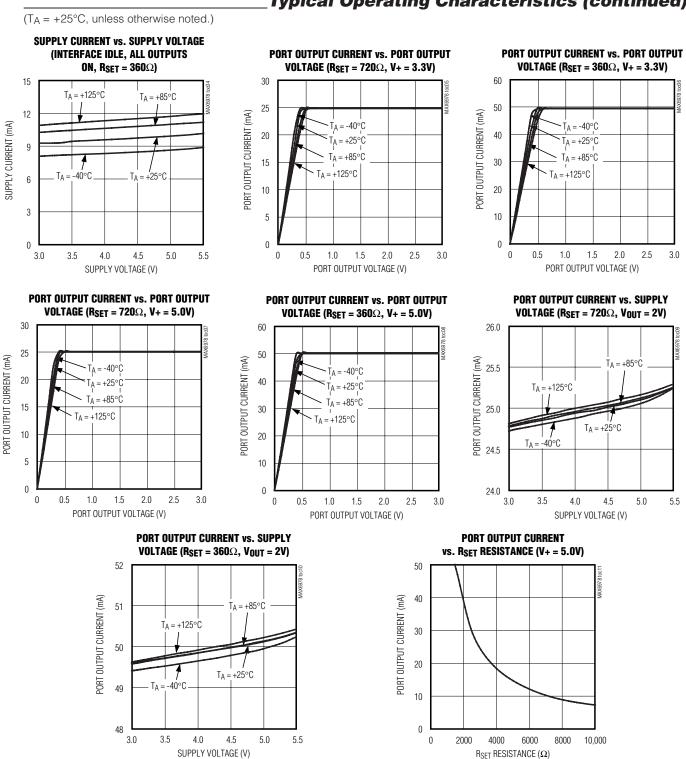

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

**Typical Operating Characteristics**

**Typical Operating Characteristics (continued)**

**MAX697**

**Pin Description**

| PIN  | NAME         | FUNCTION                                                                                                                                                                                                         |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GND          | Ground                                                                                                                                                                                                           |

| 2    | DIN          | Serial-Data Input. Data is loaded into the internal 8-bit shift register on CLK's rising edge.                                                                                                                   |

| 3    | CLK          | Serial-Clock Input. Data is loaded into the internal 8-bit shift register on CLK's rising edge.                                                                                                                  |

| 4    | LE           | Load-Enable Input. Data is loaded transparently from the internal shift register to the output latch while LE is high. Data is latched into the output latch on LE's falling edge, and retained while LE is low. |

| 5–12 | OUT0-OUT7    | LED Driver Outputs. OUT0-OUT7 are open-drain, constant-current sinking outputs rated to 5.5V.                                                                                                                    |

| 13   | ŌĒ           | Output-Enable Input. High forces outputs OUT0–OUT7 to high impedance, without altering the contents of the output latches. Low enables outputs OUT0–OUT7 to follow the state of the output latches.              |

| 14   | DOUT         | Serial-Data Output. Data is clocked out of the 8-bit internal shift-register to DOUT on CLK's rising edge.                                                                                                       |

| 15   | SET          | LED Current Setting. Connect SET to GND through a resistor (RSET) to set the maximum LED current.                                                                                                                |

| 16   | V+           | Positive Supply Voltage. Bypass V+ to GND with a 0.1µF ceramic capacitor.                                                                                                                                        |

| PAD  | Exposed Pad* | Exposed pad on package underside. Connect to GND.                                                                                                                                                                |

\*TSSOP package only.

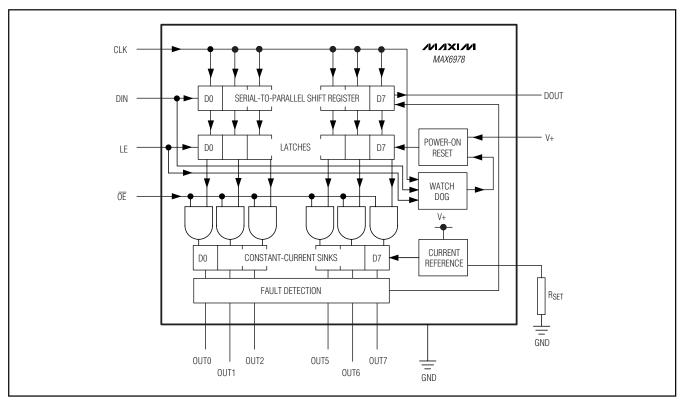

Figure 1. MAX6978 Block Diagram

# **Detailed Description**

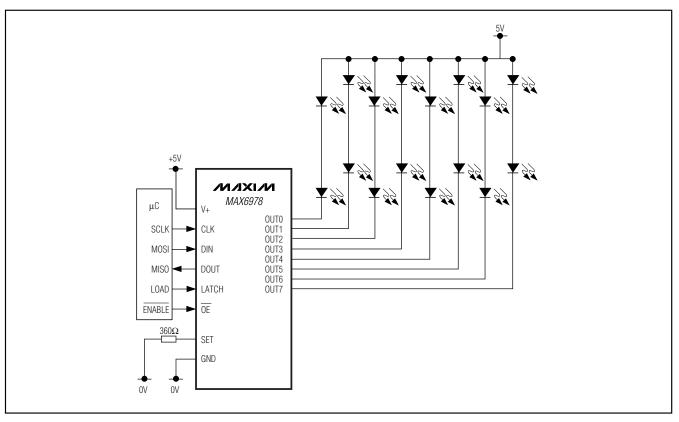

The MAX6978 LED driver comprises a 4-wire serial interface driving eight constant-current sinking opendrain output ports. The outputs drive LEDs in either static or multiplex applications (Figure 1). The constantcurrent outputs are guaranteed for current accuracy not only with chip-supply voltage variations (5V  $\pm$ 10% and 3V to 5.5V), but also over a realistic range of driver output voltage drop (0.5V to 2.5V). The drivers use current-sensing feedback circuitry (not simple current mirrors) to ensure very small current variations over the full allowed range of output voltage (see the *Typical Operating Characteristics*).

The 4-wire serial interface comprises an 8-bit shift register and an 8-bit transparent latch. The shift register is written through a clock input CLK and a data input DIN and the data propagates to a data output DOUT. The data output allows multiple drivers to be cascaded and operated together. The contents of the 8-bit shift register are loaded into the transparent latch through a latch-enable input LE. The latch is transparent to the shift register outputs when high, and latches the current state on the falling edge of LE.

Each driver output is an open-drain constant-current sink that should be connected to the cathode of either a single LED or a series string of multiple LEDs. The LED anode can be connected to a supply voltage of up to 5.5V, independent of the MAX6978 supply, V+. The constant-current capability is up to 55mA per output, set for all eight outputs by an external resistor, R<sub>SET</sub>.

## **Initial Power-Up and Operation**

An internal reset circuit clears the internal registers of the MAX6978 on power-up. All outputs OUT0–OUT7, therefore, initialize high impedance, and the interface output DOUT initializes low, regardless of the initial logic levels of the CLK, DIN, OE, and LE inputs.

### **4-Wire Serial Interface**

The serial interface on the MAX6978 is a 4-wire serial interface using four inputs (DIN, CLK, LE,  $\overline{OE}$ ) and a data output (DOUT). This interface is used to write display data to the MAX6978. The serial-interface data word length is 8 bits, D0–D7.

The functions of the five interface pins are as follows. DIN is the serial-data input, and must be stable when it is sampled on the rising edge of CLK. Data is shifted in, MSB first. This means that data bit D7 is clocked in first, followed by 7 more data bits, finishing with the LSB D0.

CLK is the serial-clock input, which shifts data at DIN into the MAX6978 8-bit shift register on its rising edge.

LE is the latch load input of the MAX6978, which transfers data from the MAX6978 8-bit shift register to its 8-bit latch when LE is a high (transparent latch), and latches the data on the LE falling edge of LE (Figure 2). The rising edge of LE loads fault data into the MAX6978 8-bit shift register, replacing bits D6 and D5 with fault data. This fault data is automatically shifted out through DOUT when the next display data is shifted in.

The fourth input provides output-enable control of the output drivers. OE is high to force outputs OUT0–OUT7 high impedance, without altering the contents of the output latches, and low to enable outputs OUT0–OUT7 to follow the state of the output latches.

| SERIAL<br>DATA | CLOCK<br>INPUT | SHIFT-REGISTER<br>CONTENTS |                |                |   | LOAD<br>INPUT    |                  | LATO | снсс           | ONTE           | INTS           |   | BLANKING<br>INPUT | c  | DUTP | ит с                          | ONT              | ENTS             | ; |                      |                    |

|----------------|----------------|----------------------------|----------------|----------------|---|------------------|------------------|------|----------------|----------------|----------------|---|-------------------|----|------|-------------------------------|------------------|------------------|---|----------------------|--------------------|

| INPUT<br>DIN   | CLK            | D <sub>0</sub>             | D <sub>1</sub> | D <sub>2</sub> |   | D <sub>n-1</sub> | Dn               | LE   | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub> |   | D <sub>n-1</sub>  | Dn | ŌĒ   | D <sub>0</sub>                | D <sub>1</sub>   | D <sub>2</sub>   |   | D <sub>n-1</sub>     | Dn                 |

| Н              |                | Н                          | R <sub>1</sub> | R <sub>2</sub> |   | Rn-2             | R <sub>n-1</sub> |      | _              |                |                |   | —                 |    | —    |                               | _                | _                | _ | —                    | $\left  - \right $ |

| L              | 7              | L                          | R <sub>1</sub> | R <sub>2</sub> |   | R <sub>n-2</sub> | R <sub>n-1</sub> |      |                | —              | —              | — | —                 | _  |      |                               | _                | _                | — | _                    | —                  |

| Х              | 7              | R <sub>0</sub>             | R <sub>1</sub> | R <sub>2</sub> |   | R <sub>n-1</sub> | Rn               | —    | _              |                | _              | _ | —                 | _  | —    | _                             | _                | —                | _ | _                    | $\left  - \right $ |

| —              | _              | Х                          | Х              | Х              |   | Х                | Х                | Н    | R <sub>0</sub> | R <sub>1</sub> | $R_2$          | _ | Rn-1              | Rn | _    | _                             | _                | _                | _ | _                    | $\left  - \right $ |

| _              | _              | P1                         | P <sub>2</sub> | P3             |   | Pn-1             | Pn               | L    | P <sub>0</sub> | P <sub>1</sub> | P2             |   | Pn-1              | Pn | L    | $\overline{P}_{\overline{0}}$ | $\overline{P_1}$ | $\overline{P_2}$ |   | $\overline{P}_{n-1}$ | $\overline{Pn}$    |

| _              | _              | _                          | _              |                | _ | —                | _                | _    | Х              | Х              | Х              |   | Х                 | Х  | Н    | Hi-Z                          | Hi-Z             | Hi-Z             |   | Hi-Z                 | Hi-Z               |

## Table 1. 4-Wire Serial-Interface Truth Table

L = Low-logic level

H = High-logic level

X = Don't care

P = Present state

R = Previous state

$\overline{\text{OE}}$  is independent of the operation of the serial interface. Data can be shifted into the serial-interface shift register and latched regardless of the state of  $\overline{\text{OE}}$ .

DOUT is the serial-data output, which shifts data out from the MAX6978's 8-bit shift register on the rising edge of CLK. Data at DIN is propagated through the shift register and appears at DOUT eight clock cycles later.

Watchdog

The MAX6978 includes a watchdog circuit that monitors the CLK, DIN, and LE inputs. If there is no transition on any one of these inputs for nominally 1s, then the output latches are cleared and outputs OUT0–OUT7 go high impedance like the initial power-up condition. This turns off all LEDs connected to the outputs. The shift-register data does not change, just the output-latch data.

The watchdog is intended to be used as a fail-safe feature for applications, which prefer a blank display to an incorrect display if the serial interface fails. When the watchdog triggers, the outputs remain off until the driver output latches are updated with data turning them on. Recovery is therefore automatic if the transmission failure is temporary, because the MAX6978 does not lock up in the watchdog timeout state. The MAX6978 operates correctly when the serial interface is next activated, and the watchdog circuit is reset and starts monitoring the serial interface again. The watchdog function requires no software change to the application driving the MAX6978.

#### **LED Fault Detection**

The MAX6978 includes circuitry that detects open-circuit LEDs automatically. An open-circuit fault occurs when an output is programmed to sink current but less than about 50% of the programmed current flows. Open circuits are checked just after the rising edge of LE, when new LED data is loaded into the output latches from the shift register(s). If one or more output port is detected with an open-circuit fault, then the 2 bits, D6 and D5, in the serial-interface shift register are both set high. If no open-circuit faults are detected, then D6 and D5 are both cleared low. The data in other 6-bit positions in the serial-interface shift register is not altered.

Fault status is automatically shifted out on DOUT when the next data transmission is shifted in. LE is normally taken high after all 8 bits of new LED data have been clocked into the shift register, and so at that time, DOUT is outputting data bit D7. On the next two rising edges of CLK, the 2 fault status bits, D6 and D5, are clocked out in that order, followed by the remaining 5 unchanged data bits D4 to D0.

A typical fault-detecting application tests all the shifted out data. Bits D0–D4 and D7 are checked against the originally transmitted data to check data link integrity. Bits D5 and D6 are checked first to see that they con-

Figure 2. 4-Wire Serial-Interface Timing Diagram

Figure 3. LE and CLK to OUT\_ Timing

tain the same data (validating the status), and second whether faults are reported by the actual logic level.

The fault status bit identifies which driver chip has at least one open-circuit LED. It is possible to determine how many LEDs driven by a chip are at fault by running eight test patterns, each of which lights a different single LED. The fault status bit then effectively identifies only one output at a time.

## Applications Information

#### Selecting External Component RSET to Set LED Output Current

The MAX6978 uses an external resistor R<sub>SET</sub> to set the LED current for outputs OUT0–OUT7. The minimum allowed value of R<sub>SET</sub> is 307.6 $\Omega$ , which sets the output currents to 55mA. The maximum allowed value of R<sub>SET</sub> is 1.5k $\Omega$ . The reference value, 360 $\Omega$ , sets the output currents to 50mA. To set a different output current, use the formula:

#### RSET = 18,000 / IOUT

where IOUT is the desired output current in mA.

#### **Computing Power Dissipation**

The upper limit for power dissipation ( $P_D$ ) for the MAX6978 is determined from the following equation:

$P_{D} = (V + x I +) + (V_{OUT} \times DUTY \times I_{OUT} \times N)$

where:

$V_{+} = supply voltage$

I+ = operating supply current when sinking I<sub>OUT</sub> LED drive current into N outputs

DUTY = PWM duty cycle applied to  $\overline{OE}$

N = number of MAX6978 outputs driving LEDs at the same time (maximum is 8)

V<sub>OUT</sub> = MAX6978 port output voltage when driving load LED(s)

IOUT = LED drive current programmed by RSET

$P_D$  = power dissipation, in mW if currents are in mA Dissipation example:

IOUT = 47mA, N = 8, DUTY = 1, VOUT = 2V, V+ = 5.25V

$P_D = (5.25V \times 25mA) + (2V \times 1 \times 47mA \times 8) = 0.883W$

Thus, for a 16-pin TSSOP package ( $T_{JA} = 1 / 0.0213 = +46.95^{\circ}$ C/W from the *Absolute Maximum Ratings*), the maximum allowed ambient temperature  $T_A$  is given by:

so T<sub>A</sub> = +108.5°C.

#### **Overtemperature Cutoff**

The MAX6978 contains an internal temperature sensor that turns off all outputs when the die temperature exceeds approximately +165°C. The outputs are enabled again when the die temperature drops below approximately +140°C. Register contents are not affected, so when a driver is overdissipating the external symptom will be the load LEDs cycling between on and off as the driver repeatedly overheats and cools, alternately turning the LEDs off and then back on again.

#### **Power-Supply Considerations**

The MAX6978 operates with a chip supply V+, and one or more LED supplies. Bypass each supply to GND with a 0.1µF capacitor as close to the MAX6978 as possible. This is normally adequate for static LED driving. For multiplex or PWM applications, it is necessary to add an additional bulk electrolytic capacitor of 4.7µF or more to each supply for every 4 to 16 MAX6978s. The necessary capacitance depends on the LED load current, PWM switching frequency, and serial interface speed. Inadequate V+ decoupling can cause timing problems, and very noisy LED supplies can affect LED current regulation.

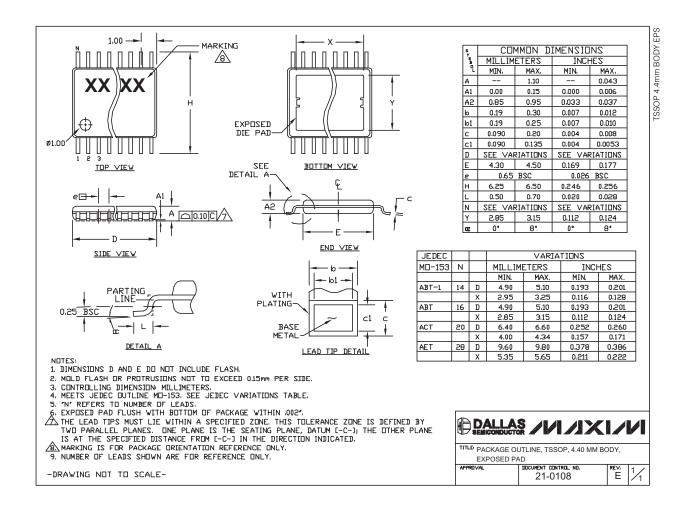

For the TSSOP version, connect the underside exposed pad to GND.

## \_Chip Information

TRANSISTOR COUNT: 2382 PROCESS: BICMOS

# **MAX6978**

|         |                   |                           |                       | Sel                    | ector Guide |

|---------|-------------------|---------------------------|-----------------------|------------------------|-------------|

| PART    | NO. OF<br>OUTPUTS | MAX OUTPUT<br>VOLTAGE (V) | MAX OUTPUT<br>CURRENT | LED FAULT<br>DETECTION | WATCHDOG    |

| MAX6968 |                   |                           |                       | _                      | _           |

| MAX6977 | 8                 | 5.5                       |                       | Yes                    | —           |

| MAX6978 |                   |                           |                       | Yes                    | Yes         |

| MAX6970 |                   |                           | ]                     | _                      | —           |

| MAX6981 | 8                 | 36                        |                       | Yes                    | —           |

| MAX6980 |                   |                           | EEmA                  | Yes                    | Yes         |

| MAX6969 |                   |                           | 55mA                  | —                      | —           |

| MAX6984 | 16                | 5.5                       |                       | Yes                    | —           |

| MAX6979 |                   |                           |                       | Yes                    | Yes         |

| MAX6971 |                   |                           | Ī                     | _                      | —           |

| MAX6982 | 16                | 36                        |                       | Yes                    | _           |

| MAX6983 |                   |                           |                       | Yes                    | Yes         |

# **Typical Application Circuit**

# \_ Package Information

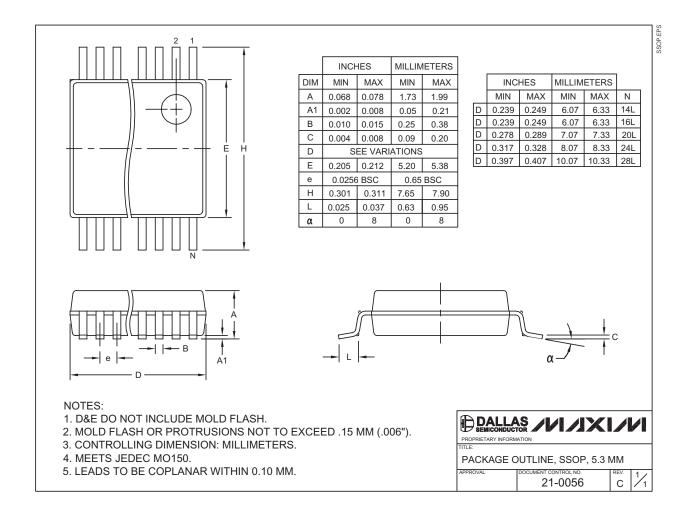

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

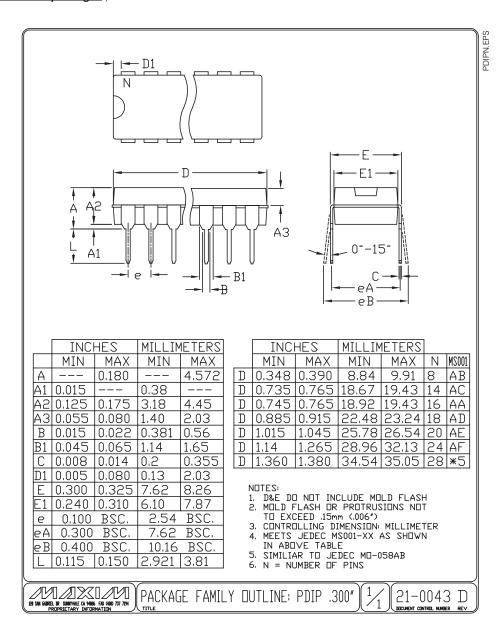

# Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

# **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2005 Maxim Integrated Products Printed USA MAXIM is a registered trademark of Maxim Integrated Products, Inc.

13

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: MAX6978AUE+ MAX6978AUE+T