#### **MAX3520**

## **DOCSIS 3.0 Upstream Amplifier**

#### **General Description**

The MAX3520 is an integrated CATV upstream amplifier IC designed to exceed the DOCSIS 3.0 requirements. The amplifier covers a 5MHz to 85MHz input frequency range (275MHz, 3dB bandwidth), and is capable of transmitting four QPSK modulated carriers, each at +58dBmV, simultaneously within this range. Both input and output ports are differential, requiring that an external balun be used at the output port. The gain is controlled in 1dB steps over a 63dB range using a SPI 3-wire interface.

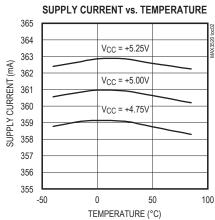

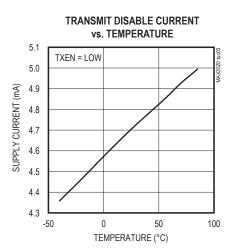

The MAX3520 operates from a single +5V supply. Four power codes are provided to allow maximum supply current to be reduced as determined by distortion requirements. In addition, for each power code, supply current is automatically reduced as gain is reduced while maintaining distortion performance. For DOCSIS 3.0 applications, the MAX3520 draws 360mA at 33dB gain, dropping to 300mA at 31dB gain. The MAX3520 supply current drops to 5mA between bursts to minimize power dissipation in transmit-disable mode. Control logic levels are 3.3V CMOS.

The MAX3520 is available in a 20-pin TQFN package, and operates over the extended industrial temperature range (-40°C to +85°C).

#### **Applications**

- DOCSIS 3.0 Cable Modems

- VOIP Modems

- Set-Top Boxes

#### **Features**

- +5V Supply Voltage

- Ultra-Low 25mW Dissipation in Transmit-Disable Mode

- 63dB Gain Control Range in 1dB Steps

- -63dBc Harmonic Distortion at 64dBmV Output

- Small 5mm x 5mm TQFN Package

- Low Burst On/Off Transient

- 275MHz, 3dB Bandwidth

Ordering Information appears at end of data sheet.

Typical Application Circuit appears at end of data sheet.

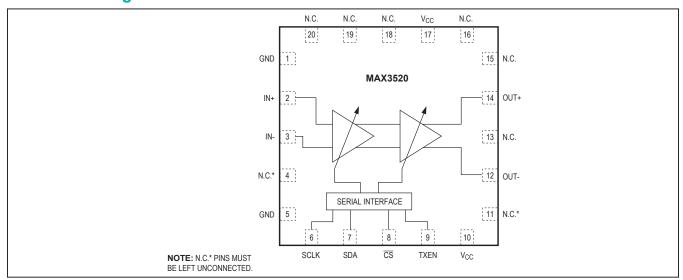

## **Functional Diagram**

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND                   | 0.3V to +5.5V                    | Operating Temperature Range       | 40°C to +85°C  |

|------------------------------------------|----------------------------------|-----------------------------------|----------------|

| IN+, IN                                  | 0.3V to (V <sub>CC</sub> + 0.3V) | Junction Temperature              | +150°C         |

| OUT+, OUT                                | 0.3V to (V <sub>CC</sub> + 3.6V) | Storage Temperature Range         | 65°C to +165°C |

| TXEN, SDA, SCLK, CS                      | 0.3V to +4.2V                    | Lead Temperature (soldering, 10s) | +300°C         |

| RF Input Power                           | +10dBm                           | Soldering Temperature (reflow)    | +260°C         |

| Continuous Power Dissipation (TA         | = +70°C)                         |                                   |                |

| (derate 29mW/°C above T <sub>A</sub> = + | 70°C)2000mW                      |                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

(*Typical Application Circuit* as shown,  $V_{CC}$  = 4.75V to 5.25V,  $V_{GND}$  = 0V, TXEN = high,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                               | SYMBOL             | CONDITIONS                                     | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------|--------------------|------------------------------------------------|------|-----|------|-------|

| Supply Voltage                          | V <sub>CC</sub>    |                                                | 4.75 |     | 5.25 | V     |

| Supply Current Transmit                 | l                  | Gain code = 63, power code = 3 (33dB gain typ) |      | 360 | 385  | m A   |

| Mode                                    | Icc                | Gain code = 59, power code = 1 (29dB gain typ) |      | 190 |      | mA    |

| Supply Current Transmit<br>Disable Mode | Icc                | TXEN = low                                     |      | 5   | 6.5  | mA    |

| Input High Voltage                      | V <sub>INH</sub>   |                                                | 2.0  |     | 3.6  | V     |

| Input Low Voltage                       | V <sub>INL</sub>   |                                                |      |     | 0.7  | V     |

| Input High Current                      | I <sub>BIASH</sub> |                                                |      |     | 10   | μA    |

| Input Low Current                       | I <sub>BIASH</sub> |                                                | -10  |     |      | μA    |

#### **AC Electrical Characteristics**

(*Typical Application Circuit* as shown,  $V_{CC}$  = 4.75V to 5.25V,  $V_{GND}$  = 0V, TXEN = high,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                             | SYMBOL          | CONDITIONS                                                     | MIN   | TYP   | MAX | UNITS |  |

|-------------------------------------------------------|-----------------|----------------------------------------------------------------|-------|-------|-----|-------|--|

| Frequency Range                                       | f <sub>IN</sub> | (Note 2)                                                       | 5     | -     | 85  | MHz   |  |

|                                                       |                 | Gain code = 63                                                 | 32 33 |       | 34  |       |  |

|                                                       |                 | Gain code = 53                                                 | 22    | 23    | 24  | 1     |  |

| Voltage Gain, $Z_{IN} = 200\Omega$ ,                  |                 | Gain code = 43                                                 | 12    | 13    | 14  |       |  |

| $Z_{OUT} = 75\Omega$ ,<br>Power Code = 3<br>(Note 3)  | A <sub>V</sub>  | Gain code = 33                                                 | 2     | 3     | 4   | dB    |  |

|                                                       |                 | Gain code = 23                                                 | -8    | -7    | -6  |       |  |

|                                                       |                 | Gain code = 13                                                 | -18   | -17   | -16 |       |  |

|                                                       |                 | Gain code = 03                                                 | -28   | -27   | -26 |       |  |

| Voltage Gain Variation with Power Code, Any Gain Code |                 |                                                                |       | ±0. 1 |     | dB    |  |

| Gain Rolloff                                          |                 | Voltage gain = -28dB to +33dB, f <sub>IN</sub> = 5MHz to 85MHz |       | -0.3  |     | dB    |  |

## **AC Electrical Characteristics (continued)**

(*Typical Application Circuit* as shown,  $V_{CC}$  = 4.75V to 5.25V,  $V_{GND}$  = 0V, TXEN = high,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                               | SYMBOL           | CONDITIONS                                                                             | MIN | TYP  | MAX | UNITS             |

|---------------------------------------------------------|------------------|----------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| Gain Step Size                                          |                  | Voltage gain = -28dB to +33dB, f <sub>IN</sub> = 5MHz to 85MHz                         | 0.7 | 1.0  | 1.3 | dB                |

| Transmit-Disable Mode<br>Noise                          |                  | Any BW = 160kHz from 5MHz to 85MHz, TXEN = low, voltage gain = -27dB to +33dB (Note 4) |     |      | -66 | dBmV              |

| Isolation in Transmit-Disable Mode                      |                  | TXEN = low                                                                             |     | 80   |     | dB                |

| Noise Figure                                            | NF               | Transmit mode, voltage gain = +13dB to +33dB (Note 4)                                  |     |      | 11  | dB                |

| Noise Figure Slope                                      |                  | Transmit mode, voltage gain = -27dB to +33dB                                           |     | -1.0 |     | dB/dB             |

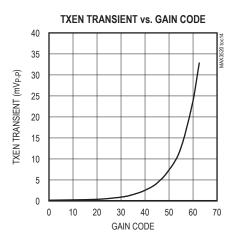

| Transmit-Disable/Transmit-<br>Enable Transient Duration |                  | TXEN input rise/fall time < 0.1μs                                                      |     | 2    |     | μs                |

| Transmit-Disable/Transmit-                              |                  | Gain = 33dB                                                                            |     | 25   | 80  | m)/               |

| Enable Transient Step Size                              |                  | Gain = 4dB                                                                             |     | 1    |     | mV <sub>P-P</sub> |

| Input Impedance                                         | Z <sub>IN</sub>  | Balanced                                                                               |     | 200  |     | Ω                 |

| Input Return Loss                                       |                  | 200Ω system                                                                            |     | 15   |     | dB                |

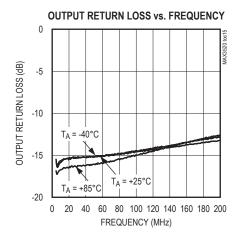

| Output Return Loss                                      |                  | 75Ω system (Note 4)                                                                    | 11  | 15   |     | dB                |

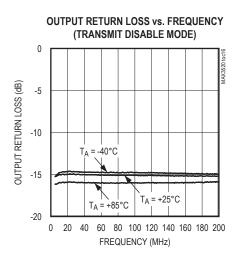

| Output Return Loss in Transmit-Disable Mode             |                  | 75Ω system, TXEN = low (Note 4)                                                        | 11  | 15   |     | dB                |

| 2nd Harmonic Distortion                                 | HD2              | Input tone at 33dBmV, V <sub>OUT</sub> = +64dBmV, power code = 3 (Note 4)              |     | -66  | -57 | dBc               |

| 3rd Harmonic Distortion                                 | HD3              | Input tone at 33dBmV, V <sub>OUT</sub> = +64dBmV, power code = 3 (Note 4)              |     | -65  | -59 | dBc               |

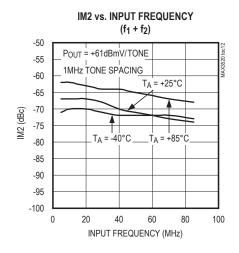

| Two-Tone 2nd-Order Distortion                           | IM2              | Input tones at 30dBmV, V <sub>OUT</sub> = +61dBmV/tone, power code = 3 (Note 4)        |     | -67  | -57 | dBc               |

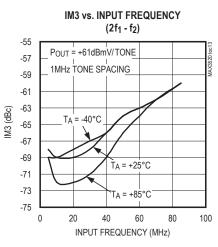

| Two-Tone 3rd-Order Distortion                           | IM3              | Input tones at 30dBmV, V <sub>OUT</sub> = +61dBmV/tone, power code = 3 (Note 4)        |     | -63  | -57 | dBc               |

| Four Tone Spurs                                         |                  | Four input tones at 27dBmV,<br>V <sub>OUT</sub> = +58dBmV/tone, power code = 3         |     | -58  |     | dBc               |

| Output 1dB Compression Point                            | P <sub>1dB</sub> | Gain = 32dB                                                                            |     | 74   |     | dBmV              |

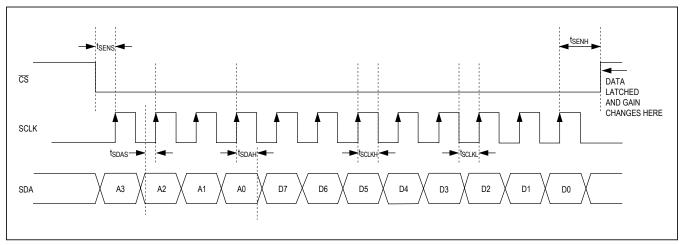

## **Timing Characteristics**

(Typical Application Circuit as shown,  $V_{CC}$  = 4.75V to 5.25V,  $V_{GND}$  = 0V,  $T_A$  = -40°C to +85°C, unless otherwise specified. Typical values are at  $V_{CC}$  = 5V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                 | SYMBOL             | CONDITIONS | MIN | TYP | MAX | UNITS |

|---------------------------|--------------------|------------|-----|-----|-----|-------|

| SEN to SCK Rise Set Time  | t <sub>SENS</sub>  |            |     | 20  |     | ns    |

| SEN to SCK Rise Hold Time | t <sub>SENH</sub>  |            |     | 10  |     | ns    |

| SDA to SCK Setup Time     | t <sub>SDAS</sub>  |            |     | 20  |     | ns    |

| SDA to SCK Hold Time      | t <sub>SDAH</sub>  |            |     | 10  |     | ns    |

| SCK Pulse-Width High      | tsclkh             |            |     | 50  |     | ns    |

| SCK Pulse-Width Low       | t <sub>SCLKL</sub> |            |     | 50  |     | ns    |

| Maximum CLK Frequency     |                    |            | 10  |     |     | MHz   |

Note 1: Min/max values are production tested at  $T_A = +85^{\circ}$ C. Min/max limits at  $T_A = -40^{\circ}$ C and  $T_A = +25^{\circ}$ C are guaranteed by design and characterization.

Note 2: Production tested at 10MHz and 85MHz.

Note 3: Voltage gain does not include loss due to input and output transformers.

Note 4: Guaranteed by design and characterization.

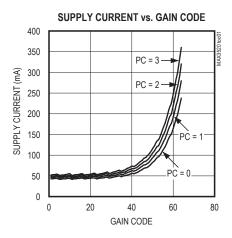

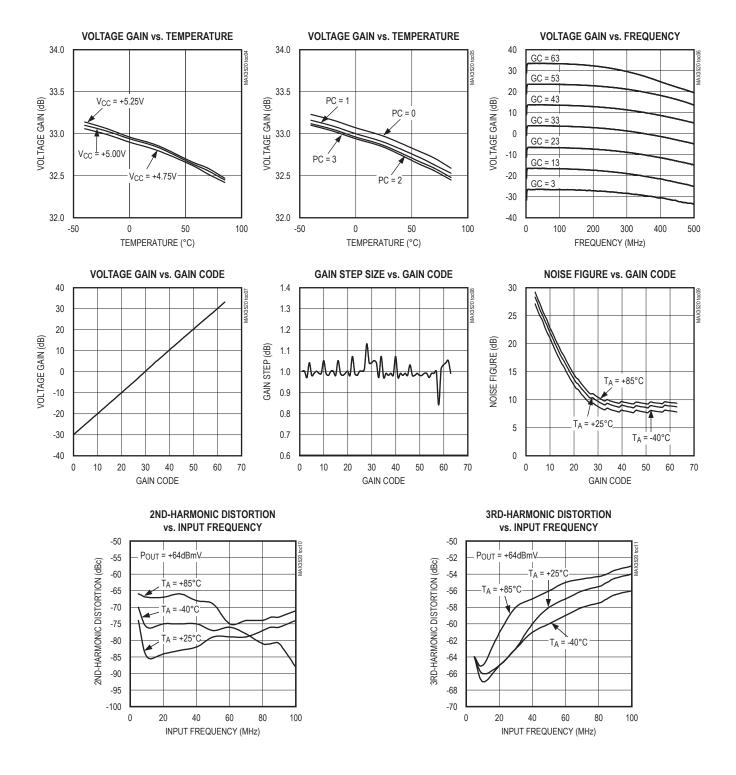

## **Typical Operating Characteristics**

$(\text{MAX3520 EV kit, V}_{\text{CC}} = +5\text{V, V}_{\text{IN}} = 33\text{dBmV, f}_{\text{IN}} = 42\text{MHz, Z}_{\text{LOAD}} = 75\Omega, T_{\text{A}} = +25^{\circ}\text{C, power code} = 3, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

(MAX3520 EV kit,  $V_{CC}$  = +5V,  $V_{IN}$  = 33dBmV,  $f_{IN}$  = 42MHz,  $Z_{LOAD}$  = 75 $\Omega$ ,  $T_A$  = +25°C, power code = 3, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(MAX3520 EV kit,  $V_{CC}$  = +5V,  $V_{IN}$  = 33dBmV,  $f_{IN}$  = 42MHz,  $Z_{LOAD}$  = 75 $\Omega$ ,  $T_A$  = +25°C, power code = 3, unless otherwise noted.)

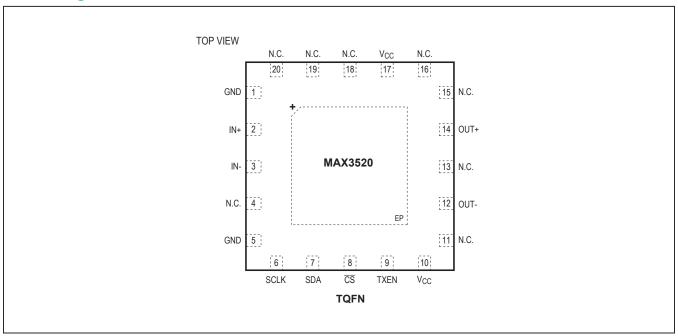

# **Pin Configuration**

# **Pin Description**

| PIN                       | NAME            | FUNCTION                                                         |

|---------------------------|-----------------|------------------------------------------------------------------|

| 1, 5                      | GND             | Ground                                                           |

| 2                         | IN+             | Positive PGA Input                                               |

| 3                         | IN-             | Negative PGA Input                                               |

| 4, 11                     | N.C.            | No Connection. These pins must remain open.                      |

| 6                         | SCLK            | Serial Interface Clock                                           |

| 7                         | SDA             | Serial Interface Data                                            |

| 8                         | CS              | Serial Interface Enable                                          |

| 9                         | TXEN            | Transmit Enable. TXEN = high places the device in transmit mode. |

| 10                        | V <sub>CC</sub> | Supply Voltage for Serial Interface                              |

| 12                        | OUT-            | Negative Output                                                  |

| 13, 15, 16, 18,<br>19, 20 | N.C.            | No Connection. Connect these pins to ground.                     |

| 14                        | OUT+            | Positive Output                                                  |

| 17                        | V <sub>CC</sub> | Supply Voltage for Programmable-Gain Amplifier (PGA)             |

| _                         | EP              | Exposed Pad. Connect EP to ground.                               |

## **Detailed Description**

#### **Programmable-Gain Amplifier**

The programmable-gain amplifier (PGA) provides 63dB of output level control in 1dB steps. The gain of the PGA is determined by a 6-bit gain code (GC5–GC0) programmed through the serial data interface (<u>Table 1</u> and <u>Table 2</u>). Specified performance is achieved when the input is driven differentially.

Four power codes (PC1–PC0) allow the PGA to be used with reduced bias current when distortion performance can be relaxed. In addition, for each power code, bias current is automatically reduced with gain code for maximum efficiency.

The PGA features a differential Class A output stage capable of driving four +58dBmV QPSK modulated signals, or a single +64dBmV QPSK modulated signal into a 75 $\Omega$  load. This architecture provides superior even-order distortion performance but requires that a transformer be used to convert to a single-ended output. In transmit-disable mode, the output amplifiers are powered down, resulting in low output noise, while maintaining impedance match.

# 3-Wire Serial Interface (SPI) and Control Registers

The MAX3520 includes two programmable registers for initializing the part and setting the gain and power consumption. The 4 MSBs are address bits; the 8 least significant bits (LSBs) are used for register data. Data is shifted MSB first.

**Note:** The registers must be written  $100\mu s$  after the device is powered up, and no earlier. Once a new set of register data is clocked in, the corresponding power code and/or gain code does not take effect until  $\overline{CS}$  transitions from low to high.

#### **Applications Information**

#### **Power Codes**

The MAX3520 is designed to exceed the stringent linearity requirements of DOCSIS 3.0 using power code (PC) 3. For DOCSIS 2.0, PC = 1 is recommended, which results in substantial supply current reduction. The full range of gain codes can be used in any power code. The gain difference between power codes is typically less than 0.1dB.

**Table 1. Register Description**

| REGISTER   | REGISTER | DATA 8 BITS |     |     |     |     |     |     |     |

|------------|----------|-------------|-----|-----|-----|-----|-----|-----|-----|

| NAME       | ADDRESS  | B7          | В6  | B5  | B4  | В3  | B2  | B1  | В0  |

| Power/Gain | 0000     | PC1         | PC0 | GC5 | GC4 | GC3 | GC2 | GC1 | GC0 |

| Initialize | 0001     | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Table 2. Reg 00 Gain Control

| BIT NAME | BIT LOCATION<br>(0 = LSB) | RECOMMENDED<br>DEFAULT | FUNCTION                                                                                                                                                              |

|----------|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC[1:0]  | 7,6                       | 11                     | Sets the power code, which controls the bias current drawn by the device in transmit mode:  11 - PC = 3, maximum current draw                                         |

| GC[5:0]  | 5,4,3,2,1,0               | 11 1111                | Sets the gain code, which determines the voltage gain of the amplifier:  11 1111 - GC = 63, voltage gain = 36dB (typ).  11 1110 - GC = 62, voltage gain = 35dB (typ). |

| BIT NAME | BIT LOCATION<br>(0 = LSB) | RECOMMENDED<br>DEFAULT | FUNCTION                                                                 |

|----------|---------------------------|------------------------|--------------------------------------------------------------------------|

| _        | 7,6,5,4,3,2,1,0           | 0000 0000              | Must be programmed to 0000 0000 upon power-up for specified performance. |

**Table 3. Initialize Register**

Figure 1. SPI 3-Wire Interface Timing Diagram

#### **Transmit Disable Mode**

Between bursts in a DOCSIS system, the MAX3520 should be put in transmit-disable mode by setting TXEN low. The output transient on the cable is kept well below the DOCSIS requirement during the TXEN transitions.

If a gain or power change is required, new values of PC and GC should be clocked in during transmit-disable mode (TXEN low). The new operating point of the MAX3520 is set when  $\overline{\text{CS}}$  transitions high during the time between bursts.

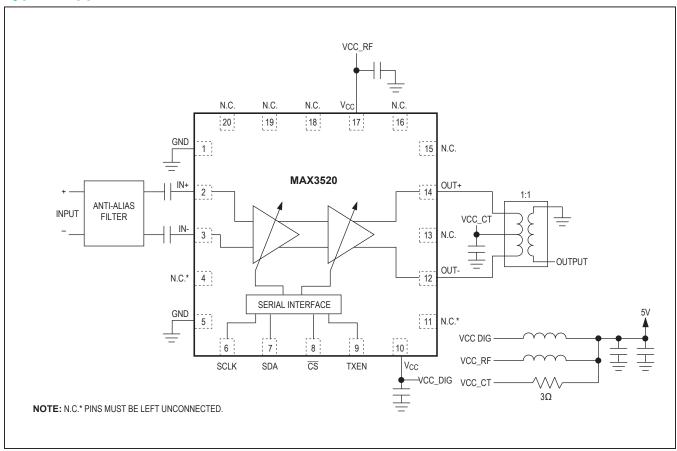

#### **Output Transformer**

The MAX3520 output circuits are open-collector differential amplifiers. On-chip resistors across the collectors provide a nominal output impedance of  $75\Omega$  in transmit mode and transmit-disable mode. To match the output of the MAX3520 to a single-ended  $75\Omega$  load, a 1:1 transformer is required. This transformer must have adequate bandwidth to cover the intended application. Note that some RF transformers specify bandwidth with a  $50\Omega$  source on the primary and a matching resistance on the secondary winding. Operating in a  $75\Omega$  system tends to shift the low-frequency edge of the transformer bandwidth specification up by a factor of 1.5 due to primary inductance. Keep this in mind when specifying a transformer.

Bias to the output stage is provided through the center tap on the transformer primary. This greatly diminishes the on/off transients present at the output when switching between transmit and transmit-disable modes. Commercially available transformers typically have adequate balance between half-windings to achieve substantial transient cancellation.

Finally, keep in mind that transformer core inductance varies with temperature. Adequate primary inductance must be present to sustain broadband output capability as temperatures vary.

#### **Input Circuit**

To achieve rated performance, the inputs of the MAX3520 must be driven differentially with an appropriate input level. The differential input impedance is  $200\Omega$ . Most applications require an anti-alias filter preceding the device. The filter should be designed to match this  $200\Omega$  impedance.

The MAX3520 has sufficient gain to produce an output level of +64dBmV QPSK when driven with a +33dBmV input signal. If an input level greater than +34dBmV is used, the 3rd-order distortion performance will degrade slightly.

#### **Layout Issues**

A well-designed printed circuit board (PCB) is an essential part of an RF circuit. For best performance, pay attention to power-supply layout issues as well as the output circuit layout.

#### **No Connect Pins**

Pins 4 and 11 must be left open, not connected to supply or ground or any other node in the circuit. Pins 13, 15, 16, 18, 19, and 20 should be connected to ground.

#### **Output Circuit Layout**

The differential implementation of the MAX3520 output has the benefit of significantly reducing even-order distortion, the most significant of which is 2nd-harmonic distortion. The degree of distortion cancellation depends on the amplitude and phase balance of the overall circuit. It is important to keep the trace lengths from the output pins equal.

#### **Power-Supply Layout**

For minimal coupling between different sections of the IC, the ideal power-supply layout is a star configuration. This configuration has a large-value decoupling capacitor at the central power-supply node. The power-supply traces branch out from this node, each going to a separate power-supply node in the circuit. At the end of each

of these traces is a decoupling capacitor that provides a very low impedance at the frequency of interest. This arrangement provides local power-supply decoupling at each power-supply pin. The power-supply traces must be capable of carrying the maximum current without significant voltage drop.

The output transformer center tap node, VCC\_CT, must be connected to supply through a  $3\Omega$  resistor to reduce the supply voltage on OUT+ and OUT-. This resistor must be rated to dissipate 250mW at +85°C.

#### **Exposed Pad Thermal Considerations**

The exposed pad (EP) of the MAX3520's 20-pin TQFN package provides a low thermal resistance path to the die. It is important that the PCB on which the MAX3520 is mounted be designed to conduct heat from this contact. In addition, the EP should be provided with a low-inductance path to electrical ground.

It is recommended that the EP be soldered to a ground plane on the PCB, either directly or through an array of plated via holes.

## **Chip Information**

PROCESS: SiGe BiCMOS

## **Typical Application Circuit**

## **Ordering Information**

| PART        | <b>TEMP RANGE</b> | PIN PACKAGE |

|-------------|-------------------|-------------|

| MAX3520ETP+ | -40°C to +85°C    | 20 TQFN-EP* |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND PATTERN NO. |  |  |

|-----------------|-----------------|----------------|------------------|--|--|

| 20 TQFN-EP      | T2055+5         | 21-0140        | 90-0010          |  |  |

<sup>\*</sup>EP = Exposed pad.

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                           | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------|------------------|

| 0                  | 9/11             | Initial release                       | _                |

| 1                  | 5/12             | Updated Transmit Disable Mode section | 9                |

For information on other Maxim Integrated products, visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX3520ETP+T MAX3520ETP+G2Z

Other:

MAX3520ETP+ MAX3520ETP+TG2Z