#### **MAX41470**

## 290MHz to 960MHz ASK/FSK Receiver with SPI Interface

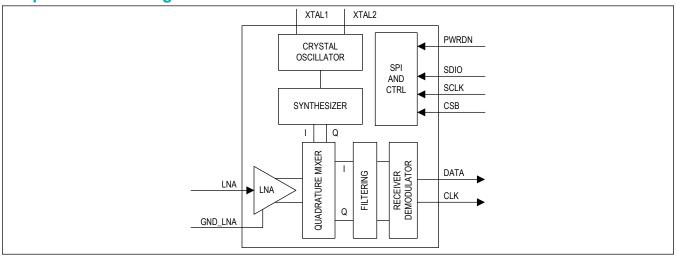

### **General Description**

The MAX41470 is a high-performance, low-power receiver that is ideal for amplitude shift-keyed (ASK) and frequency shift-keyed (FSK) data. The receiver can be configured for three popular sub-1GHz bands while using a single low-cost 16MHz crystal: 287MHz to 320MHz, 425MHz to 480MHz, and 860MHz to 960MHz.

The MAX41470 is capable of both ASK and FSK reception and is also fully programmable through an SPI interface.

The receiver has excellent RF sensitivity and allows input signals up to 0dBm of power at the RF input. With an integrated IF filter, a few external components, and low operating/power-down currents, the MAX41470 receiver is ideal for cost- and power-sensitive applications. The chip also includes a low-noise amplifier (LNA), fully differential image-rejection mixer, on-chip phase-locked loop (PLL) with integrated voltage-controlled oscillator (VCO), received signal strength indicator (RSSI), and digital demodulation.

The device operates in the 1.8V to 3.6V supply voltage range and also features a power-saving, fully programmable, self-polling (duty cycling) mode with preamble detection and interrupt output to wake up an external microcontroller unit (MCU).

The parts are available in a 12-pin thin QFN (TQFN) package and are specified for the -40°C to +105°C extended temperature range.

## **Applications**

- Home Automation and Security

- Building Access Control

- Garage Door Openers (GDO)

- Remote Keyless Entry (RKE)

- Tire Pressure Monitoring Systems (TPMS)

- Restaurant Pagers

#### **Benefits and Features**

- Low Bill of Materials (BOM)

- · No External Balun, No External Filter, etc.

- Single Low-Cost 16MHz External Crystal

- · Long Range with High Sensitivity

- Low Power Consumption

- 9mA Operating Supply Current

- 10nA Power-Down Current

- Self-Polling (Remote Wake-Up) for Reduced Power

- · Preamble Detection with Interrupt Output

- Average Current as Low as 350μA

- · Duty Cycle Less Than 1% Capable

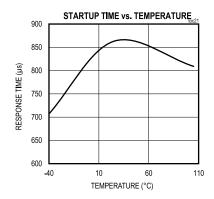

- Fast Startup Time

- Automatic Gain Control (AGC) Adjusted Digital RSSI

- Automatic Frequency Control (AFC)

- Fast Frequency Switching Frac-N Synthesizer

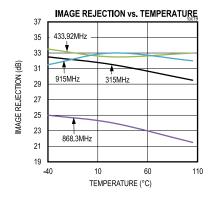

- 33dB Calibrated Image Rejection

- Passes ETSI Category 2 Blocking Requirements

- ±2.5kV HBM ESD Protection, ±4kV on LNA Input

- Up to 200kbps Data Rate (NRZ)

- 1.8V to 3.6V Supply Voltage

- -40°C to +105°C Operating Temperature Range

- 4mm x 4mm, 12-TQFN with 0.8mm Pitch

Ordering Information appears at end of datasheet.

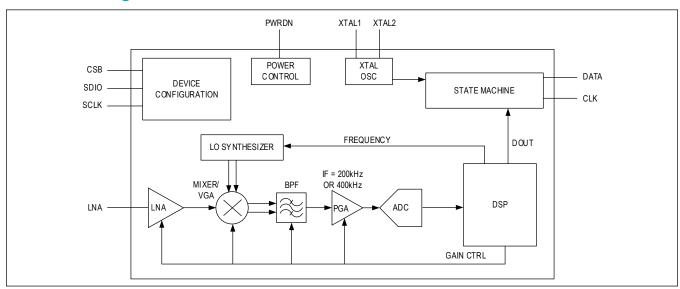

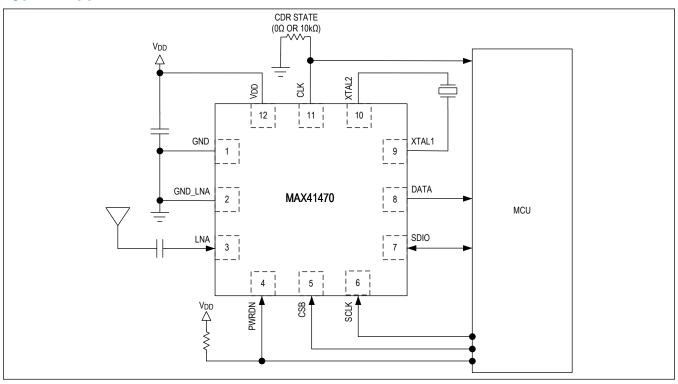

## **Simplified Block Diagram**

## **TABLE OF CONTENTS**

| General Description                                | 1  |

|----------------------------------------------------|----|

| Applications                                       | 1  |

| Benefits and Features                              | 1  |

| Simplified Block Diagram                           | 2  |

| Absolute Maximum Ratings                           | 7  |

| Package Information                                | 7  |

| 12 TQFN                                            | 7  |

| Electrical Characteristics                         | 7  |

| Typical Operating Characteristics                  | 11 |

| Pin Configuration                                  | 13 |

| Pin Description                                    | 14 |

| Functional Diagrams                                | 14 |

| Detailed Description                               | 15 |

| Power States                                       | 15 |

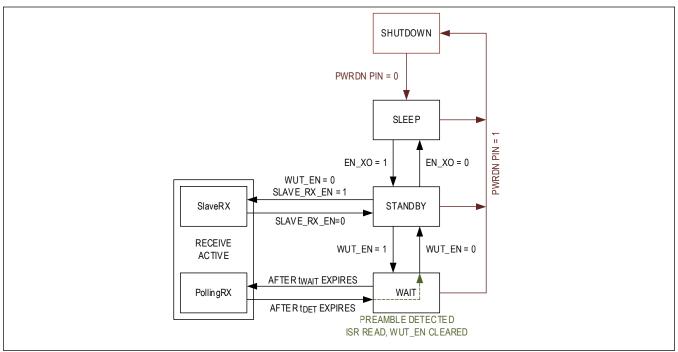

| State Diagram                                      | 15 |

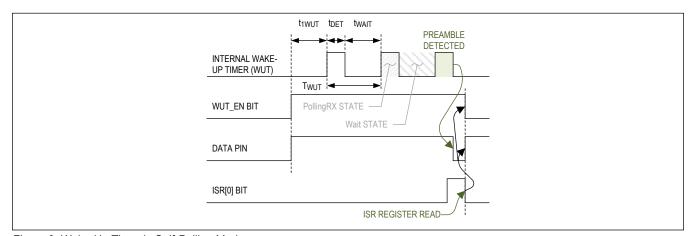

| Self-Polling Mode                                  | 16 |

| Preamble Detector                                  | 17 |

| DATA Pin                                           | 18 |

| Selection of Intermediate Frequency                | 18 |

| Selection of Channel Filter                        |    |

| Demodulator Configuration                          | 19 |

| Automatic Gain Control (AGC)                       | 20 |

| Received Signal Strength Indicator (RSSI)          | 21 |

| Automatic Frequency Control (AFC)                  | 21 |

| Frequency Error Indicator (FEI)                    | 22 |

| AFC Freeze upon Preamble Detection                 | 22 |

| Recommended Data Rate and Post Demodulation Filter | 22 |

| ASK Decision Threshold                             | 23 |

| Lower Bound of ASK Decision Threshold              | 24 |

| Squelching ASK Receiver                            | 25 |

| Receiver Sensitivity                               | 25 |

| ASK Receiver Configurations                        | 25 |

| FSK Receiver Configurations                        | 26 |

| Modulation Index Equals Approximately 0.8          | 28 |

| Serial Peripheral Interface (SPI)                  |    |

| Crystal (XTAL) Oscillator                          |    |

| Crystal Divider                                    |    |

| Phase-Locked Loop (PLL)                            | 31 |

## TABLE OF CONTENTS (CONTINUED) Register Details . .

## MAX41470

# 290MHz to 960MHz ASK/FSK Receiver with SPI Interface

| LIST OF FIGURES                                      |    |

|------------------------------------------------------|----|

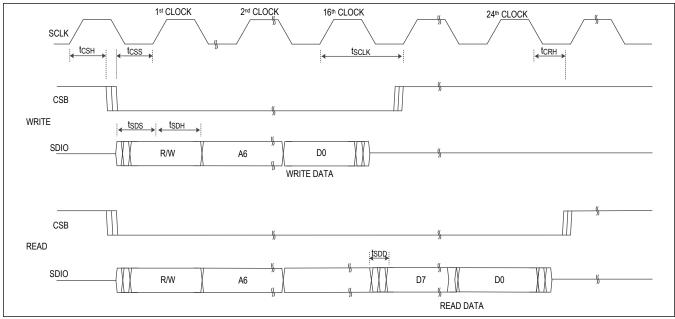

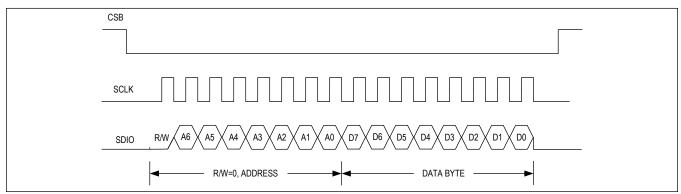

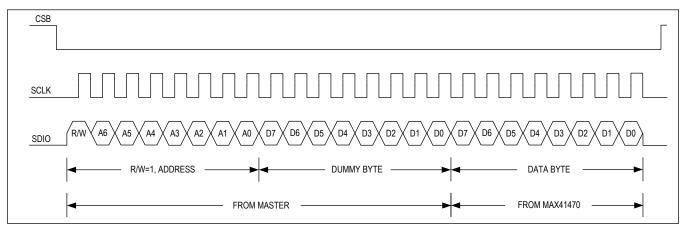

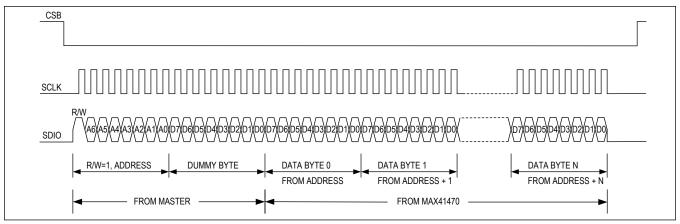

| Figure 1. SPI Serial Timing Interface Timing Diagram |    |

| Figure 2. State Diagram                              | 16 |

| Figure 3. Wake-Up Timer in Self-Polling Mode         | 17 |

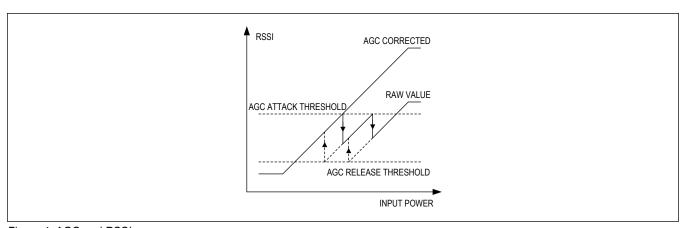

| Figure 4. AGC and RSSI                               | 20 |

| Figure 5. 3-Wire SPI Write                           | 29 |

| Figure 6. 3-Wire SPI Read                            | 29 |

| Figure 7. 3-Wire SPI Burst Read                      | 30 |

| LIST OF TABLES                                                               |    |

|------------------------------------------------------------------------------|----|

| Table 1. Supply Current in Four Power States                                 | 15 |

| Table 2. State Transition Time                                               | 16 |

| Table 3. Manchester Encoding for Preamble                                    | 17 |

| Table 4. PREAM_LEN Limitation for Guaranteed Detection                       | 18 |

| Table 5. Intermediate Frequency Selection                                    | 18 |

| Table 6. Channel Filter Selection                                            | 19 |

| Table 7. Recommended Programming of DEMOD_TCTRL                              | 19 |

| Table 8. Options of FSK Demodulator Configuration for 400kHz IF (IF_SEL = 0) | 19 |

| Table 9. Options of FSK Demodulator Configuration for 200kHz IF (IF_SEL = 1) | 20 |

| Table 10. AGC Operating Modes                                                | 20 |

| Table 11. AGC Fine-Tuning for Data Rate                                      | 21 |

| Table 12. Post Demodulation Filter Bandwidth                                 | 23 |

| Table 13. Programming of ATH_TC                                              | 23 |

| Table 14. Programming of ATH_GC                                              | 24 |

| Table 15. Lookup Table for MU1                                               | 24 |

| Table 16. Lookup Table for MU2                                               | 24 |

| Table 17. ASK Receiver for 400kHz IF                                         | 25 |

| Table 18. ASK Receiver for 200kHz IF                                         | 26 |

| Table 19. FSK Receiver for 400kHz IF                                         | 26 |

| Table 20. FSK Receiver for 200kHz IF                                         | 27 |

| Table 21. FSK Receiver for 400kHz IF                                         | 28 |

| Table 22. FSK Receiver for 200kHz IF                                         | 28 |

| Table 23. SPI Controls                                                       | 29 |

| Table 24. Required Crystal Divider Programming                               | 30 |

| Table 25. LODIV Setting                                                      | 31 |

| Table 26. Clock Data Recovery Operation Mode                                 | 31 |

| Table 27. Programming of LD_BW and LD_BUF                                    | 32 |

| Table 28. Quick Start Configurations                                         | 45 |

| Table 29. AFC Pull-In Range (for 16MHz Crystals)                             | 47 |

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND                 | 0.3V to +4V                        |

|----------------------------------------|------------------------------------|

| GND_LNA to GND                         | 0.3V to 0.3V                       |

| All Other Pins to GND                  |                                    |

| Continuous Power Dissipation (Single L | ayer Board) $(T_A = +70^{\circ}C,$ |

| derate 16.9mW/°C above +70°C.)         | 1349.1mW                           |

| Continuous Power Dissipation (Multilayer | Board) ( $T_A = +70^{\circ}C$ , |

|------------------------------------------|---------------------------------|

| derate 24.4mW/°C above +70°C)            | 1951.2mW                        |

| Operating Temperature Range              | 40°C to +105°C                  |

| Junction Temperature                     | +150°C                          |

| Storage Temperature Range                | 40°C to +150°C                  |

| Soldering Temperature (reflow)           | +260°C                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### **12 TQFN**

| T1244+4                                 |  |  |  |  |

|-----------------------------------------|--|--|--|--|

| <u>21-0139</u>                          |  |  |  |  |

| 90-0068                                 |  |  |  |  |

| Thermal Resistance, Single-Layer Board: |  |  |  |  |

| 59.3°C/W                                |  |  |  |  |

| 6°C/W                                   |  |  |  |  |

| Thermal Resistance, Four-Layer Board:   |  |  |  |  |

| 41°C/W                                  |  |  |  |  |

| 6°C/W                                   |  |  |  |  |

|                                         |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

(<u>Typical Application Circuit</u>, typical values are at  $V_{DD}$  = +3.0V,  $T_A$  = +25°C, ASK at input frequency = 433.92MHz, Manchester encoded, IF = 400kHz, RXBW = 340kHz with 16MHz crystal oscillator, unless otherwise noted. (Note 1))

| PARAMETER         | SYMBOL                | CONDITIONS | MIN | TYP                                               | MAX  | UNITS |

|-------------------|-----------------------|------------|-----|---------------------------------------------------|------|-------|

| DC SPECIFICATIONS |                       |            |     |                                                   |      |       |

| Supply Voltage    | V <sub>DD</sub>       |            | 1.8 |                                                   | 3.6  | V     |

| Supply Current    | I <sub>VDD_RCV</sub>  |            |     | 9                                                 | 14   | mA    |

| Shutdown Current  | I <sub>SHDN</sub>     |            |     | 10                                                | 1000 | nA    |

| Standby Current   | I <sub>SDBY</sub>     |            |     | 320                                               |      | μA    |

| Sleep Current     | I <sub>DD_SLEEP</sub> |            |     | 1                                                 |      | μA    |

| AC SPECIFICATIONS |                       |            |     |                                                   |      |       |

| Frequency Range   |                       |            |     | 287 to<br>320,<br>425 to<br>480,<br>860 to<br>960 |      | MHz   |

## **Electrical Characteristics (continued)**

( $\underline{Typical\ Application\ Circuit}$ , typical values are at  $V_{DD}$  = +3.0V,  $T_A$  = +25°C, ASK at input frequency = 433.92MHz, Manchester encoded, IF = 400kHz, RXBW = 340kHz with 16MHz crystal oscillator, unless otherwise noted. (Note 1))

| PARAMETER                                  | SYMBOL                | COND                                                                                             | ITIONS                                                                                          | MIN  | TYP                                | MAX   | UNITS |  |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------------------------------------|-------|-------|--|

| Maximum Receiver Input Level               | P <sub>RFIN_MAX</sub> | Modulation depth > 20dB                                                                          |                                                                                                 | -20  | 0                                  |       | dBm   |  |

| Maximum Channel<br>Bandwidth               |                       | -3dB bandwidth at 40                                                                             | 00kHz IF                                                                                        |      | 300                                |       | kHz   |  |

| Minimum Polling Mode<br>Duty Cycle         |                       |                                                                                                  |                                                                                                 |      | 0.775                              |       | %     |  |

| AC SPECIFICATIONS / S                      | ENSITIVITY / FS       | SK .                                                                                             |                                                                                                 |      |                                    |       | •     |  |

|                                            |                       | RXBW = 340kHz, 10 deviation = ±80kHz,                                                            |                                                                                                 |      | -100                               |       |       |  |

|                                            |                       | RXBW = 340kHz, 62<br>deviation = ±40kHz                                                          | .5kbps, FSK                                                                                     |      | -106                               |       |       |  |

| Sensitivity Limit FSK (Note 2)             |                       | RXBW = 24kHz, 10k<br>±8kHz                                                                       | bps, FSK deviation =                                                                            |      | -116                               |       | dBm   |  |

|                                            |                       | RXBW = 12kHz, 2kb<br>±2kHz                                                                       | ps, FSK deviation =                                                                             |      | -120                               |       |       |  |

|                                            |                       | RXBW = 12kHz, 250<br>±2kHz                                                                       | bps, FSK deviation =                                                                            |      | -127                               |       | 1     |  |

| AC SPECIFICATIONS / S                      | ENSITIVITY / AS       | SK                                                                                               |                                                                                                 |      |                                    |       | •     |  |

|                                            |                       | RXBW = 340kHz, 62.5kbps, f <sub>RF</sub> = 868MHz, modulation depth ≥ 20dB  RXBW = 120kHz, 5kbps |                                                                                                 |      | -103                               |       |       |  |

| Sensitivity Limit ASK                      |                       |                                                                                                  |                                                                                                 |      | -116                               |       |       |  |

| (Note 2)                                   |                       | RXBW = 120kHz, 2kbps                                                                             |                                                                                                 |      | -118                               |       | dBm   |  |

|                                            |                       | RXBW = 24kHz, 1kbps                                                                              |                                                                                                 | -122 |                                    |       |       |  |

|                                            |                       | RXBW = 12kHz, 250bps                                                                             |                                                                                                 |      | -127                               |       |       |  |

| AC SPECIFICATIONS / S                      | Startup Time          |                                                                                                  |                                                                                                 |      |                                    |       | •     |  |

| Mariana Bassina                            |                       | Self-polling mode (Da<br>10kbps                                                                  | ATA high), ASK,                                                                                 |      | 450                                |       |       |  |

| Maximum Receiver<br>Start-Up Time (Note 2) |                       |                                                                                                  | Slave receiver mode, from sleep state to receive ready (including crystal startup time), 10kbps |      | 860                                |       | μs    |  |

| AC SPECIFICATIONS / F                      | LL TURN-ON TI         | ME                                                                                               |                                                                                                 |      |                                    |       |       |  |

| Minimum Synthesizer<br>Frequency Step      |                       |                                                                                                  |                                                                                                 |      | f <sub>XTAL</sub> /2 <sup>16</sup> |       | Hz    |  |

| AC SPECIFICATIONS / II                     | MAGE REJECTION        | ON                                                                                               |                                                                                                 |      |                                    |       |       |  |

| Imaga Poinction                            | IR_UNCAL              | Uncalibrated                                                                                     |                                                                                                 |      | 30                                 |       | dB    |  |

| Image Rejection                            | IR_CAL                | Calibrated                                                                                       |                                                                                                 |      | 33                                 |       | ub    |  |

| AC SPECIFICATIONS / BLOCKERS               |                       |                                                                                                  |                                                                                                 |      |                                    |       |       |  |

| Minimum Blocking Level                     |                       | 3dB desense (Note                                                                                | ±2MHz offset                                                                                    |      | -58                                |       | dBm   |  |

| withing blocking Level                     |                       | 3) ±10MHz offset                                                                                 |                                                                                                 |      | -40                                | UDIII |       |  |

| Selectivity                                |                       | 3dB desense (Note 3)                                                                             | ±300kHz offset,<br>IF = 200kHz                                                                  |      | 47                                 |       | dBc   |  |

## **Electrical Characteristics (continued)**

( $\underline{Typical\ Application\ Circuit}$ , typical values are at  $V_{DD}$  = +3.0V,  $T_A$  = +25°C, ASK at input frequency = 433.92MHz, Manchester encoded, IF = 400kHz, RXBW = 340kHz with 16MHz crystal oscillator, unless otherwise noted. (Note 1))

| PARAMETER                                                | SYMBOL                           | CONDITIONS                           | MIN  | TYP                       | MAX  | UNITS |

|----------------------------------------------------------|----------------------------------|--------------------------------------|------|---------------------------|------|-------|

| AC SPECIFICATIONS / N                                    | IAXIMUM DATA                     | ARATE                                |      |                           |      | 1     |

| Mariana data arta                                        |                                  | Manchester encoded                   |      | 100                       |      | 1.1   |

| Maximum data rate                                        |                                  | Nonreturn to zero (NRZ)              | 200  |                           | kbps |       |

| AC SPECIFICATIONS / R                                    | SSI                              |                                      |      |                           |      |       |

| RSSI Resolution                                          |                                  |                                      |      | ±0.5                      |      | dB    |

| RSSI Linear Dynamic<br>Range                             |                                  |                                      | 70   | 90                        |      | dB    |

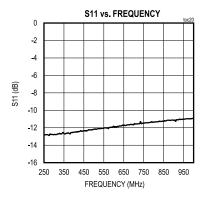

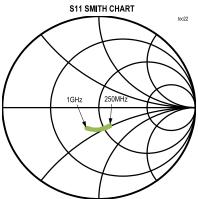

| AC SPECIFICATIONS / L                                    | NA                               |                                      |      |                           |      |       |

| Input Impedance                                          |                                  |                                      |      | 50                        |      | Ω     |

| CRYSTAL OSCILLATOR                                       |                                  | •                                    |      |                           |      |       |

| Crystal Frequency                                        | f <sub>XTAL</sub>                |                                      | 12.8 | 16                        | 19.2 | MHz   |

| Crystal Oscillator<br>Startup Time                       | t <sub>XO</sub>                  |                                      |      | 380                       |      | μs    |

| Crystal Load<br>Capacitance                              | $C_L$                            |                                      |      | 6                         |      | pF    |

| CMOS INPUT/OUTPUT (S                                     | SCLK, SDIO, C                    | SB, PWRDN, DATA)                     |      |                           |      |       |

| Input Low Voltage                                        | V <sub>IL</sub>                  | 1.8V compatible                      |      |                           | 0.36 | V     |

| Input High Voltage                                       | V <sub>IH</sub>                  | 1.8V compatible                      | 1.44 |                           |      | V     |

| Input Current                                            | I <sub>IL</sub> /I <sub>IH</sub> |                                      |      | ±10                       |      | μA    |

| Output Low Voltage                                       | $V_{OL}$                         | I <sub>SINK</sub> = 650μA            |      | 0.25                      |      | V     |

| Output High Voltage                                      | $V_{OH}$                         | I <sub>SOURCE</sub> = 350μA          |      | V <sub>DD</sub> -<br>0.25 |      | V     |

| Maximum Load<br>Capacitance at SDIO/<br>DATA Pins        | C <sub>LOAD</sub>                |                                      |      | 10                        |      | pF    |

| PWRDN Pin Glitch<br>Suppression                          | <sup>t</sup> GLITCH              | Glitches suppressed by PWRDN pin     |      | 1                         |      | ns    |

| SERIAL INTERFACE / SF                                    | PI (FIGURE 1)                    |                                      |      |                           |      |       |

| SCLK Frequency                                           | f <sub>SCLK</sub>                | 1/t <sub>SCLK</sub>                  |      |                           | 20   | MHz   |

| SCLK to CSB Setup<br>Time                                | t <sub>CSS</sub>                 |                                      |      | 10                        |      | ns    |

| SCLK to CSB Hold Time                                    | tcsH                             |                                      |      | 0                         |      | ns    |

| SDIO to SCLK Hold<br>Time                                | t <sub>SDH</sub>                 | Write                                |      | 0                         |      | ns    |

| SDIO to SCLK Setup<br>Time                               | t <sub>SDS</sub>                 | Write 5                              |      |                           | ns   |       |

| Minimum SCLK to SDIO                                     | <b>+</b>                         | Read, 10pF load from SDIO to ground  |      | 1.5                       | ns   |       |

| Data Delay tsDD_MIN Read, 100pF load from SDIO to ground |                                  | 3.5                                  |      | 115                       |      |       |

| Maximum SCLK to                                          |                                  |                                      | ne   |                           |      |       |

| SDIO Data Delay                                          | tsdd_max                         | Read, 100pF load from SDIO to ground |      | 11                        |      | ns    |

- Note 1: 100% tested at  $T_A$  = +25°C. Limits over operating temperature and relevant supply voltage are guaranteed by design and characterization over temperature.

- Note 2: All data rates are Manchester encoded, where 1kbps is equivalent to a 1kHz square wave representing a continuous string of "1" data bits. Average sensitivity at 433.92MHz, BER ≤ 0.2%.

- Note 3: Power referred to LNA input. Manchester 10kbps data rate, unless otherwise noted.

Figure 1. SPI Serial Timing Interface Timing Diagram

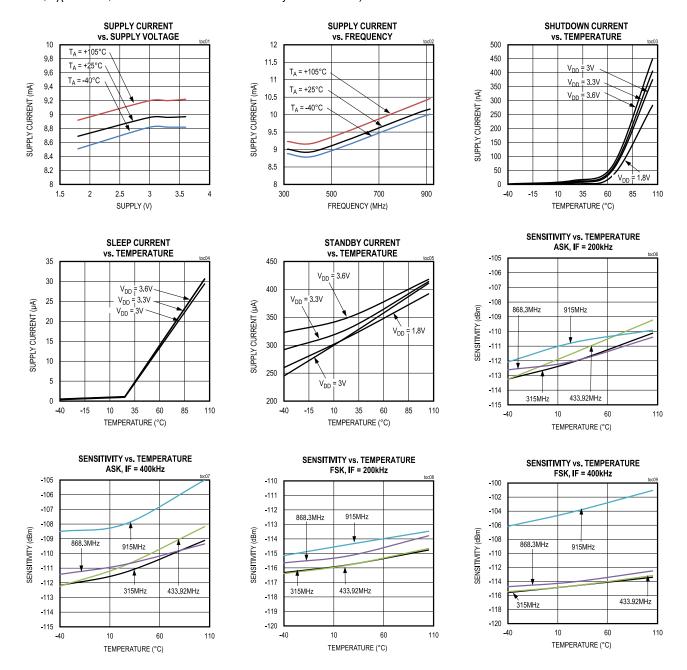

## **Typical Operating Characteristics**

(<u>Typical Application Circuit</u>. Typical values are for ASK at  $f_{RF}$  = 433.92MHz, IF = 400kHz, CHF = 340kHz, data rate = 5kbps,  $V_{DD}$  = +3V,  $T_A$  = +25°C, unless otherwise noted. Sensitivity at 0.2% BER.)

## **Typical Operating Characteristics (continued)**

(<u>Typical Application Circuit</u>. Typical values are for ASK at  $f_{RF}$  = 433.92MHz, IF = 400kHz, CHF = 340kHz, data rate = 5kbps,  $V_{DD}$  = +3V,  $T_A$  = +25°C, unless otherwise noted. Sensitivity at 0.2% BER.)

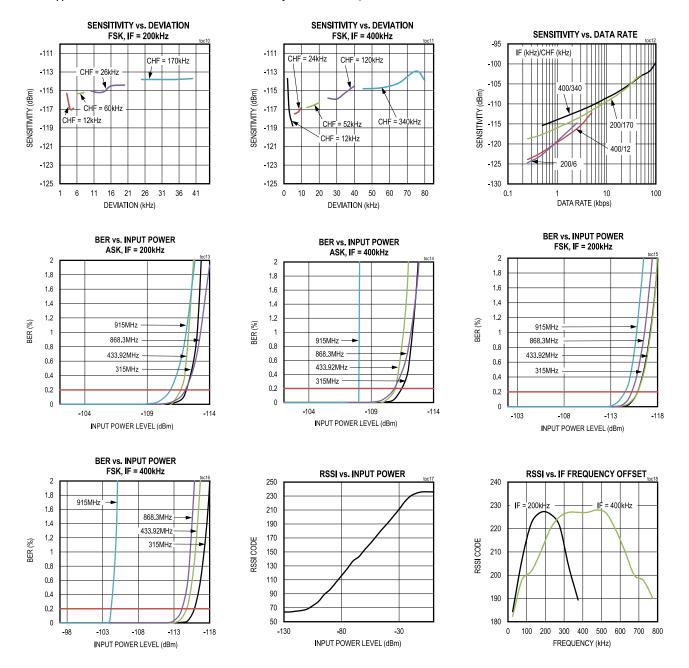

## **Typical Operating Characteristics (continued)**

(<u>Typical Application Circuit</u>. Typical values are for ASK at  $f_{RF}$  = 433.92MHz, IF = 400kHz, CHF = 340kHz, data rate = 5kbps,  $V_{DD}$  = +3V,  $T_A$  = +25°C, unless otherwise noted. Sensitivity at 0.2% BER.)

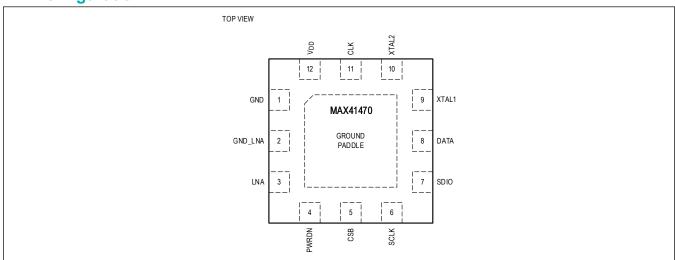

## **Pin Configuration**

## **Pin Description**

| PIN    | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1      | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 2      | GND_LNA | Ground for Low-Noise Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 3      | LNA     | Low-Noise Amplifier Input                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4      | PWRDN   | Power-Down, Active-High. When the pin is controlled by external MCU, apply logic-high for shutdown mode or logic-low to enable the device. After a falling edge of PWRDN, the internal registers are reset to default values. When the pin is connected to GND, the device cannot enter the lowest current shutdown state.  Proper start-up timing is for MCU to drive PWRDN high and wait for 1ms, then drive PWRDN low and wait for 0.2ms before writing to registers. |  |  |  |

| 5      | CSB     | Serial Interface Chip Select. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 6      | SCLK    | Serial Interface Clock Input for Register Programming                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 7      | SDIO    | Serial Interface Data Input/Output for Register Programming. When CSB is at logic-low.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 8      | DATA    | Data Output of Demodulated Received Signal                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 9      | XTAL1   | First Crystal Input. Can be driven single-ended.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 10     | XTAL2   | Second Crystal Input                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 11     | CLK     | Recovered Clock Output. If the clock output is disabled, connect to GND. If the clock output is enabled, tie the pin to GND through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                              |  |  |  |

| 12     | VDD     | Power-Supply Voltage. Connect a 0.01µF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| PADDLE | GND     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

## **Functional Diagrams**

## **Detailed Description**

The MAX41470 sub-GHz ISM RF receiver requires very few external components to complete the receiver signal chain from RF to bits. Depending on the signal power, data rates as high as 100kbps Manchester (200kbps NRZ) can be achieved.

This part is designed to receive ASK/OOK or FSK/GFSK modulated data in the 287MHz to 320MHz (nominally 315MHz), 425MHz to 480MHz (nominally 434MHz), and 860MHz to 960MHz (nominally 868MHz or 915MHz) ISM frequency bands.

The architecture of the MAX41470 is a low intermediate frequency (low-IF) receiver with digital demodulation. The antenna received signal is amplified and downconverted to a 400kHz or 200kHz IF. The local oscillator (LO) signal for downconversion is generated from an internal fractional-N PLL synthesizer and an external 16MHz crystal.

The analog receiver bandwidth is 350kHz (when IF = 400kHz) or 175kHz (when IF = 200kHz), corresponding to the IF selection. Digital channel filtering with programmable bandwidth is applied before demodulation. When the data rate is low, a narrow bandwidth channel filter can be selected to achieve high receiver sensitivity. Post-demodulation filtering with a programmable bandwidth is implemented in the digital domain where that filtered output is compared against an adaptive decision threshold to generate a 1-bit oversampled output on the DATA pin.

Supported features of the MAX4147x receiver family include: automatic gain control (AGC), a received signal strength indicator (RSSI), automatic frequency control (AFC), and a frequency error indicator (FEI).

The MAX41470 has an SPI interface to program the internal registers for full control of the device. For I<sup>2</sup>C programmability or preset capability, refer to the MAX41473/MAX41474 data sheet. When in programming mode, the MAX41470 can support self-polling operation based on a Manchester-encoded preamble detection to provide an interrupt signal on the DATA pin.

#### **Power States**

The MAX41470 receivers have four power states: Shutdown, Sleep, Standby, and Receive Active. Set the PWRDN pin low to enable (power on) the device and set PWRDN high to disable the radio. When the device is enabled, the device operational states are controlled through the serial interface by the internal registers.

Typically, PWRDN is driven by a GPIO pin from an MCU and must be driven high or low. When PWRDN is connected to GND, the device cannot enter Shutdown state.

| Table 1. Supply | Current in I | Four Power States |

|-----------------|--------------|-------------------|

|-----------------|--------------|-------------------|

| POWER STATE    | SUPPLY CURRENT<br>(TYP) | COMMENT                                       |

|----------------|-------------------------|-----------------------------------------------|

| Shutdown       | 10nA                    | No serial port access, register values lost   |

| Sleep          | 1μΑ                     | Serial port powered, register values retained |

| Standby        | 0.32mA                  | Crystal oscillator powered                    |

| Receive Active | 9mA                     | Entire receiver powered                       |

#### **State Diagram**

While in programming mode, the MAX41470 has two major operational states: slave-receiver and self-polling. While operating as a slave-receiver (SlaveRX), the MAX41470 is fully controlled by an external "master" MCU through the serial interface. In the self-polling operation (PollingRX), the MAX41470 periodically switches between standby and receiving states according to preprogrammed times, interrupts, and MCU control.

<u>Figure 2</u> is a simplified state diagram of the MAX41470. When the PWRDN pin is set high, the device will enter the low-current Shutdown state. The PWRDN should be held high for at least 1ms before transitioning to low. When the PWRDN pin is driven low, the internal supply is turned on and the device enters the Sleep state with all the internal registers reset to default values. Programming through the serial interface is allowed after a typical turn-on time of 400µs to allow settling of the device. Programming while in the Sleep state is not recommended, except for writing a 1 to the EN\_XO bit in order to change the device to the Standby state. It is recommended the user perform serial communications while in

the Standby state. To enable SlaveRX operation from the Standby state, the user writes a 0 to the WUT\_EN bit and a 1 to the SLAVE\_RX\_EN bit. All three register bits used to control the power state (EN\_XO, WUT\_EN, and SLAVE\_EN) can be found in the STATE\_CTRL1 (0x14) register.

While in the SlaveRX state, the user can read but *not write* values to the DIG\_RX registers and, in general, the device configuration cannot be changed while the receiver is active (SlaveRX or PollingRX states). The SlaveRX state does support access to the STATE\_CTRL1 (0x14) register, for example, when writing SLAVE\_RX\_EN = 0 to turn off the receiver and change the device state back to Standby.

Figure 2. State Diagram

#### **Table 2. State Transition Time**

| EVENT                   | STATE TRANSITION           | TYPICAL TIME<br>(µs) |

|-------------------------|----------------------------|----------------------|

| PWRDN Pin Cleared to 0  | Shutdown to Sleep          | 400                  |

| EN_XO Bit Set           | Sleep to Standby           | 380                  |

| SLAVE_RX_EN Bit Set     | Standby to SlaveRX         | 320                  |

| SLAVE_RX_EN Bit Cleared | SlaveRX to Standby         | 10                   |

| EN_XO Bit Cleared       | Standby to Sleep           | 10                   |

| WUT_EN Bit Set          | Standby to Wait            | 10                   |

| PWRDN Pin Set to 1      | From any state to Shutdown | 10                   |

#### **Self-Polling Mode**

Self-polling operation is enabled by writing a 1 to the WUT\_EN bit while the device is in the Standby state. This allows the user to place the master MCU into a low-power mode, allowing the MAX41470 to automatically toggle between a low-current Wait state and the higher-current PollingRX state. The periodic toggling is controlled by the internal wake-up timer (WUT) signal, which is a pulse chain as illustrated in Figure 3.

The duration the receiver is in the PollingRX state (detection time or  $t_{DET}$ ) is adjustable from 0.48ms to 20.88ms, in 0.08ms steps, by programming the TDET[7:0] field in the WUT1 (0x17) register. This detection time should be set to a value longer than the receiver turn-on time (<u>Table 2</u>) plus the preamble pattern duration. For guaranteed detection, refer to the details under the *Preamble Detector* section. The WUT period is defined as:

where  $T_{WUT}$  is the wake-up time period,  $t_{DET}$  is the programmed detection time,  $t_{WAIT}$  is the wait time, and  $N_{RATIO}$  is the programmed ratio of  $t_{DET}/t_{WAIT}$ , thus  $T_{WUT}$  is an integer multiple ( $\geq 2$ ) of  $t_{DET}$ .

The ratio of  $t_{WAIT}$  to  $t_{DET}$  ( $N_{RATIO}$ ) is adjustable from 1 to 128 in step size of 1 by programming the TSBY\_TDET\_RATIO[6:0] field in the WUT2 (0x18) register. Therefore, the WUT duty cycle is programmable from 1/2 to 1/129. The WUT response time ( $t_{1WUT}$ ) is approximately the same as  $t_{WAIT}$ .

In self-polling mode, the DATA pin serves as an interrupt source for an MCU. Once a preamble bit pattern is received and validated in the PollingRX state, the PREAMB\_DET bit in the interrupt status register ISR (0x13) will be set to 1, and a falling edge will be generated on the DATA pin to wake up an MCU at the completion of the polling cycle. After wakeup, the user must read the ISR (0x13) register to automatically clear the PREAMB\_DET bit and WUT\_EN bit in the STATE\_CTRL1 (0x14) register. The MAX41470 will thus exit self-polling mode and assert the DATA output pin to logic 1. With the read to the ISR register, the resulting state is Standby and a write to the SLAVE\_RX\_EN bit is required to transition into the SlaveRX state.

Figure 3. Wake-Up Timer in Self-Polling Mode

#### **Preamble Detector**

The MAX41470 provides a preamble detector to be used with the self-polling operation. The preamble must be Manchester encoded as shown in <u>Table 3</u>. The pattern length, from 1 to 16 bits, is set in the PREAMB\_LEN[3:0] register field where 0x0 = 1 bit in length and 0xF = 16 bits in length. The non-encoded or raw bit pattern is programmed into PREAMB\_WORD[15:0] (addresses 0x0E and 0x0D) noting that PREAMB\_WORD[0] is the LSB of the bit pattern and this is the most recent or last bit received from the RF bit stream. As bits are received and demodulated, they are effectively shifted in and compared to the PREAMB\_WORD from the LSB to the MSB.

**Table 3. Manchester Encoding for Preamble**

| RAW BIT | MANCHESTER EDGE (BAUD) | DECODED BITS |

|---------|------------------------|--------------|

| 0       | _ _                    | 10           |

| 1       | _[_                    | 01           |

For guaranteed preamble detection within the first  $t_{DET}$  cycle, the  $t_{DET}$  width would allow margin for the case where the first bit of the preamble was not received when  $t_{DET}$  state was entered. The resulting equation would be:

PREAM LEN + PREAM LEN - 1 = 2 × PREAM LEN - 1

Due to the  $t_{DET}$  time range of 0.48ms to 20.88ms, the number of bits that can fit into this range and comply with the guaranteed  $t_{DET}$  detection equation of 2 x PREAM\_LEN - 1 dictates a limitation on the number of bits detectable given a defined bit rate. For example, if the Manchester data rate is 250bps and guarantee detection with PREAM\_LEN = 16, this would equate to 2 x 16 - 1 = 31 bits required. To receive 31 bits at 250bps, it would take the following:

$$\frac{1}{\text{DataRate}} \times \text{bits required} = \frac{1}{250 \text{bps}} \times 31 \text{bits} = 124 \text{ms}$$

But the maximum  $t_{DET}$  allowed is 20.88ms. The table below states the limitations for the lower data rates if using the guaranteed timing. If the data rate is above those listed, there is no limitation.

Table 4. PREAM LEN Limitation for Guaranteed Detection

| DATA RATE (bps) | MAX PREAM_LEN BITS | t <sub>DET</sub> DURATION (ms) |

|-----------------|--------------------|--------------------------------|

| 250             | 3                  | 20                             |

| 500             | 5                  | 18                             |

| 1k              | 10                 | 19                             |

| 2k              | 16                 | 15.5                           |

For example, if PREAMB\_LEN[3:0] is programmed to 0xA (decimal value 10), then the preamble bit pattern is specified by PREAMB\_WORD[10:0], and the preamble is 22 bits after decoding the Manchester edges (or 11 raw bits before encoding). In this example, the five MSBs in the PREAMB\_WORD field [15:11] are not used.

The preamble detector is triggered when the received bit stream matches the Manchester version of the PREAMB\_WORD without regard to the phase of the pattern. For example, a non-Manchester preamble word of 0xFF = Manchester 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.101 0.1

#### **DATA Pin**

The DATA pin toggles while in the SlaveRX state to output a digital binary representation of received data. The digital base band system has a minimum requirement to oversample the signal by 16x thus limiting the data rate of received signal to no more than 100kbps Manchester (200kbps NRZ).

In self-polling operation, the DATA pin serves as both an interrupt source and the data stream from the digital baseband system. The DATA pin is driven to logic 1 while in the PollingRX state. If no match is made to the preamble pattern, the device will move to the Wait state and the DATA pin will continue to be driven high. Once the preamble pattern is detected in the PollingRX state, a falling edge will be generated on the DATA pin right after the device switches to the Wait state and DATA will be held at logic 0. After the ISR register has been read, the DATA pin will be driven back to logic 1 and the device will be placed into the Standby state (as the WUT\_EN bit is cleared automatically).

To begin streaming data from the DATA pin, the receiver needs to be moved from Standby to the SlaveRX state by writing a 1 to the SLAVE\_RX\_EN bit in the STATE\_CTRL (0x14) register. This operation can be performed right after reading the ISR register.

If the ISR register is not read (cleared) within the initial  $t_{WAIT}$  time, the receiver will automatically re-enter the PollingRX state and set the DATA pin back to logic 1. Since the ISR was not cleared during the previous cycle, the preamble detect is still triggered and once the  $t_{DET}$  time expires, the receiver will again indicate an interrupt by driving the DATA pin to 0 after it re-enters the Wait state. This cycle will continue until the ISR register is cleared.

#### **Selection of Intermediate Frequency**

The IF can be selected between two values by programming the IF\_SEL bit in the IF\_CHF\_SEL (0x02) register.

**Table 5. Intermediate Frequency Selection**

| INTERMEDIATE FREQUENCY (kHz) | ANALOG BANDWIDTH (kHz) | IF_SEL |

|------------------------------|------------------------|--------|

| 400                          | 350                    | 0      |

| 200                          | 175                    | 1      |

#### **Selection of Channel Filter**

The digital channel filter (CHF) can be selected by programming the CHF\_SEL[2:0] field in the IF\_CHF\_SEL (0x02) register. Aggregate receiver bandwidth also depends on the IF selection. See <u>Table 6</u> for digital channel filter settings.

**Table 6. Channel Filter Selection**

| 400kHz IF RECEIVER BW (kHz) | 200kHz IF RECEIVER BW (kHz) | CHF_SEL |

|-----------------------------|-----------------------------|---------|

| 340                         | 170                         | 0       |

| 120                         | 60                          | 1       |

| 52                          | 26                          | 2       |

| 24                          | 12                          | 3       |

| 12                          | 6                           | 4       |

#### **Demodulator Configuration**

The modulation mode is selected by programming the ASK\_FSK\_SEL bit in the IF\_CHF\_SEL (0x0) register. Write a 0 to the ASK\_FSK\_SEL bit for ASK modulation, or a 1 to the ASK\_FSK\_SEL bit for FSK modulation.

The ASK/FSK demodulator configuration depends on the DEMOD\_TCTRL[2:0] and DEMOD\_FSK[2:0] fields in the DEMOD (0x00) register. DEMOD TCTRL should be programmed according to the formulas in <u>Table 7</u>:

Table 7. Recommended Programming of DEMOD TCTRL

| MODULATION | CONDITIONS  |                           | DEMOD TOTAL      |

|------------|-------------|---------------------------|------------------|

| WODULATION | ASK_FSK_SEL | ATH_TYPE                  | - DEMOD_TCTRL    |

| FSK        | 1           | X                         | 4 – CHF_SEL      |

| ASK        | 0           | 0 (preLPF for Manchester) | min(2+SRC_LG, 7) |

| ASK        | 0           | 1 (aPD for NRZ)           | min(3+SRC_LG, 7) |

The DEMOD\_FSK field is used only in FSK mode. There are a total of 28 options for configuring the FSK demodulator, as seen in the following tables:

Table 8. Options of FSK Demodulator Configuration for 400kHz IF (IF\_SEL = 0)

| NOMINAL<br>FSK ±∆f<br>(kHz) | RANGE OF<br>FSK ±∆f<br>(kHz) | IF_SEL | CHF_SEL | DEMOD_FSK |

|-----------------------------|------------------------------|--------|---------|-----------|

| 80*                         | [64, 84]                     | 0      | 0       | 0         |

| 57                          | [50, 67]                     | 0      | 0       | 1         |

| 44                          | [40, 50]                     | 0      | 0       | 2         |

| 40                          | [32, 42]                     | 0      | 1       | 3         |

| 29                          | [25, 33]                     | 0      | 1       | 4         |

| 22                          | [20, 25]                     | 0      | 1       | 5         |

| 20                          | [16, 21]                     | 0      | 2       | 3         |

| 14                          | [12.5, 16.5]                 | 0      | 2       | 4         |

| 11                          | [10, 12.5]                   | 0      | 2       | 5         |

| 10                          | [8, 10.5]                    | 0      | 3       | 4         |

| 7                           | [5.3, 8]                     | 0      | 3       | 5         |

| 5                           | [4, 5.3]                     | 0      | 4       | 4         |

| 3                           | [2.6, 4]                     | 0      | 4       | 5         |

| 2                           | [1.6, 2.6]                   | 0      | 4       | 6         |

Table 9. Options of FSK Demodulator Configuration for 200kHz IF (IF\_SEL = 1)

| · ·                         |                              |        |         |           |

|-----------------------------|------------------------------|--------|---------|-----------|

| NOMINAL<br>FSK ±∆f<br>(kHz) | RANGE OF<br>FSK ±∆f<br>(kHz) | IF_SEL | CHF_SEL | DEMOD_FSK |

| 40                          | [32, 42]                     | 1      | 0       | 0         |

| 28.5                        | [25, 33.5]                   | 1      | 0       | 1         |

| 22                          | [20, 25]                     | 1      | 0       | 2         |

| 20                          | [16, 21]                     | 1      | 1       | 3         |

| 14.5                        | [12.5, 16.5]                 | 1      | 1       | 4         |

| 11                          | [10, 12.5]                   | 1      | 1       | 5         |

| 10                          | [8,10.5]                     | 1      | 2       | 3         |

| 7                           | [6.3, 8.2]                   | 1      | 2       | 4         |

| 5.5                         | [5, 6.3]                     | 1      | 2       | 5         |

| 5                           | [4, 5.2]                     | 1      | 3       | 4         |

| 3.5                         | [2.6, 4]                     | 1      | 3       | 5         |

| 2.5                         | [2, 2.6]                     | 1      | 4       | 4         |

| 1.5                         | [1.3, 2]                     | 1      | 4       | 5         |

| 1                           | [0.8, 1.3]                   | 1      | 4       | 6         |

### **Automatic Gain Control (AGC)**

The MAX41470 provides a dual-step feedback AGC, as illustrated in <u>Figure 4</u>. AGC attack, or high-to-low gain switching, happens when the raw RSSI value is higher than a threshold. AGC release, or low-to-high gain switching, happens when the raw RSSI value is lower than a second threshold. The difference between the attack and release thresholds should be large enough to provide hysteresis.

Figure 4. AGC and RSSI

The AGC operation mode is controlled by the AGC\_EN\_BO[1:0] field in the AGC (0x01) register.

### **Table 10. AGC Operating Modes**

| AUTOMATIC<br>GAIN CONTROL | RSSI DYNAMIC RANGE (TYP) (dB) | AGC_EN_BO | COMMENT         |

|---------------------------|-------------------------------|-----------|-----------------|

| Disabled                  | 36                            | 0         | Not recommended |

<sup>\*</sup> Default setting

**Table 10. AGC Operating Modes (continued)**

|         | 42 | 1  | Wider RSSI dynamic range  |

|---------|----|----|---------------------------|

| Enabled | 85 | 2* | Best receiver sensitivity |

| Enabled | 83 | 3  | Not recommended           |

<sup>\*</sup>Default setting

The release threshold of AGC can be fine-tuned by programming the AGC THREL[3:0] field.

### **Table 11. AGC Fine-Tuning for Data Rate**

| MODULATION | DATA RATE (kbps) | AGC_THREL |

|------------|------------------|-----------|

| ASK        | ≤26              | 0x9       |

| ASK        | >26              | 0xF       |

| FSK        | ≤51.5            | 0x9       |

| rok        | >51.5            | 0xF       |

### Received Signal Strength Indicator (RSSI)

The MAX41470 features an AGC-corrected RSSI, as illustrated in <u>Figure 4</u>. To get a large dynamic range of RSSI, the AGC EN BO register should be programmed to enable the AGC.

The RSSI is a dynamic value, readable from the RSSI (0x10) register with a scale of 0.5dB per bit. The RSSI is *not* calibrated based on an absolute power level at the LNA input, so part-to-part variations of receiver front-end gain will affect this RSSI value.

The RSSI functions as a logarithmic envelope detector followed by a peak detector. The discharge slope of the RSSI peak detector is expressed as:

$$PD_{SIOPE} = 1.67 \times 2^{N}$$

(µs/div)

where N = max(IF SEL + CHF SEL + DEMOD TCTRL + RSSI DT - 1, 0).

Because the RSSI scale is 0.5dB/div, the time constant of 3dB discharge is  $(10 \times 2^{N}) \mu s$ .

#### **Automatic Frequency Control (AFC)**

A feedback control loop is used to adjust the PLL synthesizer frequency within a programmable range. The center of the AFC range is programmed by 24-bit frequency word LO\_CTR\_FREQ[23:0], which can be calculated from the following equation with the default LO injection setting when MIX\_HS\_LSBAR = 0:

$$LO\_CTR\_FREQ = INT \left( 65536 \frac{\left( f_{RF} - f_{IF} \right)}{f_{XTAL}} \right)$$

where  $f_{RF}$  is the target RF frequency,  $f_{IF}$  is the 200kHz or 400kHz setting programmed with the IF\_SEL bit, and  $f_{XTAL}$  is the crystal frequency (typically 16MHz).

When MIX\_HS\_LSBAR = 1, the equation for LO\_CTR\_FREQ[23:0] is:

LO\_CTR\_FREQ = INT

$$\left(65536 \frac{\left(f_{RF} + f_{IF}\right)}{f_{XTAL}}\right)$$

where  $f_{RF}$  is the target RF frequency,  $f_{IF}$  is the 200kHz or 400kHz setting programmed with the IF\_SEL bit, and  $f_{XTAL}$  is the crystal frequency (typically 16MHz).

The AFC loop generates a frequency offset from the programmed LO center frequency. The maximum frequency offset is limited by the receiver bandwidth and the AFC\_MO[2:0] field setting in the AFC\_CFG1 (0x07) register. This maximum offset can be expressed as:

$$f_{\text{OFFSET-MAX}} = \text{AFC\_MO} \times \frac{f_{\text{XTAL}}}{2^{(\text{IF\_SEL+CHF\_SEL+10})}}$$

where AFC\_MO, IF\_SEL, and CHF\_SEL are programmed register values. When AFC\_MO = 0, the PLL synthesizer frequency is fixed and AFC is disabled.

Without AFC, the frequency mismatch between an RF transmitter (Tx) and this receiver (Rx) can be estimated from the crystal accuracy ratings and the operating frequency band. For example, assume the crystal accuracy is ±50ppm for both the Tx and Rx systems and the operating frequency is 434MHz, then the Tx/Rx frequency mismatch can be as high as ±100ppm of the operating frequency, or ±43kHz.

In ASK mode, AFC is not necessary when the receiver bandwidth is sufficiently wide, but AFC is required when a narrow channel filter is selected to achieve a high receiver sensitivity. In FSK mode, AFC is required when the Tx/Rx frequency mismatch is higher than 25% of the frequency deviation.

When a wide channel-filter option is selected (for example CHF\_SEL = 0), AFC\_MO can be programmed based on an estimate of the Tx/Rx frequency mismatch. For example, when using the 315MHz band, a 16MHz crystal, the wide channel filter (CHF\_SEL = 0), and 200kHz IF (IF\_SEL = 1), the user can program for a maximum AFC offset of 31.3kHz (AFC MO = 4). This would be sufficient to allow for a ±100ppm Tx/Rx frequency mismatch in the 315MHz band.

The AFC\_LG[1:0] field in AFC\_CFG1 (0x07) register controls the AFC loop gain and settling time. This should typically be set to AFC LG = 3 in ASK mode and AFC LG = 2 in FSK mode.

#### Frequency Error Indicator (FEI)

In programmable mode, the user can read the FEI (0x11) register to determine the frequency error. This value is an 8-bit, signed integer, in two's complement format. The frequency offset generated by AFC can be calculated as:

$$f_{\text{OFFSET}} = \text{FEI} \times \frac{f_{\text{XTAL}}}{2^{(\text{IF\_SEL} + \text{CHF\_SEL} + 14)}}$$

where FEI, IF\_SEL, and CHF\_SEL are register values and f<sub>XTAL</sub> is the crystal frequency (typically 16MHz)

Because the maximum offset is limited by the AFC\_MO register field, the absolute value of FEI output is no more than 16 x AFC\_MO. For the purpose of frequency tracking, the user can iteratively adjust the LO\_CTR\_FREQ register value based on an FEI reading.

#### **AFC Freeze upon Preamble Detection**

The operation of AFC relies on an internal frequency detector, which senses errors in the RF frequency and averages the value over a number of received bits.

The changes in frequency inherent in FSK modulation introduces a bit-pattern-dependent, self-noise effect. Therefore, in FSK mode, it is recommended the AFC only be used when employing Manchester encoding and not with NRZ. In a typical data packet, the preamble is Manchester encoded but the payload may not be. With the MAX41470, a form of Manchester encoding must be used for proper preamble detection in the PollingRX mode.

Since the preamble is often an alternating 1 and 0 (or MARK and SPACE), setting PAD\_FREEZE\_AFC = 1 and AFC\_LG = 3 will result in a fast settling of the AFC in roughly 5 bits of RF data.

The AFC starts automatically when the receiver is active (entering the SlaveRX or PollingRX state). While using FSK modulation and in the SlaveRX state, the AFC can be 'frozen' just after a valid preamble pattern is detected. This feature is enabled by setting the PAD\_FREEZE\_AFC bit to 1 in the AFC\_CFG2 (0x08) register. See the <u>Preamble Detector</u> section for how to program the preamble bit pattern. The PAD\_FREEZE\_AFC bit is not available when using ASK modulation (ASK\_FSK\_SEL = 0).

#### **Recommended Data Rate and Post Demodulation Filter**

The post-demodulation filter (PDF) is a digital filter with programmable bandwidth. The PDF bandwidth selection is closely related to the data rate of the received signal. For example, the bandwidth needed for Manchester encoding is twice that needed for the same bit rate when sending NRZ data. (See <u>Table 3</u> for more information.)

For a given configuration of IF\_SEL, CHF\_SEL[2:0], SRC\_SM[2:0], and SRC\_LG[2:0] fields, the recommended decoded bit rate  $R_b$  for Manchester is defined as:

$$R_b = \frac{200\text{kHz}}{2^{(\text{IF\_SEL} + \text{CHF\_SEL} + \text{SRC\_LG})}} \times \frac{4}{8 + \text{SRC\_SM}}$$

where integer values of registers are used in the expression.

Given the difference in NRZ format vs. Manchester data, the recommended decoded bit rate  $R_b$  for NRZ would be adjusted to:

$$R_b = \frac{200\text{kHz}}{2^{(\text{IF\_SEL} + \text{CHF\_SEL} + \text{SRC\_LG})}} \times \frac{8}{8 + \text{SRC\_SM}}$$

where integer values of registers are used in the expression.

For additional guidance on setting the SRC\_SM and SRC\_LG values based on the desired configuration, see the <u>ASK Receiver Configurations</u> and <u>FSK Receiver Configurations</u> sections. The SRC\_SM[2:0] and SRC\_LG[2:0] fields are located in the PDF\_CFG (0x03) register.

The PDF bandwidth is provided in Table 12:

Table 12. Post Demodulation Filter Bandwidth

| PDF BANDWIDTH     | LD_BW REGISTER |

|-------------------|----------------|

| 0.6R <sub>b</sub> | 0*             |

| R <sub>b</sub>    | 1              |

<sup>\*</sup> Default setting

Regardless of the LD\_BW setting, the actual transmission data rate should not exceed 1.03 x  $R_b$  and should not be any lower than 0.6 x  $R_b$  in any configuration.

#### **ASK Decision Threshold**

The digital signal out of the post-demodulation filter is compared with a threshold to make a binary decision, which is subsequently represented as a 0 or 1 on the DATA output pin. When using FSK modulation, the decision threshold is fixed at zero, where a positive value signal represents the MARK frequency and a negative value represents the SPACE frequency. With ASK modulation, the comparison threshold will automatically be adjusted to accommodate changes in signal strength based on user settings.

The MAX41470 provides two ASK threshold adjustment methods set by the user with the ATH\_TYPE bit in the ATH\_CFG3 (0x06) register. The precharged lowpass filter (preLPF) method is strongly recommended when using Manchester encoding. In the case where Manchester encoding is not used (e.g., in NRZ format, which can result in long consecutive strings of 0s or 1s), the adaptive peak detector (aPD) method should be selected.

The ATH\_BW bit in ATH\_CFG3 (0x06) register is used only with the preLPF method to control the filter bandwidth. Program ATH\_BW to 0 when the Manchester data rate is close to the recommended rate  $R_b$  (suggested close values are  $1.03R_b$  < data rate <  $0.75R_b$ ; see the <u>Recommended Data Rate and Post Demodulation Filter</u> section for the definition of  $R_b$ ). Use ATH\_BW = 1 if the transmitter data rate is expected to go as low as  $0.6R_b$ .

The ATH\_DT[1:0] field in the ATH\_CFG2 (0x05) register is used only with the aPD method to adjust the peak detector's discharge time. If using Manchester encoding, set ATH\_DT to 0 whenever the data rate is close to the recommended R<sub>b</sub> value. Set ATH\_DT to 1 if the transmitter's Manchester data rate is expected to go as low as 0.6R<sub>b</sub>. In the case of NRZ encoding, set ATH\_DT to 3.

The ATH\_TC[4:0] field in the ATH\_CFG2 (0x05) register is also used only with the aPD method to control the peak detector time constant. Set ATH\_TC according to the SRC\_LG value using <u>Table 13</u>:

## Table 13. Programming of ATH\_TC

## **Table 13. Programming of ATH\_TC (continued)**

| ATH_TC | 0x14 | 0x12 | 0x10 | 0x0D | 0x09 | 0x07 | 0x05 | 0x04 |

|--------|------|------|------|------|------|------|------|------|

The ATH\_GC[4:0] field in the ATH\_CFG3 (0x06) register should be set based on the values in the IF\_SEL and CHF\_SEL fields according to Table 14:

### **Table 14. Programming of ATH GC**

| IF_SEL  | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| CHF_SEL | 0   | 1   | 2   | 3   | 4   | 0   | 1   | 2   | 3   | 4   |

| ATH_GC  | 0xB | 0x9 | 0x8 | 0x7 | 0x6 | 0xA | 0x7 | 0x6 | 0x5 | 0x4 |

#### Lower Bound of ASK Decision Threshold

In both methods of decision threshold generation (preLPF and aPD), the lower bound of the decision threshold is set by the ATH\_LB[7:0] field in the ATH\_CFG1 (0x04) register. ATH\_LB has a range of valid values from -128 to 0 and is represented in two's complement format (e.g.,  $0x9C = -100_{dec}$ ).

To achieve the highest ASK receiver sensitivity combined with fast receiver settling within 2 bits, the optimum ATH\_LB value can be found by calibrating the PDF through a collection of output noise statistics. For this calibration process, the LNA input pin must be terminated with  $50\Omega$  to ground while the user acquires random samples of the PDF by reading the PDF\_OUT(0x12) register when the receiver is in the SlaveRX state. Without the termination, the standard deviation of the PDF\_OUT values is much larger than actual. The calculated values below should be used if not terminated properly. The value of ATH\_LB should be set using the following formula:

ATH LB =

$$\mu$$

+ 3 $\sigma$

where  $\sigma$  is the standard deviation of PDF\_OUT and  $\mu$  = MEAN(PDF\_OUT - 16) when AGC\_EN\_BO[0] = 0, or  $\mu$  = MEAN(PDF\_OUT) when AGC\_EN\_BO[0] = 1.

Here, AGC\_EN\_BO[0] is the LSB of the 2-bit field in the AGC (0x01) register.

In the absence of a calibration value, ATH\_LB should be set by calculating a recommended value based on the following formula and tables:

where MU1 and MU2 are found using Table 15 and Table 16.

Find a value for MU1 based on the receiver filter settings.

### Table 15. Lookup Table for MU1

| IF_SEL  | 0   | 0   | 0    | 0    | 0    | 1   | 1    | 1    | 1    | 1    |

|---------|-----|-----|------|------|------|-----|------|------|------|------|

| CHF_SEL | 0   | 1   | 2    | 3    | 4    | 0   | 1    | 2    | 3    | 4    |

| MU1     | -81 | -93 | -102 | -110 | -118 | -90 | -102 | -110 | -118 | -125 |

Calculate the SRC Ratio using the following formula:

$$SRC_RATIO = SRC_LG = log_2(8 + SRC_SM) - 3$$

where SRC\_LG and SRC\_SM are fields in the PDF\_CFG (0x03) register.

#### Table 16. Lookup Table for MU2

| SRC_RATIO | 0  | 1  | 2  | 3  | 4 | 5 | 6 | 7 | 8 |

|-----------|----|----|----|----|---|---|---|---|---|

| MU2       | 29 | 21 | 15 | 11 | 8 | 6 | 4 | 3 | 2 |

When the SRC\_RATIO is not an integer (SRC\_SM is non-zero), a linear interpolation should be used to determine the best value for MU2 from the lookup table. The final MU2 value must be rounded to the nearest integer. For example, if SRC\_SM = 2 and SRC\_LG = 4, the SRC\_Ratio is calculated to be 4.3. Using a linear interpolation between SRC\_RATIO and MU2, the raw value for MU2 would be 7.4, rounded to a final value of MU2 = 7.

When preLPF is selected (ATH\_TYPE = 0), the ATH\_LB value may be lower than MU1 + MU2 - 6. As an example, set the ATH\_LB field to a value of -127 (0x81 in two's complement) regardless of the IF\_SEL and CHF\_SEL settings. In this case, each device can deliver its highest sensitivity without calibration, but the receiver settling slows down when the signal power is close to the receiver sensitivity. Because some applications require fast receiver settling, the use case of ATH\_LB = -127 is not always recommended, although it is convenient, as a trade-off between sensitivity and settling time.

#### Squelching ASK Receiver

In ASK mode, ATH\_LB may be programmed higher than the value determined from the threshold calibration measurements or the value calculated from MU1 and MU2. By setting the threshold higher than the calibration or calculated value, the DATA pin could be prevented from toggling just based on RF noise present in the threshold setting process when no transmission signal is present. This is commonly referred to as squelch. The trade-off for squelching the receiver is a commensurate reduction of receiver sensitivity.

### **Receiver Sensitivity**

Receiver sensitivity is measured and specified as the average LNA input power at a 2x10<sup>-3</sup> bit-error rate (0.2% BER) when testing with Manchester-encoded data which is equivalent to 1x10<sup>-3</sup> bit-error rate (0.1% BER) for NRZ data. For ASK modulation, average power is approximately 3dB lower than peak power.

There are many ways to optimize the sensitivity of the device, such as reducing the channel filter bandwidth, using lower data rates, ensuring that the carrier frequency is not a multiple of the crystal frequency, or even using a high-side LO injection configuration to avoid noise or spurs in the environment.

The configuration tables, <u>Table 17</u>, <u>Table 18</u>, <u>Table 19</u>, and <u>Table 20</u>, identify possible configurations where the highest or best sensitivity is identified in the top rows of each table. <u>Table 19</u> and <u>Table 20</u> provide guidance to those systems targeting a 0.8 modulation index.

#### **ASK Receiver Configurations**

Table 17. ASK Receiver for 400kHz IF

| DATA RATE (kbps) | IF_SEL | CHF_SEL | SRC_SM | SRC_LG |

|------------------|--------|---------|--------|--------|

| 0.25             | 0      | 4       | 4      | 4      |

| 0.25             | 0      | 3       | 4      | 5      |

| 0.5              | 0      | 4       | 4      | 3      |

| 0.5              | 0      | 3       | 4      | 4      |

| 0.5              | 0      | 2       | 4      | 5      |

| 1                | 0      | 3       | 4      | 3      |

| 1                | 0      | 4       | 4      | 2      |

| 1                | 0      | 2       | 4      | 4      |

| 1                | 0      | 1       | 4      | 5      |

| 2                | 0      | 3       | 4      | 2      |

| 2                | 0      | 2       | 4      | 3      |

| 2                | 0      | 1       | 4      | 4      |

| 2                | 0      | 0       | 4      | 5      |

| 5                | 0      | 2       | 2      | 2      |

| 5                | 0      | 1       | 2      | 3      |

| 5                | 0      | 0       | 2      | 4      |

| 10               | 0      | 1       | 2      | 2      |

| 10               | 0      | 0       | 2      | 3      |

## Table 17. ASK Receiver for 400kHz IF (continued)

| 25   | 0 | 0 | 0 | 2 |

|------|---|---|---|---|

| 62.5 | 0 | 0 | 5 | 0 |

## Table 18. ASK Receiver for 200kHz IF

| DATA RATE (kbps) | IF_SEL | CHF_SEL | SRC_SM | SRC_LG |

|------------------|--------|---------|--------|--------|

| 0.25             | 1      | 3       | 4      | 4      |

| 0.25             | 1      | 2       | 4      | 5      |

| 0.5              | 1      | 3       | 4      | 3      |

| 0.5              | 1      | 2       | 4      | 4      |

| 0.5              | 1      | 1       | 4      | 5      |

| 1                | 1      | 3       | 4      | 2      |

| 1                | 1      | 2       | 4      | 3      |

| 1                | 1      | 1       | 4      | 4      |

| 1                | 1      | 0       | 4      | 5      |

| 2                | 1      | 2       | 4      | 2      |

| 2                | 1      | 1       | 4      | 3      |

| 2                | 1      | 0       | 4      | 4      |