Evaluation Kit Available

Design Resources

Click here to ask an associate for production status of specific part numbers.

### **MAX32660**

### **General Description**

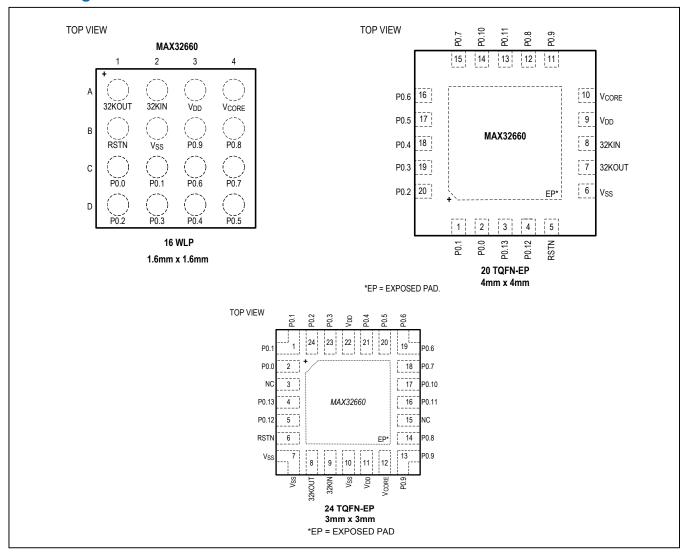

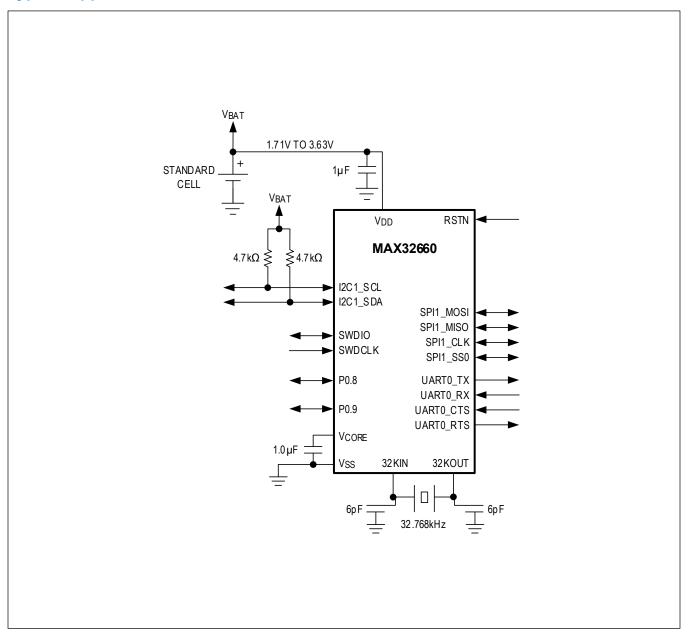

In the DARWIN family, the MAX32660 is an ultra-low-power, cost-effective, highly-integrated 32-bit microcontroller designed for battery-powered devices and wireless sensors. It combines a flexible and versatile power management unit with the powerful Arm® Cortex®-M4 processor with floating point unit (FPU) in the industry's smallest form factor: 1.6mm x 1.6mm, 16-bump WLP or 4mm x 4mm, 20-pin TQFN-EP, or 3mm x 3mm, 24-pin TQFN-EP.

The MAX32660 enables designs with complex sensor processing without compromising battery life. It also offers legacy designs an easy and cost optimal upgrade path from 8- or 16-bit microcontrollers.

The device supports SPI, UART, and I<sup>2</sup>C communication while also integrating up to 256KB of flash memory and 96KB of RAM to accommodate application and sensor code. An optional bootloader through I<sup>2</sup>C, UART, or SPI is available.

### **Applications**

- Sports Watches

- Fitness Monitors

- Wearable Medical Patches

- Portable Medical Devices

- Industrial Sensors

- loT

- Optical Modules: QSFP-DD, QSFP, 400G

### **Benefits and Features**

- High-Efficiency Microcontroller for Wearable Devices

- · Internal Oscillator Operates up to 96MHz

- 256KB Flash Memory

- 96KB SRAM, Optionally Preserved in Lowest Power Backup Mode

- · 16KB Instruction Cache

- Memory Protection Unit (MPU)

- Low 1.1V V<sub>CORE</sub> Supply Voltage

- · 3.6V GPIO Operating Range

- · Internal LDO Provides Operation from Single Supply

- Wide Operating Temperature: -40°C to +105°C

- Power Management Maximizes Uptime for Battery Applications

- 85µA/MHz Active Executing from Flash

- 2μA Full Memory Retention Power in Backup Mode at V<sub>DD</sub> = 1.8V

- 450nA Ultra-Low Power RTC at V<sub>DD</sub> = 1.8V

- · Internal 80kHz Ring Oscillator

- Optimal Peripheral Mix Provides Platform Scalability

- Up to 14 General-Purpose I/O Pins

- Up to Two SPI

- I2S

- · Up to Two UARTs

- Up to Two I<sup>2</sup>C, 3.4Mbps High Speed

- Four-Channel Standard DMA Controller

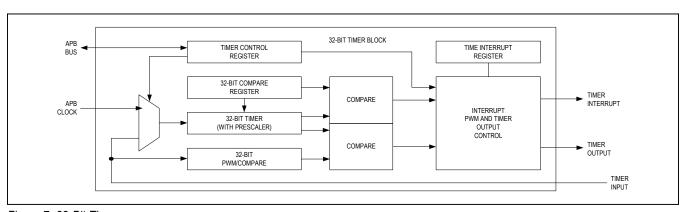

- · Three 32-Bit Timers

- · Watchdog Timer

- CMOS-Level 32.768kHz RTC Output

Ordering Information appears at end of data sheet.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

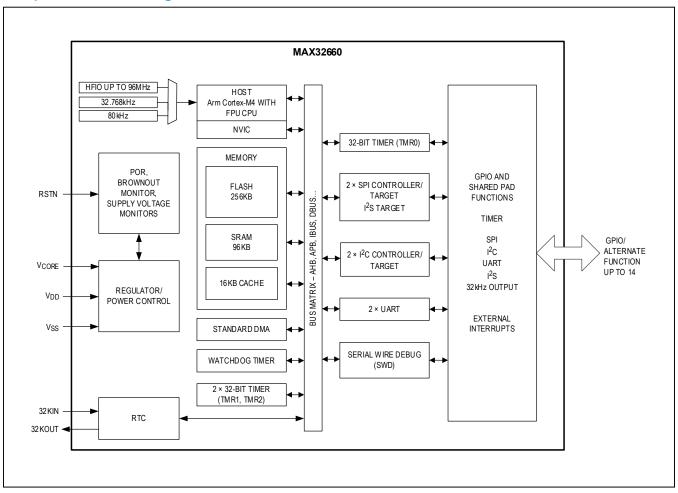

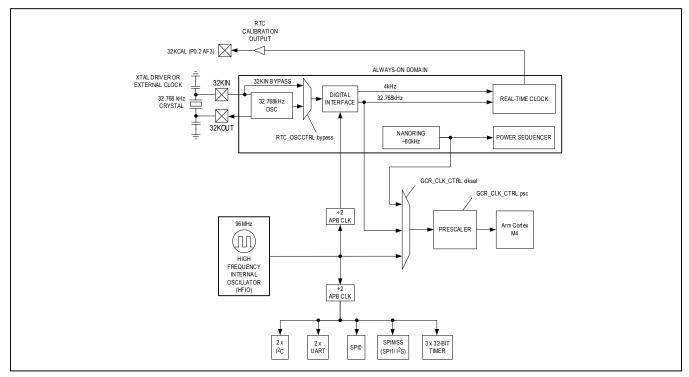

# **Simplified Block Diagram**

# Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

### **Absolute Maximum Ratings**

| •                                                         |                            |

|-----------------------------------------------------------|----------------------------|

| (All voltages with respect to V <sub>SS</sub> , unless of | therwise noted.)           |

| V <sub>CORE</sub>                                         | 0.3V to +1.21V             |

| V <sub>DD</sub>                                           | 0.3V to +3.63V             |

| 32KIN, 32KOUT                                             | $-0.3V$ to $V_{DD} + 0.3V$ |

| RSTN, All GPIO except P0.[4-7, 9]                         | $0.3V$ to $V_{DD} + 0.3V$  |

| GPIO P0.[4-7, 9]                                          | $0.3V$ to $V_{DD} + 0.3V$  |

| Total Current into All GPIO Combined (sink                | c)100mA                    |

| V <sub>SS</sub>                                           | 100mA                      |

| Output Current (sink) by Any GPIO Pin                     | 25mA                       |

| Output Current (source) by Any GPIO Pin.                  | 25mA                       |

|                                                           |                            |

| Continuous Package Power Dissipation<br>20 TQFN-EP (multilayer board) TA = +70°C |                 |

|----------------------------------------------------------------------------------|-----------------|

| (derate 30.3mW/°C above +70°C)                                                   | 2424.2mW        |

| Continuous Package Power Dissipation                                             |                 |

| 24 TQFN-EP (multilayer board) T <sub>A</sub> = +70°C                             |                 |

| (derate 16.3mW/°C above +70°C)                                                   | 1305mW          |

| Operating Temperature Range                                                      | -40°C to +105°C |

| Storage Temperature Range                                                        | -65°C to +150°C |

| Soldering Temperature (reflow)                                                   | +260°C          |

|                                                                                  |                 |

**Note:** Long-term storage at +150°C is not recommended as this will reduce the lifetime of the flash storage. Please keep long-term storage of the part below +125°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **16 WLP**

| Package Code                           | W161K1+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100241</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 66.34 °C/W                     |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

#### 20 TQFN-EP

| Package Code                            | T2044+5C |  |  |  |

|-----------------------------------------|----------|--|--|--|

| Outline Number                          | 21-0139  |  |  |  |

| Land Pattern Number                     | 90-0429  |  |  |  |

| Thermal Resistance, Single-Layer Board: |          |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 48°C/W   |  |  |  |

| Junction to Case $(\theta_{JC})$        | 2°C/W    |  |  |  |

| Thermal Resistance, Four-Layer Board:   |          |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 33°C/W   |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 2°C/W    |  |  |  |

#### 24 TQFN-EP

| Package Code                           | T2433+2C  |

|----------------------------------------|-----------|

| Outline Number                         | 21-100264 |

| Land Pattern Number                    | 90-100089 |

| Thermal Resistance, Four-Layer Board:  |           |

| Junction to Ambient (θ <sub>JA</sub> ) | 61.3°C/W  |

| Junction to Case (θ <sub>JC</sub> )    | 2.2°C/W   |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

# Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                    | SYMBOL                    | С                                                                                                                                    | ONDITIONS                                                              | MIN                                                                              | TYP      | MAX   | UNITS  |  |

|----------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------|-------|--------|--|

| POWER SUPPLIES/BOTH                          | SINGLE SUPP               | LY OPERATION A                                                                                                                       | ND DUAL SUPPLY OPERAT                                                  | TION                                                                             |          |       |        |  |

| Supply Voltage                               | $V_{DD}$                  |                                                                                                                                      |                                                                        | 1.71                                                                             | 1.8      | 3.63  | V      |  |

|                                              |                           |                                                                                                                                      | OVR = [00]                                                             | 0.855                                                                            | 0.9      | 0.945 |        |  |

| Owner by Malkana Com                         | .,                        | Dual-supply operation                                                                                                                | OVR = [01]                                                             | 0.95                                                                             | 1.0      | 1.05  | V      |  |

| Supply Voltage, Core                         | V <sub>CORE</sub>         | operation                                                                                                                            | Default OVR = [10]                                                     | 1.045                                                                            | 1.1      | 1.155 | 1      |  |

|                                              |                           | Single-supply ope                                                                                                                    | eration                                                                |                                                                                  | Not used |       |        |  |

|                                              |                           | Monitors V <sub>DD</sub>                                                                                                             |                                                                        | 1.63                                                                             |          | 1.71  |        |  |

| Power-Fail Reset Voltage                     | V <sub>RST</sub>          | Monitors V <sub>CORE</sub>                                                                                                           | during dual-supply opera-                                              | 0.80                                                                             |          | 0.845 | V      |  |

|                                              |                           | Monitors V <sub>DD</sub>                                                                                                             |                                                                        |                                                                                  | 1.4      |       |        |  |

| Power-On Reset Voltage                       | V <sub>POR</sub>          | Monitors V <sub>CORE</sub> tion                                                                                                      | during dual supply opera-                                              |                                                                                  | 0.65     |       | V      |  |

| Sleep Mode Resume Time                       | t <sub>SLP_ON</sub>       |                                                                                                                                      |                                                                        |                                                                                  | 0.57     |       | μs     |  |

| Deep Sleep Mode Resume<br>Time               | t <sub>DSL_ON</sub>       |                                                                                                                                      |                                                                        |                                                                                  | 150      |       | μs     |  |

| Backup Mode Resume<br>Time                   | t <sub>BKU_ON</sub>       |                                                                                                                                      |                                                                        |                                                                                  | 150      |       | μs     |  |

| POWER SUPPLIES/SINGLE                        | SUPPLY OP                 | ERATION (V <sub>DD</sub> ON                                                                                                          | NLY)                                                                   |                                                                                  |          |       | •      |  |

|                                              | I <sub>DD_DACT</sub>      |                                                                                                                                      | HFIO enabled, total current into                                       | OVR = [10], Internal regulator set to 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> = 96MHz |          | 85    |        |  |

| V <sub>DD</sub> Dynamic Current, Active Mode |                           | V <sub>DD</sub> pin, CPU<br>in Active mode,<br>inputs tied to<br>V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/<br>sink 0mA | OVR = [01], Internal regulator set to 1.0V,<br>fSYS_CLK(MAX) = 48MHz   |                                                                                  | 74       |       | μΑ/MHz |  |

|                                              |                           |                                                                                                                                      | OVR = [00], Internal regulator set to 0.9V,<br>fSYS_CLK(MAX) = 24MHz   |                                                                                  | 50       |       |        |  |

|                                              |                           | HFIO enabled,<br>total current into<br>V <sub>DD</sub> pin, CPU                                                                      | OVR = [10], Internal regulator set to 1.1V, fSYS_CLK(MAX) = 96MHz      |                                                                                  | 488      |       |        |  |

| V <sub>DD</sub> Fixed Current, Active Mode   | I <sub>DD_FACT</sub>      | in Active mode                                                                                                                       | OVR = [01], Internal regulator set to 1.0V, fSYS_CLK(MAX) = 48MHz      |                                                                                  | 394      |       | μΑ     |  |

|                                              | to V <sub>SS</sub> output |                                                                                                                                      | to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/<br>sink 0mA | OVR = [00], Internal regulator set to 0.9V, fSYS_CLK(MAX) = 24MHz                |          | 324   |        |  |

# Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

# **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                         | SYMBOL                 | С                                                                        | ONDITIONS                                                                                                                                                                                                                               | MIN | TYP  | MAX | UNITS  |

|---------------------------------------------------|------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

|                                                   |                        | HFIO enabled, total current into                                         | OVR = [10], Internal regulator set to 1.1V, fsys_CLK(MAX) = 96MHz                                                                                                                                                                       |     | 30.3 |     |        |

| V <sub>DD</sub> Dynamic Current,<br>Sleep Mode    | IDD_DSLP               | V <sub>DD</sub> pin, CPU<br>in Sleep mode,<br>standard DMA               | OVR = [01], Internal regulator set to 1.0V, fsys_CLK(MAX) = 48MHz                                                                                                                                                                       |     | 27   |     | μΑ/MHz |

|                                                   |                        | with two chan-<br>nels active                                            | OVR = [00], Internal regulator set to 0.9V, fsys_CLK(MAX) = 24MHz                                                                                                                                                                       |     | 24   |     |        |

|                                                   |                        | HFIO enabled,<br>total current into<br>V <sub>DD</sub> pin, CPU          | OVR = [10], Internal regulator set to 1.1V,<br>fsys_CLK(MAX) = 96MHz                                                                                                                                                                    |     | 485  |     |        |

| V <sub>DD</sub> Fixed Current, Sleep<br>Mode      | I <sub>DD_FSLP</sub>   | in Sleep mode,<br>inputs tied to<br>V <sub>SS</sub> or V <sub>DD</sub> , | OVR = [01], Internal regulator set to 1.0V, fsys_CLK(MAX) = 48MHz                                                                                                                                                                       |     | 391  |     | μA     |

|                                                   |                        | outputs source/<br>sink 0mA                                              | OVR = [00], Internal regulator set to 0.9V,<br>fsys_CLK(MAX) = 24MHz                                                                                                                                                                    |     | 321  |     |        |

| V <sub>DD</sub> Fixed Current, Deep<br>Sleep Mode | I <sub>DD_FDSL</sub>   | Standby state with full data retention and 96kB SRAM retained            |                                                                                                                                                                                                                                         |     | 4.2  |     | μA     |

|                                                   |                        | 0KB SRAM retair<br>V <sub>DD</sub> =1.8V                                 | ned with RTC enabled;                                                                                                                                                                                                                   |     | 0.53 |     |        |

|                                                   |                        | 16KB SRAM reta<br>V <sub>DD</sub> =1.8V                                  | ined with RTC enabled;                                                                                                                                                                                                                  |     | 0.99 |     |        |

| V <sub>DD</sub> Fixed Current, Backup<br>Mode     | I <sub>DD_FBKU</sub>   | 32KB SRAM reta<br>V <sub>DD</sub> =1.8V                                  | ined with RTC enabled;                                                                                                                                                                                                                  |     | 1.20 |     | μA     |

|                                                   |                        | 64KB SRAM reta<br>V <sub>DD</sub> =1.8V                                  | ined with RTC enabled;                                                                                                                                                                                                                  |     | 1.64 |     |        |

|                                                   |                        | 96KB SRAM retained with RTC enabled;<br>V <sub>DD</sub> =1.8V            |                                                                                                                                                                                                                                         |     | 1.94 |     |        |

| POWER SUPPLIES / DUAL                             | SUPPLY OPE             | RATION (V <sub>DD</sub> AN                                               | D V <sub>CORE</sub> )                                                                                                                                                                                                                   |     |      |     | •      |

| V <sub>CORE</sub> Dynamic Current,<br>Active Mode | ICORE_DACT             | Total current into abled, f <sub>SYS_CLK</sub> ([10], executing co       | Total current into V <sub>CORE</sub> pin, HFIO enabled, f <sub>SYS_CLK(MAX)</sub> = 96MHz, OVR = [10], executing code from cache memory, CPU in Active mode, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> ,outputs source/sink 0mA |     |      |     | μΑ/MHz |

| V <sub>CORE</sub> Fixed Current, Active Mode      | I <sub>CORE_FACT</sub> | into V <sub>CORE</sub> pin, (                                            | VR = [10], total current<br>CPU in Active mode 0MHz<br>tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs                                                                                                                             |     | 403  |     | μА     |

# Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                           | SYMBOL                 | CONDITIONS                                                                                                                                                                                                  | MIN | TYP   | MAX | UNITS  |

|-----------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|--------|

| V <sub>DD</sub> Dynamic Current, Active Mode        | I <sub>DD_DACT</sub>   | HFIO enabled, OVR = [10], $f_{SYS\_CLK(MAX)}$ = 96MHz, total current into $V_{DD}$ pin, executing code from cache memory, CPU in Active mode, inputs tied to $V_{SS}$ or $V_{DD}$ , outputs source/sink 0mA |     | 0.40  |     | μΑ/MHz |

| V <sub>DD</sub> Fixed Current, Active Mode          | I <sub>DD_FACT</sub>   | HFIO enabled, OVR = [10], total current into $V_{DD}$ pin, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}$ or $V_{DD}$ , outputs source/sink 0mA                                                 |     | 84.8  |     | μА     |

| V <sub>CORE</sub> Dynamic Current,<br>Sleep Mode    | I <sub>CORE_DSLP</sub> | HFIO enabled, OVR = [10], total current into $V_{CORE}$ pin, CPU in Sleep mode, standard DMA with two channels active                                                                                       |     | 27.7  |     | μΑ/MHz |

| V <sub>CORE</sub> Fixed Current,<br>Sleep Mode      | I <sub>CORE_FSLP</sub> | HFIO enabled, OVR [10], total current into V <sub>CORE</sub> pin, CPU in Sleep mode, standard DMA with two channels active                                                                                  |     | 270.3 |     | μA     |

| V <sub>DD</sub> Dynamic Current,<br>Sleep Mode      | I <sub>DD_DSLP</sub>   | HFIO enabled, OVR = [10], total current into $V_{DD}$ pin, CPU in Sleep mode, standard DMA with two channels active                                                                                         |     | 0.20  |     | μΑ/MHz |

| V <sub>DD</sub> Fixed Current, Sleep<br>Mode        | I <sub>DD_FSLP</sub>   | HFIO enabled, OVR = [10], total current into $V_{DD}$ pin, CPU in Sleep mode, standard DMA with two channels active                                                                                         |     | 65    |     | μA     |

| V <sub>CORE</sub> Fixed Current,<br>Deep-Sleep Mode | CORE_FDSL              | V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> =1.1V                                                                                                                                                             |     | 5.7   |     | μА     |

| V <sub>DD</sub> Fixed Current, Deep<br>Sleep Mode   | I <sub>DD_FDSL</sub>   | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> =1.1V                                                                                                                                                             |     | 4.2   |     | μА     |

| V <sub>CORE</sub> Fixed Current,<br>Backup Mode     | I <sub>CORE_FBKU</sub> | V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 1.1V, 96KB SRAM retained                                                                                                                                        |     | 5     |     | μA     |

|                                                     |                        | 0KB SRAM retained with RTC enabled; V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0V or unbiased                                                                                                              |     | 0.53  |     |        |

|                                                     |                        | 16KB SRAM retained with RTC enabled;<br>V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0V or unbiased                                                                                                          |     | 0.99  |     |        |

| V <sub>DD</sub> Fixed Current, Backup<br>Mode       | I <sub>DD_FBKU</sub>   | 32KB SRAM retained with RTC enabled;<br>V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0V or unbiased                                                                                                          |     | 1.20  |     | μΑ     |

|                                                     |                        | 64KB SRAM retained with RTC enabled;<br>V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0V or unbiased                                                                                                          |     | 1.64  |     |        |

|                                                     |                        | 96KB SRAM retained with RTC enabled;<br>V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0V or unbiased                                                                                                          |     | 1.94  |     |        |

# Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                               | MIN                   | TYP  | MAX          | UNITS |  |

|-----------------------------------------------------|-----------------------|--------------------------------------------------------------------------|-----------------------|------|--------------|-------|--|

| GENERAL-PURPOSE I/O                                 |                       |                                                                          | •                     |      |              |       |  |

| Input Low Voltage for All GPIO, RSTN                | V <sub>IL_GPIO</sub>  | Pin configured as GPIO                                                   |                       |      | 0.3 ×<br>VDD | V     |  |

| Input High Voltage for All GPIO, RSTN               | V <sub>IH_GPIO</sub>  | Pin configured as GPIO                                                   | 0.7 × V <sub>DD</sub> |      |              | V     |  |

|                                                     |                       | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 1mA, DS[1:0] = 00<br>(Note 1) |                       | 0.2  | 0.4          |       |  |

| Output Low Voltage for All                          | V                     | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 2mA, DS[1:0] = 10<br>(Note 1) |                       | 0.2  | 0.4          | V     |  |

| GPIO Except P0.2, P0.3, P0.8, and P0.9              | V <sub>OL_GPIO</sub>  | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 4mA, DS[1:0] = 01<br>(Note 1) |                       | 0.2  | 0.4          |       |  |

|                                                     |                       | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 6mA, DS[1:0] = 11<br>(Note 1) |                       | 0.2  | 0.4          |       |  |

| Output Low Voltage for                              |                       | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 2mA, DS = 0 (Note 1)          |                       | 0.2  | 0.4          | V     |  |

| GPIO P0.2, P0.3, P0.8,<br>P0.9                      | V <sub>OL_I2C</sub>   | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 10mA, DS = 1 (Note 1)         |                       | 0.2  | 0.4          |       |  |

|                                                     | Voн_gpio              | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 1mA, DS[1:0] = 00<br>(Note 1) | V <sub>DD</sub> - 0.4 |      |              | V     |  |

| Output High Voltage for All GPIO Except P0.2, P0.3, |                       | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 2mA, DS[1:0] = 10<br>(Note 1) | V <sub>DD</sub> - 0.4 |      |              |       |  |

| P0.8, and P0.9                                      |                       | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 4mA, DS[1:0] = 01<br>(Note 1) | V <sub>DD</sub> - 0.4 |      |              |       |  |

|                                                     |                       | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 6mA, DS[1:0] = 11<br>(Note 1) | V <sub>DD</sub> - 0.4 |      |              |       |  |

| Output High Voltage for                             |                       | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 2mA, DS = 0 (Note 1)          | V <sub>DD</sub> - 0.4 |      |              |       |  |

| GPIO P0.2, P0.3, P0.8,<br>P0.9                      | V <sub>OH_I2C</sub>   | V <sub>DD</sub> = 1.71V, I <sub>OH</sub> = 10mA, DS = 1 (Note 1)         | V <sub>DD</sub> - 0.4 |      |              | V     |  |

| Combined I <sub>OL</sub> , All GPIO                 | I <sub>OL_TOTAL</sub> |                                                                          |                       |      | 32           | mA    |  |

| Combined I <sub>OH</sub> , All GPIO                 | I <sub>OH_TOTAL</sub> |                                                                          | -32                   |      |              | mA    |  |

| Input Hysteresis (Schmitt)                          | $V_{IHYS}$            |                                                                          |                       | 300  |              | mV    |  |

| Input/Output Pin Capacitance for All Pins           | C <sub>IO</sub>       |                                                                          |                       | 4    |              | pF    |  |

| Input Leakage Current Low                           | Ι <sub>Ι</sub> L      | V <sub>IN</sub> = 0V, internal pullup disabled                           | -500                  |      | +500         | nA    |  |

| Input Leakage Current<br>High                       | I <sub>IH</sub>       | V <sub>IN</sub> = 3.6V, internal pulldown disabled                       | -500                  |      | +500         | nA    |  |

| Input Pullup Resistor to                            | Rousses               | Pullup to V <sub>DD</sub> = 1.62V                                        |                       | 22   |              | kΩ    |  |

| RSTN                                                | R <sub>PU_VDD</sub>   | Pullup to V <sub>DD</sub> = 3.63V                                        |                       | 10.5 | 1/32         | 17.22 |  |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                 | SYMBOL               | CONDITIONS                                                      | MIN  | TYP                         | MAX  | UNITS   |

|-------------------------------------------|----------------------|-----------------------------------------------------------------|------|-----------------------------|------|---------|

| Input Pullup Resistor for                 | Devi                 | Pin configured as GPIO, pullup to V <sub>DD</sub> = 1.62V       |      | 22                          |      | kΩ      |

| All GPIO                                  | R <sub>PU</sub>      | Pin configured as GPIO, pullup to V <sub>DD</sub> = 3.63V       |      | 10.5                        |      | K(2)    |

| Input Pulldown Resistor for               | В                    | Pin configured as GPIO, pulldown to $V_{SS}$ , $V_{DD}$ = 1.62V |      | 20                          |      | - kΩ    |

| All GPIO                                  | R <sub>PD</sub>      | Pin configured as GPIO, pulldown to $V_{SS}$ , $V_{DD}$ = 3.63V |      | 8.8                         |      | K(2)    |

| CLOCKS                                    |                      |                                                                 |      |                             |      |         |

| System Clock Frequency                    | fsys_clk             |                                                                 | 24   |                             | 96   | MHz     |

| System Clock Period                       | tsys_clk             |                                                                 |      | 1/f <sub>SYS</sub> _<br>CLK |      | μs      |

| High-Frequency Internal Oscillator (HFIO) | f <sub>HFIO</sub>    | Default OVR = [10]                                              | 93.5 | 96                          | 98.5 | MHz     |

| Nanoring Oscillator Frequency             | f <sub>NANO</sub>    |                                                                 |      | 80                          |      | kHz     |

| RTC Input Frequency                       | f <sub>32KIN</sub>   | 32.768kHz watch crystal, $C_L$ = 6pF, ESR < 90kΩ, $C_0$ < 2pF   |      | 32.768                      |      | kHz     |

| RTC Operating Current                     | I <sub>RTC</sub>     | All power modes, RTC enabled                                    |      | 0.45                        |      | μA      |

| RTC Power-Up Time                         | t <sub>RTC_ON</sub>  |                                                                 |      | 250                         |      | ms      |

| FLASH MEMORY                              |                      |                                                                 |      |                             |      |         |

| Flash Erase Time                          | t <sub>M_ERASE</sub> | Mass erase                                                      |      | 30                          |      | me      |

| Flasii Elase IIIIle                       | tp_ERASE             | Page erase                                                      |      | 30                          |      | ms      |

| Flash Programming Time<br>Per Word        | t <sub>PROG</sub>    | 32-bit programming mode, f <sub>FLC_CLK</sub> = 1MHz            |      | 60                          |      | μs      |

| Flash Endurance                           |                      |                                                                 | 10   |                             |      | kcycles |

| Data Retention                            | t <sub>RET</sub>     | T <sub>A</sub> = +85°C                                          | 10   |                             |      | years   |

Note 1: When using a GPIO bias voltage of 2.97V, the drive current capability of the GPIO is 2x that of its drive strength when using a GPIO bias voltage of 1.62V.

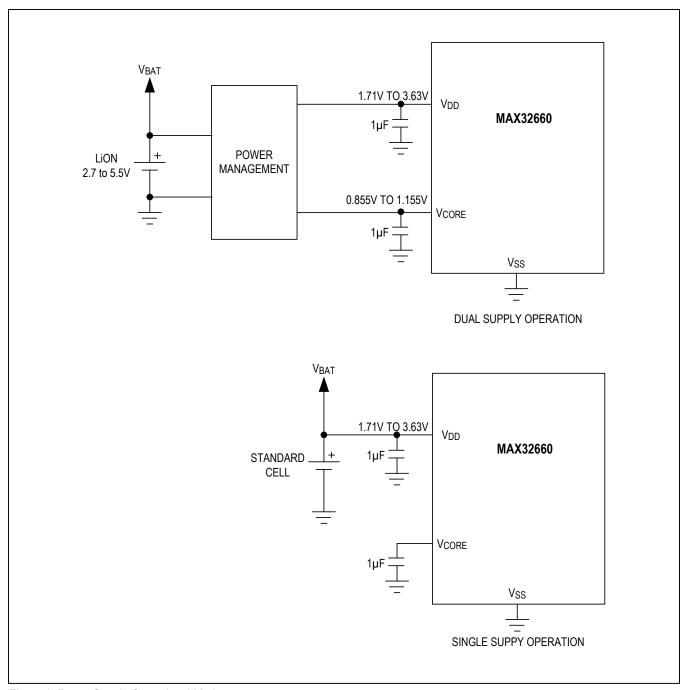

Figure 1. Power Supply Operational Modes

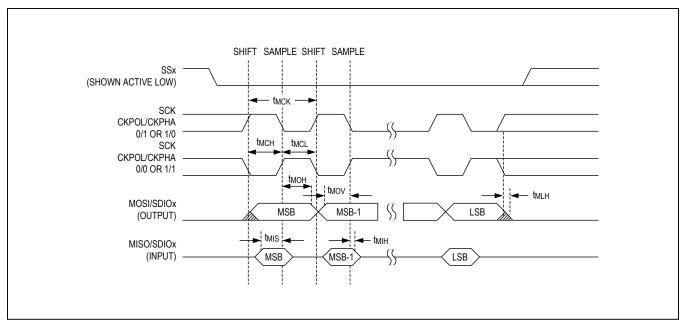

### **Electrical Characteristics—SPI**

(Tlming specifications are guaranteed by design and not production tested.)

| PARAMETER                                             | SYMBOL                              | CONDITIONS                                                                       | MIN                 | TYP                 | MAX | UNITS |

|-------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|---------------------|---------------------|-----|-------|

| CONTROLLER MODE                                       |                                     |                                                                                  | ·                   |                     |     |       |

| SPI Controller Operating Frequency                    | f <sub>MCK</sub>                    | f <sub>SYS_CLK</sub> = 96MHz,<br>f <sub>MCK(MAX)</sub> = f <sub>SYS_CLK</sub> /2 |                     |                     | 48  | MHz   |

| SPI Controller SCK Period                             | tMCK                                |                                                                                  |                     | 1/f <sub>MCK</sub>  |     | ns    |

| SCK Output Pulse-Width High/Low                       | t <sub>MCH</sub> , t <sub>MCL</sub> |                                                                                  | t <sub>MCK</sub> /2 |                     |     | ns    |

| MOSI Output Hold Time<br>After SCK Sample Edge        | tмон                                |                                                                                  | t <sub>MCK</sub> /2 |                     |     | ns    |

| MOSI Output Valid to<br>Sample Edge                   | t <sub>MOV</sub>                    |                                                                                  | t <sub>MCK</sub> /2 |                     |     | ns    |

| MISO Input Valid to SCK<br>Sample Edge Setup          | t <sub>MIS</sub>                    |                                                                                  |                     | 5                   |     | ns    |

| MISO Input to SCK<br>Sample Edge Hold                 | t <sub>MIH</sub>                    |                                                                                  |                     | t <sub>MCK</sub> /2 |     | ns    |

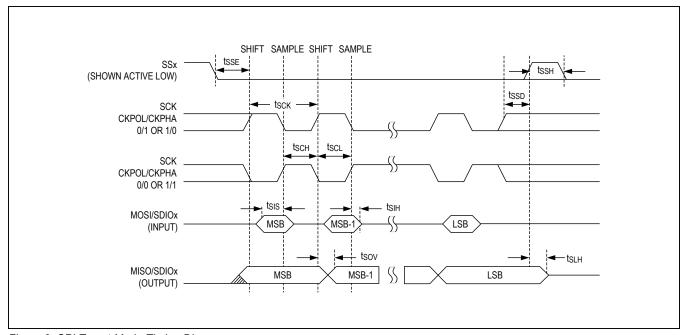

| TARGET MODE                                           |                                     |                                                                                  |                     |                     |     | •     |

| SPI Target Operating Frequency                        | f <sub>SCK</sub>                    |                                                                                  |                     |                     | 48  | MHz   |

| SPI Target SCK Period                                 | tsck                                |                                                                                  |                     | 1/f <sub>SCK</sub>  |     | ns    |

| SCK Input Pulse-Width<br>High/Low                     | t <sub>SCH</sub> , t <sub>SCL</sub> |                                                                                  |                     | t <sub>SCK</sub> /2 |     |       |

| SSx Active to First Shift<br>Edge                     | t <sub>SSE</sub>                    |                                                                                  |                     | 10                  |     | ns    |

| MOSI Input to SCK Sample<br>Edge Rise/Fall Setup      | tsis                                |                                                                                  |                     | 5                   |     | ns    |

| MOSI Input from SCK<br>Sample Edge Transition<br>Hold | tsін                                |                                                                                  |                     | 1                   |     | ns    |

| MISO Output Valid After SCLK Shift Edge Transition    | tsov                                |                                                                                  |                     | 5                   |     | ns    |

| SCK Inactive to SSx Inactive                          | t <sub>SSD</sub>                    |                                                                                  |                     | 10                  |     | ns    |

| SSx Inactive Time                                     | t <sub>SSH</sub>                    |                                                                                  |                     | 1/f <sub>SCK</sub>  |     | μs    |

| MISO Hold Time After SSx<br>Deassertion               | t <sub>SLH</sub>                    |                                                                                  |                     | 10                  |     | ns    |

Figure 2. SPI Controller Mode Timing Diagram

Figure 3. SPI Target Mode Timing Diagram

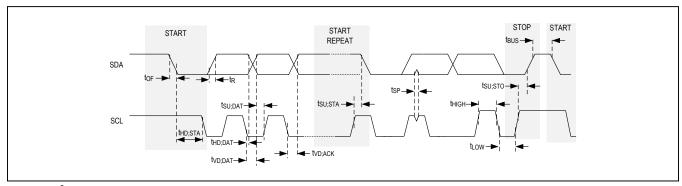

### Electrical Characteristics—I<sup>2</sup>C

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                               | MIN  | TYP | MAX | UNITS |

|--------------------------------------------------|---------------------|--------------------------------------------------------------------------|------|-----|-----|-------|

| STANDARD-MODE                                    |                     |                                                                          | '    |     |     |       |

| Output Fall Time                                 | t <sub>OF</sub>     | Standard mode, from V <sub>OL_I2C(MIN)</sub> to V <sub>OL_I2C(MAX)</sub> |      | 150 |     | ns    |

| SCL Clock Frequency                              | f <sub>SCL</sub>    |                                                                          | 0    |     | 100 | kHz   |

| Low Period SCL Clock                             | t <sub>LOW</sub>    |                                                                          | 4.7  |     |     | μs    |

| High Time SCL Clock                              | t <sub>HIGH</sub>   |                                                                          | 4.0  |     |     | μs    |

| Setup Time for Repeated Start Condition          | tsu;sta             |                                                                          | 4.7  |     |     | μs    |

| Hold Time for Repeated Start Condition           | t <sub>HD;STA</sub> |                                                                          | 4.0  |     |     | μs    |

| Data Setup Time                                  | tsu;dat             |                                                                          |      | 300 |     | ns    |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                                                                          |      | 10  |     | ns    |

| Rise Time for SDA and SCL                        | t <sub>R</sub>      |                                                                          |      | 800 |     | ns    |

| Fall Time for SDA and SCL                        | t <sub>F</sub>      |                                                                          |      | 200 |     | ns    |

| Setup Time for a Stop<br>Condition               | tsu;sто             |                                                                          | 4.0  |     |     | μs    |

| Bus Free Time Between a Stop and Start Condition | t <sub>BUS</sub>    |                                                                          | 4.7  |     |     | μs    |

| Data Valid Time                                  | t <sub>VD;DAT</sub> |                                                                          | 3.45 |     |     | μs    |

| Data Valid Acknowledge<br>Time                   | t <sub>VD;ACK</sub> |                                                                          | 3.45 |     |     | μs    |

| FAST-MODE                                        |                     |                                                                          |      |     |     |       |

| Output Fall Time                                 | t <sub>OF</sub>     | From V <sub>OL_I2C(MIN)</sub> to V <sub>OL_I2C(MAX)</sub>                |      | 150 |     | ns    |

| Pulse Width Suppressed by Input Filter           | t <sub>SP</sub>     |                                                                          |      | 75  |     | ns    |

| SCL Clock Frequency                              | f <sub>SCL</sub>    |                                                                          | 0    |     | 400 | kHz   |

| Low Period SCL Clock                             | t <sub>LOW</sub>    |                                                                          | 1.3  |     |     | μs    |

| High Time SCL Clock                              | tHIGH               |                                                                          | 0.6  |     |     | μs    |

| Setup Time for Repeated Start Condition          | t <sub>SU;STA</sub> |                                                                          | 0.6  |     |     | μs    |

| Hold Time for Repeated Start Condition           | t <sub>HD;STA</sub> |                                                                          | 0.6  |     |     | μs    |

| Data Setup Time                                  | t <sub>SU;DAT</sub> |                                                                          |      | 125 |     | ns    |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                                                                          |      | 10  |     | ns    |

| Rise Time for SDA and SCL                        | t <sub>R</sub>      |                                                                          |      | 30  |     | ns    |

| Fall Time for SDA and SCL                        | t <sub>F</sub>      |                                                                          |      | 30  |     | ns    |

| Setup Time for a Stop<br>Condition               | tsu;sto             |                                                                          | 0.6  |     |     | μs    |

# Electrical Characteristics—I<sup>2</sup>C (continued)

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                           | SYMBOL              | CONDITIONS                                                | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------|---------------------|-----------------------------------------------------------|------|-----|------|-------|

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                           | 1.3  |     |      | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                           | 0.9  |     |      | μs    |

| Data Valid Acknowledge<br>Time                      | t <sub>VD;ACK</sub> |                                                           | 0.9  |     |      | μs    |

| FAST-MODE PLUS                                      |                     |                                                           |      |     |      |       |

| Output Fall Time                                    | t <sub>OF</sub>     | From V <sub>OL_I2C(MIN)</sub> to V <sub>OL_I2C(MAX)</sub> |      | 80  |      | ns    |

| Pulse Width Suppressed by Input Filter              | t <sub>SP</sub>     |                                                           |      | 75  |      | ns    |

| SCL Clock Frequency                                 | f <sub>SCL</sub>    |                                                           | 0    |     | 1000 | kHz   |

| Low Period SCL Clock                                | t <sub>LOW</sub>    |                                                           | 0.5  |     |      | μs    |

| High Time SCL Clock                                 | tHIGH               |                                                           | 0.26 |     |      | μs    |

| Setup Time for Repeated Start Condition             | t <sub>SU;STA</sub> |                                                           | 0.26 |     |      | μs    |

| Hold Time for Repeated Start Condition              | t <sub>HD;STA</sub> |                                                           | 0.26 |     |      | μs    |

| Data Setup Time                                     | t <sub>SU;DAT</sub> |                                                           |      | 50  |      | ns    |

| Data Hold Time                                      | t <sub>HD;DAT</sub> |                                                           |      | 10  |      | ns    |

| Rise Time for SDA and SCL                           | t <sub>R</sub>      |                                                           |      | 50  |      | ns    |

| Fall Time for SDA and SCL                           | t <sub>F</sub>      |                                                           |      | 30  |      | ns    |

| Setup Time for a Stop<br>Condition                  | tsu;sто             |                                                           | 0.26 |     |      | μs    |

| Bus Free Time Between a<br>Stop and Start Condition | t <sub>BUS</sub>    |                                                           | 0.5  |     |      | μs    |

| Data Valid Time                                     | t <sub>VD;DAT</sub> |                                                           | 0.45 |     |      | μs    |

| Data Valid Acknowledge<br>Time                      | t <sub>VD;ACK</sub> |                                                           | 0.45 |     |      | μs    |

Figure 4. I<sup>2</sup>C Timing Diagram

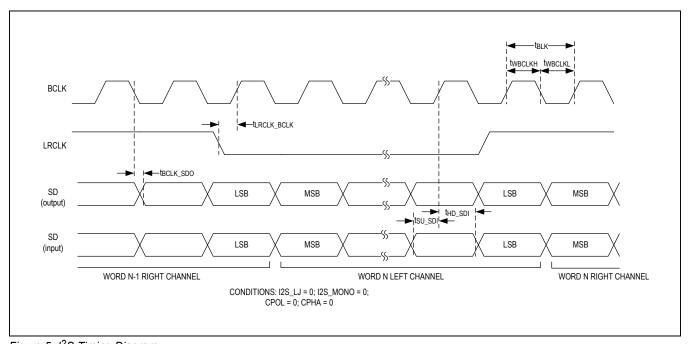

# Electrical Characteristics—I2S Target

(Limits are 100% tested at  $T_A = +25$ °C and  $T_A = +105$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                             | SYMBOL              | CONDITIONS            | MIN | TYP | MAX   | UNITS               |

|---------------------------------------|---------------------|-----------------------|-----|-----|-------|---------------------|

| Bit Clock Frequency                   | f <sub>BCLK</sub>   | 96kHz LRCLK frequency |     |     | 3.072 | MHz                 |

| BCLK High Time                        | twbclkh             |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| BCLK Low Time                         |                     |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| LRCLK Setup Time                      | tLRCLK_BLCK         |                       |     | 25  |       | ns                  |

| Delay Time, BCLK to SD (Output) Valid | tBCLK_SDO           |                       |     | 12  |       | ns                  |

| Setup Time for SD (Input)             | tsu_sdi             |                       |     | 6   |       | ns                  |

| Hold Time SD (Input)                  | t <sub>HD_SDI</sub> |                       |     | 3   |       | ns                  |

Figure 5. I<sup>2</sup>S Timing Diagram

Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

# **Pin Configurations**

# **Pin Description**

|        | PIN               |                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|-------------------|-------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 WLP | 20<br>TQFN-<br>EP | 24<br>TQFN-<br>EP | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| POWER  |                   |                   |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A3     | 9                 | 11, 22            | V <sub>DD</sub> | Digital Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0µF capacitor with $60m\Omega$ to $200m\Omega$ ESR as close as possible to the package. The device can operate soley from this one power supply pin without the need to connect $V_{CORE}$ by utilizing the internal $V_{CORE}$ regulator. The internal $V_{CORE}$ regulator automatically operates if the presence of a voltage on the $V_{CORE}$ pin is not detected. This provides single supply battery operation capability. |

# **Pin Description (continued)**

| PIN     |                   |                   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 WLP  | 20<br>TQFN-<br>EP | 24<br>TQFN-<br>EP | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A4      | 10                | 12                | V <sub>CORE</sub> | Core Supply Voltage. This pin provides dual supply operation to support PMIC-based systems and should be left open-circuit for single supply operation. This pin must always be bypassed to $V_{SS}$ with a $1.0\mu F$ capacitor with $60m\Omega$ to $200m\Omega$ ESR as close as possible to the package regardless of the supply mode of operation.                                                                                                                                                                                                    |

| B2      | 6                 | 7, 10             | V <sub>SS</sub>   | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _       | _                 | _                 | EP                | Exposed Pad (TQFN only). This pad must be connected to V <sub>SS</sub> . Refer to Application Note 3273: Exposed Pads: A Brief Introduction for additional information.                                                                                                                                                                                                                                                                                                                                                                                  |

| CLOCK   |                   |                   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A2      | 8                 | 9                 | 32KIN             | 32.768kHz Crystal Oscillator Input. Connect a 6pF 32.768kHz crystal between 32KIN and 32KOUT for RTC operation. Optionally, an external clock source can be driven on 32KIN if the 32KOUT pin is left unconnected.                                                                                                                                                                                                                                                                                                                                       |

| A1      | 7                 | 8                 | 32KOUT            | 32.768kHz Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RESET   |                   |                   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B1      | 5                 | 6                 | RSTN              | Active-Low, External System Reset Input. The device remains in reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a POR reset (resetting all logic on all supplies except for real-time clock circuitry) and begins execution. This pin is internally connected with an internal pullup to the V <sub>DD</sub> supply as indicated in the <i>Electrical Characteristics</i> table. This pin should be left unconnected if the system design does not provide a reset signal to the device. |

| GENERAL | -PURPOSE          | I/O (See Ta       | ble 3 and T       | able 4 for pin mapping.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| C1      | 2                 | 2                 | P0.0              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C2      | 1                 | 1                 | P0.1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1      | 20                | 24                | P0.2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D2      | 19                | 23                | P0.3              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D3      | 18                | 21                | P0.4              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D4      | 17                | 20                | P0.5              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C3      | 16                | 19                | P0.6              | General-Purpose I/O. Most port pins have multiple special functions. See Table 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| C4      | 15                | 18                | P0.7              | and <u>Table 4</u> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B4      | 12                | 14                | P0.8              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| В3      | 11                | 13                | P0.9              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| _       | 14                | 17                | P0.10             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 13                | 16                | P0.11             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| _       | 4                 | 5                 | P0.12             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | 3                 | 4                 | P0.13             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Tiny, Ultra-Low-Power Arm Cortex-M4 Processor with FPU-Based Microcontroller (MCU) with 256KB Flash and 96KB SRAM

### **Detailed Description**

The MAX32660 is an ultra-low power, cost-effective, highly-integrated microcontroller designed for battery-powered devices and wireless sensors. It combines a flexible and versatile power management unit with the powerful Arm Cortex-M4 processor with FPU. The device enables designs with complex sensor processing without compromising battery life. It also offers legacy designs an easy and cost optimal upgrade path from 8- or 16-bit microcontrollers. The device integrates up to 256KB of flash memory and 96KB of RAM to accommodate application and sensor code.

The device features four powerful and flexible power modes. It can operate from a single- or dual-supply battery voltage, typically provided by a PMIC. The I<sup>2</sup>C port supports standard, fast, fast-plus, and high-speed modes, operating up to 3400kbps. Two UARTs are provided, and the SPI ports can run up to 48MHz in both controller and target mode. Three general-purpose 32-bit timers, a watchdog timer, and a real-time clock are also provided. An I<sup>2</sup>S interface provides audio streaming to a codec.

#### Memory

#### **Internal Flash Memory**

256KB of internal flash memory provides nonvolatile storage of program and data memory.

#### **Internal SRAM**

The internal 96KB SRAM provides low-power retention of application information in all power modes except shutdown. The SRAM can be divided into granular banks that create a flexible SRAM retention architecture. This data retention feature is optional, and is configurable. This granularity allows the application to minimize its power consumption by only retaining the most essential data.

#### **Clocking Scheme**

The high-frequency internal oscillator (HFIO) operates at a nominal frequency of 96MHz.

Optionally, two other oscillators can be selected depending upon power needs:

- 80kHz nanoring oscillator

- 32.768kHz oscillator (external crystal required)