19-3332; Rev 3; 3/08

#

## 12-Bit, Multichannel ADCs/DACs with FIFO, Temperature Sensing, and GPIO Ports

## **General Description**

\_Features

- The MAX1340/MAX1342/MAX1346/MAX1348 integrate a multichannel, 12-bit, analog-to-digital converter (ADC) and a quad, 12-bit, digital-to-analog converter (DAC) in a single IC. The devices also include a temperature sensor and configurable general-purpose I/O ports (GPIOs) with a 25MHz SPI™-/QSPI™-/MICROWIRE™-compatible serial interface. The ADC is available in a 4 or an 8 input-channel version. The four DAC outputs settle within 2.0µs, and the ADC has a 225ksps conversion rate.

- All devices include an internal reference (4.096V) providing a well-regulated, low-noise reference for both the ADC and DAC. Programmable reference modes for the ADC and DAC allow the use of an internal reference, an external reference, or a combination of both. Features such as an internal ±1°C accurate temperature sensor, FIFO, scan modes, programmable internal or external clock modes, data averaging, and AutoShutdown<sup>™</sup> allow users to minimize both power consumption and processor requirements. The low glitch energy (4nV•s) and low digital feedthrough (0.5nV•s) of the integrated quad DACs make these devices ideal for digital control of fastresponse closed-loop systems.

The devices are guaranteed to operate with a supply voltage from +4.75V to +5.25V The devices consume 2.5mA at 225ksps throughput, only 22 $\mu$ A at 1ksps throughput, and under 0.2 $\mu$ A in the shutdown mode. The MAX1342/MAX1348 offer four GPIOs that can be configured as inputs or outputs.

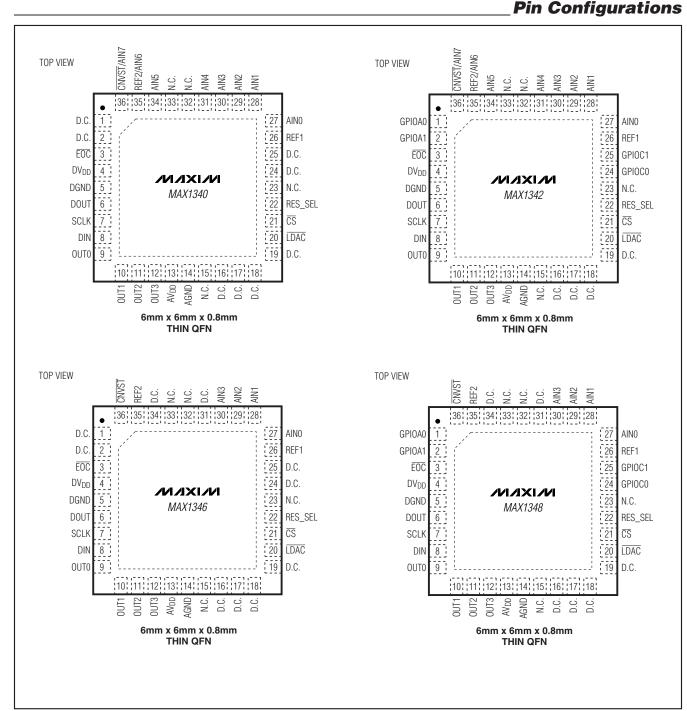

The MAX1340/MAX1342/MAX1346/MAX1348 are available in 36-pin thin QFN packages. All devices are specified over the -40°C to +85°C temperature range.

## **Applications**

Closed-Loop Controls for Optical Components and Base Stations System Supervision and Control Data-Acquisition Systems

- 12-Bit, 225ksps ADC Analog Multiplexer with True-Differential

- Tračk/Hold (T/H) 8 Single-Ended Channels or 4 Differential Channels (Unipolar or Bipolar) (MAX1340/MAX1342)

- (MAX1340/MAX1342) 4 Single-Ended Channels or 2 Differential Channels (Unipolar or Bipolar) (MAX1346/MAX1348)

- Excellent Accuracy: ±0.5 LSB INL, ±0.5 LSB DNL

- 12-Bit, Quad, 2µs Settling DAC Ultra-Low Glitch Energy (4nV·s) Power-Up Options from Zero Scale or Full Scale Excellent Accuracy: ±0.5 LSB INL

- Internal Reference or External Single-Ended/ Differential Reference Internal Reference Voltage (4.096V)

- ♦ Internal ±1°C Accurate Temperature Sensor

- On-Chip FIFO Capable of Storing 16 ADC Conversion Results and One Temperature Result

- On-Chip Channel-Scan Mode and Internal Data-Averaging Features

- Analog Single-Supply Operation +4.75V to +5.25V

- Digital Supply: 2.7V to AVDD

- ♦ 25MHz, SPI/QSPI/MICROWIRE Serial Interface

- AutoShutdown Between Conversions

- ♦ Low-Power ADC 2.5mA at 225ksps 22µA at 1ksps 0.2µA at Shutdown

- Low-Power DAC: 1.5mA

- Evaluation Kit Available (Order MAX1258EVKIT)

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp. AutoShutdown is a trademark of Maxim Integrated Products, Inc.

Pin Configurations appear at end of data sheet.

### **Ordering Information/Selector Guide** REF ANALOG RESOLUTION ADC DAC SUPPLY VOLTAGE GPIOs PART **TEMP RANGE** PIN-PACKAGE BITS\*\* CHANNELS CHANNELS (V) VOLTAGE (V) MAX1340BETX -40°C to +85°C 36 Thin QFN-EP\* 4.096 4.75 to 5.25 12 8 4 0 MAX1342BETX -40°C to +85°C 36 Thin QFN-EP\* 4.096 4.75 to 5.25 12 8 4 4 MAX1346BETX -40°C to +85°C 36 Thin QFN-EP\* 4.096 4.75 to 5.25 12 4 4 0 MAX1348BETX -40°C to +85°C 36 Thin QFN-EP\* 4.096 4.75 to 5.25 12 4 4 4

\*EP = Exposed pad.

\*\*Number of resolution bits refers to both DAC and ADC.

## M/IXI/M

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to AGND             | -0.3V to +6V                      |

|--------------------------------------|-----------------------------------|

| DGND to AGND                         |                                   |

| DV <sub>DD</sub> to AV <sub>DD</sub> |                                   |

| Digital Inputs to DGND               | 0.3V to +6V                       |

| Digital Outputs to DGND              | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| Analog Inputs, Analog Outputs and F  | REF_                              |

| to AGND                              | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| Maximum Current into Any Pin (exce   | pt AGND, DGND, AV <sub>DD</sub> , |

| DV <sub>DD</sub> , and OUT_)         | 50mA                              |

| Maximum Current into OUT                            | 100mA          |

|-----------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ |                |

| 36-Pin Thin QFN (6mm x 6mm)                         |                |

| (derate 26.3mW/°C above +70°C)                      | 2105.3mW       |

| Operating Temperature Range                         | 40°C to +85°C  |

| Storage Temperature Range                           | 60°C to +150°C |

| Junction Temperature                                | +150°C         |

| Lead Temperature (soldering, 10s)                   | +300°C         |

Note: If the package power dissipation is not exceeded, one output at a time may be shorted to AV<sub>DD</sub>, DV<sub>DD</sub>, AGND, or DGND indefinitely.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

| PARAMETER                                               | SYMBOL      | CONDITIONS                                                    | MIN            | ТҮР  | МАХ  | UNITS                         |

|---------------------------------------------------------|-------------|---------------------------------------------------------------|----------------|------|------|-------------------------------|

|                                                         | •           | ADC                                                           |                |      |      |                               |

| DC ACCURACY (Note 1)                                    |             |                                                               |                |      |      |                               |

| Resolution                                              |             |                                                               | 12             |      |      | Bits                          |

| Integral Nonlinearity                                   | INL         |                                                               |                | ±0.5 | ±1.0 | LSB                           |

| Differential Nonlinearity                               | DNL         |                                                               |                | ±0.5 | ±1.0 | LSB                           |

| Offset Error                                            |             |                                                               |                | ±0.5 | ±4.0 | LSB                           |

| Gain Error                                              |             | (Note 2)                                                      |                | ±0.5 | ±4.0 | LSB                           |

| Gain Temperature Coefficient                            |             |                                                               |                | ±0.8 |      | ppm/°C                        |

| Channel-to-Channel Offset                               |             |                                                               |                | ±0.1 |      | LSB                           |

| <b>DYNAMIC SPECIFICATIONS (1</b>                        | 0kHz sine-w | ave input, V <sub>IN</sub> = 4.096V <sub>P-P</sub> , 225ksps, | fclk = 3.6MHz) |      |      |                               |

| Signal-to-Noise Plus Distortion                         | SINAD       |                                                               |                | 70   |      | dB                            |

| Total Harmonic Distortion<br>(Up to the Fifth Harmonic) | THD         |                                                               |                | -76  |      | dBc                           |

| Spurious-Free Dynamic Range                             | SFDR        |                                                               |                | 72   |      | dBc                           |

| Intermodulation Distortion                              | IMD         | $f_{IN1} = 9.9 \text{kHz}, f_{IN2} = 10.2 \text{kHz}$         |                | 76   |      | dBc                           |

| Full-Linear Bandwidth                                   |             | SINAD > 70dB                                                  |                | 100  |      | kHz                           |

| Full-Power Bandwidth                                    |             | -3dB point                                                    |                | 1    |      | MHz                           |

| CONVERSION RATE (Note 3)                                |             | •                                                             | ·              |      |      |                               |

|                                                         |             | External reference                                            |                | 0.8  |      | μs                            |

| Power-Up Time                                           | t₽U         | Internal reference (Note 4)                                   |                | 218  |      | Conversion<br>Clock<br>Cycles |

(AVDD = DVDD = 4.75V to 5.25V, external reference VREF = 4.096V, fCLK = 3.6MHz (50% duty cycle), TA = -40°C to +85°C, unless otherwise noted. Typical values are at AVDD = DVDD = 5V, TA = +25°C. Outputs are unloaded, unless otherwise noted.)

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 4.75V \text{ to } 5.25V, \text{ external reference } V_{REF} = 4.096V, f_{CLK} = 3.6MHz$  (50% duty cycle),  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $AV_{DD} = DV_{DD} = 5V$ ,  $T_A = +25^{\circ}C$ . Outputs are unloaded, unless otherwise noted.)

| PARAMETER                               | SYMBOL            | CONDITIONS                                                 | MIN                  | ТҮР   | МАХ                        | UNITS  |  |

|-----------------------------------------|-------------------|------------------------------------------------------------|----------------------|-------|----------------------------|--------|--|

| Acquisition Time                        | tacq              | (Note 5)                                                   | 0.6                  |       |                            | μs     |  |

|                                         |                   | Internally clocked                                         |                      | 5.5   |                            |        |  |

| Conversion Time                         | <b>t</b> CONV     | Externally clocked                                         | 3.6                  |       |                            | μs     |  |

| External-Clock Frequency                | fCLK              | Externally clocked conversion (Note 5)                     | 0.1                  |       | 3.6                        | MHz    |  |

| Duty Cycle                              |                   |                                                            | 40                   |       | 60                         | %      |  |

| Aperture Delay                          |                   |                                                            |                      | 30    |                            | ns     |  |

| Aperture Jitter                         |                   |                                                            |                      | < 50  |                            | ps     |  |

| ANALOG INPUTS                           |                   |                                                            |                      |       |                            |        |  |

| Input Voltage Denge (Note 6)            |                   | Unipolar                                                   | 0                    |       | V <sub>REF</sub>           | V      |  |

| Input-Voltage Range (Note 6)            |                   | Bipolar                                                    | -V <sub>REF</sub> /2 |       | V <sub>REF</sub> /2        | V      |  |

| Input Leakage Current                   |                   |                                                            |                      | ±0.01 | ±1                         | μΑ     |  |

| Input Capacitance                       |                   |                                                            |                      | 24    |                            | pF     |  |

| INTERNAL TEMPERATURE SE                 | NSOR              |                                                            |                      |       |                            |        |  |

|                                         |                   | $T_A = +25^{\circ}C$                                       |                      | ±0.7  |                            | °C     |  |

| Measurement Error (Notes 5, 7)          |                   | $T_A = T_{MIN}$ to $T_{MAX}$                               |                      | ±1.0  | ±3.0                       | Ĵ      |  |

| Temperature Resolution                  |                   |                                                            |                      | 1/8   |                            | °C/LSB |  |

| INTERNAL REFERENCE                      |                   |                                                            |                      |       |                            |        |  |

| REF1 Output Voltage                     |                   | (Note 8)                                                   | 4.066                | 4.096 | 4.126                      | V      |  |

| REF1 Voltage Temperature<br>Coefficient | TC <sub>REF</sub> |                                                            |                      | ±30   |                            | ppm/°C |  |

| REF1 Output Impedance                   |                   |                                                            |                      | 6.5   |                            | kΩ     |  |

| REF1 Short-Circuit Current              |                   | V <sub>REF</sub> = 4.096V                                  |                      | 0.63  |                            | mA     |  |

| EXTERNAL REFERENCE                      |                   | ·                                                          | •                    |       |                            |        |  |

| REF1 Input-Voltage Range                | V <sub>REF1</sub> | REF mode 11 (Note 4)                                       | 1                    |       | AV <sub>DD</sub> +<br>0.05 | V      |  |

| REF2 Input-Voltage Range                | V <sub>REF2</sub> | REF mode 01                                                | 1                    |       | AV <sub>DD</sub> +<br>0.05 | V      |  |

| (Note 4)                                |                   | REF mode 11                                                | 0                    |       | 1                          |        |  |

|                                         |                   | $V_{REF} = 4.096V$ , $f_{SAMPLE} = 225ksps$                |                      | 40    | 80                         | _      |  |

| REF1 Input Current (Note 9)             | IREF1             | Acquisition between conversions                            |                      | ±0.01 | ±1                         | μA     |  |

|                                         |                   | $V_{\text{REF}} = 4.096V$ , $f_{\text{SAMPLE}} = 225$ ksps |                      | 40    | 80                         |        |  |

| REF2 Input Current                      | IREF2             | Acquisition between conversions                            |                      | ±0.01 | ±1                         | μA     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 4.75V \text{ to } 5.25V, \text{ external reference } V_{REF} = 4.096V, f_{CLK} = 3.6MHz$  (50% duty cycle),  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $AV_{DD} = DV_{DD} = 5V$ ,  $T_A = +25^{\circ}C$ . Outputs are unloaded, unless otherwise noted.)

| PARAMETER                                      | SYMBOL     | CONDITIONS                                               | MIN  | ТҮР  | МАХ                        | UNITS             |  |

|------------------------------------------------|------------|----------------------------------------------------------|------|------|----------------------------|-------------------|--|

|                                                | 1          | DAC                                                      |      |      |                            |                   |  |

| DC ACCURACY (Note 10)                          |            |                                                          |      |      |                            |                   |  |

| Resolution                                     |            |                                                          | 12   |      |                            | Bits              |  |

| Integral Nonlinearity                          | INL        |                                                          |      | ±0.5 | ±4                         | LSB               |  |

| Differential Nonlinearity                      | DNL        | Guaranteed monotonic                                     |      |      | ±1.0                       | LSB               |  |

| Offset Error                                   | Vos        | (Note 8)                                                 |      | ±3   | ±10                        | mV                |  |

| Offset-Error Drift                             |            |                                                          |      | ±10  |                            | ppm of<br>FS/°C   |  |

| Gain Error                                     | GE         | (Note 8)                                                 |      | ±5   | ±10                        | LSB               |  |

| Gain Temperature Coefficient                   |            |                                                          |      | ±8   |                            | ppm of<br>FS/°C   |  |

| DAC OUTPUT                                     |            |                                                          |      |      |                            |                   |  |

| Output Valtage Dange                           |            | No load                                                  | 0.02 |      | AV <sub>DD</sub> -<br>0.02 | N                 |  |

| Output-Voltage Range                           |            | 10k $\Omega$ load to either rail                         | 0.1  |      | AV <sub>DD</sub> -<br>0.1  | V                 |  |

| DC Output Impedance                            |            |                                                          |      | 0.5  |                            | Ω                 |  |

| Capacitive Load                                |            | (Note 11)                                                |      |      | 1                          | nF                |  |

| Resistive Load to AGND                         | RL         | $AV_{DD} = 4.75V$ , $V_{REF} = 4.096V$ , gain error < 2% | 500  |      |                            | Ω                 |  |

|                                                |            | From power-down mode, AV <sub>DD</sub> = 5V              |      | 25   |                            |                   |  |

| Wake-Up Time (Note 12)                         |            | From power-down mode, AV <sub>DD</sub> = 2.7V            |      | 21   |                            | μs                |  |

| 1k $\Omega$ Output Termination                 |            | Programmed in power-down mode                            |      | 1    |                            | kΩ                |  |

| 100k $\Omega$ Output Termination               |            | At wake-up or programmed in<br>power-down mode           |      | 100  |                            | kΩ                |  |

| DYNAMIC PERFORMANCE (No                        | tes 5, 13) | •                                                        |      |      |                            |                   |  |

| Output-Voltage Slew Rate                       | SR         | Positive and negative                                    | 3    |      |                            | V/µs              |  |

| Output-Voltage Settling Time                   | ts         | To 1 LSB, 400 - C00 hex (Note 7)                         |      | 2    | 5                          | μs                |  |

| Digital Feedthrough                            |            | Code 0, all digital inputs from 0 to DVDD                |      | 0.5  |                            | nV∙s              |  |

| Major Code Transition Glitch<br>Impulse        |            | Between codes 2047 and 2048                              |      | 4    |                            | nV•s              |  |

|                                                |            | From V <sub>REF</sub>                                    |      | 660  |                            |                   |  |

| Output Noise (0.1Hz to 50MHz)                  |            | Using internal reference                                 |      | 720  |                            | μV <sub>P-P</sub> |  |

| <b>0</b> · · · · · · · · · · · · · · · · · · · |            | From V <sub>REF</sub>                                    |      | 260  |                            | /                 |  |

| Output Noise (0.1Hz to 500kHz)                 |            | Using internal reference 320                             |      |      |                            | μV <sub>P-P</sub> |  |

| DAC-to-DAC Transition<br>Crosstalk             |            |                                                          |      | 0.5  |                            | nV∙s              |  |

M/IXI/N

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 4.75V \text{ to } 5.25V, \text{ external reference } V_{REF} = 4.096V, f_{CLK} = 3.6MHz$  (50% duty cycle),  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $AV_{DD} = DV_{DD} = 5V$ ,  $T_A = +25^{\circ}C$ . Outputs are unloaded, unless otherwise noted.)

| PARAMETER                    | SYMBOL            | CONDITIONS                        | MIN                       | ΤΥΡ   | MAX              | UNITS  |

|------------------------------|-------------------|-----------------------------------|---------------------------|-------|------------------|--------|

| INTERNAL REFERENCE           |                   | •                                 |                           |       |                  |        |

| REF1 Output Voltage          |                   |                                   | 4.066                     | 4.096 | 4.126            | V      |

| REF1 Temperature Coefficient | TCREF             |                                   |                           | ±30   |                  | ppm/°C |

| REF1 Short-Circuit Current   |                   | $V_{REF} = 4.096V$                |                           | 0.63  |                  | mA     |

| EXTERNAL-REFERENCE INPL      | IT                |                                   |                           |       |                  |        |

| REF1 Input-Voltage Range     | V <sub>REF1</sub> | REF modes 01, 10, and 11 (Note 4) | 0.7                       |       | AV <sub>DD</sub> | V      |

| REF1 Input Impedance         | R <sub>REF1</sub> |                                   | 70                        | 100   | 130              | kΩ     |

|                              |                   | DIGITAL INTERFACE                 |                           |       |                  |        |

| DIGITAL INPUTS (SCLK, DIN,   | CS, CNVST, I      | LDAC)                             |                           |       |                  |        |

| Input-Voltage High           | VIH               | DV <sub>DD</sub> = 2.7V to 5.25V  | 2.4                       |       |                  | V      |

|                              | M                 | DV <sub>DD</sub> = 3.6V to 5.25V  |                           |       | 0.8              |        |

| Input-Voltage Low            | VIL               | DV <sub>DD</sub> = 2.7V to 3.6V   |                           |       | 0.6              | V      |

| Input Leakage Current        | ١L                |                                   |                           | ±0.01 | ±10              | μA     |

| Input Capacitance            | CIN               |                                   |                           | 15    |                  | рF     |

| DIGITAL OUTPUT (DOUT) (Not   | te 14)            | •                                 |                           |       |                  |        |

| Output-Voltage Low           | VOL               | I <sub>SINK</sub> = 2mA           |                           |       | 0.4              | V      |

| Output-Voltage High          | V <sub>OH</sub>   | ISOURCE = 2mA                     | DV <sub>DD</sub> -<br>0.5 |       |                  | V      |

| Tri-State Leakage Current    |                   |                                   |                           |       | ±10              | μA     |

| Tri-State Output Capacitance | Cout              |                                   |                           | 15    |                  | pF     |

| DIGITAL OUTPUT (EOC) (Note   |                   | 1                                 |                           |       |                  |        |

| Output-Voltage Low           | VOL               | I <sub>SINK</sub> = 2mA           |                           |       | 0.4              | V      |

| Output-Voltage High          | V <sub>OH</sub>   | ISOURCE = 2mA                     | DV <sub>DD</sub> -<br>0.5 |       |                  | V      |

| Tri-State Leakage Current    |                   |                                   |                           |       | ±10              | μA     |

| Tri-State Output Capacitance | Соит              |                                   |                           | 15    |                  | pF     |

| DIGITAL OUTPUTS (GPIO_) (N   |                   |                                   |                           |       |                  |        |

|                              | ,                 | I <sub>SINK</sub> = 2mA           |                           |       | 0.4              |        |

| GPIOC_Output-Voltage Low     |                   | Isink = 4mA                       |                           |       | 0.8              | V      |

| GPIOC_Output-Voltage High    |                   | ISOURCE = 2mA                     | DV <sub>DD</sub> -<br>0.5 |       |                  | V      |

| GPIOA_ Output-Voltage Low    |                   | I <sub>SINK</sub> = 15mA          |                           |       | 0.8              | V      |

| GPIOA_ Output-Voltage High   |                   | ISOURCE = 15mA                    | DV <sub>DD</sub> -<br>0.8 |       | -                | V      |

| Tri-State Leakage Current    |                   |                                   |                           |       | ±10              | μA     |

| Tri-State Output Capacitance | Соит              |                                   |                           | 15    | -                | pF     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 4.75V \text{ to } 5.25V, \text{ external reference } V_{REF} = 4.096V, f_{CLK} = 3.6MHz$  (50% duty cycle),  $T_A = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $AV_{DD} = DV_{DD} = 5V$ ,  $T_A = +25^{\circ}C$ . Outputs are unloaded, unless otherwise noted.)

| PARAMETER                                                   | SYMBOL           | CONDITIONS                                       | MIN  | ТҮР   | MAX              | UNITS |

|-------------------------------------------------------------|------------------|--------------------------------------------------|------|-------|------------------|-------|

| POWER REQUIREMENTS (Note                                    | 15)              | •                                                |      |       |                  |       |

| Digital Positive-Supply Voltage                             | DVDD             |                                                  | 4.75 |       | AV <sub>DD</sub> | V     |

| Digital Degitive Currenty Current                           | DI               | Idle, all blocks shut down                       |      | 0.2   | 4                | μΑ    |

| Digital Positive-Supply Current                             | DIDD             | Only ADC on, external reference                  |      | 1     |                  | mA    |

| Analog Positive-Supply Voltage                              | AV <sub>DD</sub> |                                                  | 4.75 |       | 5.25             | V     |

|                                                             |                  | Idle, all blocks shut down                       |      | 0.2   | 2                | μA    |

| Analog Positive-Supply Current                              | A.65             | Only ADC on, fsample = 225ksps                   |      | 2.8   | 4.2              |       |

| Analog Fositive-Supply Current                              | Aidd             | external reference f <sub>SAMPLE</sub> = 100ksps |      | 2.6   |                  | mA    |

|                                                             |                  | All DACs on, no load, internal reference         |      | 1.5   | 4.0              |       |

| REF1 Positive-Supply Rejection                              | PSRR             | $AV_{DD} = 4.75V$                                |      | -80   |                  | dB    |

| DAC Positive-Supply Rejection                               | PSRD             | Output code = FFFhex, $AV_{DD} = 4.75V$ to 5.25V |      | ±0.1  | ±0.5             | mV    |

| ADC Positive-Supply Rejection                               | PSRA             | Full-scale input, $AV_{DD} = 4.75V$ to 5.25V     |      | ±0.06 | ±0.5             | mV    |

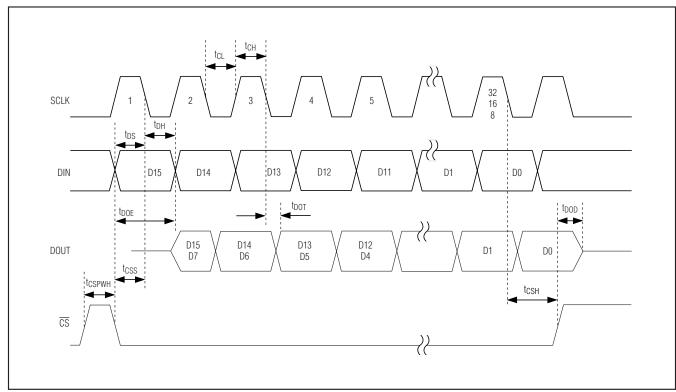

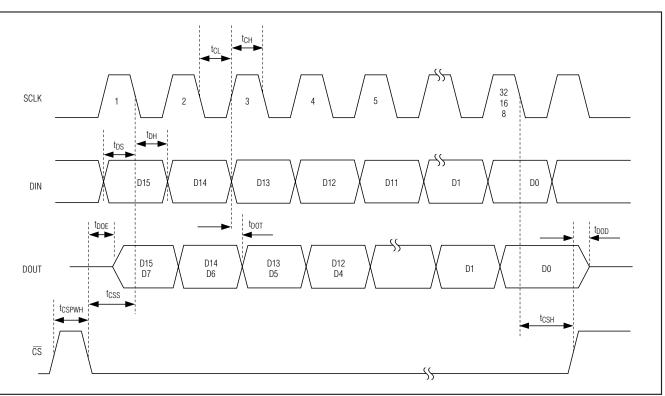

| TIMING CHARACTERISTICS (Fi                                  | gures 6–13)      |                                                  |      |       |                  |       |

| SCLK Clock Period                                           | tCP              |                                                  | 40   |       |                  | ns    |

| SCLK Pulse-Width High                                       | tсн              | 40/60 duty cycle                                 | 16   |       |                  | ns    |

| SCLK Pulse-Width Low                                        | tCL              | 60/40 duty cycle                                 | 16   |       |                  | ns    |

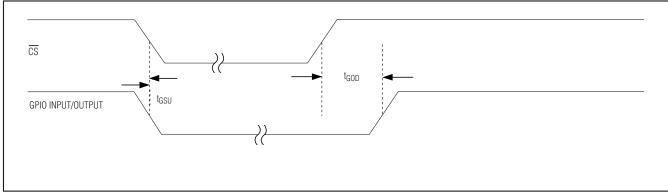

| GPIO Output Rise/Fall After $\overline{CS}$ Rise            | tGOD             | C <sub>LOAD</sub> = 20pF                         |      |       | 100              | ns    |

| GPIO Input Setup Before CS Fall                             | tgsu             |                                                  | 0    |       |                  | ns    |

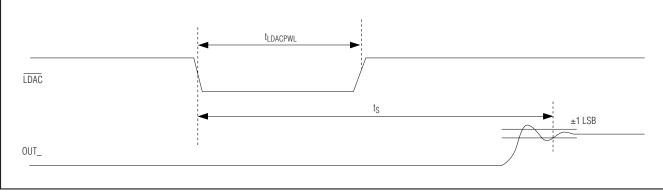

| LDAC Pulse Width                                            | tLDACPWL         |                                                  | 20   |       |                  | ns    |

| SCLK Fall to DOUT Transition                                |                  | $C_{LOAD} = 20 pF, SLOW = 0$                     | 1.8  |       | 12.0             |       |

| (Note 16)                                                   | tdot             | $C_{LOAD} = 20 pF, SLOW = 1$                     | 10   |       | 40               | ns    |

| SCLK Rise to DOUT Transition                                | 4.               | $C_{LOAD} = 20 pF, SLOW = 0$                     | 1.8  |       | 12.0             |       |

| (Notes 16, 17)                                              | tdot             | $C_{LOAD} = 20 pF, SLOW = 1$                     | 10   |       | 40               | ns    |

| CS Fall to SCLK Fall Setup Time                             | tcss             |                                                  | 10   |       |                  | ns    |

| SCLK Fall to $\overline{\text{CS}}$ Rise Setup Time         | tCSH             |                                                  | 0    |       | 2000             | ns    |

| DIN to SCLK Fall Setup Time                                 | tDS              |                                                  | 10   |       |                  | ns    |

| DIN to SCLK Fall Hold Time                                  | tDH              |                                                  | 0    |       |                  | ns    |

| CS Pulse-Width High                                         | tCSPWH           |                                                  | 50   |       |                  | ns    |

| CS Rise to DOUT Disable                                     | tdod             | C <sub>LOAD</sub> = 20pF                         |      |       | 25               | ns    |

| CS Fall to DOUT Enable                                      | <b>t</b> DOE     | C <sub>LOAD</sub> = 20pF                         | 1.5  |       | 25.0             | ns    |

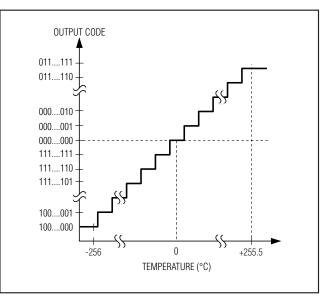

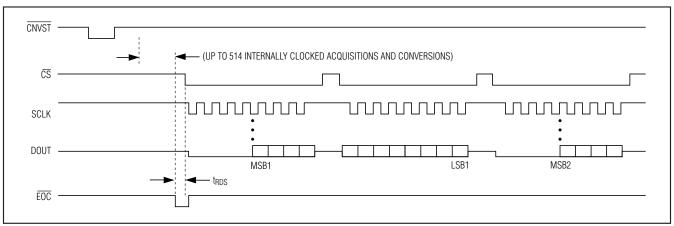

| $\overline{\text{EOC}}$ Fall to $\overline{\text{CS}}$ Fall | t <sub>RDS</sub> |                                                  | 30   |       |                  | ns    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 4.75V$  to 5.25V, external reference  $V_{REF} = 4.096V$ ,  $f_{CLK} = 3.6MHz$  (50% duty cycle),  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $AV_{DD} = DV_{DD} = 5V$ ,  $T_A = +25^{\circ}C$ . Outputs are unloaded, unless otherwise noted.)

| PARAMETER                             | SYMBOL | CONDITIONS                                                                                 | MIN | ТҮР | MAX | UNITS |

|---------------------------------------|--------|--------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| CS or CNVST Rise to EOC Fall—         | tdov   | CKSEL = 01 (temp sense) or CKSEL = 10 (temp sense), internal reference on                  |     |     | 65  |       |

|                                       |        | CKSEL = 01 (temp sense) or CKSEL =<br>10 (temp sense), internal reference<br>initially off |     |     | 140 |       |

| Internally Clocked<br>Conversion Time |        | CKSEL = 01 (voltage conversion)                                                            |     |     | 9   | μs    |

| Conversion time                       |        | CKSEL = 10 (voltage conversion),<br>internal reference on                                  |     |     | 9   |       |

|                                       |        | CKSEL = 10 (voltage conversion),<br>internal reference initially off                       |     |     | 80  |       |

| CNVST Pulse Width                     | toow   | CKSEL = 00, CKSEL = 01 (temp sense)                                                        | 40  |     |     | ns    |

|                                       | tcsw   | CKSEL = 01 (voltage conversion)                                                            | 1.4 |     |     | μs    |

**Note 1:** Tested at  $DV_{DD} = AV_{DD} = +5.25V$ .

Note 2: Offset nulled.

**Note 3:** No bus activity during conversion. Conversion time is defined as the number of conversion clock cycles, multiplied by the clock period.

**Note 4:** See Table 5 for reference-mode details.

Note 5: Not production tested. Guaranteed by design.

**Note 6:** See the *ADC/DAC References* section.

Note 7: Fast automated test, excludes self-heating effects.

**Note 8:** Specified over the -40°C to +85°C temperature range.

**Note 9:** REFSEL[1:0] = 00 or when DACs are not powered up.

Note 10: DAC linearity, gain, and offset measurements are made between codes 115 and 3981.

Note 11: The DAC buffers are guaranteed by design to be stable with a 1nF load.

Note 12: Time required by the DAC output to power up and settle within 1 LSB in the external reference mode.

**Note 13:** All DAC dynamic specifications are valid for a load of 100pF and  $10k\Omega$ .

Note 14: Only one digital output (either DOUT, EOC, or the GPIOs) can be indefinitely shorted to either supply at one time.

**Note 15:** All digital inputs at either DV<sub>DD</sub> or DGND. DV<sub>DD</sub> should not exceed AV<sub>DD</sub>.

Note 16: See the Reset Register section and Table 9 for details on programming the SLOW bit.

Note 17: Clock mode 11 only.

M/XI/M

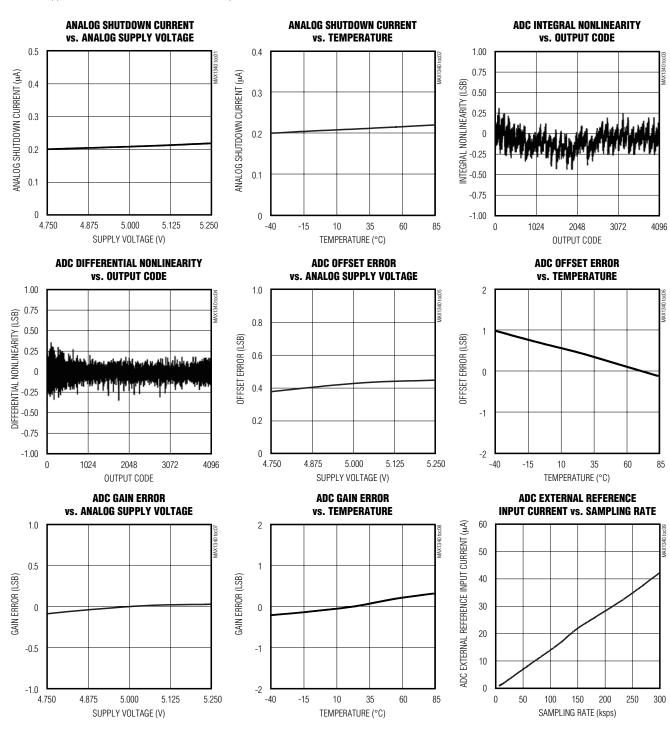

(AVDD = DVDD = 5V, external VREF = 4.096V, fCLK = 3.6MHz (50% duty cycle), fSAMPLE = 225ksps, CLOAD = 50pF, 0.1µF capacitor

**Typical Operating Characteristics**

MAX1340/MAX1342/MAX1346/MAX1348

at REF,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MIXIM

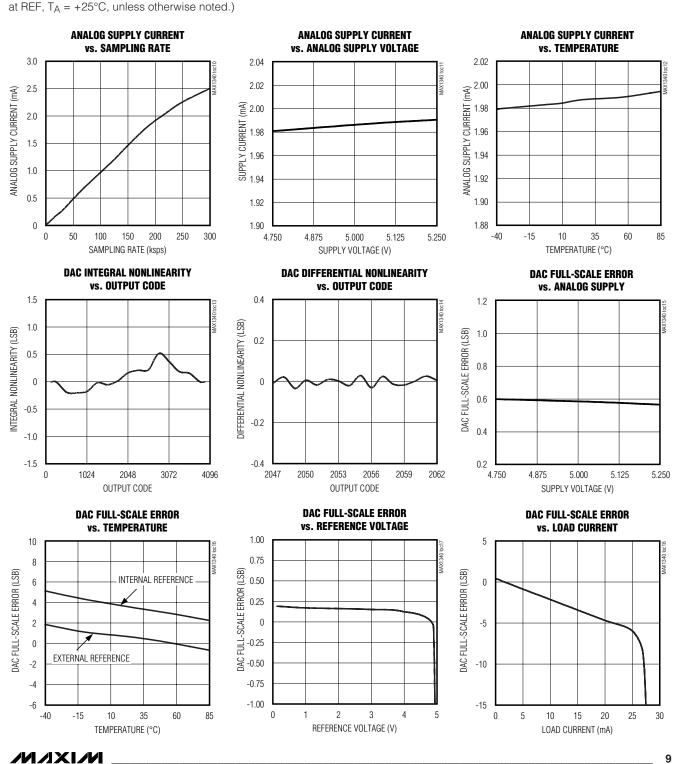

(AV<sub>DD</sub> = DV<sub>DD</sub> = 5V, external V<sub>REF</sub> = 4.096V, f<sub>CLK</sub> = 3.6MHz (50% duty cycle), f<sub>SAMPLE</sub> = 225ksps, C<sub>LOAD</sub> = 50pF, 0.1µF capacitor

**Typical Operating Characteristics (continued)**

MAX1340/MAX1342/MAX1346/MAX1348

MAX1340/MAX1342/MAX1346/MAX1348

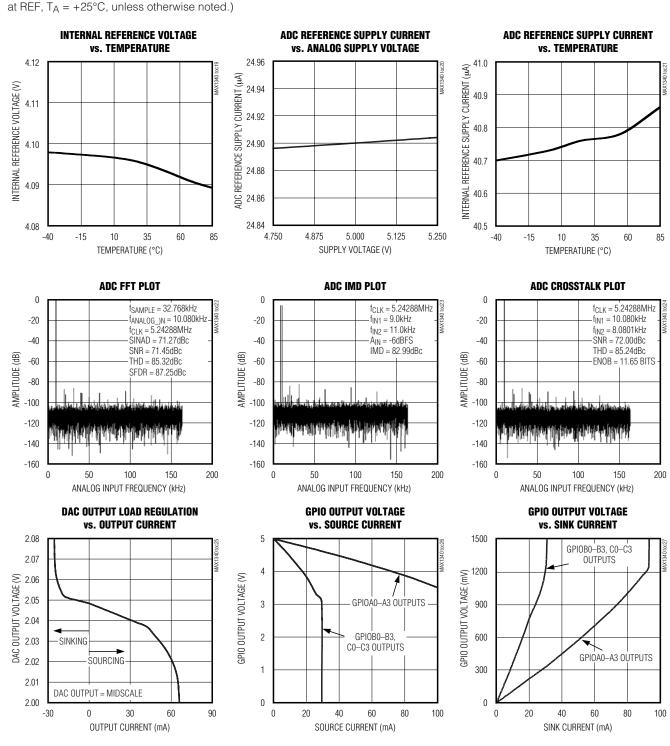

# (AVDD = DVDD = 5V, external VREF = 4.096V, fCLK = 3.6MHz (50% duty cycle), fSAMPLE = 225ksps, CLOAD = 50pF, 0.1µF capacitor

**Typical Operating Characteristics (continued)**

///XI///

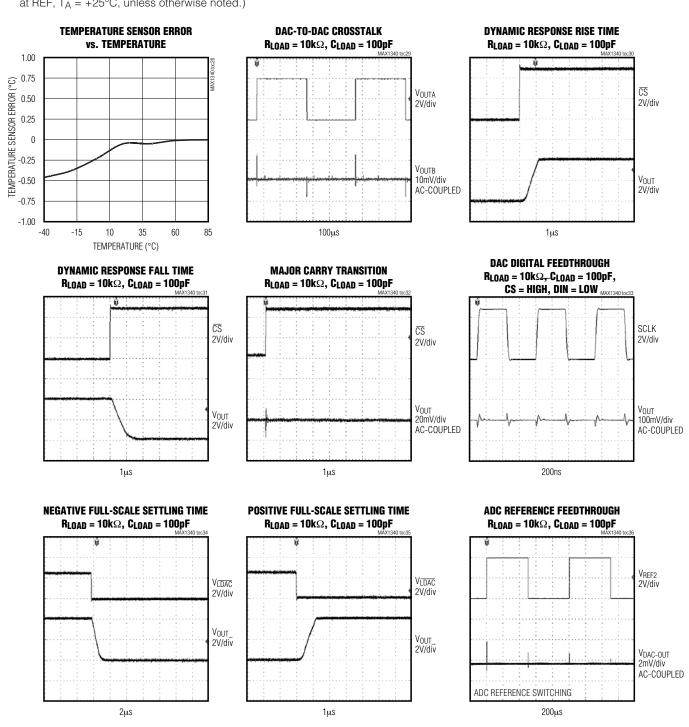

**Typical Operating Characteristics (continued)** (AV<sub>DD</sub> = DV<sub>DD</sub> = 5V, external V<sub>REF</sub> = 4.096V, f<sub>CLK</sub> = 3.6MHz (50% duty cycle), f<sub>SAMPLE</sub> = 225ksps, C<sub>LOAD</sub> = 50pF, 0.1µF capacitor at REF, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Description**

| MAX1340                | MAX1342           | MAX1346                           | MAX1348           | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                            |

|------------------------|-------------------|-----------------------------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 16–19,<br>24, 25 | 16–19             | 1, 2, 16–19,<br>24, 25, 31,<br>34 | 16–19, 31,<br>34  | D.C.             | Do Not Connect. Do not connect to this pin.                                                                                                                                                                                                                                                                                                         |

| 3                      | 3                 | 3                                 | 3                 | EOC              | Active-Low End-of-Conversion Output. Data is valid after the falling edge of EOC.                                                                                                                                                                                                                                                                   |

| 4                      | 4                 | 4                                 | 4                 | DV <sub>DD</sub> | Digital Positive Power Input. Bypass DV <sub>DD</sub> to DGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                               |

| 5                      | 5                 | 5                                 | 5                 | DGND             | Digital Ground. Connect DGND to AGND.                                                                                                                                                                                                                                                                                                               |

| 6                      | 6                 | 6                                 | 6                 | DOUT             | Serial Data Output. Data is clocked out on the falling edge of the SCLK clock in clock modes 00, 01, and 10. Data is clocked out on the rising edge of the SCLK clock in clock mode 11. High impedance when $\overline{\text{CS}}$ is high.                                                                                                         |

| 7                      | 7                 | 7                                 | 7                 | SCLK             | Serial Clock Input. Clocks data in and out of the serial interface. (Duty cycle must be 40% to 60%.) See Table 4 for details on programming the clock mode.                                                                                                                                                                                         |

| 8                      | 8                 | 8                                 | 8                 | DIN              | Serial Data Input. DIN data is latched into the serial interface<br>on the falling edge of SCLK.                                                                                                                                                                                                                                                    |

| 9–12                   | 9–12              | 9–12                              | 9–12              | OUT0–<br>OUT3    | DAC Outputs                                                                                                                                                                                                                                                                                                                                         |

| 13                     | 13                | 13                                | 13                | AV <sub>DD</sub> | Positive Analog Power Input. Bypass $AV_{DD}$ to AGND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                       |

| 14                     | 14                | 14                                | 14                | AGND             | Analog Ground                                                                                                                                                                                                                                                                                                                                       |

| 15, 23, 32,<br>33      | 15, 23, 32,<br>33 | 15, 23, 32,<br>33                 | 15, 23, 32,<br>33 | N.C.             | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                            |

| 20                     | 20                | 20                                | 20                | LDAC             | Active-Low Load DAC. <u>LDAC</u> is an asynchronous active-low input that updates the DAC outputs. Drive <u>LDAC</u> low to make the DAC registers transparent.                                                                                                                                                                                     |

| 21                     | 21                | 21                                | 21                | CS               | Active-Low Chip-Select Input. When $\overline{CS}$ is low, the serial interface is enabled. When $\overline{CS}$ is high, DOUT is high impedance.                                                                                                                                                                                                   |

| 22                     | 22                | 22                                | 22                | RES_SEL          | Reset Select. Selects DAC wake-up mode. Set RES_SEL low to wake up the DAC outputs with a 100k $\Omega$ resistor to GND or set RES_SEL high to wake up the DAC outputs with a 100k $\Omega$ resistor to V <sub>REF</sub> . Set RES_SEL high to power up the DAC input register to FFFh. Set RES_SEL low to power up the DAC input register to 000h. |

## **Pin Description (continued)**

|           |           |         |         | 1                 |                                                                                                                                                                                                                                                                                                                |

|-----------|-----------|---------|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX1340   | MAX1342   | MAX1346 | MAX1348 | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                       |

| 26        | 26        | 26      | 26      | REF1              | Reference 1 Input. Reference voltage. Leave unconnected to<br>use the internal reference (4.096V). REF1 is the positive<br>reference in ADC external differential reference mode. Bypass<br>REF1 to AGND with a 0.1µF capacitor in external reference<br>mode only. See the <i>ADC/DAC References</i> section. |

| 27–31, 34 | 27–31, 34 |         |         | AIN0-AIN5         | Analog Inputs                                                                                                                                                                                                                                                                                                  |

| 35        | 35        |         |         | REF2/AIN6         | Reference 2 Input/Analog Input Channel 6. See Table 5 for<br>details on programming the setup register. REF2 is the<br>negative reference in the ADC external differential reference<br>mode.                                                                                                                  |

| 36        | 36        | _       | _       | CNVST/<br>AIN7    | Active-Low Conversion Start Input/Analog Input 7. See Table 5 for details on programming the setup register.                                                                                                                                                                                                   |

| _         | 1, 2      |         | 1, 2    | GPIOA0,<br>GPIOA1 | General-Purpose I/O A0, A1. GPIOA0, GPIOA1 can sink and source 15mA.                                                                                                                                                                                                                                           |

| _         | 24, 25    | _       | 24, 25  | GPIOC0,<br>GPIOC1 | General-Purpose I/O C0, C1. GPIOC0, GPIOC1 can sink 4mA and source 2mA.                                                                                                                                                                                                                                        |

| —         | _         | 27–30   | 27–30   | AIN0-AIN3         | Analog Inputs                                                                                                                                                                                                                                                                                                  |

| _         |           | 35      | 35      | REF2              | Reference 2 Input. See Table 5 for details on programming the setup register. REF2 is the negative reference in the ADC external differential reference mode.                                                                                                                                                  |

| _         | _         | 36      | 36      | CNVST             | Active-Low Conversion Start Input. See Table 5 details on programming the setup register.                                                                                                                                                                                                                      |

|           | —         | _       | _       | EP                | Exposed Paddle. Must be externally connected to AGND. Do not use as a ground connect.                                                                                                                                                                                                                          |

## **Detailed Description**

The MAX1340/MAX1342/MAX1346/MAX1348 integrate a multichannel 12-bit ADC, and a quad 12-bit DAC in a single IC. The devices also include a temperature sensor and configurable GPIOs with a 25MHz SPI-/QSPI-/MICROWIRE-compatible serial interface. The ADC is available in a 4 or an 8 input-channel version. The four DAC outputs settle within 2.0µs, and the ADC has a 225ksps conversion rate.

All devices include an internal reference (4.096V) providing a well-regulated, low-noise reference for both the ADC and DAC. Programmable reference modes for the ADC and DAC allow the use of an internal reference, an external reference, or a combination of both. Features such as an internal ±1°C accurate temperature sensor, FIFO, scan modes, programmable internal or external clock modes, data averaging, and AutoShutdown allow users to minimize both power consumption and processor requirements. The low glitch energy (4nV•s) and low digital feedthrough (0.5nV•s) of the integrated quad DACs make these devices ideal for digital control of fast-response closed-loop systems.

The devices are guaranteed to operate with a supply voltage from +4.75V to +5.25V. The devices consume 2.5mA at 225ksps throughput, only 22 $\mu$ A at 1ksps throughput, and under 0.2 $\mu$ A in the shutdown mode. The MAX1342/MAX1348 offer four GPIOs that can be configured as inputs or outputs.

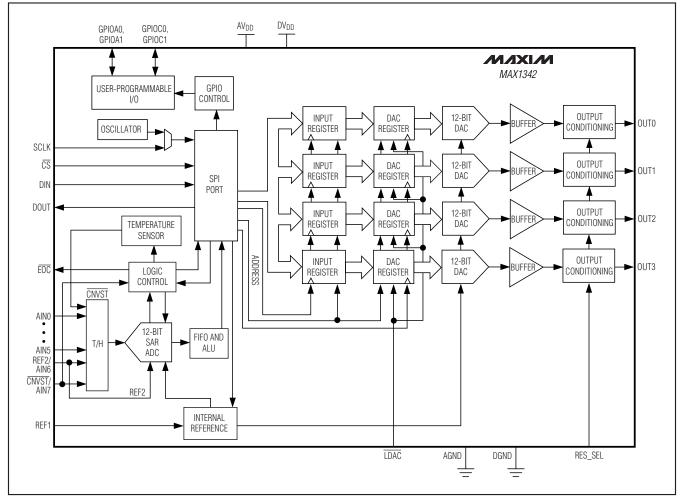

Figure 1 shows the MAX1342 functional diagram. The MAX1342/MAX1348 only include the GPIO A0, A1, GPIO C0, C1 blocks. The MAX1340/MAX1346 exclude the GPIOs. The output-conditioning circuitry takes the internal parallel data bus and converts it to a serial data format at DOUT, with the appropriate wake-up timing. The arithmetic logic unit (ALU) performs the averaging function.

## **SPI-Compatible Serial Interface**

The MAX1340/MAX1342/MAX1346/MAX1348 feature a serial interface that is compatible with SPI and MICROWIRE devices. For SPI, ensure the SPI bus master (typically a microcontroller ( $\mu$ C)) runs in master mode so that it generates the serial clock signal. Select the SCLK frequency of 25MHz or less, and set the clock polarity (CPOL) and phase (CPHA) in the  $\mu$ C control registers to the same value. The MAX1340/MAX1342/MAX1346/MAX1348 operate with SCLK idling high or low, and thus operate with CPOL = CPHA = 0 or CPOL = CPHA = 1. Set  $\overline{CS}$  low to latch any input data

at DIN on the falling edge of SCLK. Output data at DOUT is updated on the falling edge of SCLK in clock modes 00, 01, and 10. Output data at DOUT is updated on the rising edge of SCLK in clock mode 11. See Figures 6–11. Bipolar true-differential results and temperature-sensor results are available in two's complement format, while all other results are in binary.

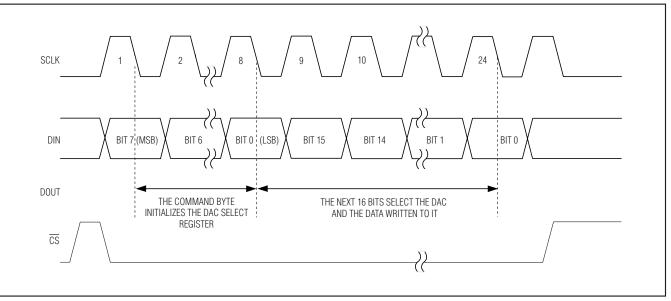

A high-to-low transition on  $\overline{CS}$  initiates the data-input operation. Serial communications to the ADC always begin with an 8-bit command byte (MSB first) loaded from DIN. The command byte and the subsequent data bytes are clocked from DIN into the serial interface on the falling edge of SCLK. The serial-interface and fastinterface circuitry is common to the ADC, DAC, and GPIO sections. The content of the command byte determines whether the SPI port should expect 8, 16, or 24 bits and whether the data is intended for the ADC, DAC, or GPIOs (if applicable). See Table 1. Driving  $\overline{CS}$ high resets the serial interface.

The conversion register controls ADC channel selection, ADC scan mode, and temperature-measurement requests. See Table 4 for information on writing to the conversion register. The setup register controls the clock mode, reference, and unipolar/bipolar ADC configuration. Use a second byte, following the first, to write to the unipolar-mode or bipolar-mode registers. See Table 5 for details of the setup register and see Tables 6, 7, and 8 for setting the unipolar- and bipolarmode registers. Hold  $\overline{CS}$  low between the command byte and the second and third byte. The ADC averaging register is specific to the ADC. See Table 9 to address that register. Table 11 shows the details of the reset register.

Begin a write to the DAC by writing 0001XXXX as a command byte. The last 4 bits of this command byte are don't-care bits. Write another 2 bytes (holding  $\overline{CS}$  low) to the DAC interface register following the command byte to select the appropriate DAC and the data to be written to it. See the *DAC Serial Interface* section and Tables 10, 17, and 18.

Write to the GPIOs (if applicable) by issuing a command byte to the appropriate register. Writing to the MAX1342/MAX1348 GPIOs requires 1 additional byte following the command byte. See Tables 12–16 for details on GPIO configuration, writes, and reads. See the *GPIO Command* section. Command bytes written to the GPIOs on devices without GPIOs are ignored.

Figure 1. MAX1342 Functional Diagram

| REGISTER NAME    | BIT 7 | BIT 6 | BIT 5  | BIT 4  | BIT 3   | BIT 2          | BIT 1    | BIT 0           |

|------------------|-------|-------|--------|--------|---------|----------------|----------|-----------------|

| Conversion*      | 1     | Х     | CHSEL2 | CHSEL1 | CHSEL0  | SCAN1          | SCAN0    | TEMP            |

| Setup            | 0     | 1     | CKSEL1 | CKSEL0 | REFSEL1 | <b>REFSEL0</b> | DIFFSEL1 | <b>DIFFSEL0</b> |

| ADC Averaging    | 0     | 0     | 1      | AVGON  | NAVG1   | NAVG0          | NSCAN1   | NSCAN0          |

| DAC Select       | 0     | 0     | 0      | 1      | Х       | Х              | Х        | Х               |

| Reset            | 0     | 0     | 0      | 0      | 1       | RESET          | SLOW     | FBGON           |

| GPIO Configure** | 0     | 0     | 0      | 0      | 0       | 0              | 1        | 1               |

| GPIO Write**     | 0     | 0     | 0      | 0      | 0       | 0              | 1        | 0               |

| GPIO Read**      | 0     | 0     | 0      | 0      | 0       | 0              | 0        | 1               |

| No Operation     | 0     | 0     | 0      | 0      | 0       | 0              | 0        | 0               |

| X - Don't caro   |       |       |        | 1      |         |                |          | 1               |

## Table 1. Command Byte (MSB First)

X = Don't care.

\*CHESL2 bit is only valid on the MAX1340/MAX1342. Set CHSEL2 to zero on the MAX1346/MAX1348. \*\*Only applicable on the MAX1342/MAX1348.

## Power-Up Default State

The MAX1340/MAX1342/MAX1346/MAX1348 power up with all blocks in shutdown (including the reference). All registers power up in state 0000000, except for the setup register and the DAC input register. The setup register powers up at 0010 1000 with CKSEL1 = 1 and REFSEL1 = 1. The DAC input register powers up to FFFh when RES\_SEL is high and powers up to 000h when RES\_SEL is low.

## 12-Bit ADC

The MAX1340/MAX1342/MAX1346/MAX1348 ADCs use a fully differential successive-approximation register (SAR) conversion technique and on-chip track-andhold (T/H) circuitry to convert temperature and voltage signals into 12-bit digital results. The analog inputs accept both single-ended and differential input signals. Single-ended signals are converted using a unipolar transfer function, and differential signals are converted using a selectable bipolar or unipolar transfer function. See the *ADC Transfer Functions* section for more data.

## ADC Clock Modes

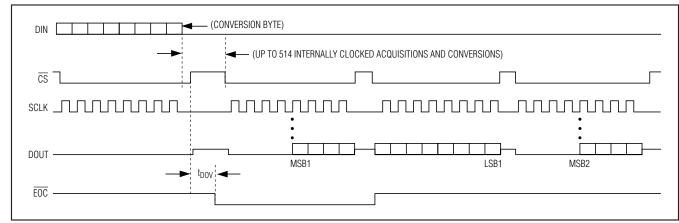

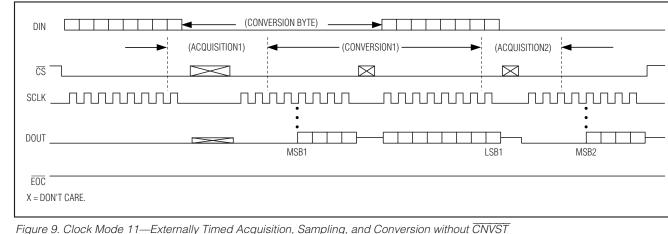

When addressing the setup, register bits 5 and 4 of the command byte (CKSEL1 and CKSEL0, respectively) control the ADC clock modes. See Table 5. Choose between four different clock modes for various ways to start a conversion and determine whether the acquisitions are internally or externally timed. Select clock mode 00 to configure CNVST/AIN\_ to act as a conversion start and use it to request internally timed conversions, without tying up the serial bus. In clock mode 01, use CNVST to request conversions one channel at a time, thereby controlling the sampling speed without tying up the serial bus. Request and start internally

timed conversions through the serial interface by writing to the conversion register in the default clock mode, 10. Use clock mode 11 with SCLK up to 3.6MHz for externally timed acquisitions to achieve sampling rates up to 225ksps. Clock mode 11 disables scanning and averaging. See Figures 6–9 for timing specifications on how to begin a conversion.

These devices feature an active-low, end-of-conversion output. EOC goes low when the ADC completes the last requested operation and is waiting for the next command byte. EOC goes high when CS or CNVST go low. EOC is always high in clock mode 11.

## Single-Ended or Differential Conversions

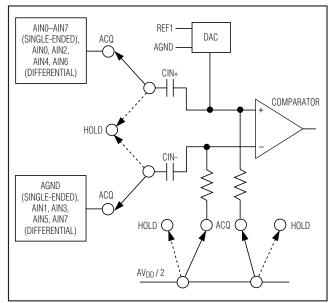

The MAX1340/MAX1342/MAX1346/MAX1348 use a fully differential ADC for all conversions. When a pair of inputs are connected as a differential pair, each input is connected to the ADC. When configured in single-ended mode, the positive input is the single-ended channel and the negative input is referred to AGND. See Figure 2.

In differential mode, the T/H samples the difference between two analog inputs, eliminating common-mode DC offsets and noise. IN+ and IN- are selected from the following pairs: AIN0/AIN1, AIN2/AIN3, AIN4/AIN5, AIN6/AIN7. AIN0–AIN3 are available on all devices. AIN0–AIN7 are available on the MAX1340/MAX1342. See Tables 5–8 for more details on configuring the inputs. For the inputs that are configurable as CNVST, REF2, and an analog input, only one function can be used at a time.

## Unipolar or Bipolar Conversions

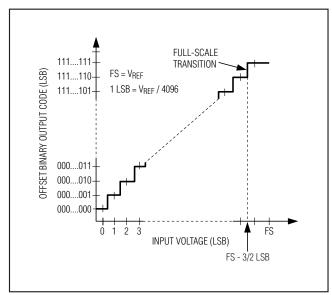

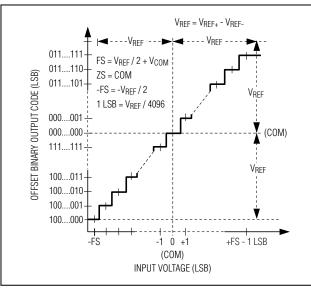

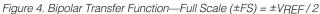

Address the unipolar- and bipolar-mode registers through the setup register (bits 1 and 0). See Table 5 for

the setup register. See Figures 3 and 4 for the transferfunction graphs. Program a pair of analog inputs for differential operation by writing a one to the appropriate bit of the bipolar- or unipolar-mode register. Unipolar mode sets the differential input range from 0 to V<sub>REF1</sub>. A negative differential analog input in unipolar mode causes the digital output code to be zero. Selecting bipolar mode sets the differential input range to  $\pm$ V<sub>REF1</sub>/2. The digital output code is binary in unipolar mode and two's complement in bipolar mode.

In single-ended mode, the MAX1340/MAX1342/ MAX1346/MAX1348 always operate in unipolar mode. The analog inputs are internally referenced to AGND with a full-scale input range from 0 to the selected reference voltage.

## Analog Input (T/H)

The equivalent circuit of Figure 2 shows the ADC input architecture of the MAX1340/MAX1342/MAX1346/ MAX1348. In track mode, a positive input capacitor is connected to AIN0–AIN7 in single-ended mode and AIN0, AIN2, AIN4, and AIN6 in differential mode. A negative input capacitor is connected to AGND in singleended mode or AIN1, AIN3, AIN5, and AIN7 in differential mode. For external T/H timing, use clock mode 01. After the T/H enters hold mode, the difference between the sampled positive and negative input voltages is converted. The input capacitance charging rate determines the time required for the T/H to acquire an input signal. If the input signal's source impedance is high, the required acquisition time lengthens.

Figure 2. Equivalent Input Circuit

Any source impedance below  $300\Omega$  does not significantly affect the ADC's AC performance. A high-impedance source can be accommodated either by lengthening t<sub>ACQ</sub> (only in clock mode 01) or by placing a 1µF capacitor between the positive and negative analog inputs. The combination of the analog-input source impedance and the capacitance at the analog input creates an RC filter that limits the analog input bandwidth.

## Input Bandwidth

The ADC's input-tracking circuitry has a 1MHz small-signal bandwidth, making it is possible to digitize highspeed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. Anti-alias prefiltering of the input signals is necessary to avoid high-frequency signals aliasing into the frequency band of interest.

## **Analog-Input Protection**

Internal electrostatic-discharge (ESD) protection diodes clamp all analog inputs to  $AV_{DD}$  and AGND, allowing the inputs to swing from (AGND - 0.3V) to ( $AV_{DD}$  + 0.3V) without damage. However, for accurate conversions near full scale, the inputs must not exceed  $AV_{DD}$  by more than 50mV or be lower than AGND by 50mV. If an analog input voltage exceeds the supplies, limit the input current to 2mA.

### Internal FIFO

The MAX1340/MAX1342/MAX1346/MAX1348 contain a first-in/first-out (FIFO) buffer that holds up to 16 ADC results plus one temperature result. The internal FIFO allows the ADC to process and store multiple internally clocked conversions and a temperature measurement without being serviced by the serial bus.

If the FIFO is filled and further conversions are requested without reading from the FIFO, the oldest ADC results are overwritten by the new ADC results. Each result contains 2 bytes, with the MSB preceded by four leading zeros. After each falling edge of  $\overline{CS}$ , the oldest available pair of bytes of data is available at DOUT, MSB first. When the FIFO is empty, DOUT is zero.

The first 2 bytes of data read out after a temperature measurement always contain the 12-bit temperature result, preceded by four leading zeros, MSB first. If another temperature measurement is performed before the first temperature result is read out, the old measurement is overwritten by the new result. Temperature results are in degrees Celsius (two's complement), at a resolution of 8 LSB per degree. See the *Temperature Measurements* section for details on converting the digital code to a temperature.

## 12-Bit DAC

In addition to the 12-bit ADC, the MAX1340/MAX1342/ MAX1346/MAX1348 also include four voltage-output, 12-bit, monotonic DACs with less than 4 LSB integral nonlinearity error and less than 1 LSB differential nonlinearity error. Each DAC has a 2µs settling time and ultralow glitch energy (4nV•s). The 12-bit DAC code is unipolar binary with 1 LSB = V<sub>REF</sub> / 4096.

## DAC Digital Interface

Figure 1 shows the functional diagram of the MAX1342. The shift register converts a serial 16-bit word to parallel data for each input register operating with a clock rate up to 25MHz. The SPI-compatible digital interface to the shift register consists of  $\overline{CS}$ , SCLK, DIN, and DOUT. Serial data at DIN is loaded on the falling edge of SCLK. Pull  $\overline{CS}$  low to begin a write sequence. Begin a write to the DAC by writing 0001XXXX as a command byte. The last 4 bits of the DAC select register are don't-care bits. See Table 10. Write another 2 bytes to the DAC interface register following the command byte to select the appropriate DAC and the data to be written to it. See Tables 17 and 18.

The four double-buffered DACs include an input and a DAC register. The input registers are directly connected to the shift register and hold the result of the most recent write operation. The four 12-bit DAC registers hold the current output code for the respective DAC. Data can be transferred from the input registers to the DAC registers by pulling LDAC low or by writing the appropriate DAC command sequence at DIN. See Table 17. The outputs of the DACs are buffered through four rail-to-rail op amps.

The MAX1340/MAX1342/MAX1346/MAX1348 DAC output-voltage range is based on the internal reference or an external reference. Write to the setup register (see Table 5) to program the reference. If using an external voltage reference, bypass REF1 with a 0.1µF capacitor to AGND. The internal reference is 4.096V. When using an external reference, the voltage range is 0.7V to AV<sub>DD</sub>.

### DAC Transfer Function

See Table 2 for various analog outputs from the DAC.

## DAC Power-On Wake-Up Modes

The state of the RES\_SEL input determines the wake-up state of the DAC outputs. Connect RES\_SEL to AVDD or AGND upon power-up to be sure the DAC outputs wake up to a known state. Connect RES\_SEL to AGND to wake up all DAC outputs at 000h. While RES\_SEL is low, the 100k $\Omega$  internal resistor pulls the DAC outputs to AGND and the output buffers are powered down. Connect RES\_SEL to AVDD to wake up all DAC outputs at FFFh. While RES\_SEL is high, the 100k $\Omega$  pullup resistor pulls the DAC outputs to VREF1 and the output buffers are powered down.

## DAC Power-Up Modes

See Table 18 for a description of the DAC power-up and power-down modes.

## **GPIO**s

In addition to the internal ADC and DAC, the MAX1342/MAX1348 also provide four GPIO channels, GPIOA0, GPIOA1, GPIOC0, GPIOC1. Read and write to the GPIOs as detailed in Table 1 and Tables 12–16. Also, see the *GPIO Command* section. See Figures 11 and 12 for GPIO timing.

Write to the GPIOs by writing a command byte to the GPIO command register. Write a single data byte to the MAX1342/MAX1348 following the command byte.

## Table 2. DAC Output Code Table

| DAC  | CONTEN | ITS  |                                                                                   |

|------|--------|------|-----------------------------------------------------------------------------------|

| MSB  |        | LSB  | ANALOG OUTPUT                                                                     |

| 1111 | 1111   | 1111 | $+V_{REF}\left(\frac{4095}{4096}\right)$                                          |

| 1000 | 0000   | 0001 | $+ V_{REF} \left(\frac{2049}{4096}\right)$                                        |

| 1000 | 0000   | 0000 | $+ V_{REF} \left( \frac{2048}{4096} \right) = \left( \frac{+ V_{REF}}{2} \right)$ |

| 0111 | 0111   | 0111 | $+ V_{\text{REF}} \left(\frac{2047}{4096}\right)$                                 |

| 0000 | 0000   | 0001 | $+V_{\text{REF}}\left(\frac{1}{4096}\right)$                                      |

| 0000 | 0000   | 0000 | 0                                                                                 |

The GPIOs can sink and source current. The MAX1342/MAX1348 GPIOA0 and GPIOA1 can sink and source up to 15mA. GPIOC0 and GPIOC1 can sink 4mA and source 2mA. See Table 3.

## **Clock Modes**

## Internal Clock

The MAX1340/MAX1342/MAX1346/MAX1348 can operate from an internal oscillator. The internal oscillator is active in clock modes 00, 01, and 10. Figures 6, 7, and 8 show how to start an ADC conversion in the three internally timed conversion modes.

Read out the data at clock speeds up to 25MHz through the SPI interface.

**External Clock** Set CKSEL1 and CKSEL0 in the setup register to 11 to set up the interface for external clock mode 11. See Table 5. Pulse SCLK at speeds from 0.1MHz to 3.6MHz. Write to SCLK with a 40% to 60% duty cycle. The SCLK frequency controls the conversion timing. See Figure 9 for clock mode 11 timing. See the *ADC Conversions in Clock Mode 11* section.

## **ADC/DAC** References

Address the reference through the setup register, bits 3 and 2. See Table 5. Following a wake-up delay, set REFSEL[1:0] = 00 to program both the ADC and DAC for internal reference use. Set REFSEL[1:0] = 10 to program the ADC for internal reference use without a wake-up delay. Set REFSEL[1:0] = 10 to program the DAC for external reference, REF1. When using REF1 or REF2/AIN\_ in external reference, connect a  $0.1\mu$ F capacitor to AGND. Set REFSEL[1:0] = 01 to program the ADC and DAC for external-reference mode. The DAC uses REF1 as its external reference, while the ADC uses REF2 as its external reference. Set REFSEL[1:0] = 11 to program the ADC for external differential reference mode. REF1 is the positive reference

# Table 3. GPIO Maximum Sink/Source Current

|         | MAX1342/MAX1348        |                        |  |  |

|---------|------------------------|------------------------|--|--|

| CURRENT | GPIOA0, GPIOA1<br>(mA) | GPIOC0, GPIOC1<br>(mA) |  |  |

| Sink    | 15                     | 4                      |  |  |

| Source  | 15                     | 2                      |  |  |

and REF2 is the negative reference in the ADC external

differential mode.

When REFSEL[1:0] = 00 or 10, REF2/AIN\_ functions as an analog input channel. When REFSEL[1:0] = 01 or 11, REF2/AIN\_ functions as the device's negative reference.

## **Temperature Measurements**

Issue a command byte setting bit 0 of the conversion register to one to take a temperature measurement. See Table 4. The MAX1340/MAX1342/MAX1346/MAX1348 perform temperature measurements with an internal diode-connected transistor. The diode bias current changes from  $68\mu$ A to  $4\mu$ A to produce a temperature-dependent bias voltage difference. The second conversion result at  $4\mu$ A is subtracted from the first at  $68\mu$ A to calculate a digital value that is proportional to absolute temperature. The output data appearing at DOUT is the digital code above, minus an offset to adjust from Kelvin to Celsius.

The reference voltage used for the temperature measurements is always derived from the internal reference source to ensure that 1 LSB corresponds to 1/8 of a degree Celsius. On every scan where a temperature measurement is requested, the temperature conversion is carried out first. The first 2 bytes of data read from the FIFO contain the result of the temperature measurement. If another temperature measurement is performed before the first temperature result is read out, the old measurement is overwritten by the new result. Temperature results are in degrees Celsius (two's complement). See the *Applications Information* section for information on how to perform temperature measurements in each clock mode.

## **Register Descriptions**

The MAX1340/MAX1342/MAX1346/MAX1348 communicate between the internal registers and the external circuitry through the SPI-compatible serial interface. Table 1 details the command byte, the registers, and the bit names. Tables 4–12 show the various functions within the conversion register, setup register, unipolar-mode register, bipolar-mode register, ADC averaging register, DAC select register, reset register, and GPIO command register, respectively.

## **Conversion Register**

Select active analog input channels, scan modes, and a single temperature measurement per scan by issuing a command byte to the conversion register. Table 4 details channel selection, the four scan modes, and how to request a temperature measurement. Start a scan by writing to the conversion register when in clock mode 10 or 11, or by applying a low pulse to the CNVST pin when in clock mode 00 or 01. See Figures 6 and 7 for timing specifications for starting a scan with CNVST.

A conversion is not performed if it is requested on a channel or one of the channel pairs that has been configured as CNVST or REF2. For channels configured as differential pairs, the CHSEL0 bit is ignored and the two pins are treated as a single differential channel. For the MAX1346/MAX1348, the CHSEL2 bit must be zero. Channels 4–7 are invalid. Any scans or averages on these channels can cause corrupt data.

Select scan mode 00 or 01 to return one result per single-ended channel and one result per differential pair within the selected scanning range (set by bits 2 and 1, SCAN1 and SCAN0), plus one temperature result if selected. Select scan mode 10 to scan a single input channel numerous times, depending on NSCAN1 and NSCAN0 in the ADC averaging register (Table 9). Select scan mode 11 to return only one result from a single channel.

## Setup Register

Issue a command byte to the setup register to configure the clock, reference, power-down modes, and ADC single-ended/differential modes. Table 5 details the bits in the setup-register command byte. Bits 5 and 4 (CKSEL1 and CKSEL0) control the clock mode, acquisition and sampling, and the conversion start. Bits 3 and 2 (REFSEL1 and REFSEL0) set the device for either internal or external reference. Bits 1 and 0 (DIFFSEL1 and DIFFSEL0) address the ADC unipolar-mode and bipolar-mode registers and configure the analog-input channels for differential operation.

The ADC reference is always on if any of the following conditions are true:

- 1) The FBGON bit is set to one in the reset register.

- 2) At least one DAC output is powered up and REFSEL[1:0] (in the setup register) = 00.

- 3) At least one DAC is powered down through the  $100k\Omega$  to V<sub>REF</sub> and REFSEL[1:0] = 00.

If any of the above conditions exist, the ADC reference is always on, but there is a 188 clock-cycle delay before temperature-sensor measurements begin, if requested.

## Table 4. Conversion Register\*

| BIT<br>NAME | BIT     | FUNCTION                                                                                                                                |

|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| _           | 7 (MSB) | Set to one to select conversion register.                                                                                               |

| Х           | 6       | Don't care.                                                                                                                             |

| CHSEL2      | 5       | Analog-input channel select<br>(MAX1340/MAX1342). Set to 0 on<br>MAX1346/MAX1348.                                                       |

| CHSEL1      | 4       | Analog-input channel select.                                                                                                            |

| CHSEL0      | 3       | Analog-input channel select.                                                                                                            |

| SCAN1       | 2       | Scan-mode select.                                                                                                                       |

| SCAN0       | 1       | Scan-mode select.                                                                                                                       |

| TEMP        | 0 (LSB) | Set to one to take a single temp-<br>erature measurement. The first<br>conversion result of a scan contains<br>temperature information. |

\*See below for bit details.