SBVS012B - DECEMBER 2000 - REVISED OCTOBER 2004

# Miniature, 1W Isolated UNREGULATED DC/DC CONVERTERS

#### **FEATURES**

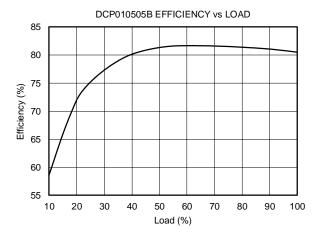

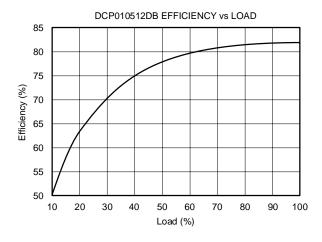

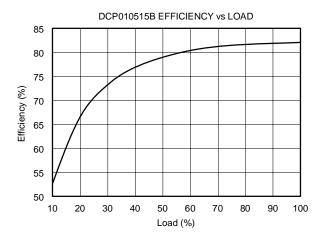

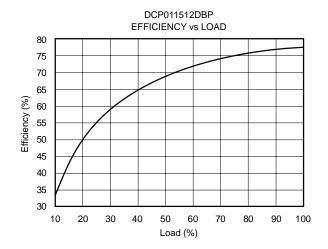

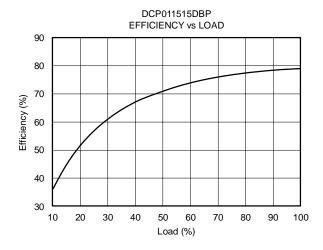

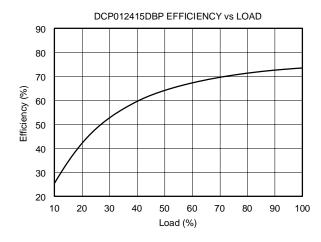

- Up To 85% Efficiency

- Thermal Protection

- Device-to-Device Synchronization

- Short-Circuit Protection

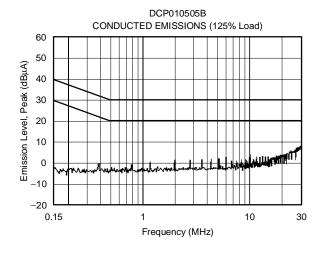

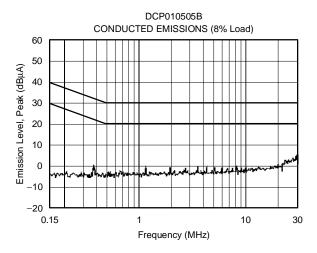

- EN55022 Class B EMC Performance

- UL1950 Recognized Component

- JEDEC DIP-14 and SOP-14 Packages

#### **APPLICATIONS**

- Point-of-Use Power Conversion

- Ground Loop Elimination

- Data Acquisition

- Industrial Control and Instrumentation

- Test Equipment

#### DESCRIPTION

The DCP01B series is a family of 1W, unregulated, isolated DC/DC converters. Requiring a minimum of external components and including on-chip device protection, the DCP01B series provides extra features such as output disable and synchronization of switching frequencies.

The use of a highly-integrated package design results in highly reliable products with a power density of 40W/in<sup>3</sup> (2.4W/cm<sup>3</sup>). This combination of features and small sizes makes the DCP01B suitable for a wide range of applications.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### SBVS012B - DECEMBER 2000 - REVISED OCTOBER 2004

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                 |                     | DCP01B SERIES | UNIT |

|-----------------|---------------------|---------------|------|

|                 | 5V models           | 7             | V    |

| Input voltage   | 15V models          | 18            | V    |

|                 | 24V models          | 29            | V    |

| Storage tempera | iture               | -40 to +125   | °C   |

| Lead temperatur | re (soldering, 10s) | +270          | °C   |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

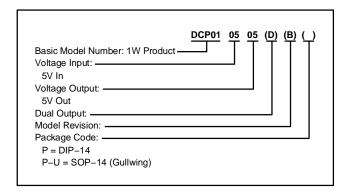

#### SUPPLEMENTAL ORDERING INFORMATION

#### ORDERING INFORMATION(1)

| PRODUCT       | PACKAGE-LEAD          | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA |

|---------------|-----------------------|-----------------------|-----------------------------------|--------------------|--------------------------------|--------------------|

| SINGLE VOLTAG | E(3)                  |                       |                                   |                    |                                |                    |

| DODOMOFOE     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010505BP        | DCP010505BP                    | Rails              |

| DCP010505     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010505BP-U      | DCP010505BP-U/700              | Tape and Reel      |

| DOD040540     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010512BP        | DCP010512BP                    | Rails              |

| DCP010512     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010512BP-U      | DCP010512BP-U/700              | Tape and Reel      |

| DOD040545     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010515BP        | DCP010515BP                    | Rails              |

| DCP010515     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010515BP-U      | DCP010515BP-U/700              | Tape and Reel      |

| DOD040405     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP012405BP        | DCP012405BP                    | Rails              |

| DCP012405     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP012405BP-U      | DCP012405BP-U/700              | Tape and Reel      |

| DUAL VOLTAGE  | (3)                   |                       | 1                                 |                    |                                |                    |

| DCP010505 -   | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010505DBP       | DCP010505DBP                   | Rails              |

|               | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010505DBP-U     | DCP010505DBP-U/700             | Tape and Reel      |

|               | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010512DBP       | DCP010512DBP                   | Rails              |

| DCP010512     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010512DBP-U     | DCP010512DBP-U/700             | Tape and Reel      |

| DOD040545     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP010515DBP       | DCP010515DBP                   | Rails              |

| DCP010515     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP010515DBP-U     | DCP010515DBP-U/700             | Tape and Reel      |

| DOD044540     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP011512DBP       | DCP011512DBP                   | Rails              |

| DCP011512     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP011512DBP-U     | DCP011512DBP-U/700             | Tape and Reel      |

| DOD044545     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP011515DBP       | DCP011515DBP                   | Rails              |

| DCP011515     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP011515DBP-U     | DCP011515DBP-U/700             | Tape and Reel      |

| DCD040445     | DIP-14                | NVA                   | -40°C to +100°C                   | DCP012415DBP       | DCP012415DBP                   | Rails              |

| DCP012415     | SOP-14 <sup>(4)</sup> | DUA                   | -40°C to +100°C                   | DCP012415DBP-U     | DCP012415DBP-U/700             | Tape and Reel      |

<sup>(1)</sup> All devices also available in tray quatities. For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or refer to our web site at www.ti.com.

<sup>(2)</sup> Models with a (/) are available only in Tape and Reel in the quantities indicated (for example, /700 indicates 700 devices per reel). Ordering 700 pieces of "DCP010505BP-U/700" will get a single 700-piece Tape and Reel.

<sup>(3)</sup> Single voltage versions have six active pins; dual voltage versions have seven active pins.

<sup>(4)</sup> SOP package is gullwing surface-mount.

## **ELECTRICAL CHARACTERISTICS**

At  $T_A$  = +25°C,  $V_S$  = nominal,  $C_{IN}$  = 2.2 $\mu$ F, and  $C_{OUT}$  = 0.1 $\mu$ F, unless otherwise noted.

|                                               |                                                                                                                                                                                      | DCP01B SERIE | ES .              |                                  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|----------------------------------|

| PARAMETER                                     | TEST CONDITIONS                                                                                                                                                                      | MIN TYP      | MAX               | UNITS                            |

| Output                                        |                                                                                                                                                                                      | •            |                   |                                  |

| Power                                         | 100% full load                                                                                                                                                                       | 0.97         |                   | W                                |

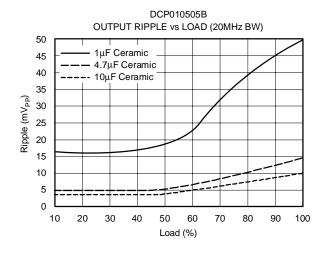

| Ripple                                        | O/P capacitor = 1μF, 50% load                                                                                                                                                        | 20           |                   | $mV_{PP}$                        |

|                                               | Room to cold                                                                                                                                                                         | 0.046        |                   | %/°C                             |

| Voltage vs Temperature                        | Room to hot                                                                                                                                                                          | 0.016        |                   | %/°C                             |

| Input                                         | •                                                                                                                                                                                    |              |                   |                                  |

| Voltage range on V <sub>S</sub>               |                                                                                                                                                                                      | -10          | +10               | %                                |

| Isolation                                     |                                                                                                                                                                                      |              |                   |                                  |

|                                               | 1s flash test                                                                                                                                                                        | 1            |                   | kVrms                            |

| Voltage                                       | 60s test, UL1950 <sup>(1)</sup>                                                                                                                                                      | 1            |                   | kVrms                            |

| Line Regulation                               | •                                                                                                                                                                                    |              |                   |                                  |

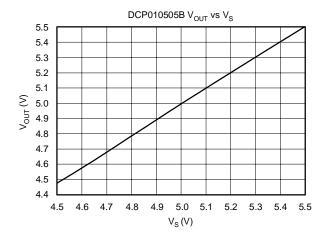

| Voltage Source (V <sub>S</sub> )              | $\begin{aligned} & \text{Minimum } V_S \leq I_O \text{ constant} \leq \text{typical } V_S \\ & \text{Typical } V_S \leq I_O \text{ constant} \leq \text{maximum } V_S \end{aligned}$ | 1            | 15 <sup>(2)</sup> | %<br>change<br>of V <sub>S</sub> |

| Switching/Synchronization                     | •                                                                                                                                                                                    |              |                   |                                  |

| Oscillator frequency (f <sub>OSC</sub> )      | Switcing frequency = f <sub>OSC</sub> /2                                                                                                                                             | 800          |                   | kHz                              |

| Sync input low                                |                                                                                                                                                                                      |              | 0.4               | V                                |

| Sync input current                            | V <sub>SYNC</sub> = +2V                                                                                                                                                              | 75           |                   | μΑ                               |

| Disable time                                  |                                                                                                                                                                                      | 2            |                   | μs                               |

| Capacitance loading on SYNC <sub>IN</sub> pin | External                                                                                                                                                                             |              | 3                 | pF                               |

| Reliability                                   | •                                                                                                                                                                                    |              |                   |                                  |

| Demonstrated                                  | MSL 3–(U) versions T <sub>A</sub> = +55°C                                                                                                                                            | -40          | +70               | °C                               |

| Thermal Shutdown                              |                                                                                                                                                                                      |              |                   |                                  |

| IC temperature at shutdown                    |                                                                                                                                                                                      | +150         |                   | °C                               |

| Shutdown current                              |                                                                                                                                                                                      | 3            |                   | mA                               |

| Temperature Range                             |                                                                                                                                                                                      | •            |                   |                                  |

| Operating                                     |                                                                                                                                                                                      | -40          | +100              | °C                               |

<sup>(1)</sup> During UL1950 recognition tests only.

## **ELECTRICAL CHARACTERISTICS PER DEVICE**

At  $T_A$  = +25°C,  $V_S$  = nominal,  $C_{IN}$  = 2.2 $\mu$ F, and  $C_{OUT}$  = 0.1 $\mu$ F, unless otherwise noted.

|             | INPL           | INPUT VOLTAGE OUTPUT VOLTAGE (V) (V) |      | LOAD REGULATION<br>(%)                    |                         | NO LOAD<br>CURRENT<br>(mA) | EFFICIENCY (%)      | BARRIER<br>CAPACITANCE<br>(pF) |         |                  |                                        |

|-------------|----------------|--------------------------------------|------|-------------------------------------------|-------------------------|----------------------------|---------------------|--------------------------------|---------|------------------|----------------------------------------|

|             | V <sub>S</sub> |                                      |      | V <sub>NOM</sub> = V <sub>S</sub> Typical |                         |                            |                     | IQ                             |         | C <sub>ISO</sub> |                                        |

|             |                |                                      |      | 7:                                        | 75% LOAD <sup>(3)</sup> |                            | 10% TO 100% LOAD(4) |                                | 0% LOAD | 100% LOAD        | V <sub>ISO</sub> = 750V <sub>RMS</sub> |

| PRODUCT     | MIN            | TYP                                  | MAX  | MIN                                       | TYP                     | MAX                        | TYP                 | TYP MAX                        |         | TYP              | TYP                                    |

| DCP010505B  | 4.5            | 5                                    | 5.5  | 4.75                                      | 5                       | 5.25                       | 19                  | 31                             | 20      | 80               | 3.6                                    |

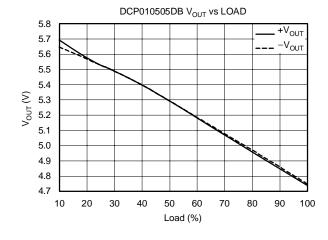

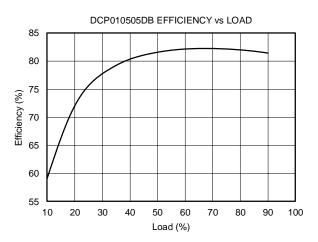

| DCP010505DB | 4.5            | 5                                    | 5.5  | ±4.25                                     | ±5                      | ±5.75                      | 18                  | 32                             | 22      | 81               | 3.8                                    |

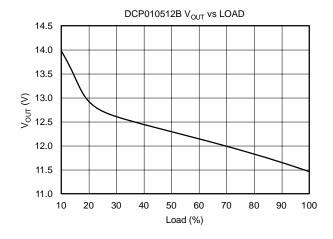

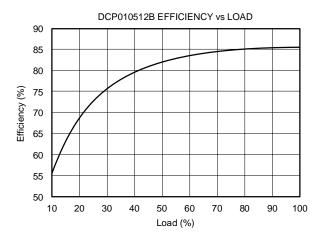

| DCP010512B  | 4.5            | 5                                    | 5.5  | 11.4                                      | 12                      | 12.6                       | 21                  | 38                             | 29      | 85               | 5.1                                    |

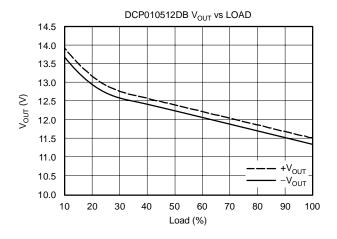

| DCP010512DB | 4.5            | 5                                    | 5.5  | ±11.4                                     | ±12                     | ±12.6                      | 19                  | 37                             | 40      | 82               | 4.0                                    |

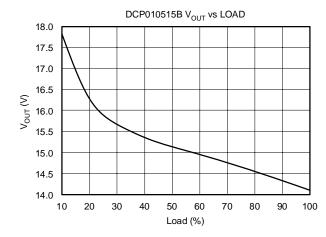

| DCP010515B  | 4.5            | 5                                    | 5.5  | 14.25                                     | 15                      | 15.75                      | 26                  | 42                             | 34      | 82               | 3.8                                    |

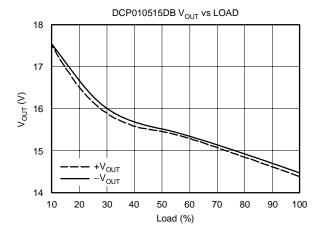

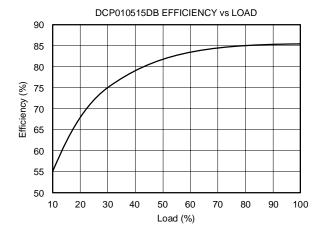

| DCP010515DB | 4.5            | 5                                    | 5.5  | ±14.25                                    | ±15                     | ±15.75                     | 19                  | 41                             | 42      | 85               | 4.7                                    |

| DCP011512DB | 13.5           | 15                                   | 16.5 | ±11.4                                     | ±12                     | ±12.6                      | 11                  | 39                             | 19      | 78               | 2.5                                    |

| DCP011515DB | 13.5           | 15                                   | 16.5 | ±14.25                                    | ±15                     | ±15.75                     | 12                  | 39                             | 20      | 80               | 2.5                                    |

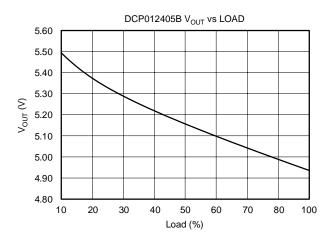

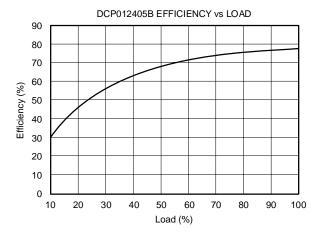

| DCP012405B  | 21.6           | 24                                   | 26.4 | 4.75                                      | 5                       | 5.25                       | 13                  | 23                             | 14      | 77               | 2.5                                    |

| DCP012415DB | 21.6           | 24                                   | 26.4 | ±14.25                                    | ±15                     | ±15.75                     | 10                  | 35                             | 17      | 76               | 3.8                                    |

<sup>(3) 100%</sup> load current = 1W/V<sub>S</sub> typical.

<sup>(2)</sup> Line regulation is measured at constant load current. Line regulation =  $(V_{OUT} \text{ at } I_{OUT} \text{ fixed})/V_S$ . Variation % =  $V_S$  min to  $V_S$  typ,  $V_S$  typ to  $V_S$  max.

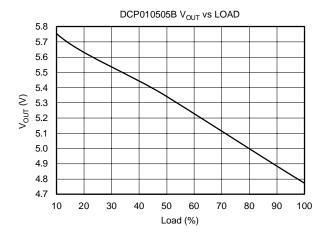

<sup>(4)</sup> Load regulation = (V<sub>OUT</sub> at 10% load – V<sub>OUT</sub> at 100% load)/V<sub>OUT</sub> at 75% load.

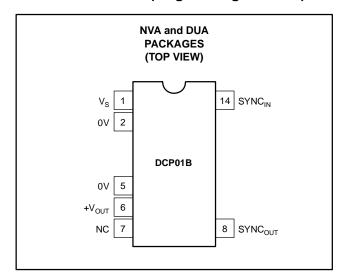

# PIN ASSIGNMENTS (Single Voltage Version)

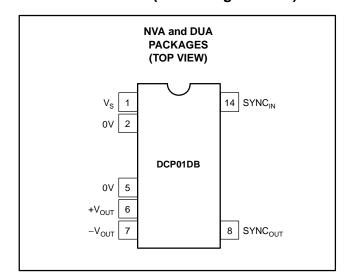

# PIN ASSIGNMENTS (Dual Voltage Version)

# **Terminal Functions (Single Voltage)**

| TERMINAL            |    |     |                                |

|---------------------|----|-----|--------------------------------|

| NAME NO.            |    | I/O | DESCRIPTION                    |

| Vs                  | 1  | - 1 | Voltage input                  |

| 0V                  | 2  | - 1 | Input side common              |

| 0V                  | 5  | 0   | Output side common             |

| +V <sub>OUT</sub>   | 6  | 0   | +Voltage out                   |

| NC                  | 7  |     | Not connected                  |

| SYNC <sub>OUT</sub> | 8  | 0   | Unrectified transformer output |

| SYNC <sub>IN</sub>  | 14 | 1   | Synchronization pin            |

NOTE: I = input and O = output.

# **Terminal Functions (Dual Voltage)**

| TERMINAL            |    |     |                                |

|---------------------|----|-----|--------------------------------|

| NAME NO.            |    | I/O | DESCRIPTION                    |

| Vs                  | 1  | 1   | Voltage input                  |

| 0V                  | 2  | I   | Input side common              |

| 0V                  | 5  | 0   | Output side common             |

| +V <sub>OUT</sub>   | 6  | 0   | +Voltage out                   |

| -V <sub>OUT</sub>   | 7  | 0   | -Voltage out                   |

| SYNC <sub>OUT</sub> | 8  | 0   | Unrectified transformer output |

| SYNC <sub>IN</sub>  | 14 | I   | Synchronization pin            |

NOTE: I = input and O = output.

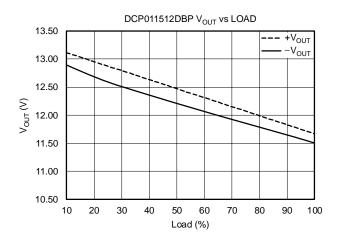

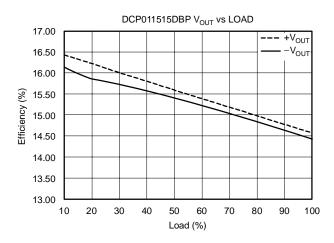

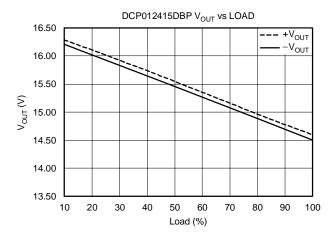

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS (continued)**

# **TYPICAL CHARACTERISTICS (continued)**

# **TYPICAL CHARACTERISTICS (continued)**

#### **FUNCTIONAL DESCRIPTION**

#### **OVERVIEW**

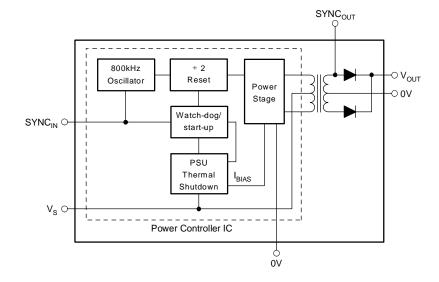

The DCP01B offers up to 1W of unregulated output power with a typical efficiency of up to 85%. This is achieved through highly integrated packaging technology and the implementation of a custom power stage and control IC. The circuit design uses an advanced BiCMOS/DMOS process. For additional information, refer to the application notes located in the DCP01B product folder at www.ti.com.

#### **POWER STAGE**

This uses a push-pull, center-tapped topology switching at 400kHz (divide-by-2 from 800kHz oscillator).

#### **OSCILLATOR AND WATCHDOG**

The onboard 800kHz oscillator generates the switching frequency via a divide-by-2 circuit. The oscillator can be synchronized to other DCP01B circuits or an external source, and is used to minimize system noise.

A watchdog circuit checks the operation of the oscillator circuit. The oscillator can be stopped by pulling the SYNC pin low. The output pins will be tri-stated. This will occur in  $2\mu s$ .

#### THERMAL SHUTDOWN

The DCP01B is protected by a thermal shutdown circuit. If the on-chip temperature exceeds 150°C, the device will shut down. Once the temperature falls below 150°C, normal operation will resume. If the thermal condition continues, operation will randomly cycle on and off. This will continue until the temperature is reduced.

#### **SYNCHRONIZATION**

In the event that more than one DC/DC converter is needed onboard, beat frequencies and other electrical interference can be generated. This is due to the small variations in switching frequencies between the DC/DC converters.

The DCP01B overcomes this by allowing devices to be synchronized to one another. Up to eight devices can be synchronized by connecting the SYNC<sub>IN</sub> pins together, taking care to minimize the stray capacitance. Stray capacitance (> 3pF) will have the effect of reducing the switching frequency, or even stopping the oscillator circuit.

If synchronized devices are used, it should be noted that at startup, all devices will draw maximum current simultaneously. This can cause the input voltage to dip. If it dips below the minimum input voltage (4.5V), the devices may not start up. A  $2.2\mu F$  capacitor should be connected close to the input pins.

If more than eight devices are to be synchronized, it is recommended that the SYNC<sub>IN</sub> pins are driven by an external device. Details are contained in Application Report SBAA035, *External Synchronization of the DCP01/02 Series of DC/DC Converters*, available for download at www.ti.com.

#### CONSTRUCTION

The DCP01B basic construction is the same as standard ICs. There is no substrate within the molded package. The DCP01B is constructed using an IC, rectifier diodes, and a wound magnetic toroid on a leadframe. Since there is no solder within the package, the DCP01B does not require any special PCB assembly processing. This results in an isolated DC/DC converter with inherently high reliability.

#### ADDITIONAL FUNCTIONS

#### DISABLE/ENABLE

The DCP01B can be disabled or enabled by driving the SYNC pin using an open drain CMOS gate. If the SYNC $_{\rm IN}$  pin is pulled low, the DCP01B will be disabled. The disable time depends upon the external loading; the internal disable function is implemented in  $2\mu s$ . Removal of the pull-down will cause the DCP01B to be enabled.

Capacitive loading on the SYNC<sub>IN</sub> pin should be minimized in order to prevent a reduction in the oscillator frequency.

#### **DECOUPLING**

## Ripple Reduction

A high switching frequency of 400kHz allows simple filtering. To reduce ripple, it is recommended that at least a 1µF capacitor is used on  $V_{OUT}$ . Dual outputs should have both the positive and negative buses decoupled to  $V_{OUT}$  ground (pin 5). The required 2.2µF low equivalent series resistance (ESR) ceramic capacitor on the input of the 5V to 15V versions, and the  $\geq$  0.47µF low-ESR ceramic capacitor on the 24V versions help reduce ripple and noise. See Application Bulletin SBVA012, DC-to-DC Converter Noise Reduction, available for download at www.ti.com.

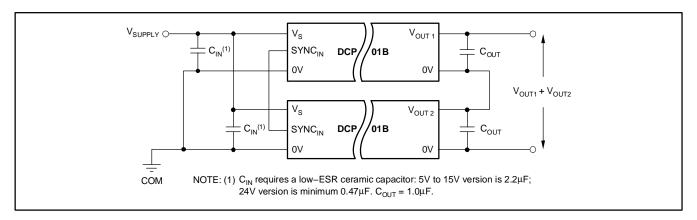

#### Connecting the DCP01B in Series

Multiple DCP01B isolated 1W DC/DC converters can be connected in series to provide nonstandard voltage rails. This is possible by using the floating outputs provided by the DCP01B galvanic isolation.

Connect the positive  $V_{OUT}$  from one DCP01B to the negative  $V_{OUT}$  (0V) of another, as shown in Figure 1. If the SYNC<sub>IN</sub> pins are tied together, the self-synchronization feature of the DCP01B will prevent beat frequencies on the voltage rails. The SYNC<sub>IN</sub> feature of the DCP01B allows easy connection in series, which reduces separate filtering components.

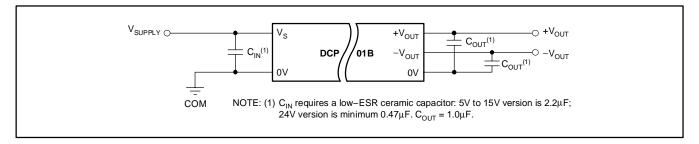

The outputs on dual output DCP01B versions can also be connected in series to provide two times the magnitude of  $V_{OUT}$ , as shown in Figure 2. For example, a dual 15V DCP01B could be connected to provide a 30V rail.

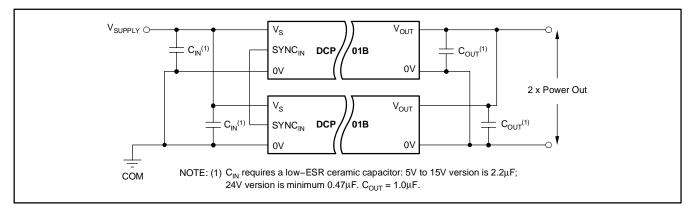

#### Connecting the DCP01B in Parallel

If the output power from one DCP01B is not sufficient, it is possible to parallel the outputs of multiple DCP01B converters (see Figure 3). Again, the SYNC<sub>IN</sub> feature allows easy synchronization to prevent power-rail beat frequencies at no additional filtering cost.

Figure 1. Connecting the DCP01B in Series

Figure 2. Connecting Dual Outputs in Series

Figure 3. Connecting Multiple DCP01Bs in Parallel

#### **APPLICATION INFORMATION**

The DCP01B, DCV01, and DCP02 are three families of miniature DC/DC converters providing an isolated unregulated voltage output. All are fabricated using a CMOS/DMOS process with the DCP01B replacing the familiar DCP01 family that was fabricated from a bipolar process. The DCP02 is essentially an extension of the DCP01B family providing a higher power output with a significantly improved load regulation, and the DCV01 is tested to a higher isolation voltage.

#### TRANSFORMER DRIVE CIRCUIT

Transformer drive transistors have a characteristically low value of transistor on resistance ( $R_{DS}$ ); thus, more power is transferred to the transformer. The transformer drive circuit is limited by the base current available to switch on the power transistors driving the transformer and their characteristic current gain (beta), resulting in a slower turn-on time. Consequently, more power is dissipated within the transistor. This results in a lower overall efficiency, particularly at higher output load currents.

#### **SELF-SYNCHRONIZATION**

The input synchronizations facility (SYNC $_{\rm IN}$ ), allows for easy synchronizing of multiple devices. If two to eight devices (maximum) have their respective SYNC $_{\rm IN}$  pins connected together, then all devices will be synchronized.

Each device has its own onboard oscillator. This is generated by charging a capacitor from a constant current and producing a ramp. When this ramp passes a threshold, an internal switch is activated that discharges the capacitor to a second threshold before the cycle is repeated.

When several devices are connected together, all the internal capacitors are charged simultaneously.

When one device passes its threshold during the charge cycle, it starts the discharge cycle. All the other devices sense this falling voltage and, likewise, initiate a discharge cycle so that all devices discharge together. A subsequent charge cycle is only restarted when the last device has finished its discharge cycle.

#### OPTIMIZING PERFORMANCE

Optimum performance can only be achieved if the device is correctly supported. By the very nature of a switching converter, it requires power to be instantly available when it switches on. If the converter has DMOS switching transistors, the fast edges will create a high current demand on the input supply. This transient load placed on the input is supplied by the external input decoupling capacitor, thus maintaining the input voltage. Therefore, the input supply does not see this transient (this is an analogy to high-speed digital circuits). The positioning of the capacitor is critical and must be placed as close as possible to the input pins and connected via a low-impedance path.

The optimum performance is primarily dependent on two factors:

- Connection of the input and output circuits for minimal loss.

- 2. The ability of the decoupling capacitors to maintain the input and output voltages at a constant level.

#### **PCB Design**

The copper losses (resistance and inductance) can be minimized by the use of mutual ground and power planes (tracks) where possible. If that is not possible, use wide tracks to reduce the losses. If several devices are being powered from a common power source, a star-connected system for the track must be deployed; devices must not be connected in series, as this will cascade the resistive losses. The position of the decoupling capacitors is important. They must be as close to the devices as possible in order to reduce losses. See the *PCB Layout* section for more details.

#### **Decoupling Ceramic Capacitors**

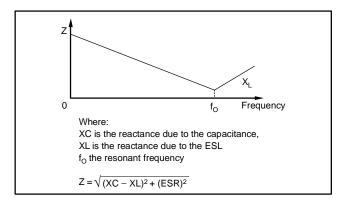

All capacitors have losses due to their internal equivalent series resistance (ESR), and to a lesser degree their equivalent series inductance (ESL). Values for ESL are not always easy to obtain. However, some manufacturers provide graphs of Frequency versus Capacitor Impedance. These will show the capacitors' impedance falling as frequency is increased (see Figure 4). As the frequency is increased, the impedance will stop decreasing and begin to rise. The point of minimum impedance indicates the capacitors' resonant frequency. This frequency is where the components of capacitance and inductance reactance are of equal magnitude. Beyond this point, the capacitor is not effective as a capacitor.

Figure 4. Capacitor Impedance vs Frequency

At  $f_O$ ,  $X_C = X_{L}$ ; however, there is a 180° phase difference resulting in cancellation of the imaginary component. The resulting effect is that the impedance at the resonant point is the real part of the complex impedance; namely, the value of the ESR. The resonant frequency must be well above the 800kHz switching frequency of the DCP and DCVs.

The effect of the ESR is to cause a voltage drop within the capacitor. The value of this voltage drop is simply the product of the ESR and the transient load current, as shown in Equation (1):

$$V_{IN} = V_{PK} - (ESR \times I_{TR})$$

(1)

Where:

V<sub>IN</sub> is the voltage at the device input.

$V_{\mbox{\footnotesize{PK}}}$  is the maximum value of the voltage on the capacitor during charge.

ITR is the transient load current.

The other factor that affects the performance is the value of the capacitance. However, for the input and the full wave outputs (single-output voltage devices), the ESR is the dominant factor.

#### Input Capacitor and the effects of ESR

If the input decoupling capacitor is not ceramic with  $< 20 m\Omega$  ESR, then at the instant the power transistors switch on, the voltage at the input pins will fall momentarily. Should the voltage fall below approximately 4V, the DCP will detect an under-voltage condition and switch the DCP drive circuits to the off state. This is carried out as a precaution against a genuine low input voltage condition that could slow down or even stop the internal circuits from operating correctly. This would result in the drive transistors being turned on too long, causing saturation of the transformer and destruction of the device.

Following detection of a low input voltage condition, the device switches off the internal drive circuits until the input voltage returns to a safe value. Then the device tries to restart. If the input capacitor is still unable to maintain the input voltage, shutdown recurs. This process is repeated until the capacitor is charged sufficiently to start the device correctly. Otherwise, the device will be caught up in a loop.

Normal startup should occur in approximately 1ms from power being applied to the device. If a considerably longer startup duration time is encountered, it is likely that either (or both) the input supply or the capacitors are not performing adequately.

For 5V to 15V input devices, a  $2.2\mu F$  low-ESR ceramic capacitor will ensure a good startup performance, and for the remaining input voltage ranges,  $0.47\mu F$  ceramic capacitors are good. Tantalum capacitors are not recommended, since most do not have low-ESR values and will degrade performance. If tantalum capacitors must be used, close attention must be paid to both the ESR and voltage as derated by the vendor.

#### **Output Ripple Calculation Example**

DCP020505: Output voltage 5V, Output current 0.4A. At full output power, the load resistor is 12.5 $\Omega$ . Output capacitor of 1 $\mu$ F, ESR of 0.1 $\Omega$ . Capacitor discharge time 1% of 800kHz (ripple frequency):

$$\begin{split} t_{DIS} &= 0.0125 \mu s \\ t &= C \times R_{LOAD} \\ t &= 1 \times 10^{-6} \times 12.5 = 12.5 \mu s \\ V_{DIS} &= V_{O} (1 - EXP(-t_{DIS}/\tau)) \\ V_{DIS} &= 5 mV \end{split}$$

By contrast the voltage dropped due to the ESR:

$$V_{ESR} = I_{LOAD} \times ESR$$

$V_{ESR} = 40mV$

Ripple voltage = 45mV

Clearly, increasing the capacitance will have a much smaller effect on the output ripple voltage than reducing the value of the ESR for the filter capacitor.

#### **DUAL OUTPUT VOLTAGE DCP AND DCVs**

The voltage output for the dual DCPs is half wave rectified; therefore, the discharge time is  $1.25\mu s$ . Repeating the above calculations using the 100% load resistance of  $25\Omega$  (0.2A per output), the results are shown below:

$\tau = 25 \mu s$

$T_{DIS} = 1.25 \mu s.$

$V_{DIS} = 244mV$

$V_{ESR} = 20mV$

Ripple Voltage = 266mV

This time, it is the capacitor discharging that is contributing to the largest component of ripple. Changing the output filter to  $10\mu$ F, and repeating the calculations:

Ripple Voltage = 45mV.

This value is composed of almost equal components.

The above calculations are given only as a guide. Capacitor parameters usually have large tolerances and can be susceptible to environmental conditions.

#### **PCB LAYOUT**

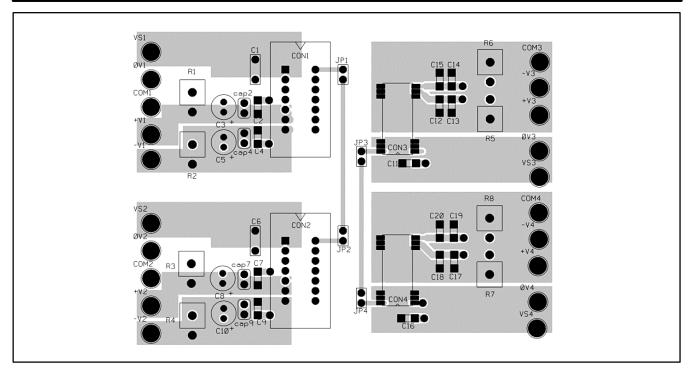

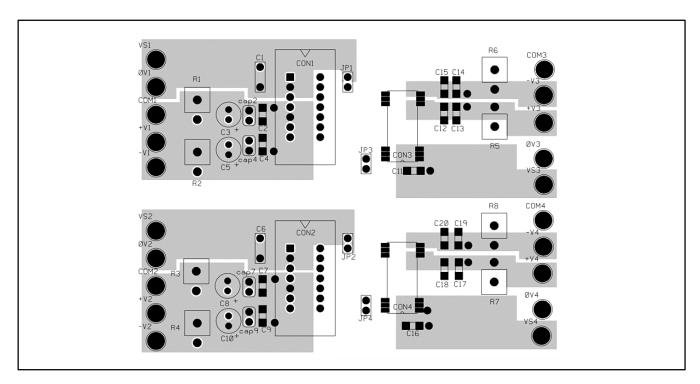

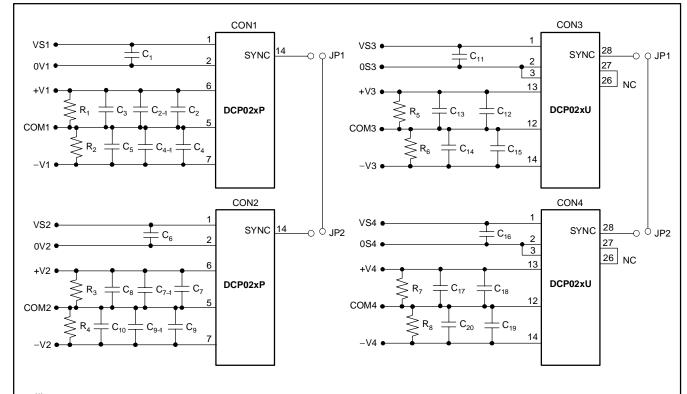

Figure 5 and Figure 6 illustrate a printed circuit board (PCB) layout for the two conventional (DCP01/02, DCV01), and two SO-28 surface-mount packages (DCP02U). Figure 7 shows the schematic.

Input power and ground planes have been used, providing a low-impedance path for the input power. For the output, the common or 0V has been connected via a ground plane, while the connections for the positive and negative voltage outputs are conducted via wide traces in order to minimize losses.

The location of the decoupling capacitors in close proximity to their respective pins ensures low losses due to the effects of stray inductance; thus, improving the ripple performance. This is of particular importance to the input decoupling capacitor as this supplies the transient current associated with the fast switching waveforms of the power drive circuits.

The Sync pin, when not being used, is best left as a floating pad. A ground ring or annulus connected around the pin will prevent noise being conducted onto the pin. If the Sync pin is being connected to one or more Sync pins, then the linking trace should be narrow and must be kept short in length. In addition, no other trace should be in close proximity to this trace because that will increase the stray capacitance on this pin, and that will effect the performance of the oscillator.

#### Ripple and Noise

Careful consideration should be given to the layout of the PCB, in order that the best results can be obtained.

The DCP01B is a switching power supply and as such can place high peak current demands on the input supply. In order to avoid the supply falling momentarily during the fast switching pulses, ground and power planes should be used to connect the power to the input of DCP01B. If this is not possible, then the supplies must be connected in a star formation with the traces made as wide as possible.

If the SYNC $_{\rm IN}$  pin is being used, then the trace connection between device SYNC $_{\rm IN}$  pins should be short to avoid stray capacitance. If the SYNC $_{\rm IN}$  pin is not being used, it is advisable to place a guard ring (connected to input ground) around this pin to avoid any noise pick up.

The output should be taken from the device using ground and power planes; this ensures minimum losses.

A good quality low-ESR ceramic capacitor placed as close as practical across the input will reduce reflected ripple and ensure a smooth startup.

A good quality low-ESR capacitor (ceramic preferred) placed as close as practical across the rectifier output terminal and output ground gives the best ripple and noise performance. See SBVA012 for more information on noise rejection.

#### THERMAL MANAGEMENT

Due to the high power density of this device, it is advisable to provide ground planes on the input and output.

Figure 5. Example of PCB Layout, Component-Side View

Figure 6. Example of PCB Layout, Non-component-Side View

- (1) Capacitors C2-1, C4-1, C7-1, and C9-1 are through-hole plated components connected in parallel with C2, C4, C7 and C9 (1206 SMD), respectively.

- (2) For optimum low-noise performance, use low-ESR capacitors.

- (3) Do not connect the SYNC pin jumper (JP1–JP4) if the SYNC function is not being used.

- (4) Connections to the power input should be made with a minimum wire of 16/0.2 twisted pair, with the length kept short.

- $^{(5)}\,\,$  VSx and 0Vx are input supply and ground respecively (x represents the channel).

- (6) +Vx and -Vx are the positive and negative outputs, referenced to a common ground COMx.

- (7) JPx are the links used for self-synchronization; if this facility is not being used, the links should be unconnected.

- (8) R1–R8 are the power output loads; do not fit these if an external load is connected.

- $^{(9)}\,$  CON1 and CON2 are DIL-14; CON3 and CON4 are SO-28 packages.

- (10) NC = not connected.

Figure 7. Example of PCB Layout, Schematic Diagram

#### PACKAGE OPTION ADDENDUM

#### **PACKAGING INFORMATION**

| Orderable Device   | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|--------------------|-----------------------|-----------------|--------------------|------|----------------|-------------------------|------------------|------------------------------|

| DCP010505BP        | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010505BP-U      | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010505BP-U/700  | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010505DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010505DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010505DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010512BP        | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010512BP-U      | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010512BP-U/700  | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010512DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010512DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010512DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010515BP        | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010515BP-U      | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010515BP-U/700  | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010515DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP010515DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP010515DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP011512DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP011512DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP011512DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP011515DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP011515DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP011515DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP012415DBP       | ACTIVE                | PDIP            | NVA                | 7    | 25             | TBD                     | CU SNPB          | Level-NA-NA-NA               |

| DCP012415DBP-U     | ACTIVE                | SOP             | DUA                | 7    | 25             | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

| DCP012415DBP-U/700 | ACTIVE                | SOP             | DUA                | 7    | 700            | TBD                     | CU SNPB          | Level-3-240C-168 HR          |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

# PACKAGE OPTION ADDENDUM

30-Mar-2005

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

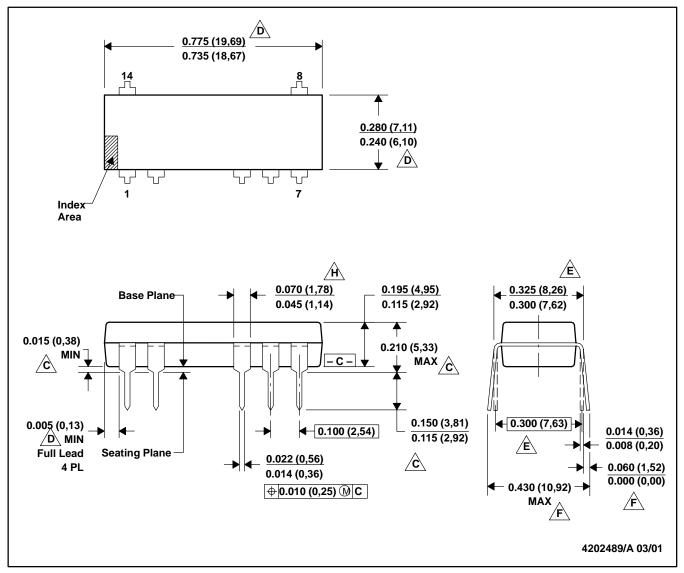

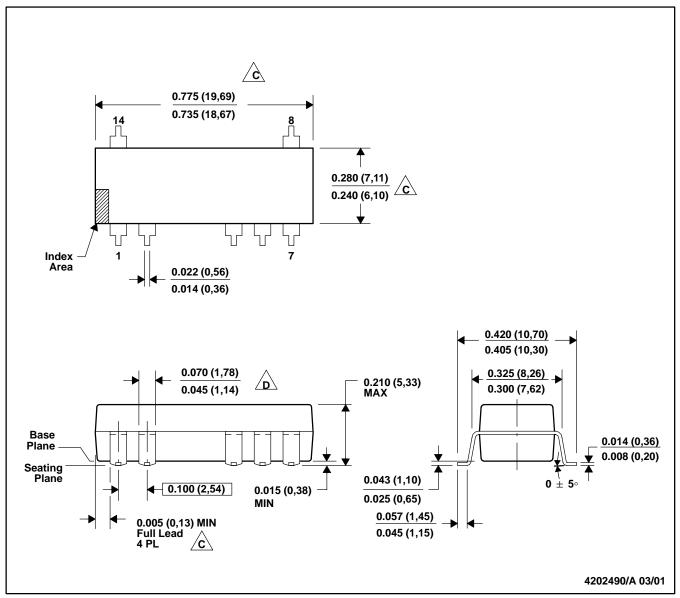

#### NVA (R-PDIP-T7/14)

#### PLASTIC DUAL-IN-LINE

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Dimensions are measured with the package seated in JEDEC seating plane gauge GS-3.

- Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

- Dimensions measured with the leads constrained to be perpendicular to Datum C.

- Dimensions are measured at the lead tips with the leads unconstrained.

- G. Pointed or rounded lead tips are preferred to ease a insertion.

- H.\text{Lead shoulder maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25).

- I. Distance between leads including dambar protrusions to be 0.005 (0,13) minumum.

- J. A visual index feature must be located within the cross-hatched area.

- K. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- L. Falls within JEDEC MS-001-AA.

#### **DUA (R-PDSO-G7/14)**

#### PLASTIC SMALL-OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

This drawing is subject to change without notice.

Dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 (0,25).

Lead shoulder maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25).

- E. Distance between leads including dambar protrusions to be 0.005 (0,13) minimum.

- F. A visual index feature must be located within the cross–hatched area.

- G. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated