# **30-W STEREO DIGITAL AMPLIFIER POWER STAGE**

### **FEATURES**

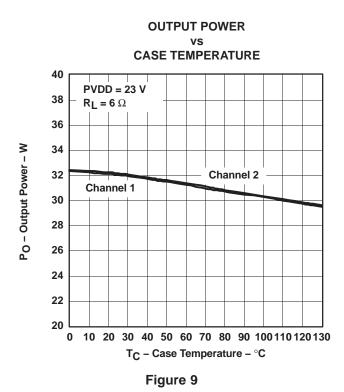

- $2 \times 30$  W (BTL) Into 6  $\Omega$  at 1 kHz

- 95-dB Dynamic Range (in System With TAS5026)

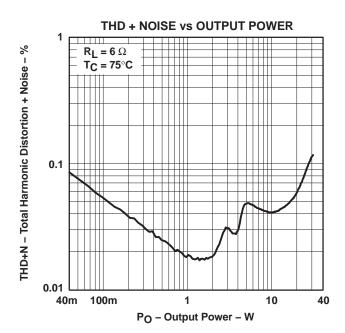

- < 0.2% THD+N (in System 30 W RMS Into 6-Ω Resistive Load)

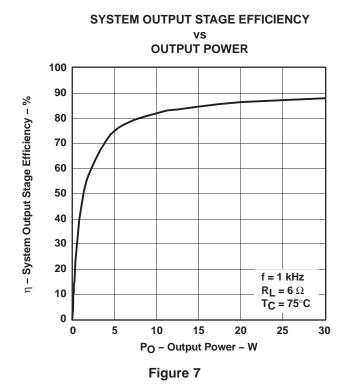

- Device Power Efficiency Typical >90% Into 6-Ω Load

- Self-Protection Design (Including Undervoltage, Overtemperature, and Short Conditions) With Error Reports

- Internal Gate Drive Supply Voltage Regulator

- EMI Compliant When Used With Recommended System Design

# **APPLICATIONS**

- DVD Receiver

- Home Theatre

- Mini/Micro Component Systems

- Internet Music Appliance

# DESCRIPTION

The TAS5122 is a high-performance, integrated stereo digital amplifier power stage designed to drive  $6-\Omega$  speakers at up to 30 W per channel. The device incorporates TI's PurePath Digital  $^{\text{TM}}$  technology and is used with a digital audio PWM processor (TAS50XX) and a simple, passive demodulation filter to deliver high-quality, high-efficiency, true-digital audio amplification.

The efficiency of this digital amplifier is typically greater than 90%. Overcurrent protection, overtemperature protection, and undervoltage protection are built into the TAS5122, safeguarding the device and speakers against fault conditions that could damage the system.

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PurePath Digital and PowerPAD are trademarks of Texas Instruments. Other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### **GENERAL INFORMATION**

# **Terminal Assignment**

The TAS5122 is offered in a thermally enhanced 56-pin DCA package (thermal pad is on the bottom). Output of the DCA package is highly dependent on thermal design. See the *Thermal Information* section. Therefore, it is important to design the heatsink carefully.

### DCA PACKAGE (TOP VIEW)

| GND □                   | 10 | 56 | □□ GND   |

|-------------------------|----|----|----------|

| GND ===                 | 2  | 55 | GVDD     |

| GREG ==                 | 3  | 54 | BST A    |

| DVDD ===                | 4  | 53 | PVDD A   |

| GND □                   | 5  | 52 | PVDD A   |

| DGND ===                | 6  | 51 | OUT_A    |

| GND ===                 | 7  | 50 | OUT A    |

| PWM AP ===              | 8  | 49 | GND      |

| PWM AM                  | 9  | 49 | GND GND  |

| RESET AB                | 10 | 46 |          |

| PWM BM ===              |    |    | OUT_B    |

| _                       | 11 | 46 | OUT_B    |

| PWM_BP ===              | 12 | 45 | PVDD_B   |

| DREG ===                | 13 | 44 | PVDD_B   |

| M1 ===                  | 14 | 43 | BST_B    |

| M2 —                    | 15 | 42 | BST_C    |

| M3 <u> </u>             | 16 | 41 | PVDD_C   |

| DREG_RTN <sup>□□□</sup> | 17 | 40 | PVDD_C   |

| PWM_CP □□□              | 18 | 39 | OUT_C    |

| PWM_CM ===              | 19 | 38 | OUT_C    |

| RESET_CD □□□            | 20 | 37 | ── GND   |

| PWM_DM □□□              | 21 | 36 | ─ GND    |

| PWM_DP □□               | 22 | 35 | OUT_D    |

| SD_AB □□                | 23 | 34 | OUT_D    |

| SD_CD □□                | 24 | 33 | PVDD_D   |

| OTW □□                  | 25 | 32 | PVDD_D   |

| GREG □                  | 26 | 31 | □□ BST_D |

| GND □                   | 27 | 30 | GVDD     |

| GND □□                  | 28 | 29 | □ GND    |

|                         |    |    | 1        |

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

| TAS5122                                                | UNITS                  |

|--------------------------------------------------------|------------------------|

| DVDD to DGND                                           | –0.3 V to 4.2 V        |

| GVDD to GND                                            | 28 V                   |

| PVDD_X to GND (dc voltage)                             | 28 V                   |

| OUT_X to GND (dc voltage)                              | 28 V                   |

| BST_X to GND (dc voltage)                              | 40 V                   |

| GREG to GND (2)                                        | 14.2 V                 |

| PWM_XP, RESET, M1, M2, M3, SD, OTW                     | -0.3 V to DVDD + 0.3 V |

| Maximum operating junction temperature, T <sub>J</sub> | -40°C to 150°C         |

| Storage temperature                                    | -40°C to 125°C         |

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

- (2) GREG is treated as an input when the GREG pin is overdriven by GVDD of 12 V.

#### ORDERING INFORMATION

| TA          | PACKAGE    | DESCRIPTION        |

|-------------|------------|--------------------|

| 0°C to 70°C | TAS5122DCA | 56-pin small TSSOP |

# PACKAGE DISSIPATION RATINGS

| PACKAGE          | R <sub>θ</sub> JC<br>(°C/W) | R <sub>θ</sub> JA<br>(°C/W) |

|------------------|-----------------------------|-----------------------------|

| 56-pin DCA TSSOP | 1.14                        | See Note 1                  |

(1) The TAS5122 package is thermally enhanced for conductive cooling using an exposed metal pad area. It is impractical to use the device with the pad exposed to ambient air as the only heat sinking of the device.

For this reason,  $R_{\theta JA}$ , a system parameter that characterizes the thermal treatment, is provided in the *Application Information* section of the data sheet. An example and discussion of typical system  $R_{\theta JA}$  values are provided in the *Thermal Information* section. This example provides additional information regarding the power dissipation ratings. This example should be used as a reference to calculate the heat dissipation ratings for a specific application. TI application engineering provides technical support to design heatsinks if needed.

# **Terminal Functions**

| TERMINAL |             |                         |                                                                             |  |  |

|----------|-------------|-------------------------|-----------------------------------------------------------------------------|--|--|

| NAME     | NO.         | FUNCTION <sup>(1)</sup> | DESCRIPTION                                                                 |  |  |

| BST_A    | 54          | Р                       | HS bootstrap supply (BST), external capacitor to OUT_A required             |  |  |

| BST_B    | 43          | Р                       | HS bootstrap supply (BST), external capacitor to OUT_B required             |  |  |

| BST_C    | 42          | Р                       | HS bootstrap supply (BST), external capacitor to OUT_C required             |  |  |

| BST_D    | 31          | Р                       | HS bootstrap supply (BST), external capacitor to OUT_D required             |  |  |

| DGND     | 6           | Р                       | Digital I/O reference ground                                                |  |  |

| DREG     | 13          | Р                       | Digital supply voltage regulator decoupling pin, capacitor connected to GND |  |  |

| DREG_RTN | 17          | Р                       | Digital supply voltage regulator decoupling return pin                      |  |  |

| DVDD     | 4           | Р                       | I/O reference supply input (3.3 V)                                          |  |  |

| GND      | 1, 2, 5,    | Р                       | Power ground (I/O reference ground – pin 22)                                |  |  |

|          | 7, 27, 28,  |                         |                                                                             |  |  |

|          | 29, 36, 37, |                         |                                                                             |  |  |

|          | 48, 49, 56  |                         |                                                                             |  |  |

| GREG     | 3, 26       | Р                       | Gate drive voltage regulator decoupling pin, capacitor to GND               |  |  |

| GVDD     | 30, 55      | Р                       | Voltage supply to on-chip gate drive and digital supply voltage regulators  |  |  |

| M1       | 14          | I                       | Mode selection pin                                                          |  |  |

| M2       | 15          | I                       | Mode selection pin                                                          |  |  |

| M3       | 16          | I                       | Mode selection pin                                                          |  |  |

| OTW      | 25          | 0                       | Overtemperature warning output, open drain with internal pullup             |  |  |

| OUT_A    | 50, 51      | 0                       | Output, half-bridge A                                                       |  |  |

| OUT_B    | 46, 47      | 0                       | Output, half-bridge B                                                       |  |  |

| OUT_C    | 38, 39      | 0                       | Output, half-bridge C                                                       |  |  |

| OUT_D    | 34, 35      | 0                       | Output, half-bridge D                                                       |  |  |

| PVDD_A   | 52, 53      | Р                       | Power supply input for half-bridge A                                        |  |  |

| PVDD_B   | 44, 45      | Р                       | Power supply input for half-bridge B                                        |  |  |

| PVDD_C   | 40, 41      | Р                       | Power supply input for half-bridge C                                        |  |  |

| PVDD_D   | 32, 33      | Р                       | Power supply input for half-bridge D                                        |  |  |

| PWM_AM   | 9           | I                       | Input signal (negative), half-bridge A                                      |  |  |

| PWM_AP   | 8           | I                       | Input signal (positive), half-bridge A                                      |  |  |

| PWM_BM   | 11          | I                       | Input signal (negative), half-bridge B                                      |  |  |

| PWM_BP   | 12          | I                       | Input signal (positive), half-bridge B                                      |  |  |

| PWM_CM   | 19          | I                       | Input signal (negative), half-bridge C                                      |  |  |

| PWM_CP   | 18          | I                       | Input signal (positive), half-bridge C                                      |  |  |

| PWM_DM   | 21          | I                       | Input signal (negative), half-bridge D                                      |  |  |

| PWM_DP   | 22          | I                       | Input signal (positive), half-bridge D                                      |  |  |

| RESET_AB | 10          | I                       | Reset signal, active low                                                    |  |  |

| RESET_CD | 20          | I                       | Reset signal, active low                                                    |  |  |

| SD_AB    | 23          | 0                       | Shutdown signal for half-bridges A and B                                    |  |  |

| SD_CD    | 24          | 0                       | Shutdown signal for half-bridges C and D                                    |  |  |

<sup>|</sup> SD\_CD | 24 | (1) | = input, O = output, P = power

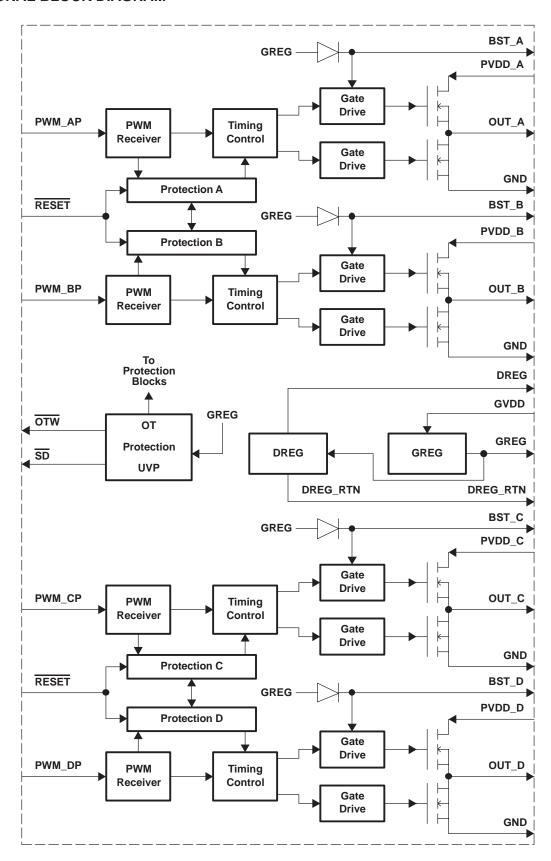

# **FUNCTIONAL BLOCK DIAGRAM**

# **RECOMMENDED OPERATING CONDITIONS**

|        |                                                     |                                                            | MIN | TYP | MAX  | UNIT |

|--------|-----------------------------------------------------|------------------------------------------------------------|-----|-----|------|------|

| DVDD   | Digital supply (1)                                  | Relative to DGND                                           | 3   | 3.3 | 3.6  | V    |

| GVDD   | Supply for internal gate drive and logic regulators | Relative to GND                                            | 16  | 23  | 25.5 | V    |

| PVDD_x | Half-bridge supply                                  | Relative to GND, R <sub>L</sub> = $6 \Omega$ to $8 \Omega$ | 0   | 23  | 25.5 | V    |

| TJ     | Junction temperature                                |                                                            | 0   |     | 125  | °C   |

<sup>(1)</sup> It is recommended for DVDD to be connected to DREG via a  $100-\Omega$  resistor.

# **ELECTRICAL CHARACTERISTICS**

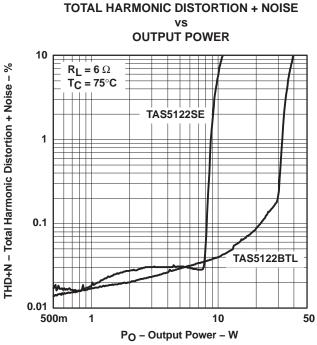

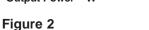

PVDD\_X = 23 V, GVDD = 23 V, DVDD = 3.3 V, DVDD connected to DREG via a 100- $\Omega$  resistor, R<sub>L</sub> = 6  $\Omega$ , 8X f<sub>S</sub> = 384 kHz, unless otherwise noted. AC performance is recorded as a chipset with TAS5010 as the PWM processor and TAS5122 as the power stage.

| SYMBOL   | PARAMETER                         | TEST CONDITIONS                                                               | TYPICAL<br>T <sub>A</sub> =25°C | T <sub>A</sub> =25°C | T <sub>Case</sub> =<br>75°C | UNITS | MIN/TYP/<br>MAX |

|----------|-----------------------------------|-------------------------------------------------------------------------------|---------------------------------|----------------------|-----------------------------|-------|-----------------|

| AC PERFO | DRMANCE, BTL MODE, 1 kHz          | 1                                                                             |                                 | 11                   |                             |       | •               |

|          |                                   | $R_L$ = 8 $Ω$ , unclipped, AES17 filter                                       |                                 |                      | 24                          | W     | Тур             |

|          |                                   | $R_L = 8 \Omega$ , THD = 10%,<br>AES17 filter                                 |                                 |                      | 29                          | W     | Тур             |

| PO       | Output power                      | $R_L = 6 \Omega$ , THD = 0.4%, AES17 filter                                   |                                 |                      | 30                          | W     | Тур             |

|          |                                   | $R_L = 6 \Omega$ , THD = 10%,<br>AES17 filter                                 |                                 |                      | 37                          | W     | Тур             |

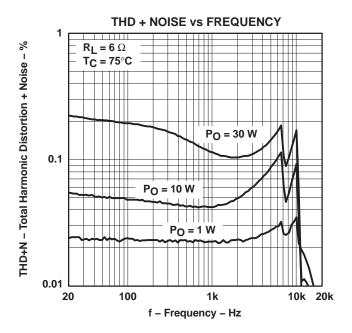

|          |                                   | Po = 1 W/ channel, $R_L = 6 \Omega$ , AES17 filter                            |                                 |                      | 0.05%                       |       | Тур             |

| THD+N    | Total harmonic distortion + noise | Po = 10 W/channel, $R_L = 6 \Omega$ , AES17 filter                            |                                 |                      | 0.05%                       |       | Тур             |

|          |                                   | Po = 30 W/channel, $R_L = 6 \Omega$ , AES17 filter                            |                                 |                      | 0.2%                        |       | Тур             |

| Vn       | Output RMS noise                  | A-weighted, mute, R <sub>L</sub> = 6 $\Omega$ , 20 Hz to 20 kHz, AES17 filter |                                 |                      | 240                         | μV    | Max             |

| SNR      | Signal-to-noise ratio             | $f = 1 \text{ kHz}$ , A-weighted, $R_L = 6 \Omega$ , AES17 filter             |                                 |                      | 95                          | dB    | Тур             |

| DR       | Dynamic range                     | f = 1  kHz, A-weighted,<br>R <sub>L</sub> = 6 $\Omega$ , AES17 filter         |                                 |                      | 95                          | dB    | Тур             |

| INTERNAL | VOLTAGE REGULATOR                 |                                                                               |                                 |                      |                             |       |                 |

| DREG     | Voltage regulator                 | I <sub>O</sub> = 1 mA,<br>PVDD = 18 V-30.5 V                                  | 3.1                             |                      |                             | V     | Тур             |

| GREG     | Voltage regulator                 | I <sub>O</sub> = 1.2 mA,<br>PVDD = 18 V-30.5 V                                | 13.4                            |                      |                             | V     | Тур             |

| IGVDD    | GVDD supply current, operating    | f <sub>S</sub> = 384 kHz, no load, 50% duty cycle                             |                                 | 24 (1)               |                             | mA    | Max             |

| IDVDD    | DVDD supply current, operating    | f <sub>S</sub> = 384 kHz, no load                                             | 1                               | 5                    |                             | mA    | Max             |

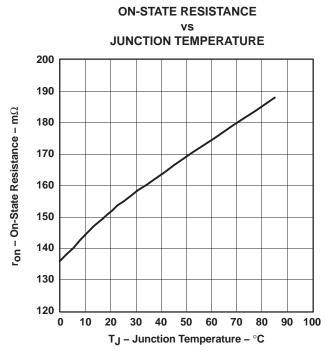

| OUTPUT S | STAGE MOSFETs                     |                                                                               |                                 |                      |                             |       |                 |

|          | Forward on-resistance, LS         | T <sub>J</sub> = 25°C                                                         | 155                             |                      |                             | mΩ    | Max             |

|          | Forward on-resistance, HS         | T <sub>J</sub> = 25°C                                                         | 155                             |                      |                             | mΩ    | Max             |

<sup>(1)</sup> Measured with TI standard manufacturing hardware configuration

# **ELECTRICAL CHARACTERISTICS**

PVDD\_x = 23 V, GVDD = 23 V, DVDD = 3.3 V, RL = 6  $\Omega$ , 8X fs = 384 kHz, unless otherwise noted

| SYMBOL                        | PARAMETER                               | TEST CONDITIONS      | TYPICAL<br>T <sub>A</sub> =25°C | T <sub>A</sub> =25°C | T <sub>Case</sub> =<br>75°C | UNITS | MIN/TYP/<br>MAX |

|-------------------------------|-----------------------------------------|----------------------|---------------------------------|----------------------|-----------------------------|-------|-----------------|

| INPUT/OU                      | TPUT PROTECTION                         |                      | •                               | •                    |                             |       | •               |

| .,                            | Hadamakan makasi at limit OVD           |                      | 7.4                             | 6.9                  |                             | V     | Min             |

| V <sub>uvp,G</sub>            | Undervoltage protection limit, GVDD     |                      | 7.4                             | 7.9                  |                             | V     | Max             |

| OTW                           | Overtemperature warning                 |                      | 125                             |                      |                             | °C    | Тур             |

| OTE                           | Overtemperature error                   |                      | 150                             |                      |                             | °C    | Тур             |

| ОС                            | Overcurrent protection                  |                      |                                 | 5.0                  |                             | Α     | Min             |

| STATIC DI                     | GITAL SPECIFICATION                     |                      |                                 |                      |                             |       |                 |

|                               | PWM_AP, PWM_BP, M1, M2, M3, SD, OTW     |                      |                                 |                      |                             |       |                 |

| .,                            | LP also be and beginning                |                      |                                 | 2                    |                             | V     | Min             |

| VIH                           | High-level input voltage                |                      |                                 | DVDD                 |                             | V     | Max             |

| VIL                           | Low-level input voltage                 |                      |                                 | 0.8                  |                             | V     | Max             |

| 11                            | Land Indiana and Indiana                |                      |                                 | -10                  |                             | μΑ    | Min             |

| Leakage Input leakage current |                                         |                      |                                 | 10                   |                             | μΑ    | Max             |

| OTW/SHU                       | TDOWN (SD)                              |                      |                                 |                      |                             |       |                 |

|                               | Internally pullup R from OTW/SD to DVDD |                      | 30                              | 22.5                 |                             | kΩ    | Min             |

| VOL                           | Low-level output voltage                | $I_O = 4 \text{ mA}$ |                                 | 0.4                  |                             | V     | Max             |

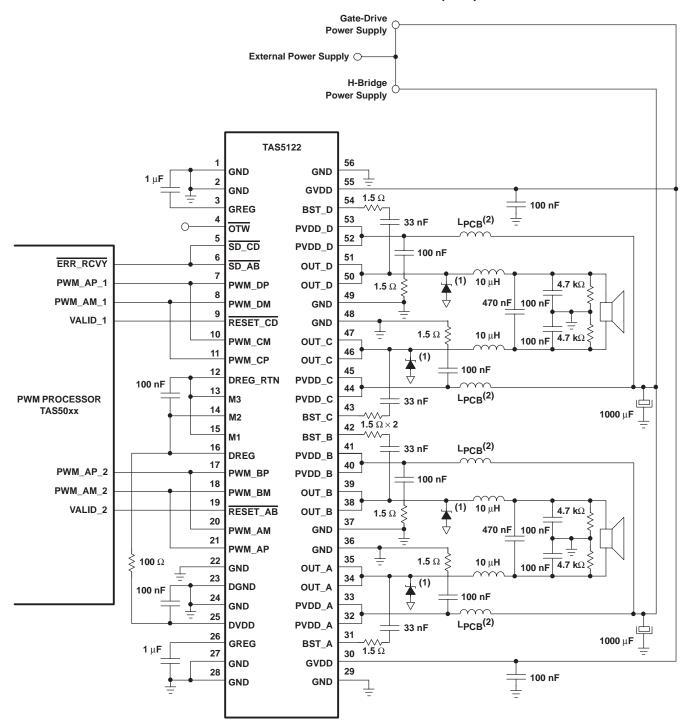

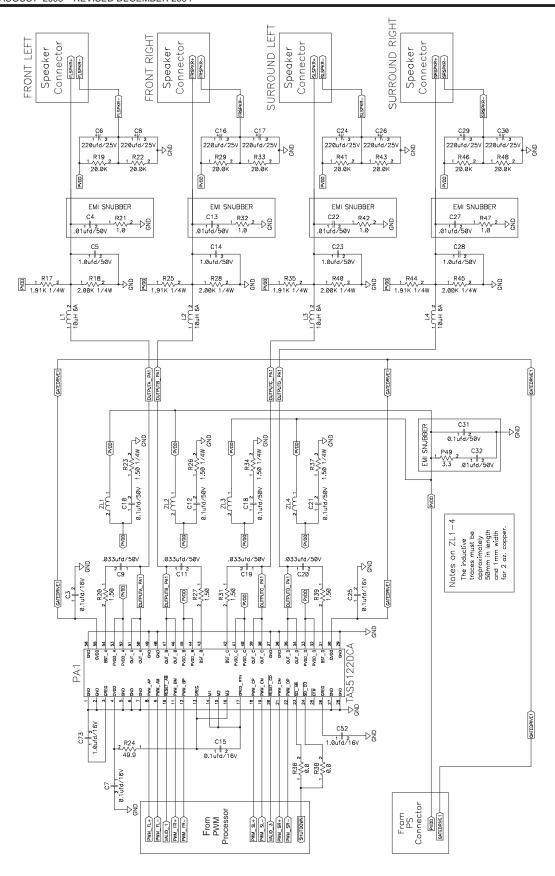

# SYSTEM CONFIGURATION USED FOR CHARACTERIZATION (BTL)

<sup>(1)</sup> Voltage Clamp 30 V, PN SMAJ28A, MFG MICROSEMI

<sup>(2)</sup> LPCB: Track in the PCB (1 mm wide and 50 mm long)

Figure 1. Typical Single-Ended Design With TAS5122 DCA

# TYPICAL CHARACTERISTICS

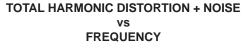

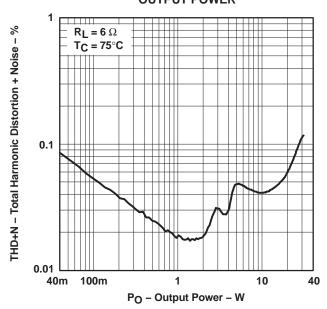

Figure 4

Figure 3

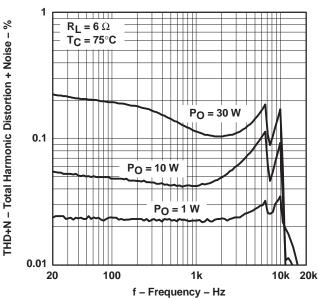

# TOTAL HARMONIC DISTORTION + NOISE vs OUTPUT POWER

Figure 5

Figure 11

# THEORY OF OPERATION

#### **POWER SUPPLIES**

The power device only requires two supply voltages, GVDD and PVDD x.

GVDD is the gate drive supply for the device, regulated internally down to approximately 12 V, and decoupled with regards to board GND on the GREG pins through an external capacitor. GREG powers both the low side and high side via a bootstrap step-up conversion. The bootstrap supply is charged after the first low-side turnon pulse. Internal digital core voltage DREG is also derived from GVDD and regulated down by internal low-dropout regulators (LDRs) to 3.3 V.

The gate-driver LDR can be bypassed for reducing idle loss in the device by shorting GREG to GVDD and directly feeding in 12 V. This can be useful in an application where thermal conduction of heat from the device is difficult. Bypassing the LDR reduces power dissipation.

PVDD x is the H-bridge power supply pin. Two power pins exist for each half-bridge to handle the current density. It is important that the circuitry recommendations concerning the PVDD\_x pins are followed carefully both topologyand lavout-wise. For topology recommendations, see the System Configuration Used for Characterization section. Following these recommendations is important for parameters like EMI, reliability, and performance.

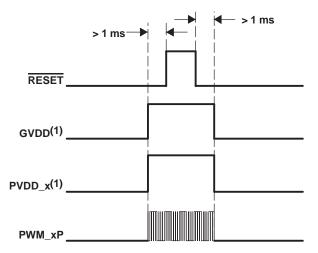

# SYSTEM POWER-UP/POWER-DOWN SEQUENCE

# Powering Up

(1) PVDD should not be powered up before GVDD.

During power up when RESET is asserted LOW, all MOSFETs are turned off and the two internal half-bridges are in the high-impedance state (Hi-Z). The bootstrap capacitors supplying high-side gate drive are at this point

not charged. To comply with the click and pop scheme and use of non-TI PWM processors, it is recommended to use a 4-k $\Omega$  pulldown resistor on each PWM output node to ground. This precharges the bootstrap supply capacitors and discharges the output filter capacitor (see the *System Configuration Used for Characterization* section).

After GVDD has been applied, it takes approximately 800  $\mu$ s to fully charge the BST capacitor. Within this time, RESET must be kept low. After approximately 1 ms, the power stage bootstrap capacitor is charged.

RESET can now be released if the modulator is powered up and streaming PWM signals to the power stage PWM xP.

A constant HIGH dc level on PWM\_xP is not permitted, because it would force the high-side MOSFET ON until it eventually ran out of BST capacitor energy and might damage the device.

An unknown state of the PWM output signals from the processor is illegal and should be avoided, which in practice means that the PWM processor must be powered up and initialized before RESET is deasserted HIGH to the power stage.

#### **Powering Down**

For powering down the power stage, an opposite approach is necessary. RESET must be asserted LOW before the valid PWM signal is removed.

When TI PWM processors are used with TI power stages, the correct timing control of RESET and PWM\_xP is performed by the modulator.

#### **Precaution**

The TAS5122 must always start up in the high-impedance (Hi-Z) state. In this state, the bootstrap (BST) capacitor is precharged by a resistor on each PWM output node to ground. See *System Configuration Used for Characterization*. This ensures that the power stage is ready for receiving PWM pulses, indicating either HIGH-or LOW-side turnon after RESET is deasserted to the power stage.

With the following pulldown and BST capacitor size, the charge time is:

$$C = 33 \text{ nF}, R = 4.7 \text{ k}\Omega$$

$R \times C \times 5 = 775.5 \text{ us}$

After GVDD has been applied, it takes approximately  $800~\mu s$  to fully charge the BST capacitor. During this time, RESET must be kept low. After approximately 1 ms, the power stage BST is charged and ready. RESET can now be released if the PWM modulator is ready and is streaming valid PWM signals to the power stage. Valid PWM signals are switching PWM signals with a frequency between 350–400 kHz. A constant HIGH level on the PWM\_xP forces the high-side MOSFET ON until it eventually runs out of BST capacitor energy. Putting the device in this condition should be avoided.

In practice this means that the DVDD-to-PWM processor should be stable and initialization should be completed before RESET is deasserted to the power stage.

#### CONTROL I/O

# Shutdown Pin: SD

The  $\overline{SD}$  pin functions as an output pin and is intended for protection-mode signaling to, for example, a controller or other PWM processor device. The pin is open-drain with an internal pullup to DVDD.

The logic output is, as shown in the following table, a combination of the device state and  $\overline{\text{RESET}}$  input:

| SD   | RESET | DESCRIPTION                                                    |

|------|-------|----------------------------------------------------------------|

| 0    | 0     | Not used                                                       |

| 0    | 1     | Device in protection mode, i.e., UVP and/or OC and/or OT error |

| 1(2) | 0     | Device set high-impedance (Hi-Z), SD forced high               |

| 1    | 1     | Normal operation                                               |

<sup>(2)</sup> SD is pulled high when RESET is asserted low independent of chip state (i.e., protection mode). This is desirable to maintain compatibility with some TI PWM processors.

# **Temperature Warning Pin: OTW**

The OTW pin gives a temperature warning signal when temperature exceeds the set limit. The pin is of the open-drain type with an internal pullup to DVDD.

| OTW | DESCRIPTION                            |  |

|-----|----------------------------------------|--|

| 0   | Junction temperature higher than 125°C |  |

| 1   | Junction temperature lower than 125°C  |  |

# **Overall Reporting**

The  $\overline{\text{SD}}$  pin, together with the  $\overline{\text{OTW}}$  pin, gives chip state information as described in Table 1.

**Table 1. Error Signal Decoding**

| OTW | SD | DESCRIPTION                                  |

|-----|----|----------------------------------------------|

| 0   | 0  | Overtemperature error (OTE)                  |

| 0   | 1  | Overtemperature warning (OTW)                |

| 1   | 0  | Overcurrent (OC) or undervoltage (UVP) error |

| 1   | 1  | Normal operation, no errors/warnings         |

## **Chip Protection**

The TAS5122 protection function is implemented in a closed loop with, for example, a system controller or other TI PWM processor device. The TAS5122 contains three individual systems protecting the device against fault conditions. All of the error events covered result in the output stage being set in a high-impedance state (Hi-Z) for maximum protection of the device and connected equipment.

The device can be recovered by toggling RESET low and then high, after all errors are cleared.

# **Overcurrent (OC) Protection**

The device has individual forward current protection on both high-side and low-side power stage FETs. The OC protection works only with the demodulation filter present at the output. See *Demodulation Filter Design* in the *Application Information* section of this data sheet for design constraints.

# **Overtemperature (OT) Protection**

A dual temperature protection system asserts a warning signal when the device junction temperature exceeds 125°C. The OT protection circuit is shared by all half-bridges.

# **Undervoltage (UV) Protection**

Undervoltage lockout occurs when GVDD is insufficient for proper device operation. The UV protection system protects the device under power-up and power-down situations. The UV protection circuits are shared by all half-bridges.

#### **Reset Functions**

The functions of the reset input are:

- Reset is used for reenabling operation after a latching error event (PMODE1).

- Reset is used for disabling output stage switching (mute function).

The error latch is cleared on the falling edge of reset and normal operation is resumed when reset goes high.

# PROTECTION MODE

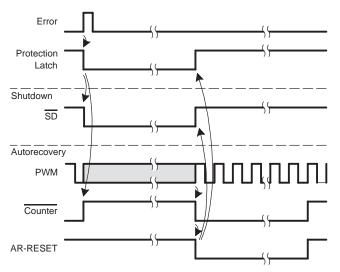

### Autorecovery (AR) After Errors (PMODE0)

In autorecovery mode (PMODE0), the TAS5122 is self-supported in handling of error situations. All protection systems are active, setting the output stage in the high-impedance state to protect the output stage and connected equipment. However, after a short time the device auto-recovers, i.e., operation is automatically resumed provided that the system is fully operational.

The autorecovery timing is set by counting PWM input cycles, i.e., the timing is relative to the switching frequency.

The AR system is common to both half-bridges.

### Timing and Function

The function of the autorecovery circuit is as follows:

- 1. An error event occurs and sets the protection latch (output stage goes Hi-Z).

- 2. The counter is started.

- After n/2 cycles, the protection latch is cleared but the output stage remains Hi-Z (identical to pulling RESET low).

- 4. After n cycles, operation is resumed (identical to pulling RESET high) (n = 512).

Figure 12. Autorecovery Function Latching Shutdown on All Errors (PMODE1)

In latching shutdown mode, all error situations result in a permanent shutdown (output stage Hi-Z). Reenabling can be done by toggling the RESET pin.

# All Protection Systems Disabled (PMODE2)

In PMODE2, all protection systems are disabled. This mode is purely intended for testing and characterization purposes and thus not recommended for normal device operation.

### **MODE Pins Selection**

The protection mode is selected by shorting M1/M2 to DREG or DGND according to Table 2.

**Table 2. Protection Mode Selection**

| M1 | M2 | PROTECTION MODE                          |

|----|----|------------------------------------------|

| 0  | 0  | Reserved                                 |

| 0  | 1  | Latching shutdown on all errors (PMODE1) |

| 1  | 0  | Reserved                                 |

| 1  | 1  | Reserved                                 |

The output configuration mode is selected by shorting the M3 pin to DREG or DGND according to Table 3.

**Table 3. Output Mode Selection**

| М3 | OUTPUT MODE                         |  |  |  |  |  |

|----|-------------------------------------|--|--|--|--|--|

| 0  | Bridge-tied load output stage (BTL) |  |  |  |  |  |

| 1  | Reserved                            |  |  |  |  |  |

# APPLICATION INFORMATION

# DEMODULATION FILTER DESIGN AND SPIKE CONSIDERATIONS

The output square wave is susceptible to overshoots (voltage spikes). The spike characteristics depend on many elements, including silicon design and application design and layout. The device should be able to handle narrow spike pulses, less than 65 ns, up to 65 volts peak. For more detailed information, see TI application report SLEA025.

The PurePath Digital amplifier outputs are driven by heavy-duty DMOS transistors in an H-bridge configuration. These transistors are either off or fully on, which reduces the DMOS transistor on-state resistance, R<sub>DSon</sub>, and the power dissipated in the device, thereby increasing efficiency.

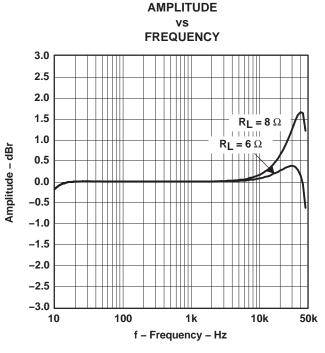

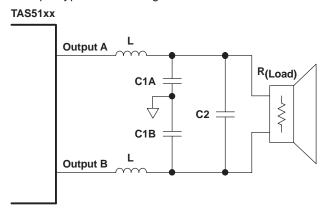

The result is a square-wave output signal with a duty cycle that is proportional to the amplitude of the audio signal. It is recommended that a second-order LC filter be used to recover the audio signal. For this application, EMI is considered important; therefore, the selected filter is the full-output type shown in Figure 13.

Figure 13. Demodulation Filter (AD Mode)

The main purpose of the output filter is to attenuate the high-frequency switching component of the PurePath Digital amplifier while preserving the signals in the audio band.

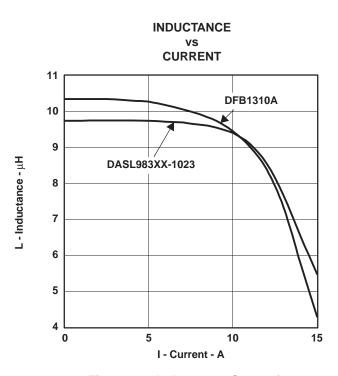

Design of the demodulation filter affects the performance of the power amplifier significantly. As a result, to ensure proper operation of the overcurrent (OC) protection circuit and meet the device THD+N specifications, the selection of the inductors used in the output filter must be considered according to the following. The rule is that the inductance should remain stable within the range of peak current seen at maximum output power and deliver at least 5  $\mu H$  of inductance at 15 A.

If this rule is observed, the TAS5122 does not have distortion issues due to the output inductors, and overcurrent conditions do not occur due to inductor saturation in the output filter.

Another parameter to be considered is the idle current loss in the inductor. This can be measured or specified as inductor dissipation (D). The target specification for dissipation is less than 0.05.

In general, 10- $\mu$ H inductors suffice for most applications. The frequency response of the amplifier is slightly altered by the change in output load resistance; however, unless tight control of frequency response is necessary (better than 0.5 dB), it is not necessary to deviate from 10  $\mu$ H.

The graph in Figure 14 displays the inductance vs current characteristics of two inductors that are recommended for use with the TAS5122.

Figure 14. Inductance Saturation

The selection of the capacitor that is placed across the output of each inductor (C2 in Figure 13) is simple. To complete the output filter, use a 0.47- $\mu F$  capacitor with a voltage rating at least twice the voltage applied to the output stage (PVDD).

This capacitor should be a good quality polyester dielectric such as a Wima MKS2-047ufd/100/10 or equivalent.

In order to minimize the EMI effect of unbalanced ripple loss in the inductors, 0.1- $\mu$ F, 50-V, SMD capacitors (X7R or better) (C1A and C1B in Figure 13) should be added from the output of each inductor to ground.

### THERMAL INFORMATION

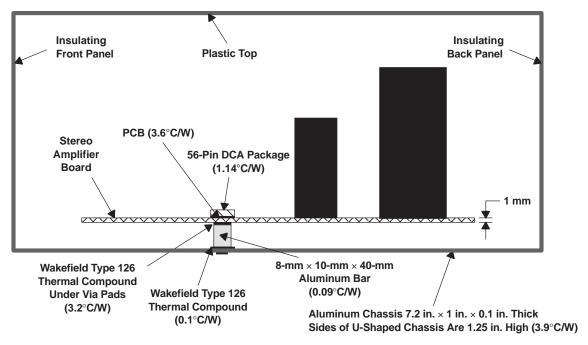

$R_{\theta JA}$  is a system thermal resistance from junction to ambient air. As such, it is a system parameter with roughly the following components:

- R<sub>θJC</sub> (the thermal resistance from junction to case, or in this case the metal pad)

- Thermal grease thermal resistance

- Heatsink thermal resistance

$R_{\theta JC}$  has been provided in the *Package Dissipation Ratings* section.

The thermal grease thermal resistance can be calculated from the exposed pad area and the thermal grease manufacturer's area thermal resistance (expressed in °C-in²/W). The area thermal resistance of the example thermal grease with a 0.002-inch-thick layer is about 0.1 °C-in²/W. The approximate exposed pad area is as follows:

56-pin HTSSOP 0.045 in<sup>2</sup>

Dividing the example thermal grease area resistance by the surface area gives the actual resistance through the thermal grease for both ICs inside the package:

56-pin HTSSOP 2.27 °C/W

The thermal resistance of thermal pads is generally considerably higher than a thin thermal grease layer. Thermal tape has an even higher thermal resistance. Neither pads nor tape should be used with either of these two packages. A thin layer of thermal grease with careful clamping of the heatsink is recommended. It may be difficult to achieve a layer 0.001 inch thick or less, so the modeling below is done with a 0.002-inch-thick layer, which may be more representative of production thermal grease thickness.

Heatsink thermal resistance is generally predicted by the heatsink vendor, modeled using a continuous flow dynamics (CFD) model, or measured.

Thus, for a single monaural IC, the system  $R_{\theta JA} = R_{\theta JC}$  + thermal grease resistance + heatsink resistance.

## DCA THERMAL INFORMATION

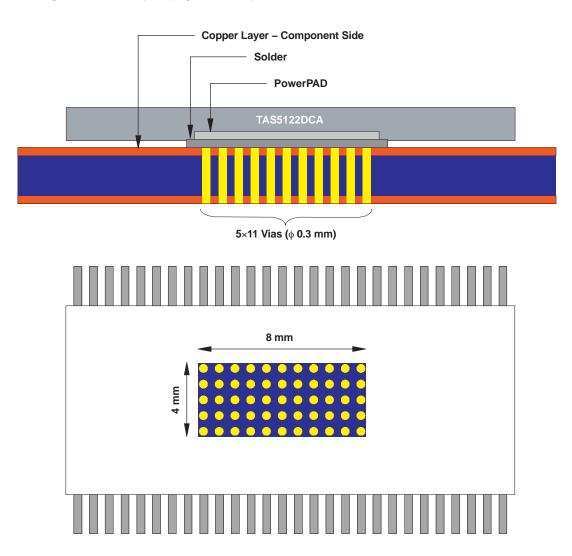

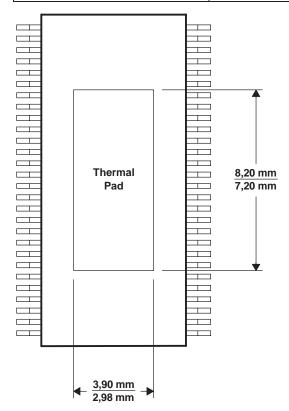

The thermally enhanced DCA package is based on the 56-pin HTSSOP, but includes a thermal pad (see Figure 15) to provide an effective thermal contact between the IC and the PCB.

The PowerPAD™ package (thermally enhanced HTSSOP) combines fine-pitch, surface-mount technology with thermal performance comparable to much larger power packages.

The PowerPAD package is designed to optimize the heat transfer to the PWB. Because of the small size and limited mass of an HTSSOP package, thermal enhancement is

achieved by improving the thermal conduction paths that remove heat from the component. The thermal pad is formed using a patented lead-frame design and manufacturing technique to provide a direct connection to the heat-generating IC. When this pad is soldered or otherwise thermally coupled to an external heat dissipater, high power dissipation in the ultrathin, fine-pitch, surface-mount package can be reliably achieved.

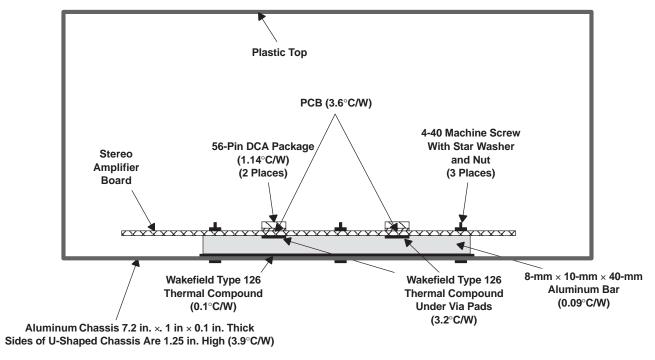

# Thermal Methodology for the DCA 56-Pin, $2\times15$ -W, $8-\Omega$ Package

The thermal design for the DCA part (e.g., thermal pad

soldered to the board) should be similar to the design in the following figures. The cooling approach is to conduct the dissipated heat into the via pads on the board, through the vias in the board, and into a heatsink (aluminum bar) (if necessary).

Figure 15 shows a recommended land pattern on the PCB.

Figure 15. Recommended Land Pattern

The lower via pad area, slightly larger than the IC pad itself, is exposed with a window in the solder resist on the bottom surface of the board. It is not coated with solder during the board construction to maintain a flat surface. In production, this can be accomplished with a peelable solder mask.

An aluminum bar is used to keep the through-hole leads

from shorting to the chassis. The thermal compound shown has a pad-to-aluminum bar thermal resistance of about 3.2°C/W.

The chassis provides the only heatsink to air and is chosen as representative of a typical production cooling approach.

Figure 16. 56-Pin DCA Package Cross-Sectional View (Side)

Figure 17. Spatial Separation With Multiple Packages

The land pattern recommendation shown in Figure 15 is for optimal performance with aluminum bar thermal resistance of 0.09°C/W. The following table shows the

decrease in thermal resistance through the PCB with a corresponding increase in the land pattern size. Use the table for thermal design tradeoffs.

| LAND PATTERN        | PCB THERMAL<br>RESISTANCE |  |  |

|---------------------|---------------------------|--|--|

| 7×13 vias (5×10 mm) | 2.2°C/W                   |  |  |

| 5×11 vias (4×8 mm)  | 3.6°C/W                   |  |  |

Figure 18. Thermal Pad Dimensions for DCA Package

### **CLICK AND POP REDUCTION**

TI modulators feature a pop and click reduction system that controls the timing when switching starts and stops.

Going from nonswitching to switching operation causes a spectral energy burst to occur within the audio bandwidth, which is heard in the speaker as an audible click, for instance, after having asserted RESET LH during a system start-up.

To make this system work properly, the following design rules must be followed when using the TAS5122 power stage:

- The relative timing between the PWM\_AP/M\_x signals and their corresponding VALID\_x signal should not be skewed by inserting delays, because this increases the audible amplitude level of the click.

- The output stage must start switching from a fully discharged output filter capacitor. Because

the output stage prior to operation is in the high-impedance state, this is done by having a passive pulldown resistor on each speaker output to GND (see *System Configuration Used for Characterization*).

Other things that can affect the audible click level:

- The spectrum of the click seems to follow the speaker impedance vs frequency curve—the higher the impedance, the higher the click energy.

- Crossover filters used between woofer and tweeter in a speaker can have high impedance in the audio band, which should be avoided if possible.

Another way to look at it is that the speaker impulse response is a major contributor to how the click energy is shaped in the audio band and how audible the click is.

The following mode transitions feature click and pop reduction in Texas Instruments PWM processors.

|                       | CLICK AND<br>POP REDUCED |                         |     |

|-----------------------|--------------------------|-------------------------|-----|

| Normal <sup>(1)</sup> | $\rightarrow$            | Mute                    | Yes |

| Mute                  | $\rightarrow$            | Normal(1)               | Yes |

| Normal(1)             | $\rightarrow$            | Error recovery (ERRCVY) | Yes |

| Error recovery        | $\rightarrow$            | Normal(1)               | Yes |

| Normal <sup>(1)</sup> | $\rightarrow$            | Hard reset              | No  |

| Hard reset            | $\rightarrow$            | Normal(1)               | Yes |

(1) Normal = switching

# **REFERENCES**

- TAS5000 Digital Audio PWM Processor data manual (SLAS270)

- True Digital Audio Amplifier TAS5001 Digital Audio PWM Processor data sheet (SLES009)

- 3. True Digital Audio Amplifier TAS5010 Digital Audio PWM Processor data sheet (SLAS328)

- 4. True Digital Audio Amplifier TAS5012 Digital Audio PWM Processor data sheet (SLES006)

- 5. TAS5026 Six-Channel Digital Audio PWM Processor data manual (SLES041)

- TAS5036A Six-Channel Digital Audio PWM Processor data manual (SLES061)

- 7. TAS3103 Digital Audio Processor With 3D Effects data manual (SLES038)

- 8. *Digital Audio Measurements* application report (SLAA114)

- System Design Considerations for True Digital Audio Power Amplifiers application report (SLAA117)

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TAS5122DCA       | ACTIVE     | HTSSOP       | DCA                | 56   | 35             | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5122                 | Samples |

| TAS5122DCAR      | ACTIVE     | HTSSOP       | DCA                | 56   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5122                 | Samples |

| TAS5122DCARG4    | ACTIVE     | HTSSOP       | DCA                | 56   | 2000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | 0 to 70      | TAS5122                 | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 14-Feb-2019

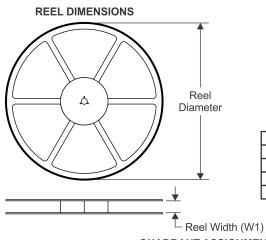

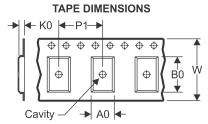

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

# \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TAS5122DCAR | HTSSOP          | DCA                | 56 | 2000 | 330.0                    | 24.4                     | 8.6        | 15.6       | 1.8        | 12.0       | 24.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Feb-2019

#### \*All dimensions are nominal

| I | Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---|-------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| I | TAS5122DCAR | HTSSOP       | DCA             | 56   | 2000 | 350.0       | 350.0      | 43.0        |  |

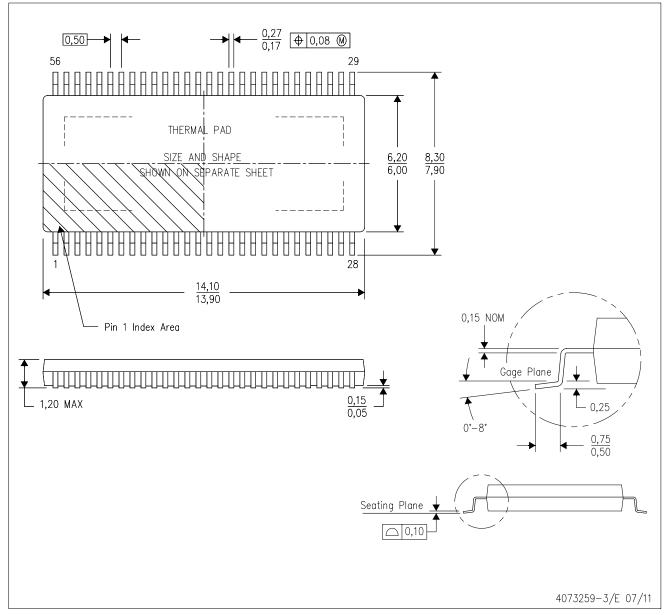

DCA (R-PDSO-G56)

# PowerPAD ™ PLASTIC SMALL-OUTLINE

NOTES:

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

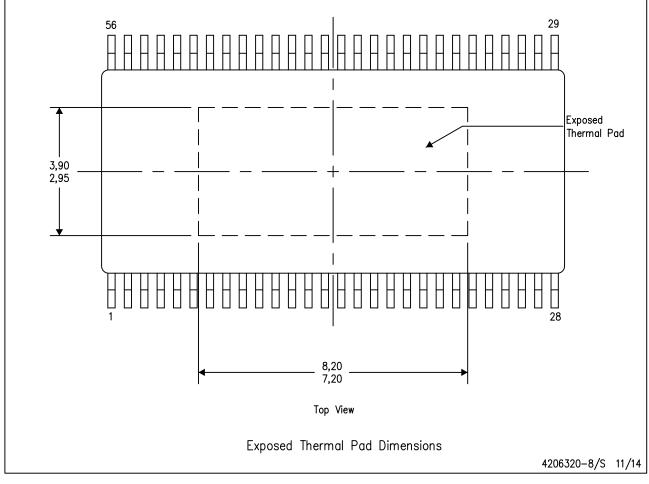

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# DCA (R-PDSO-G56)

PowerPAD™ PLASTIC SMALL OUTLINE

# THERMAL INFORMATION

This PowerPAD package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated