Order

Now

DS90C187

SNLS401C - FEBRUARY 2012 - REVISED SEPTEMBER 2018

# DS90C187 Low Power, 1.8-V Dual Pixel FPD-Link (LVDS) Serializer

Technical

Documents

#### Features

- 100 mW Typical Power Consumption at 185 MHz (SIDO Mode)

- Drives QXGA and WQXGA Class Displays

- Three Operating Modes:

- Single Pixel In, Single Pixel Out (SISO): 105 MHz Maximum

- Single Pixel In, Dual Pixel Out (SIDO): 185 MHz Maximum

- Dual Pixel In, Dual Pixel Out (DIDO): 105MHz

- Supports 24-Bit RGB, 48-Bit RGB

- Optional low Power Mode Supports 18-Bit RGB, 36-Bit RGB

- Supports 3D+C, 4D+C, 6D+C, 6D+2C, 8D+C, and 8D+2C LVDS Configurations

- Compatible With FPD-Link Deserializers

- Operates Off a Single 1.8-V Supply

- Interfaces Directly With 1.8-V LVCMOS

- Less Than 1 mW Power Consumption in Sleep • Mode

- Spread Spectrum Clock Compatible .

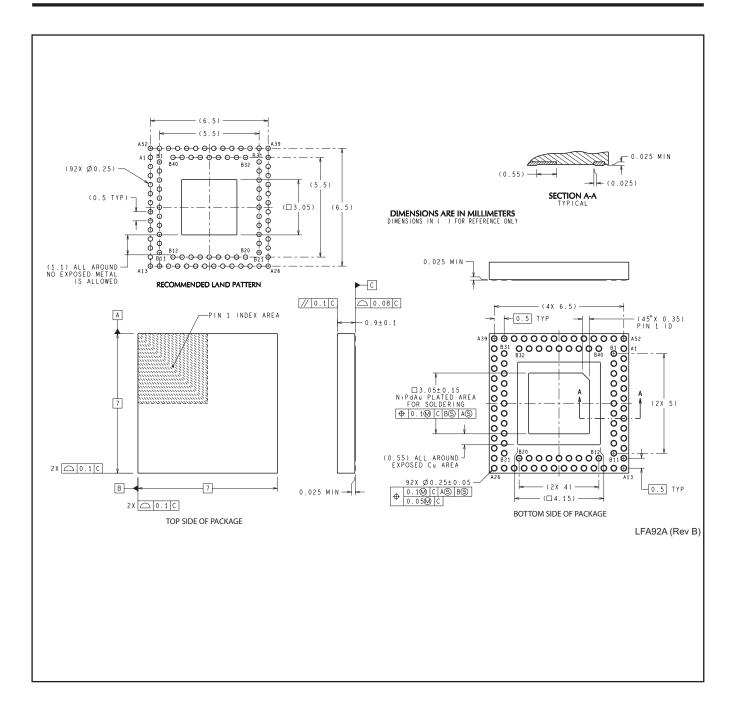

- Small 7-mm x 7-mm x 0.9-mm 92-Pin Dual Row VQFN Package

#### Applications 2

- Camera Monitor Systems (CMS)

- Automotive Head Units

- Smart Mirrors

- Cluster

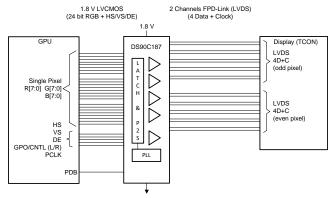

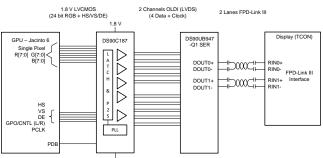

#### Typical Application

#### 3 Description

Tools &

Software

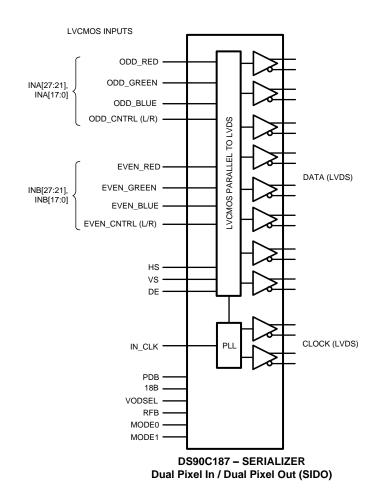

The DS90C187 is a low power Serializer for portable battery powered that reduces the size of the RGB interface between the host GPU and the Display.

Support &

Community

22

The DS90C187 Serializer is designed to support dual pixel data transmission between a Host and a Flat Panel Display at resolutions of up to QXGA (2048x1536) at 60 Hz. The transmitter converts up to 48 bits (Dual Pixel 24-bit color) of 1.8-V LVCMOS data into two channels of 4 data + clock (4D+C) reduced width interface LVDS compatible data streams.

DS90C187 supports 3 modes of operation.

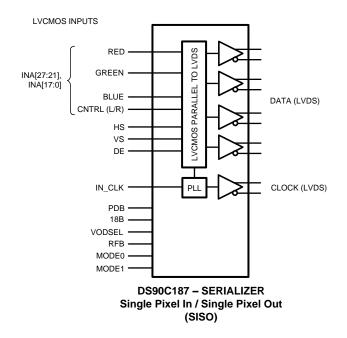

- In single pixel mode in/out mode, the device can drive up to SXGA+ (1400x1050) at 60 Hz. In this mode, the device converts one bank of 24-bit RGB data to a one channel 4D+C LVDS data stream.

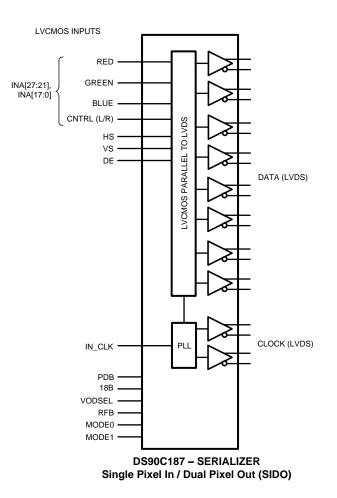

- In single pixel in / dual pixel out mode, the device can drive up to WUXGA+ (1920x1440) at 60 Hz. In this configuration, the device provides single-todual pixel conversion and converts one bank of 24-bit RGB data into two channels of 4D+C LVDS streams at half the pixel clock rate.

In dual pixel in / dual pixel out mode, the device can drive up to QXGA 2048x1536 at 60Hz or up to QSXGA 2560x2048 at 30Hz. In this mode, the device converts 2 channels of 24 bit RGB data into 2 channels of 4D+C LVDS streams. For all the modes, the device supports 18bpp and 24bpp color.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE      | BODY SIZE (NOM)   |

|-------------|--------------|-------------------|

| DS90C187    | VQFN-MR (92) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the order addendum at the end of the data sheet.

#### Typical Application

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Page

Page

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Des  | cription (continued) 3             |

| 6 | Pin  | Configuration and Functions 3      |

| 7 | Spe  | cifications5                       |

|   | 7.1  | Absolute Maximum Ratings 5         |

|   | 7.2  | ESD Ratings5                       |

|   | 7.3  | Recommended Operating Conditions 5 |

|   | 7.4  | Thermal Information 5              |

|   | 7.5  | Electrical Characteristics5        |

|   | 7.6  | Recommended Input Characteristics  |

|   | 7.7  | Switching Characteristics          |

|   | 7.8  | AC Timing Diagrams8                |

|   | 7.9  | Typical Characteristics 11         |

| 8 | Deta | ailed Description 12               |

|   | 8.1  | Overview 12                        |

|   | 8.2  | Functional Block Diagrams 12       |

|   |      |                                    |

|    | 8.3  | Device Functional Modes                         | . 15              |

|----|------|-------------------------------------------------|-------------------|

|    | 8.4  | Programming                                     | . 17              |

| 9  | App  | lication and Implementation                     | 24                |

|    | 9.1  | Application Information                         | . 24              |

|    | 9.2  | Typical Application                             | . 24              |

| 10 | Pow  | ver Supply Recommendations                      | 26                |

|    | 10.1 | Power Up Sequence                               | . 26              |

|    | 10.2 | Power Supply Filtering                          | . 26              |

| 11 | Lay  | out                                             | 27                |

|    | 11.1 | Layout Guidelines                               | . 27              |

|    | 11.2 | Layout Example                                  | . 28              |

| 12 | Dev  | ice and Documentation Support                   | 29                |

|    | 12.1 | Documentation Support                           | . 29              |

|    | 12.2 | Receiving Notification of Documentation Updates | ; <mark>29</mark> |

|    | 12.3 | Community Resources                             | . 29              |

|    | 12.4 | Trademarks                                      | . 29              |

|    | 12.5 | Electrostatic Discharge Caution                 | . 29              |

|    | 12.6 | Glossary                                        | . 29              |

| 13 | Мес  | hanical, Packaging, and Orderable               |                   |

|    |      | rmation                                         | 29                |

|    |      |                                                 |                   |

#### **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision B (April 2013) to Revision C

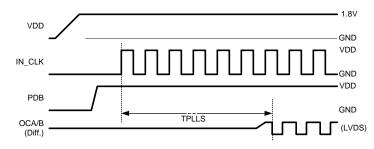

# Added Device Information table, Device Comparison table, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section......1 Added Start Up / Phase Lock Loop Set Time timing diagram 9 Added content to the Power Up Sequence section

#### Changes from Revision A (April 2013) to Revision B

Changed layout of National Data Sheet to TI format ......1

#### **5** Description (continued)

The DS90C187 is offered in a small 92 pin dual row VQFN package and features single 1.8 V supply for minimal power dissipation.

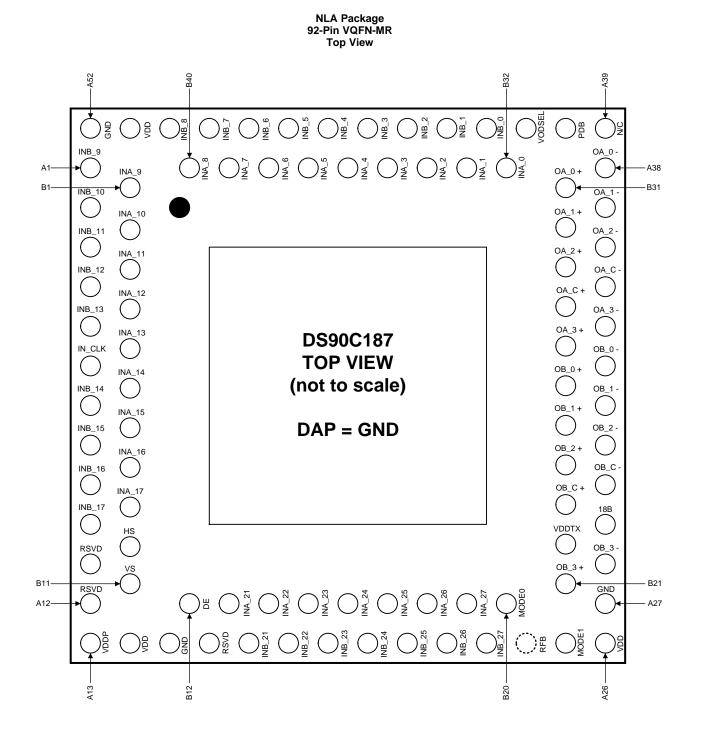

#### 6 Pin Configuration and Functions

DS90C187 SNLS401C-FEBRUARY 2012-REVISED SEPTEMBER 2018 Texas Instruments

# EMBER 2018 www.ti.com DS90C187 Pin Descriptions — Serializer

|                                                       |                                          | DS90C18 | 7 Pin Descriptions — Serializer                                                                                                                           |

|-------------------------------------------------------|------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                  | PIN NO.                                  | I/O     | DESCRIPTION                                                                                                                                               |

| 1.8-V LVCMOS VI                                       | DEO INPUTS                               |         |                                                                                                                                                           |

| INA_[27:21]<br>INA_[17:9]<br>NA_[8:0]                 | B19-B13,<br>B9-B1,<br>B40-B32            | I       | Channel A Data Inputs<br>Typically consists of 8 Red, 8 Green, 8 Blue and a general purpose or L/R control<br>bit.<br>Includes pull down.                 |

| INB_[27:21]<br>INB_[17:14],<br>INB_[13:9]<br>INB_[8:0 | A23-A17,<br>A10-A7,<br>A5-A1,<br>A50-A42 | I       | Channel B Data Inputs<br>Typically consists of 8 Red, 8 Green, 8 Blue and a general purpose or L/R control<br>bit.<br>Includes pull down.                 |

| HS (INA_18),<br>VS (INA_19),<br>DE (INA_20)           | B10,<br>B11<br>B12                       | I       | Video Control Signal Inputs -<br>HS = Horizontal Sync, VS = Vertical SYNC, and DE = Data Enable                                                           |

| IN_CLK                                                | A6                                       | I       | Pixel Input Clock<br>Includes pull down.                                                                                                                  |

| 1.8-V LVCMOS CO                                       | ONTROL INPUTS                            |         |                                                                                                                                                           |

| MODE0,<br>MODE1                                       | B20,<br>A25                              | I       | Mode Control Input (MODE0)<br>00 = Single In / Single Out<br>01 = Single In / Dual Out<br>10 = Dual In / Dual Out<br>11 = Reserved<br>Includes pull down. |

| RFB                                                   | A24                                      | I       | Rising / Falling Clock Edge Select Input -<br>0 = Falling Edge, 1 = Rising Edge<br>Includes pull down.                                                    |

| PDB                                                   | A40                                      | I       | Power Down (Sleep) Control Input -<br>0 = Sleep (Power Down mode), 1 = device active (enabled)<br>Includes pull down.                                     |

| 18B                                                   | A29                                      | I       | 18 bit / 24 bit Control Input -<br>0 = 24 bit mode,<br>1 = 18 bit mode<br>Includes pull down.                                                             |

| VODSEL                                                | A41                                      | I       | VOD Level Select Input -<br>0 = Low swing, 1 = Normal swing<br>Includes pull down.                                                                        |

| N/C                                                   | A39                                      | I       | no connect pin — leave open                                                                                                                               |

| RSVD                                                  | A11, A12, A16                            | I       | Reserved - Tie to Ground.                                                                                                                                 |

| LVDS OUTPUTS                                          |                                          |         |                                                                                                                                                           |

| OA_C+<br>OA_C-                                        | B28,<br>A35                              | 0       | Channel A LVDS Output Clock — Expects 100 $\Omega$ DC load.                                                                                               |

| OA_[3:0]+,<br>OA_[3:0]-                               | B27, B29-B31<br>A34, A36-A38             | 0       | Channel A LVDS Output Data — Expects 100 $\Omega$ DC load.                                                                                                |

| OB_C+,<br>OB_C-                                       | B23,<br>A30                              | 0       | Channel B LVDS Output Clock —<br>Expects 100 Ω DC load.                                                                                                   |

| OB_[3:0]+,<br>OB_[3:0]-                               | B21, B24-B26<br>A28, A16-A33             | 0       | Channel B LVDS Output Data —<br>Expects 100 Ω DC load.                                                                                                    |

| POWER AND GRO                                         | DUND                                     |         |                                                                                                                                                           |

| V <sub>DDTX</sub>                                     | B22                                      | Р       | Power supply for LVDS Drivers, 1.8V.                                                                                                                      |

| V <sub>DD</sub>                                       | A14, A26, A51                            | Р       | Power supply pin for core, 1.8V.                                                                                                                          |

| V <sub>DDP</sub>                                      | A13                                      | Р       | Power supply pin for PLL, 1.8V.                                                                                                                           |

| GND                                                   | A15, A27, A52                            | G       | Ground pins.                                                                                                                                              |

| DAP                                                   | DAP                                      | G       | Connect DAP to Ground plane.                                                                                                                              |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

See (1)

|                                         | MIN  | MAX       | UNIT |

|-----------------------------------------|------|-----------|------|

| Supply Voltage (V <sub>CC</sub> )       | -0.3 | 2.5       | V    |

| LVCMOS Input Voltage                    | -0.3 | VDD + 0.3 | V    |

| LVDS Driver Output Voltage              | -0.3 | 3.6       | V    |

| LVDS Output Short-Circuit Duration      | Con  | tinuous   |      |

| Junction Temperature                    |      | 150       | °C   |

| Storage Temperature (T <sub>stg</sub> ) | -65  | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±8000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1250 | V    |

|                    | Machine model           | ±250                                                                                  |       |      |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. [Following sentence optional; see the wiki.] Manufacturing with less than 500-V HBM is possible with the necessary precautions. [Following sentence optional; see the wiki.] Pins listed as ±XXX V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. [Following sentence optional; see the wiki.] Manufacturing with less than 250-V CDM is possible with the necessary precautions. [Following sentence optional; see the wiki.] Pins listed as ±YYY V may actually have higher performance.

#### 7.3 Recommended Operating Conditions

|                                                 | MIN  | NOM  | MAX  | UNIT              |

|-------------------------------------------------|------|------|------|-------------------|

| Supply Voltage                                  | 1.71 | 1.80 | 1.89 | V                 |

| Operating Free Air Temperature (T <sub>A)</sub> | -10  | +25  | +70  | °C                |

| Differential Load Impedance                     | 80   | 100  | 120  | Ω                 |

| Supply Noise Voltage                            |      |      | <90  | mV <sub>p-p</sub> |

#### 7.4 Thermal Information

|                       |                                                       | DS90C187      |      |

|-----------------------|-------------------------------------------------------|---------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                         | NLA (VQFN-MR) | UNIT |

|                       |                                                       | 92 PINS       |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance <sup>(2)</sup> | 35.1          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance             |               | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                  |               | °C/W |

| ΨJT                   | Junction-to-top characterization parameter            |               | °C/W |

| Ψјв                   | Junction-to-board characterization parameter          |               | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance          |               | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Above +22°C

#### 7.5 Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

| PARAMETER                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------|-----------------|-----|-----|-----|------|

| LVCMOS DC SPECIFICATIONS |                 |     |     |     |      |

Copyright © 2012–2018, Texas Instruments Incorporated

NSTRUMENTS

Texas

# **Electrical Characteristics (continued)**

| Over recommended | operating supply | and temperature ranges | s unless otherwise specified. |

|------------------|------------------|------------------------|-------------------------------|

|                  |                  |                        |                               |

|                 | PARAMETER                                                        | TEST C                                                                                                                         | CONDITIONS                                                 | MIN                 | TYP          | MAX             | UNIT                       |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------|--------------|-----------------|----------------------------|

| V <sub>IH</sub> | High Level Input Voltage                                         |                                                                                                                                |                                                            | 0.65V <sub>DD</sub> |              | V <sub>DD</sub> | V                          |

| VIL             | Low Level Input Voltage                                          |                                                                                                                                |                                                            | GND                 |              | $0.35V_{DD}$    | V                          |

| I <sub>IN</sub> | Input Current                                                    | $V_{IN} = 0V \text{ or } V_{DD} = 0$                                                                                           | 1.71 V to 1.89 V                                           | -10                 | ±1           | +10             | μA                         |

|                 | RIVER DC SPECIFICATIONS                                          |                                                                                                                                |                                                            |                     |              | 1               |                            |

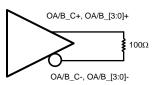

| V <sub>OD</sub> | Differential Output Voltage                                      | R <sub>L</sub> = 100Ω                                                                                                          | VODSEL = V <sub>IH</sub>                                   | 160<br>(320)        | 300<br>(600) | 450<br>(900)    | mV<br>(mV <sub>P-P</sub> ) |

| VOD             | Dinerential Ouput Voltage                                        | Figure 3                                                                                                                       | $VODSEL = V_{IL}$                                          | 110<br>(220)        | 180<br>(360) | 300<br>(600)    | mV<br>(mV <sub>P-P</sub> ) |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between<br>Complimentary Output States | R <sub>L</sub> = 100Ω<br>Figure 3                                                                                              |                                                            |                     |              | 50              | mV                         |

| V <sub>OS</sub> | Offset Voltage                                                   | R <sub>L</sub> = 100Ω<br>Figure 3                                                                                              | igure 3                                                    |                     | 0.9          | 1.0             | V                          |

| $\Delta V_{OS}$ | Change in V <sub>OS</sub> between<br>Complimentary Output States | R <sub>L</sub> = 100Ω<br>Figure 3                                                                                              |                                                            |                     |              | 50              | mV                         |

| I <sub>OS</sub> | Output Short Circuit Current                                     | $V_{OUT} = GND, VOD$                                                                                                           | SEL = V <sub>DD</sub>                                      | -45                 | -35          | -25             | mA                         |

| SUPPLY          | CURRENT                                                          | - 1                                                                                                                            |                                                            |                     |              |                 |                            |

| IDDT1           |                                                                  | Checkerboard<br>pattern,<br>$R_L = 100 \Omega$ ,<br>$18B = V_{IL}$ ,<br>$VODSEL = V_{IH}$ ,<br>$V_{DD} = 1.89 V$ ,<br>Figure 1 | f = 105 MHz,<br>MODE[1:0] = 00<br>(SISO)                   |                     | 60           | 85              | mA                         |

| IDDT2           | Serializer Worst Case Supply<br>Current (includes load current)  |                                                                                                                                | f = 185 MHz,<br>MODE[1:0] = 01<br>(SIDO)                   |                     | 95           | 140             | mA                         |

| IDDT3           |                                                                  |                                                                                                                                | f = 105 MHz,<br>MODE[1:0] = 10<br>(DIDO)                   |                     | 100          | 150             | mA                         |

|                 |                                                                  | MODE[1:0] = 01<br>(SIDO),<br>f = 150 MHz,                                                                                      | $18B = V_{IL},$<br>VODSEL = V <sub>IL</sub> ,<br>VDD = 1.8 |                     | 55           |                 | mA                         |

|                 |                                                                  |                                                                                                                                | $18B = V_{IL},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8 |                     | 75           |                 | mA                         |

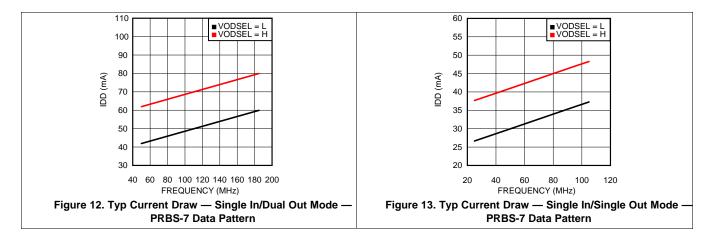

| IDDTP           | Serializer Supply Current PRBS-7                                 | $R_L = 100 \Omega$ ,<br>PRBS-7 Pattern<br>Figure 12                                                                            | $18B = V_{IH},$<br>VODSEL = V <sub>IL</sub> ,<br>VDD = 1.8 |                     | 49           |                 | mA                         |

|                 |                                                                  |                                                                                                                                | $18B = V_{IH},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8 |                     | 65           |                 | mA                         |

|                 |                                                                  |                                                                                                                                | $18B = V_{IL},$<br>VODSEL = V <sub>IL</sub> ,<br>VDD = 1.8 |                     | 53           |                 | mA                         |

| IDDTG           | Serializer Supply Current 16                                     | MODE[1:0] = 01<br>(SIDO),<br>f = 150 MHz,                                                                                      | $18B = V_{IL},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8 |                     | 71           |                 | mA                         |

|                 | Grayscale                                                        | $R_L = 100 \Omega,$<br>16 Grayscale<br>Pattern                                                                                 | $18B = V_{IH},$<br>VODSEL = V <sub>IL</sub> ,<br>VDD = 1.8 |                     | 48           |                 | mA                         |

|                 |                                                                  |                                                                                                                                | $18B = V_{IH},$<br>VODSEL = V <sub>IH</sub> ,<br>VDD = 1.8 |                     | 63           |                 | mA                         |

| IDDZ            | Power Down Supply Current                                        | PDB = GND                                                                                                                      |                                                            |                     | 18           | 200             | μA                         |

#### 7.6 Recommended Input Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

|      | PARAMETER                     |                      |       | TYP  | MAX   | UNIT |

|------|-------------------------------|----------------------|-------|------|-------|------|

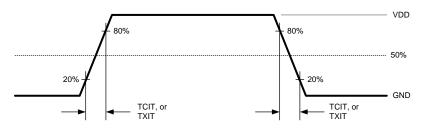

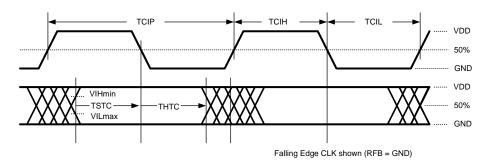

| тсіт | IN_CLK Transition Time        | MODE[1:0] = 00 or 10 | 1     | Т    | 4     | ns   |

|      | Figure 5                      | MODE[1:0] = 01       | 1     |      | 2     | ns   |

| TCIP | IN_CLK Period<br>Figure 6     | MODE[1:0] = 00 or 10 | 9.53  | Т    | 40    | ns   |

|      |                               | MODE[1:0] = 01       | 5.40  | Т    | 20    | ns   |

| TCIH | IN_CLK High Time              | See Figure 6         | 0.35T | 0.5T | 0.65T | ns   |

| TCIL | IN_CLK Low Time               | See Figure 6         | 0.35T | 0.5T | 0.65T | ns   |

| TXIT | INA_x & INB_x Transition Time | See Figure 5         | 1.5   |      | 0.3T  | ns   |

#### 7.7 Switching Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

| PARAMETER |                                                             | MIN TYF                                     | MAX               | UNIT  |    |

|-----------|-------------------------------------------------------------|---------------------------------------------|-------------------|-------|----|

| TSTC      | INn_x Setup to IN_CLK                                       | See Figure 6                                | 0                 |       | ns |

| THTC      | INn_x Hold from IN_CLK                                      | See Figure 6                                | 2.5               |       | ns |

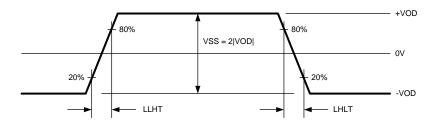

| LLHT      | LVDS Low-to-High Transition Time<br>Figure 4 <sup>(1)</sup> |                                             | 0.18              | 0.5   | ns |

| LHLT      | LVDS High-to-Low Transition Time<br>Figure 4 <sup>(1)</sup> |                                             | 0.18              | 0.5   | ns |

| твіт      | LVDS Output Bit Width                                       | MODE[1:0] = 00, or 10                       | 1/7 TCIF          | )     | ns |

| IDII      |                                                             | MODE[1:0] = 01                              | 2/7 TCIF          | •     | ns |

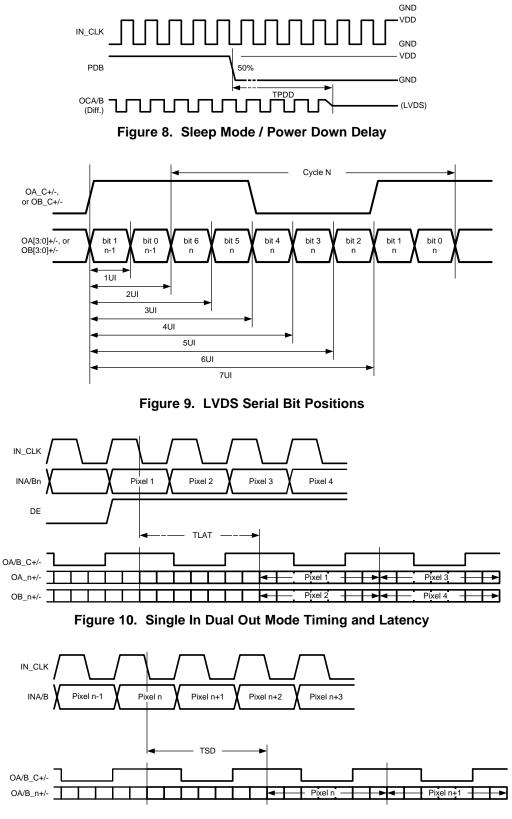

| TPPOS0    | Transmitter Output Pulse Positions Normalized<br>for Bit 0  | See Figure 9                                | 1                 |       | UI |

| TPPOS1    | Transmitter Output Pulse Positions Normalized<br>for Bit 1  | See Figure 9                                | 2                 | 2     | UI |

| TPPOS2    | Transmitter Output Pulse Positions Normalized<br>for Bit 2  | See Figure 9                                | 3                 | 5     | UI |

| TPPOS3    | Transmitter Output Pulse Positions Normalized<br>for Bit 3  | See Figure 9                                | 2                 | Ļ     | UI |

| TPPOS4    | Transmitter Output Pulse Positions Normalized<br>for Bit 4  | See Figure 9                                | 5                 | ;     | UI |

| TPPOS5    | Transmitter Output Pulse Positions Normalized<br>for Bit 5  | See Figure 9                                | 6                 | ;     | UI |

| TPPOS6    | Transmitter Output Pulse Positions Normalized<br>for Bit 6  | See Figure 9                                | 7                 |       | UI |

| ΔTPPOS    | Variation in Transmitter Pulse Position (Bit 6 — Bit 0)     | See Figure 9                                | ±0.06             | ;     | UI |

| TCCS      | LVDS Channel to Channel Skew                                |                                             | 110               | )     | ps |

| TJCC      | Jitter Cycle-to-Cycle                                       | MODE0, MODE1 = 0,<br>f = 105 MHz,<br>(1)    | 0.028             | 0.035 | UI |

| TPLLS     | Phase Lock Loop Set (Enable Time)                           | Figure 7                                    |                   | 1     | ms |

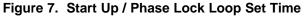

| TPDD      | Powerdown Delay                                             | Figure 8                                    |                   | 100   | ns |

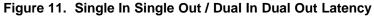

| TSD       | Latency Delay                                               | MODE0 = 0,<br>MODE1 = 1 or 0<br>Figure 10   | 2*TCIP +<br>10.54 | -     | ns |

| TLAT      | Latency Delay for Single Pixel In / Dual Pixel Out Mode     | MODE0 = 1,<br>MODE1 = 0<br>Figure 10<br>(1) | 9*TCIP +<br>4.19  |       | ns |

(1) Parameter is ensured by characterization and is not tested at final test.

(2) Parameter is ensured by design and is not tested at final test.

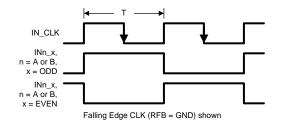

#### 7.8 AC Timing Diagrams

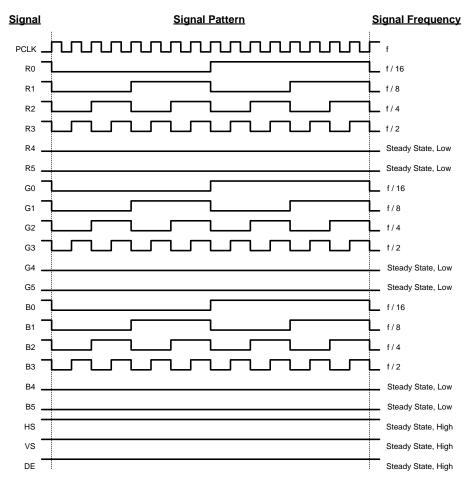

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

- B. Figure 1 and Figure 2 show a falling edge data strobe (IN\_CLK).

Figure 1. Checker Board Test Pattern

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

- B. Recommended pin to signal mapping for 18 bits per pixel, customer may choose to define differently. The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

- C. Figure 2 shows a falling edge data strobe (IN\_CLK).

#### Figure 2. "16 Gray Scale" Test Pattern (Falling Edge Clock shown)

8

#### AC Timing Diagrams (continued)

Figure 3. DS90C187 (Transmitter) LVDS Output Load

Figure 4. LVDS Output Transition Times

Figure 5. LVCMOS Input Transition Times

Figure 6. LVCMOS Input Setup/Hold and Clock High/Low Times (Falling Edge Strobe)

#### AC Timing Diagrams (continued)

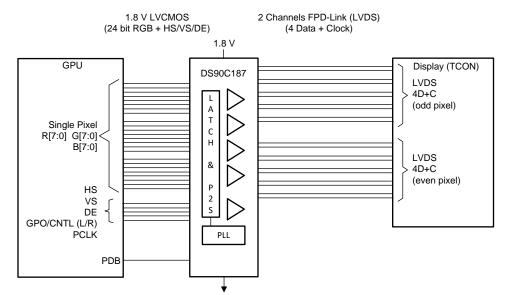

#### 7.9 Typical Characteristics

#### 8 Detailed Description

#### 8.1 Overview

DS90C187 converts a wide parallel LVCMOS input bus into banks of FPD-Link LVDS data. The device can be configured to support RGB-888 (24-bit color) or RGB-666 (18 bit color) in three main configurations: single pixel in / single pixel out; single pixel out; dual pixel out; dual pixel in / dual pixel out. The DS90C187 has several power saving features including: selectable VOD, 18 bit / 24 bit mode select, and a power down pin control.

#### 8.2 Functional Block Diagrams

## **Functional Block Diagrams (continued)**

#### **Functional Block Diagrams (continued)**

#### 8.3 Device Functional Modes

#### 8.3.1 Device Configuration

The MODE0 and MODE1 pins are used to configure the DS90C187 into the three main operation modes as shown in the table below.

| MODE1 | MODE0 | CONFIGURATION                                  |

|-------|-------|------------------------------------------------|

| 0     | 0     | Single Pixel Input, Single Pixel Output (SISO) |

| 0     | 1     | Single Pixel Input, Dual Pixel Output (SIDO)   |

| 1     | 0     | Dual Pixel Input, Dual Pixel Output (DIDO)     |

| 1     | 1     | RESERVED                                       |

#### Table 1. Mode Configurations

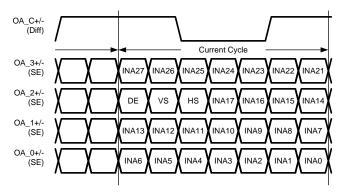

#### 8.3.2 Single Pixel Input / Single Pixel Output

When MODE0 and MODE1 are both set to low, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- with OA\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- is powered down and the corresponding LVCMOS input signals are ignored.

In this configuration IN\_CLK can range from 25 MHz to 105 MHz, resulting in a total maximum payload of 700 Mbps (28 bits \* 25MHz) to 2.94 Gbps (28 bits \* 105 MHz). Each LVDS driver will operate at a speed of 7 bits per input clock cycle, resulting in a serial line rate of 175 Mbps to 735 Mbps. OA\_C+/- will operate at the same rate as IN\_CLK with a duty cycle ratio of 57:43.

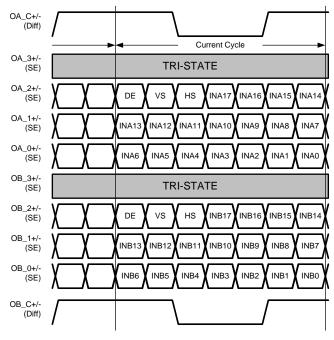

#### 8.3.3 Single Pixel Input / Dual Pixel Output

When MODE0 is HIGH and MODE1 is LOW, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- and OB\_[3:0]+/- with OA\_C+/- and OB\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- and OB\_3+/- are powered down and the corresponding LVCMOS input signals are ignored. The input LVCMOS data is split into odd and even pixels starting with the odd (first) pixel outputs OA\_[3:0]+/- and then the even (second) pixel outputs OB\_[3:0]+/-. The splitting of the data signals starts with DE (data enable) transitioning from logic LOW to HIGH indicating active data (see Figure 10). The number of clock cycles during blanking must be an EVEN number. This configuration will allow the user to interface with two FPD-Link receivers or other dual pixel inputs.

In this configuration IN\_CLK can range from 50 MHz to 185 MHz, resulting in a total maximum payload of 1.4 Gbps (28 bits \* 50 MHz) to 5.18 Gbps (28 bits \* 185 MHz). Each LVDS driver will operate at a speed of 7 bits per 2 input clock cycles, resulting in a serial line rate of 175 Mbps to 647.5 Mbps. OA\_C+/- and OA\_B+/- will operate at ½ the rate as IN\_CLK with a duty cycle ratio of 57:43.

- 1. Disable the clock and data.

- 2. Toggle PDB to Low and then High.

- 3. After PDB settles reset the data pattern and enable the clock and data.

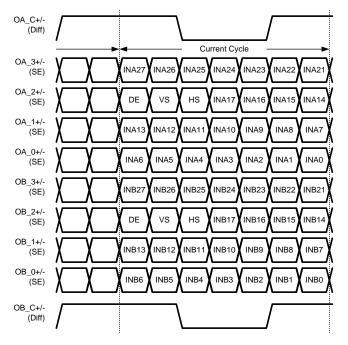

#### 8.3.4 Dual Pixel Input / Dual Pixel Output

When MODE0 is LOW and MODE1 is set to HIGH, data from INA\_[27:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- with OA\_C+/-, while data from INB\_[27:0], HS, VS and DE is serializer and driven out on OB\_[3:0]+/- with OB\_C+/-. If 18B\_MODE is LOW, then OA\_3+/- and OB\_3+/- is powered down and the corresponding LVCMOS input signals are ignored.

In this configuration IN\_CLK can range from 25 MHz to 105 MHz, resulting in a total maximum payload of 1.325 Gbps (53 bits \* 25 MHz) to 5.565 Gbps (53 bits \* 105 MHz). Each LVDS driver will operate at a speed of 7 bits per input clock cycle, resulting in a serial line rate of 175 Mbps to 735 Mbps. OA\_C+/- and OB\_C+/- will operate at the same rate as IN\_CLK with a duty cycle ratio of 57:43.

#### 8.3.5 Pixel Clock Edge Select (RFB)

The RFB pin determines the edge that the input LVCMOS data is latched on. If RFB is HIGH, input data is latched on the RISING EDGE of the pixel clock (IN\_CLK). If RFB is LOW, the input data is latched on the FALLING EDGE of the pixel clock. Note: This can be set independently of receiver's output clock strobe.

#### TEXAS INSTRUMENTS

www.ti.com

#### Table 2. Pixel Clock Edge

| RFB | Result       |  |

|-----|--------------|--|

| 0   | FALLING edge |  |

| 1   | RISING edge  |  |

#### 8.3.6 Power Management

The DS90C187 has several features to assist with managing power consumption. The device can be configured through the MODE0 and MODE1 control pins to enable only the required number of LVDS drivers for each application. The 18B\_MODE pin allows the DS90C187 to power down the unused LVDS driver(s) for RGB-666 (18 bit color) applications for an additional level of power management. If no clock is applied to the IN\_CLK pin, the DS90C187 will enter a low power state. To place the DS90C187 in its lowest power state, the device can be powered down by driving the PDB pin to LOW.

#### 8.3.7 Sleep Mode (PDB)

The DS90C187 provides a power down feature. When the device has been powered down, current draw through the supply pins is minimized and the PLL is shut down. The LVDS drivers are also powered down with their outputs pulled to GND through  $100-\Omega$  resistors (not tri-stated).

| Table 3. | Power Dow | vn Select |

|----------|-----------|-----------|

|----------|-----------|-----------|

| PDB | Result               |

|-----|----------------------|

| 0   | SLEEP Mode (default) |

| 1   | ACTIVE (enabled)     |

#### 8.3.8 LVDS Outputs

The DS90C187's LVDS drivers are compatible with ANSI/TIA/EIA-644-A LVDS receivers. The LVDS drivers can output a power saving low  $V_{OD}$ , or a high  $V_{OD}$  to enable longer trace and cable lengths by configuring the VODSEL pin.

| Table | 4. | VOD | Select |

|-------|----|-----|--------|

|       |    |     |        |

| VODSEL | Result             |

|--------|--------------------|

| 0      | ±220 mV (440 mVpp) |

| 1      | ±340 mV (680 mVpp) |

Any unused LVDS outputs that are not powered down or put into TRI-STATE® due to the MODE0, MODE1, or 18B pins should be externally terminated differentially with a 100 ohm resistor. For example, when driving a timing controller (TCON) that only requires an 8D + C LVDS interface, rather than 8D + 2C, the unused clock line should be terminated near the package of the DS90C187. For more information regarding the output state of unused LVDS drivers, refer to the next section, 18 bit / 24 bit Color Mode (18B). For more information regarding the electrical characteristics of the LVDS outputs, refer to the LVDS DC Characteristics and LVDS Switching Specifications.

#### 8.3.9 18 bit / 24 bit Color Mode (18B)

The 18B pin can be used to further save power by powering down the 4th LVDS driver in each used bank when the application requires only 18 bit color or 3D+C LVDS. Set the 18B pin to logic HIGH to TRI-STATE® OA\_3+/- and OB\_3+/- (if the device is configured for dual pixel output). For 24 bit color applications this pin should be set to logic LOW. Note that the power down function takes priority over the TRI-STATE® function. So if the device is configured for 18 bit color Single Pixel In/Single Pixel Out, LVDS channel OB\_3+/- will be powered down and not TRI-STATE®. If an LVDS driver is powered down, each output terminal is pulled low by a 100 ohm resistor to ground.

| 18B | Result                    |

|-----|---------------------------|

| 0   | 24bpp, LVDS 4D+C or 8D+2C |

| 1   | 18bpp, LVDS 3D+C or 6D+2C |

#### 8.3.10 LVCMOS Inputs

The DS90C187 has two banks of 24 data inputs, one set of video control signal (HS, VS and DE) inputs and several device configuration LVCMOS pins. All LVCMOS input pins are designed for 1.8 V LVCMOS logic. All LVCMOS inputs, including clock, data and configuration pins, have an internal pull down resistor to set a default state. If any inputs are unused, they can be left as no connect (NC) or connected to ground.

#### 8.4 Programming

#### 8.4.1 LVDS Interface / TFT Color Data Recommended Mapping

Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application. The DS90C187 supports three modes of operation for single and dual pixel applications supporting either 24bpp or 18bpp color depths.

Copyright © 2012–2018, Texas Instruments Incorporated

#### **Programming (continued)**

In the Dual Pixel / 24bpp mode, eight LVDS data lines are provided along with two LVDS clock lines (8D+2C). The Deserializer may utilize one or two clock lines. The 53 bit interface typically assigns 24 bits to RGB for the odd pixel, 24 bits to RGB for the even pixel, 3 bits for the video control signals (HS, VS and DE), 1 bit for odd pixel and 1 bit for even pixel which can be ignored or used for general purpose data, control or L/R signaling.

A reduced width input interface is also supported with a Single-to-Dual Pixel conversion where the data is presented at double rate (same clock edge, 2X speed, see ) and the DE transition is used to flag the first pixel. Also note in both 8D+2C configurations, the three video control signals are sent over **both** the A and B outputs. The DES / TCON may recover one set, or both depending upon its implementation. The Dual Pixel / 24bpp 8D+2C LVDS Interface Mapping is shown in .

A Dual Pixel / 18bpp mode is also supported. In this configuration OA3 and OB3 LVDS output channels are placed in TRI-STATE® to save power. Their respective inputs are ignored. (Figure 15)

In the Single Pixel / 24bpp mode, four LVDS data lines are provided along with a LVDS clock line (4D+C). The 28 bit interface typically assigns 24 bits to RGB color data, 3 bits to video control (HS, VS and DE) and one spare bit can be ignored, used for L/R signaling or function as a general purpose bit. The Single Pixel / 24bpp 4D+C LVDS Interface Mapping is shown in .

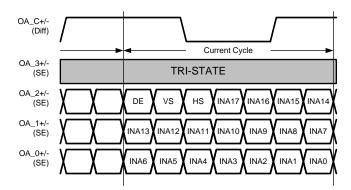

A Single Pixel / 18bpp mode is also supported. In this configuration the OA3 LVDS output channel is placed in TRI-STATE® to save power. Its respective inputs are ignored. (Figure 17)

Figure 14. Dual Pixel / 24bpp LVDS Mapping

#### **Programming (continued)**

Figure 15. Dual Pixel / 18bpp LVDS Mapping

Figure 16. Single Pixel / 24bpp LVDS Mapping

#### **Programming (continued)**

#### 8.4.1.1 Color Mapping Information

A defacto color mapping is shown next. Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application.

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_22         | R7            | MSB             |

| INA_21         | R6            |                 |

| INA_5          | R5            |                 |

| INA_4          | R4            |                 |

| INA_3          | R3            |                 |

| INA_2          | R2            |                 |

| INA_1          | R1            |                 |

| INA_0          | R0            | LSB             |

| INA_24         | G7            | MSB             |

| INA_23         | G6            |                 |

| INA_11         | G5            |                 |

| INA_10         | G4            |                 |

| INA_9          | G3            |                 |

| INA_8          | G2            |                 |

| INA_7          | G1            |                 |

| INA_6          | G0            | LSB             |

| INA_26         | B7            | MSB             |

| INA_25         | B6            |                 |

| INA_17         | B5            |                 |

| INA_16         | B4            |                 |

| INA_15         | B3            |                 |

| INA_14         | B2            |                 |

| INA_13         | B1            |                 |

| INA_12         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

#### Table 6. Single Pixel Input / 24bpp / MSB on CH3

#### Table 7. Single Pixel Input / 24bpp / LSB on CH3

| DS90C187 Input | Color Mapping | Note |

|----------------|---------------|------|

| INA_5          | R7            | MSB  |

| INA_4          | R6            |      |

| INA_3          | R5            |      |

| INA_2          | R4            |      |

| INA_1          | R3            |      |

| INA_0          | R2            |      |

| INA_22         | R1            |      |

| INA_21         | R0            | LSB  |

| INA_11         | G7            | MSB  |

| INA_10         | G6            |      |

| INA_9          | G5            |      |

#### Table 7. Single Pixel Input / 24bpp / LSB on CH3 (continued)

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_8          | G4            |                 |

| INA_7          | G3            |                 |

| INA_6          | G2            |                 |

| INA_24         | G1            |                 |

| INA_23         | G0            | LSB             |

| INA_17         | B7            | MSB             |

| INA_16         | B6            |                 |

| INA_15         | B5            |                 |

| INA_14         | B4            |                 |

| INA_13         | B3            |                 |

| INA_12         | B2            |                 |

| INA_26         | B1            |                 |

| INA_25         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

#### Table 8. Single Pixel Input / 18bpp

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| INA_5          | R5            | MSB             |

| INA_4          | R4            |                 |

| INA_3          | R3            |                 |

| INA_2          | R2            |                 |

| INA_1          | R1            |                 |

| INA_0          | R0            | LSB             |

| INA_11         | G5            | MSB             |

| INA_10         | G4            |                 |

| INA_9          | G3            |                 |

| INA_8          | G2            |                 |

| INA_7          | G1            |                 |

| INA_6          | G0            | LSB             |

| INA_17         | B5            | MSB             |

| INA_16         | B4            |                 |

| INA_15         | B3            |                 |

| INA_14         | B2            |                 |

| INA_13         | B1            |                 |

| INA_12         | B0            |                 |

| DE             | DE            | Data Enable*    |

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

#### Table 9. Dual Pixel Input / 24bpp

| DS90C187 Input | Color Mapping | Note |

|----------------|---------------|------|

| INA_22         | O_R7          | MSB  |

| INA_21         | O_R6          |      |

| DS90C187 Input   | Color Mapping | Note         |

|------------------|---------------|--------------|

| INA_5            | O_R5          |              |

| INA_4            | O_R4          |              |

| INA_3            | O_R3          |              |

| INA_2            | 0_R2          |              |

| INA_1            | O_R1          |              |

| INA_0            | O_R0          | LSB          |

| INA_24           | O_G7          | MSB          |

| INA_23           | O_G6          |              |

| INA_11           | O_G5          |              |

| INA_10           | O_G4          |              |

| INA_9            | O_G3          |              |

| INA_8            | O_G2          |              |

| INA_7            | O_G1          |              |

| <br>INA_6        | <br>O_G0      | LSB          |

| INA_26           | O_B7          | MSB          |

| INA_25           | O_B6          |              |

| INA_17           | O_B5          |              |

| <br>INA 16       | O B4          |              |

| INA 15           | O B3          |              |

| INA_14           | O_B2          |              |

| INA_13           | 0_B1          |              |

| INA_12           | O_B0          |              |

| INB_22           | E R7          |              |

| INB_21           | E_R6          |              |

| INB_5            | E_R5          |              |

| INB_4            | E_R4          |              |

| INB_3            | E_R3          |              |

| INB_2            | E R2          |              |

| INB_1            | E_R1          |              |

| INB_0            | E_R0          |              |

| INB_24           | E_G7          |              |

| INB_23           | E_G6          |              |

| INB_11           | E_G5          |              |

| INB_10           | E_G4          |              |

| INB_9            | E G3          |              |

| INB_8            | E_G2          |              |

| INB_7            | E_G1          |              |

| INB_6            | E_G0          |              |

| INB_26           | E_B7          |              |

| INB_25           | E_B6          |              |

| INB_23<br>INB_17 | E_B5          |              |

| INB_17<br>INB_16 | E_B3          |              |

|                  |               |              |

| INB_15           | E_B3          |              |

| INB_12           | E_B2          |              |

| INB_13           | E_B1          |              |

| INB_12           | E_B0          | Data English |

| DE               | DE            | Data Enable* |

#### Table 9. Dual Pixel Input / 24bpp (continued)

| DS90C187 Input | Color Mapping | Note            |

|----------------|---------------|-----------------|

| VS             | VS            | Vertical Sync   |

| HS             | HS            | Horizontal Sync |

| INA_27         | GP            | General Purpose |

| INB_27         | GP            | General Purpose |

#### Table 9. Dual Pixel Input / 24bpp (continued)

23

TEXAS INSTRUMENTS

www.ti.com

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The DS90C187 is a Low Power Bridge for automotive application that reduces the size of the RGB interface between the host GPU and the Display. It is designed to support single pixel data transmission between Host and Flat Panel Display up to QXGA (2048x1536) at 60 Hz resolutions. The transmitter converts up to 24 bits (Single Pixel 24 bit color) of 1.8-V LVCMOS data into two channels of 4 data + clock (4D+C) reduced width interface LVDS compatible data streams.

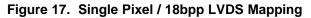

#### 9.2 Typical Application

Figure 18. Single Pixel In Dual Pixel Out (SIDO) Mode

#### 9.2.1 Design Requirements

The DS90C187 is used to convert 24-bit color to two channels of LVDS datastreams.

#### Table 10. Design Parameters

| DESIGN PARAMETER | VALUE         |

|------------------|---------------|

| Supply           | 1.8V          |

| Display Driven   | SXGA+, WUXGA+ |

| Pixel Depth      | 24 bits       |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 LVDS Interconnect Guidelines

Refer to the AN-1108 Channel-Link PCB and Interconnect Design-In Guidelines (SNLA008) and Transmission Line RAPIDESIGNER Operation and Applications Guide (SNLA035) for full details.

- Use 100-Ω coupled differential pairs

- Use differential connectors when above 500 Mbps

- Minimize skew within the pair

- Use the S/2S/3S rule in spacings

- S = space between the pairs

- 2S = space between pairs

- 3S = space to LVCMOS signals

- Place ground vias next to signal vias when changing between layers

- When a signal changes reference planes, place a bypass cap and vias between the new and old reference plane

For more tips and detailed suggestions regarding high speed board layout principles, see the LVDS Owner's Manual at http://www.ti.com/lvds

#### 9.2.3 Application Curves

#### **10** Power Supply Recommendations

#### **10.1** Power Up Sequence

The  $V_{DD}$  power supply pins do not require a specific power on sequence and can be powered on in any order. However, the PDB pin should only be set to logic HIGH once the power sent to all supply pins is stable. Active data inputs should not be applied to the DS90C187 until all of the input power pins have been powered on, settled to the recommended operating voltage and the PDB pin has be set to logic HIGH.

The user experience can be impacted by the way a system powers up and powers down an LCD screen. The following sequence is recommended:

Power up sequence (DS90C187 PDB input initially LOW):

- 1. Ramp up LCD power (maybe 0.5ms to 10ms) but keep backlight turned off.

- 2. Toggle DS90C187 power down pin to PDB =  $V_{DD}$ .

- 3. Enable clock and wait for additional 0-200ms to ensure display noise won't occur.

- 4. Enable video source output; start sending black video data.

- 5. Send >1ms of black video data; this allows the DS90C187 to be phase locked, and the display to show black data first.

- 6. Start sending true image data.

- 7. Enable backlight.

Power Down sequence (DS90C187 PDB input initially HIGH):

- 1. Disable LCD backlight; wait for the minimum time specified in the LCD data sheet for the backlight to go low.

- 2. Video source output data switch from active video data to black image data (all visible pixel turn black); drive this for >2 frame times.

- 3. Set DS90C187 power down pin to PDB = GND.

- 4. Disable the video output of the video source.

- 5. Remove power from the LCD panel for lowest system power.

The DS90C187 is highly sensitive to the VDD input. Even small levels on the VDD pin prior to full power up should be avoided. The user should additionally take care to not drive or pull up the CMOS inputs to the device prior to device power up so as to ensure proper power on behavior.

#### **10.2 Power Supply Filtering**

The DS90C187 has several power supply pins at 1.8 V. It is important that these pins all be connected and properly bypassed. Bypassing should consist of at least one 0.1 $\mu$ F capacitor placed on each pin, with an additional 4.7  $\mu$ F - 22  $\mu$ F capacitor placed on the PLL supply pin (VDDP). 0.01  $\mu$ F capacitors are typically recommended for each pin. Additional filtering including ferrite beads may be necessary for noisy systems. It is recommended to place a 0 ohm resistor at the bypass capacitors that connect to each power pin to allow for additional filtering if needed. A large bulk capacitor is recommended at the point of power entry. This is typically in the 50  $\mu$ F — 100  $\mu$ F range.

#### 11 Layout

#### 11.1 Layout Guidelines

Circuit board layout and stack-up for the LVDS devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power / ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies, and makes the value and placement of external bypass capacitors less critical. This practice is easier to implement in dense pcbs with many layers and may not be practical in simpler boards. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. It is recommended to connect power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane with vias on both ends of the capacitor.

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20-30 MHz. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency. Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter many be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate LVCMOS signals away from the LVDS lines to prevent coupling from the LVCMOS lines to the LVDS lines. Closely coupled differential lines of 100 Ohms are typically recommended for LVDS interconnect. The closely coupled lines help to ensure that coupled noise will appear as common mode and thus is rejected by the receivers. The tightly coupled lines will also radiate less.

For more information on the VQFN package, refer to the AN-1187 Leadless Leadframe Package (LLP) application note (SNOA401).

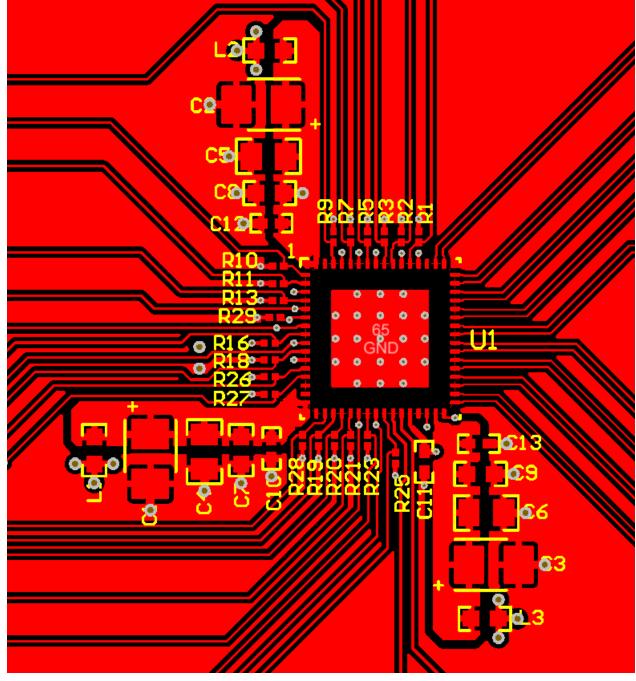

### 11.2 Layout Example

Figure 21. Layout Example

#### **12 Device and Documentation Support**

#### **12.1** Documentation Support

#### 12.1.1 Related Documentation

For related documentation, see:

- LVDS Owner's Manual (SNLA187)

- AN-1108 Channel-Link PCB and Interconnect Design-In Guidelines (SNLA008)

- Transmission Line RAPIDESIGNER Operation and Applications Guide (SNLA035)

- AN-1187 Leadless Leadframe Package (LLP) (SNOA401)

#### 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.3 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.4 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 12.6 Glossary

#### SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |         |

| DS90C187LF/NOPB  | ACTIVE        | VQFN-MR      | NLA                | 92   | 1000           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -10 to 70    | 90C187LF                | Samples |

| DS90C187LFE/NOPB | ACTIVE        | VQFN-MR      | NLA                | 92   | 250            | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -10 to 70    | 90C187LF                | Samples |

| DS90C187LFX/NOPB | ACTIVE        | VQFN-MR      | NLA                | 92   | 2500           | RoHS & Green    | NIPDAU                        | Level-3-260C-168 HR | -10 to 70    | 90C187LF                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

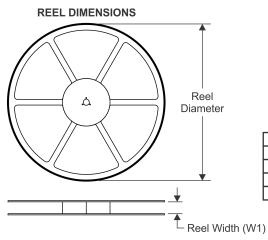

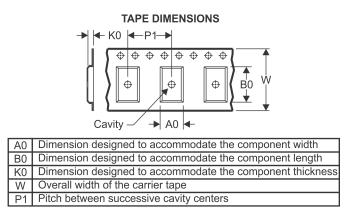

#### TAPE AND REEL INFORMATION

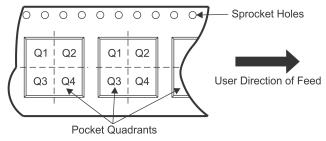

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS90C187LF/NOPB  | VQFN-<br>MR     | NLA                | 92 | 1000 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS90C187LFE/NOPB | VQFN-<br>MR     | NLA                | 92 | 250  | 178.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

| DS90C187LFX/NOPB | VQFN-<br>MR     | NLA                | 92 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.3        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

6-Sep-2018

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90C187LF/NOPB  | VQFN-MR      | NLA             | 92   | 1000 | 367.0       | 367.0      | 38.0        |

| DS90C187LFE/NOPB | VQFN-MR      | NLA             | 92   | 250  | 210.0       | 185.0      | 35.0        |

| DS90C187LFX/NOPB | VQFN-MR      | NLA             | 92   | 2500 | 367.0       | 367.0      | 38.0        |

# **MECHANICAL DATA**

# NLA0092A

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated