## **High-Frequency, High Side** and Low Side Gate Driver IC

The FAN8811 is high side and low side gate-drive IC designed for high-voltage, high-speed, driving MOSFETs operating up to 80 V.

The FAN8811 integrates a driver IC and a bootstrap diode. The driver IC features low delay time and matched PWM input propagation delays, which further enhance the performance of the part.

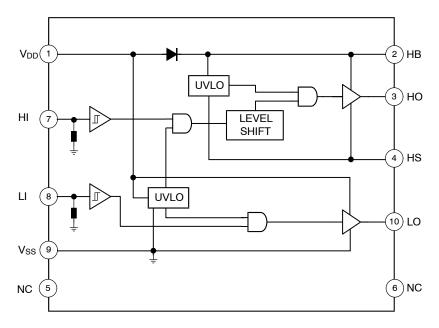

The high speed dual gate drivers are designed to drive both the high-side and low-side of N-Channel MOSFETs in a half bridge or synchronous buck configuration. The floating high-side driver is capable of operating with supply voltages of up to 80 V. In the dual gate driver, the high side and low side each have independent inputs to allow maximum flexibility of input control signals in the application. The PWM input signal (high level) can be 3.3 V, 5 V or up to V<sub>DD</sub> logic input to cover all possible applications. The bootstrap diode for the high-side driver bias supply is integrated in the chip. The high-side driver is referenced to the switch node (HS) which is typically the source pin of the high-side MOSFET and drain pin of the low-side MOSFET. The low-side driver is referenced to V<sub>SS</sub> which is typically ground. The functions contained are the input stages, UVLO protection, level shift, bootstrap diode, and output driver stages.

### Features

- Drives two N-Channel MOSFETs in High & Low Side

- Integrated Bootstrap Diode for High Side Gate Drive

- Bootstrap Supply Voltage Range up to 100 V

- 3 A Source, 6 A Sink Output Current Capability

- Drives 1 nF Load with Typical Rise/Fall Times of 6 ns/4 ns

- TTL Compatible Input Thresholds

- Wide Supply Voltage Range 7.5 V to 16 V (Absolute Maximum 18 V)

- Fast Propagation Delay Times (Typ. 30 ns)

- 2 ns Delay Matching (Typical)

- Under-Voltage Lockout (UVLO) Protection for Drive Voltage

- Operating Junction Temperature Range of -40°C to 125°C

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- Power Supplies for Telecom and Datacom

- Half-Bridge and Full-Bridge Converters

- Synchronous-Buck Converters

- Two–Switch Forward Converters

- Class–D Audio Amplifiers

### **ON Semiconductor®**

www.onsemi.com

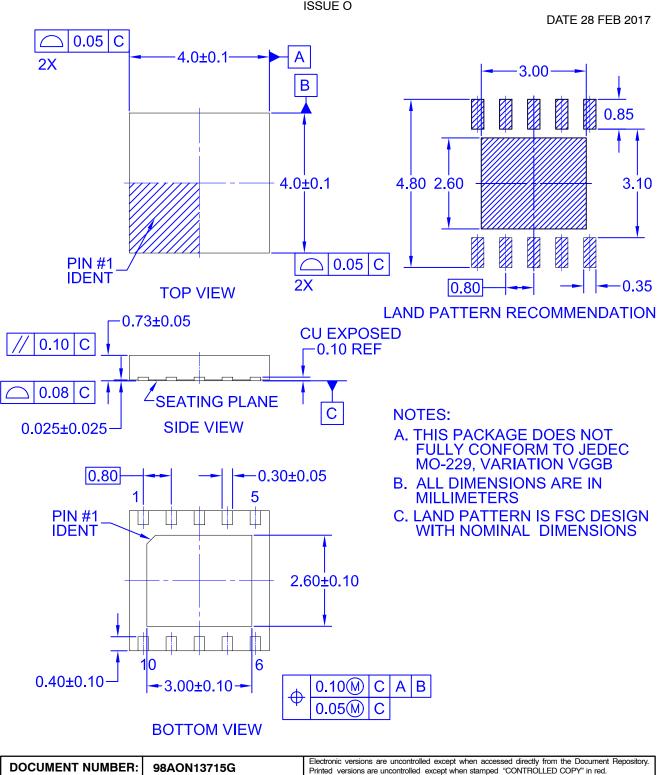

WDFN10 4x4. 0.8P CASE 511DU

### MARKING DIAGRAM

| FAN8811 | Γ = Specific Device Code |

|---------|--------------------------|

| 7       | = Plant Code             |

= Plant Code

Х

Υ

MP

Х

- = 1-Digit Year Code

- = 1-Digit Week Code

- TT = 2-Digit Die Run Code

- = Package Type

- = Reel Package

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

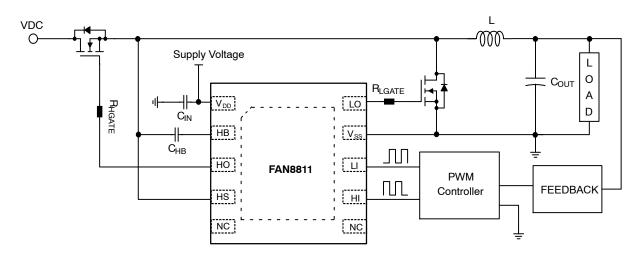

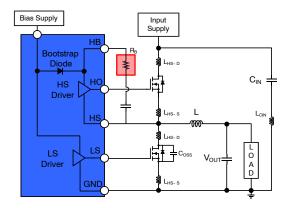

Figure 1. Application Schematic – Synchronous Buck Converter

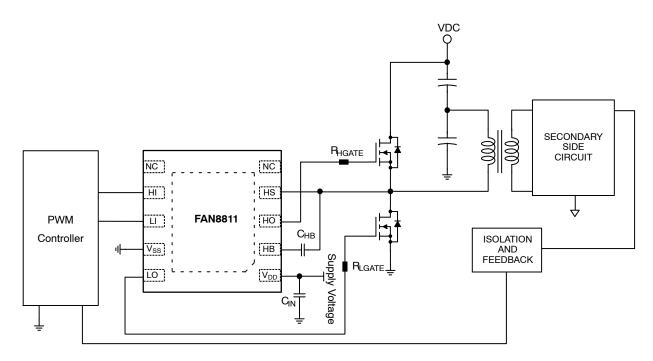

Figure 2. Application Schematic – Half Bridge Converter

### **BLOCK DIAGRAM**

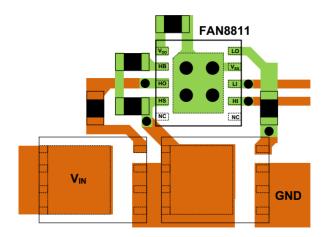

### **PIN CONNECTIONS**

Figure 4. Pin Assignments – 10 Lead MLP (Top View)

### Table 1. PIN DESCRIPTION

| Pin No. | Pin Name        | Description                                         |

|---------|-----------------|-----------------------------------------------------|

| 1       | V <sub>DD</sub> | Logic and low-side gate driver power supply voltage |

| 2       | HB              | High-side floating supply                           |

| 3       | НО              | High-side driver output                             |

| 4       | HS              | High-voltage floating supply return                 |

| 5       | NC              | No Connection                                       |

| 6       | NC              | No Connection                                       |

| 7       | н               | Logic input for High-side gate driver output        |

| 8       | LI              | Logic input for Low-side gate driver output         |

| 9       | V <sub>SS</sub> | Logic Ground                                        |

| 10      | LO              | Low-side driver output                              |

### Table 2. MAXIMUM RATINGS

All voltage parameters are referenced to  $V_{SS}$ , unless otherwise noted.

| Symbol            | Parameter                                         | Min.                     | Max.                  | Units |

|-------------------|---------------------------------------------------|--------------------------|-----------------------|-------|

| V <sub>DD</sub>   | Low-Side and Logic Fixed Supply Voltage           | -0.3                     | 18                    | V     |

| V <sub>HS</sub>   | High-Side Floating Supply Offset Voltage(Note 1)  | -1                       | 100                   | V     |

|                   | Repetitive Pulse (< 100 ns)(Note 2)               | -(24 - V <sub>DD</sub> ) | 100                   | V     |

| V <sub>LO</sub>   | Low-Side Output Voltage, LO Pin                   | -0.3                     | V <sub>DD</sub> + 0.3 | V     |

|                   | Repetitive Pulse (< 100 ns)(Note 2)               | -2                       | V <sub>DD</sub> + 0.3 | V     |

| V <sub>HO</sub>   | High-Side Floating Output Voltage, HO Pin         | V <sub>HS</sub> – 0.3    | V <sub>HB</sub> + 0.3 | V     |

|                   | Repetitive Pulse (< 100 ns)(Note 2)               |                          | V <sub>HB</sub> + 0.3 | V     |

| $V_{LI}, V_{HI}$  | Logic Input Voltage                               | -0.3                     | V <sub>DD</sub> + 0.3 | V     |

| V <sub>HB</sub>   | High-Side Floating Supply Voltage                 | -0.3                     | 100                   | V     |

| $V_{HB} - V_{HS}$ | V <sub>HS</sub> to V <sub>HB</sub> Supply Voltage | -0.3                     | 18                    | V     |

| T <sub>J</sub> ,  | Operating Junction Temperature                    | -55                      | 150                   | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The V<sub>HS</sub> negative voltage capability can be calculated using ( $V_{HB} - V_{HS}$ )-18 V base on  $V_{HB}$ , due to its dependence on  $V_{DD}$  voltage level. 2. Verified at bench characterization.

### Table 3. ESD AND MSL

| Symbol             |                                                                       | Value                              | Unit.s |   |

|--------------------|-----------------------------------------------------------------------|------------------------------------|--------|---|

| ESD <sub>HBM</sub> | Electrostatic Discharge Capability Human Body Model, per AEC Q100-002 |                                    | 2000   | V |

| ESD <sub>CDM</sub> |                                                                       | Charged Device Model, AEC Q100–011 |        |   |

### **Table 4. THERMAL INFORMATION**

| Symbol        |                                 | Value                           | Unit.s |      |

|---------------|---------------------------------|---------------------------------|--------|------|

| PD            | Power Dissipation (Note 3)      | 1S0P with thermal vias (Note 4) | 0.6    | W    |

|               |                                 | 1S2P with thermal vias (Note 5) | 2.4    |      |

| $\theta_{JA}$ | Thermal Resistance Junction-Air | 1S0P with thermal vias (Note 4) | 163    | °C/W |

|               |                                 | 1S2P with thermal vias (Note 5) | 41     |      |

3. JEDEC standard: JESD51-2, JESD51-3. Mounted on 76.2 x 114.3 x1.6 mm PCB (FR-4 glass epoxy material)

4. 1S0P with thermal via: one signal layer with zero power plane and thermal via

5. 1S2P with thermal via: one signal layer with two power planes and thermal via

### Table 5. RECOMMENDED OPERATING RANGES

All voltage parameters are referenced to V<sub>SS</sub>

| Symbol               | Parameters                | Test Condition              | Min.                     | Max.                 | Units |

|----------------------|---------------------------|-----------------------------|--------------------------|----------------------|-------|

| V <sub>DD</sub>      | Supply Voltage            | DC                          | 7.5                      | 16                   | V     |

| V <sub>HS</sub>      | High Side Floating Return | DC                          | -1                       | 80                   | V     |

|                      |                           | Repetitive Pulse (< 100 ns) | -(24 - V <sub>DD</sub> ) | 100                  | V     |

| V <sub>HB</sub>      | Voltage on HB             | DC                          | V <sub>HS</sub> + 7.5    | V <sub>HS</sub> + 16 | V     |

| dV <sub>SW</sub> /dt | Voltage Slew Rate on SW   |                             |                          | 50                   | V/ns  |

| TJ                   | Operating Temperature     |                             | -40                      | 125                  | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### Table 6. ELECTRICAL CHARACTERISTICS

$V_{DD} = V_{HB} = 12 \text{ V}, V_{HS} = V_{SS} = 0 \text{ V}, T_A = T_J = -40^{\circ}C \text{ to } 125^{\circ}C, \text{ no load on HO or LO, unless otherwise noted.}$

| Symbol                    | Parameters                              | Test Condition                                        | Min. | Тур. | Max. | Units |

|---------------------------|-----------------------------------------|-------------------------------------------------------|------|------|------|-------|

| Power Supply              | Section                                 |                                                       | _    |      |      |       |

| I <sub>DD</sub>           | V <sub>DD</sub> Quiescent Current       | V <sub>HI</sub> = 0 V; V <sub>LI</sub> = 0 V          |      | 0.17 | 0.3  | mA    |

| I <sub>DDO</sub>          | V <sub>DD</sub> Operating Current       | f <sub>SW</sub> = 500 kHz                             |      | 1.5  | 3.0  | mA    |

| I <sub>HB</sub>           | HB Quiescent Current                    | V <sub>HI</sub> = 0 V; V <sub>LI</sub> = 0 V          |      | 0.1  | 0.2  | mA    |

| I <sub>HBO</sub>          | HB Operating Current                    | f <sub>SW</sub> = 500 kHz                             |      | 1.9  | 3.0  | mA    |

| I <sub>HBS</sub>          | HB to V <sub>SS</sub> Quiescent Current | V <sub>HS</sub> = V <sub>HB</sub> = 80 V              |      | 0    | 10   | μA    |

| I <sub>HBSO</sub>         | HB to V <sub>SS</sub> Operating Current | f <sub>SW</sub> = 500 kHz                             |      | 0.3  | 1.0  | mA    |

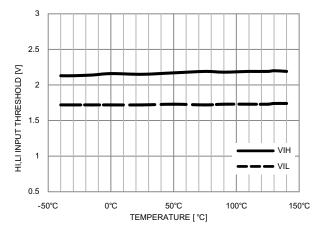

| V <sub>DDR</sub>          | V <sub>DD</sub> UVLO Threshold          | V <sub>DD</sub> Rising                                | 6.2  | 6.8  | 7.4  | V     |

| V <sub>DDH</sub>          | V <sub>DD</sub> UVLO Hysteresis         |                                                       |      | 0.6  |      | V     |

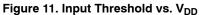

| V <sub>HBR</sub>          | HB UVLO Threshold                       | HB Rising                                             | 5.5  | 6.3  | 7.2  | V     |

| V <sub>HBH</sub>          | HB UVLO Hysteresis                      |                                                       |      | 0.4  |      | V     |

| Input Logic Se            | ection                                  | •                                                     | •    |      |      |       |

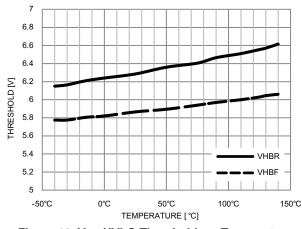

| V <sub>IH</sub>           | High Level Input Voltage Threshold      |                                                       | 1.80 | 2.2  | 2.50 | V     |

| V <sub>IL</sub>           | Low Level Input Voltage Threshold       |                                                       | 1.3  | 1.7  | 2.0  | V     |

| V <sub>IHYS</sub>         | Input Logic Voltage Hysteresis          |                                                       |      | 0.5  |      | V     |

| R <sub>IN</sub>           | Input Pull-down Resistance              |                                                       |      | 100  |      | kΩ    |

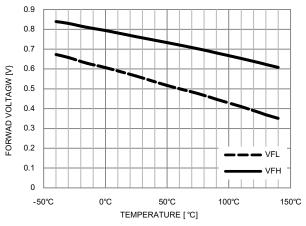

| Bootstrap Dio             | de                                      |                                                       | •    |      |      |       |

| V <sub>FL</sub>           | Forward Voltage @ Low Current           | I <sub>VDD</sub> - <sub>HB</sub> = 100 μA             |      | 0.55 | 0.8  | V     |

| V <sub>FH</sub>           | Forward Voltage @ High Current          | I <sub>VDD</sub> - <sub>HB</sub> = 100 mA             |      | 0.8  | 1.0  | V     |

| R <sub>D</sub>            | Dynamic Resistance                      | I <sub>VDD-HB</sub> = 100 mA                          |      | 0.7  | 1.5  | Ω     |

| t <sub>BS</sub> (Note 6)  | Diode Turn-off Time                     | I <sub>F</sub> = 20 mA, I <sub>REV</sub> = 0.5 A      |      | 20   |      | ns    |

| Low Side Driv             | er                                      |                                                       |      | 1    | 1    |       |

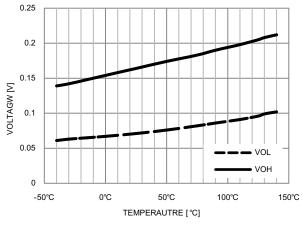

| V <sub>OLL</sub>          | Low Level Output Voltage                | I <sub>LO</sub> = 100 mA                              |      | 0.06 | 0.15 | V     |

| V <sub>OHL</sub>          | High Level Output Voltage               | $I_{LO} = -100 \text{ mA}, V_{OHL} = V_{DD} - V_{LO}$ |      | 0.16 | 0.28 | V     |

| I <sub>OHL</sub> (Note 6) | Peak Pull-up Current                    | V <sub>LO</sub> = 0 V                                 |      | 3    |      | А     |

| I <sub>OLL</sub> (Note 6) | Peak Pull-down Current                  | V <sub>LO</sub> = 12 V                                |      | 6    |      | А     |

| t <sub>R LO</sub>         | LO Rise Time                            | 10% to 90%, C <sub>LOAD</sub> = 1 nF                  |      | 6    |      | ns    |

| t <sub>FLO</sub>          | LO Fall Time                            | 90% to 10%, C <sub>LOAD</sub> = 1 nF                  |      | 4    |      | ns    |

| t <sub>R LO1</sub>        | LO Rise Time                            | 3 V to 9 V, C <sub>LOAD</sub> = 100 nF                |      | 300  | 500  | ns    |

| t <sub>F LO1</sub>        | LO Fall Time                            | 9 V to 3 V, C <sub>LOAD</sub> = 100 nF                |      | 140  | 300  | ns    |

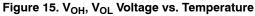

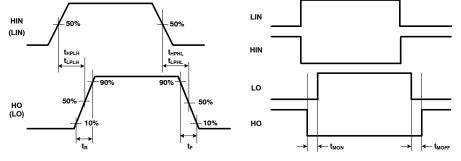

| t <sub>LPHL</sub>         | LI = Low Propagation Delay              | $V_{LI}$ Falling to $V_{LO}$ Falling, $C_{LOAD} = 0$  |      | 28   | 43   | ns    |

| t <sub>LPLH</sub>         | LI = High Propagation Delay             | $V_{LI}$ Rising to $V_{LO}$ Rising, $C_{LOAD} = 0$    |      | 30   | 45   | ns    |

| High Side Driv            | /er                                     |                                                       |      | 1    | 1    |       |

| V <sub>OLH</sub>          | Low Level Output Voltage                | I <sub>HO</sub> = 100 mA                              |      | 0.06 | 0.15 | V     |

| V <sub>OHH</sub>          | High Level Output Voltage               | $I_{HO} = -100 \text{ mA}, V_{OHH} = V_{HB} - V_{HO}$ | 1    | 0.16 | 0.28 | V     |

| I <sub>OHH</sub> (Note 6) | Peak Pull-up Current                    | V <sub>HO</sub> = 0 V                                 | 1    | 3    |      | А     |

| I <sub>OLH</sub> (Note 6) | Peak Pull-down Current                  | V <sub>HO</sub> = 12 V                                | 1    | 6    |      | А     |

| t <sub>R HO</sub>         | HO Rise Time                            | 10% to 90%, C <sub>LOAD</sub> = 1 nF                  | 1    | 6    |      | ns    |

| t <sub>F HO</sub>         | HO Fall Time                            | 90% to 10%, C <sub>LOAD</sub> = 1 nF                  | 1    | 4    |      | ns    |

| t <sub>R HO1</sub>        | HO Rise Time                            | 3 V to 9 V, C <sub>LOAD</sub> = 100 nF                | 1    | 300  | 500  | ns    |

| t <sub>F HO1</sub>        | HO Fall Time                            | 9 V to 3 V, C <sub>LOAD</sub> = 100 nF                | 1    | 140  | 300  | ns    |

| t <sub>HPHL</sub>         | HI = Low Propagation Delay              | $V_{HI}$ Falling to $V_{HO}$ Falling, $C_{LOAD} = 0$  |      | 28   | 43   | ns    |

| t <sub>HPLH</sub>         | HI = High Propagation Delay             | $V_{HI}$ Rising to $V_{HO}$ Rising, $C_{LOAD} = 0$    | 1    | 30   | 45   | ns    |

### Table 6. ELECTRICAL CHARACTERISTICS

$V_{DD} = V_{HB} = 12$  V,  $V_{HS} = V_{SS} = 0$  V,  $T_A = T_J = -40^{\circ}$ C to 125°C, no load on HO or LO, unless otherwise noted.

| Symbol              | Parameters                                    | Test Condition | Min. | Тур. | Max. | Units |

|---------------------|-----------------------------------------------|----------------|------|------|------|-------|

| Delay Matchin       | g                                             |                |      |      |      |       |

| t <sub>MON</sub>    | HI Turn-OFF to LI Turn-ON                     |                |      | 2    | 10   | ns    |

| t <sub>MOFF</sub>   | LI Turn-OFF to HI Turn-ON                     |                |      | 2    | 10   | ns    |

| Minimum Pulse Width |                                               |                |      |      |      |       |

| t <sub>PW</sub>     | Minimum Pulse Width for HI and LI<br>(Note 6) |                |      |      | 50   | ns    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. These parameters are guaranteed by design.

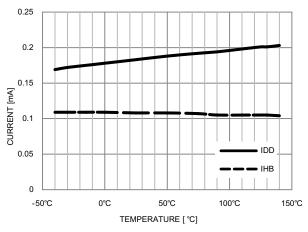

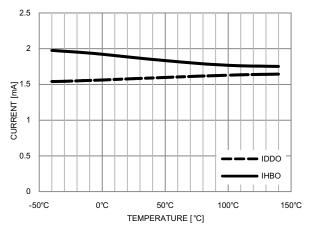

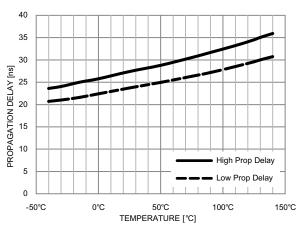

### **TYPICAL CHARACTERISTICS**

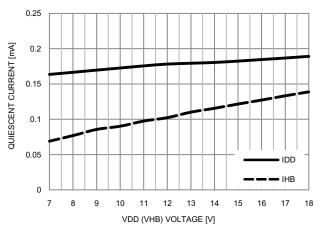

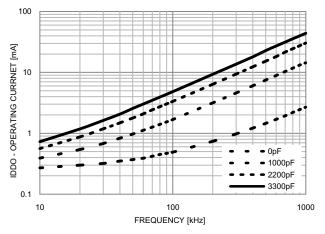

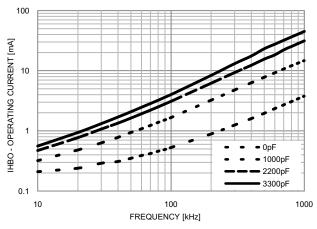

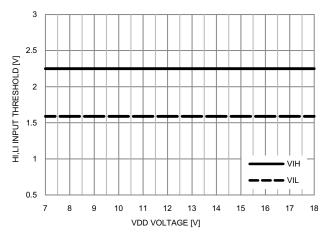

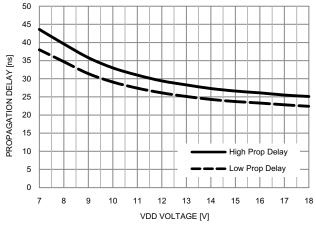

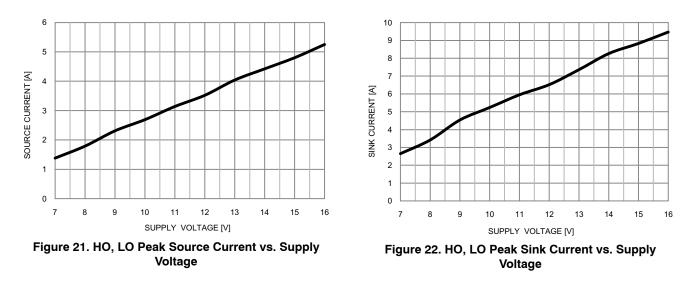

Typical characteristics are provided at 25°C and  $V_{DD}$ ,  $V_{HB}$  = 12 V unless otherwise noted.

Figure 5. Quiescent Current vs. Temperature

Figure 6. Quiescent Current vs. V<sub>DD</sub> (V<sub>HB</sub>)

Figure 8. I<sub>DD</sub> Operating Current vs. Frequency

Figure 9. I<sub>HB</sub> Operating Current vs. Frequency

Figure 13. V<sub>HB</sub> UVLO Threshold vs. Temperature

Figure 10. Input Threshold vs. Temperature

Figure 12.  $V_{\text{DD}}$  UVLO Threshold vs. Temperature

Figure 14. Bootstrap Diode V<sub>F</sub> vs. Temperature

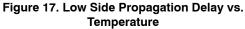

Figure 19. Low Side Propagation Delay vs. V<sub>DD</sub>

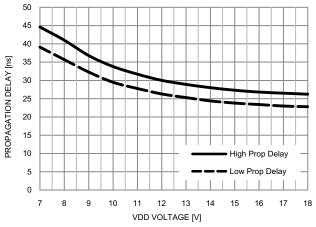

Figure 16.  $V_{OH}$ ,  $V_{OL}$  Voltage vs.  $V_{DD}$  ( $V_{HB}$ )

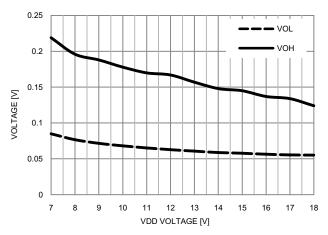

Figure 18. High Side Propagation Delay vs. Temperature

Figure 20. High Side Propagation Delay vs.  $\mathrm{V}_{\mathrm{HB}}$

### **Switching Time Definitions**

Figure 23 shows the switching time waveforms definitions of the turn on and off propagation delay times.

### Input to Output Definitions

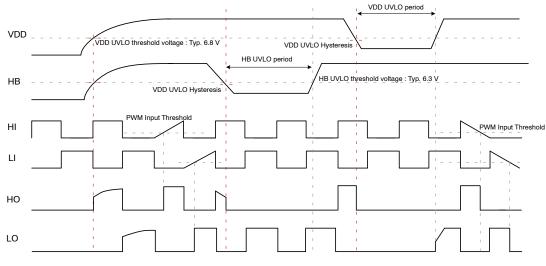

Figure 24 shows an input to output timing diagram for overall operation.

Figure 24. Overall Operation Timing Diagram

### APPLICATIONS INFORMATION

The FAN8811 is designed to drive high side and the low side N-channel power MOSFETs in a half bridge or synchronous buck. The driver IC integrates a bootstrap diode for the high side driver bias supply. High side and Low side outputs are independently controlled by each of input control signals with TTL or logic compatibility. The floating high side driver can operate with supply voltage up to 80 V. The FAN8811 functions consist of the input stage, level shift, bootstrap diode, Under-Voltage Lockout (UVLO) protection and output stage. The UVLO function is included in both the high-and low side.

### Input Stage

The input pins (HI,LI) of gate driver devices are based on a TTL compatible input threshold logic that is independent of the V<sub>DD</sub> supply voltage. The PWM input signal (high level) can be 3.3 V, 5 V or up to VDD logic input to accommodate all possible applications. The input impedance of the FAN8811 is 100 k $\Omega$  nominal. The 100 k $\Omega$ is a pull-down resistance to ground (GND). The logic level compatible input provides a 2.2 V rising threshold and a 1.7 V falling threshold.

### Level Shift

The level shift circuit is the interface from the high side input to the high side driver stage which is referenced to the switch node (HS). The level shift allows control of the HO output referenced to the HS pin and provides excellent delay matching with the low side driver.

To control the high side output drive utilizes a widely used technique for high side level shifter circuit so-called pulsed latch level translators.

### **Bootstrap Diode**

The FAN8811 integrates a high voltage bootstrap diode to generate the high side bias. It is provided to charge high side gate drive bootstrap capacitor. The diode anode is connected to  $V_{DD}$  and cathode connected to HB. The boot capacitor should be connected externally to HB and the HS pins, the HB capacitor charge is refreshed every switching cycle when HS transitions to Ground. The bootstrap diode provides fast recovery times, and a low resistance value of 0.7  $\Omega$  typ.

### Under-Voltage Lockout (UVLO)

Both high side and low side drivers have independent UVLO protections which monitor the  $V_{DD}$  supply voltage and HB bootstrap voltage. The function of the UVLO circuits is to ensure that there is enough supply voltages ( $V_{DD}$  and HB) to correctly bias high side and low side circuits. This also ensures that the gate of external MOSFETs are driven at an optimum voltage. The  $V_{DD}$  UVLO disables both high side and low side drivers when  $V_{DD}$  is below the specified threshold. The rise  $V_{DD}$  threshold is 6.8 V with 0.6 V hysteresis. The HB UVLO disables only the high side driver when the HB to HS

differential voltage is below the specified threshold. The HB UVLO rise threshold is 6.3 V with 0.4 V hysteresis.

### **Output Stage**

The FAN8811 output stage is able to Sink/Source 3.0 A/6.0 A typical which can effectively charge and discharge a 1 nF load in few ns. High speed switching, low resistance and high current capability of both high side and low side drivers allow for efficient switching operation. The low side driver is referenced from V<sub>DD</sub> to V<sub>SS</sub> and the high side is referenced from HB to HS. The device logic status shows as below.

| Table 7. | DEVICE L | LOGIC | STATUS |

|----------|----------|-------|--------|

|----------|----------|-------|--------|

|        | HI | LI | НО | LO |

|--------|----|----|----|----|

| Status | L  | L  | L  | L  |

|        | L  | Н  | L  | Н  |

|        | Н  | L  | Н  | L  |

|        | Н  | Н  | Н  | Н  |

|        | Х  | Х  | L  | L  |

#### Select Bootstrap Capacitor

The maximum allowable voltage drop across the bootstrap capacitor to ensure enough gate-source voltage is highly dependent to the internal under-voltage Lockout level of the gate drive IC, and the voltage level at the source connection of switching node HS. The maximum allowable drop voltage can be obtained by (eq.1)

$$\Delta V_{HB} = V_{DD} - V_{f} - V_{HB,UVLO}$$

(eq. 1)

Where:

- V<sub>DD</sub>: Gate drive IC supply voltage

- V<sub>f</sub> : Static forward voltage drop of bootstrap diode

- V<sub>HB,UVLO</sub>: HB Under-Voltage Lockout level

The total charge  $(Q_{bs})$  required by the bootstrap capacitor can be calculated by summing the  $Q_g$  of the MOSFET and the charge required for the level shifter in the gate drive IC which is negligible quantity to compared  $Q_g$  of the MOSFET.

$$Q_{BS} = Q_{g} + (I_{HBS} \times T_{ON})$$

(eq. 2)

Where:

- Q<sub>BS</sub>: Total gate charge of bootstrap capacitor

- Qg: Gate charge of the MOSFET

- I<sub>HBS</sub>: Quiescent current in High side gate drive IC.

- T<sub>ON</sub>: Turning on of MOSFET

The guiding criteria for calculating the minimum required bootstrap capacitance can be obtained through (eq.4).

$$C_{BOOT.MIN} \ge \frac{Q_{BS}}{\Delta V_{HB}}$$

(eq. 3)

#### Select External Bootstrap Series Resistor

The FAN8811 utilizes high speed gate driving for synchronous buck and half bridge applications. In these applications, voltage ringing can be generated by parasitic inductance of the primary power path, consisting of the input capacitor and switching MOSFETs ( $C_{oss}$ ).

To reduce this ringing phenomenon, the first step is to optimize the PCB layout to reduce parasitic components of the power path. The second step is to add a series resistor with the bootstrap capacitor to slow down the turn-on transition of the high side MOSFET.

Figure 25. Application Circuit with Parasitic Components

Figure 25 shows the synchronous buck with the parasitic component at the power path. Each of parasitic inductance and low side  $C_{OSS}$  of MOSFET made up the ringing phenomenon at the HS node, when the high side turns on. When the bootstrap series resistor  $R_B$  installed with bootstrap capacitor, the bootstrap resistor limits the current available to charge the gate of the high side MOSFET, increasing the time needed to turn the high side MOSFET on. The increased switching time slows the HS node rate of rising and can have a significant impact on the peak voltage on the HS node.

We recommend selecting less than 10  $\Omega$  for R<sub>B</sub>.

$$I_{\text{BOOT}(\text{PEAK})} = \frac{V_{\text{DD}} - V_{\text{f}}}{R_{\text{B}}} \tag{eq. 4}$$

### Select Gate Resistor

The gate resistor is also sized to reduce a ringing voltage of the HS node by parasitic inductances and capacitances. But, it limits the current capability of the gate driver output by the resistance value. The limited current capability value by the gate resistor can be obtained (eq.5).

$$\begin{split} I_{OHH} &= \frac{V_{DD} - V_f - V_{OHH}}{R_{gate}} \\ I_{OLH} &= \frac{V_{DD} - V_f - V_{OLH}}{R_{gate}} \\ I_{OHL} &= \frac{V_{DD} - V_{OHL}}{R_{gate}} \\ I_{OLL} &= \frac{V_{DD} - V_{OLL}}{R_{gate}} \end{split}$$

(eq. 5)

Where:

- I<sub>OHH</sub>: High side peak source current

- IOLH: High side peak sink current

- I<sub>OHL</sub>: Low side peak source current

- IOLL: Low side peak sink current

- V<sub>f</sub>: Bootstrap diode forward voltage drop

- V<sub>OHH</sub>: High level output voltage drop (high side)

- V<sub>OLH</sub>: Low level output voltage drop (high side)

- V<sub>OHL</sub>: High level output voltage drop (low side)

- V<sub>OLL</sub>: Low level output voltage drop (low side)

### **Gate Driver Power Dissipation**

The total power dissipation is the sum of the gate driver losses and the bootstrap diode losses. The gate driver losses are:

- The static and dynamic losses related to the switching frequency

- Output load capacitance losses on high and low side drivers

- Internal consumption supply voltage, V<sub>DD</sub>

The static losses are due to the quiescent current from the voltage supplies  $V_{DD}$  and ground in low side driver and the leakage current in the level shifting stage in high side driver, which are dependent on the voltage supplied on the HS pin and proportional to the duty cycle when only the high side power device is turned on. The quiescent current is consumed by the device through all internal circuits such as input stage, reference voltage, logic circuits, protections, and also any current associated with switching of internal devices when the driver output changes state. The effect of the static losses within the gate driver can be safely assumed to be negligible thanks to the FAN8811 low 0.17 mA quiescent current.

The dynamic losses are defined as follows: In the low side driver, the dynamic losses are due to two different sources. One is due to whenever a load capacitor is charged or discharged through a gate resistor, half of the energy that goes into the capacitance is dissipated in the resistor. The losses in the gate driver resistance, internal and external to the gate driver, and the switching losses of the internal CMOS circuitry. The dynamic losses of the high side driver also have two different sources. One is due to the level shifting circuit and one due to the charging and discharging of the capacitance of the high side. The static losses are neglected here because the total IC power dissipation is mainly dynamic losses of gate drive IC and can be estimated as:

$$P_{DGATE} = 2 \times C_{L} \times f_{S} \times V_{DD}^{2}[W]$$

(eq. 6)

The bootstrap circuit power dissipation is the sum of the bootstrap diode losses and the bootstrap resistor losses if any exist. The bootstrap diode loss is the sum of the forward bias power loss that occurs while charging the bootstrap capacitor and the reverse bias power loss that occurs during reverse recovery. Since each of these events happens once per cycle, the diode power loss is proportional to switching frequency. Larger capacitive loads require more current to recharge the bootstrap capacitor, resulting in more losses.

### PCB Layout Guideline

FAN8811 is a high speed and high current high side and low side driver. To avoid any device malfunction during device operation, it is very important that there is very low parasitic inductance in the current switching path. It is very important that the best layout practices are followed for the PCB layout of the FAN8811. The following should be considered before beginning a PCB layout using the FAN8811.

- The gate driver should be located as close as possible of switching MOSFET.

- The V<sub>DD</sub> capacitor and bootstrap capacitor should be located as near as possible to the device.

- In order to reduce a ringing voltage of the HS node, the space between high side source and low side drain of the MOSFET should be as small as possible.

- The exposed pad should be connected to GND plane and use at least four or more vias for improved thermal performance.

- Avoid driver input pulse signal close to the HS node.

One of recommendation layout pattern for the driver is shown in Figure 26.

Figure 26. Layout Recommendation

### **ORDERING INFORMATION**

| Device       | Output Configuration   | Temperature Range (°C) | Package                       | Shipping $^{\dagger}$                                     |

|--------------|------------------------|------------------------|-------------------------------|-----------------------------------------------------------|

| FAN8811TMPX  | High-Side and Low-Side | -40 to 125             | WDFN10 4x4, 0.8P<br>(Pb-Free) | Tape & Reel<br>(Pin 1 upper left near<br>sprocket holes)  |

| FAN8811MNTXG | High-Side and Low-Side | -40 to 125             | WDFN10 4x4, 0.8P<br>(Pb-Free) | Tape & Reel<br>(Pin 1 upper right near<br>sprocket holes) |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

**ON Semiconductor**

CASE 511DU

ON Semiconductor and 💷 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**DESCRIPTION:**

WDFN10 4x4, 0.8P

PAGE 1 OF 1

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative