SLOS598A - MARCH 2009 - REVISED OCTOBER 2009

# CLASS-G DIRECTPATH™ STEREO HEADPHONE AMPLIFIER WITH I<sup>2</sup>C VOLUME CONTROL

Check for Samples: TPA6140A2

#### **FEATURES**

- TI Class-G Technology Significantly Prolongs Battery Life and Music Playback Time

- 0.6 mA / Ch Quiescent Current

- 50% to 80% Lower Quiescent Current than Ground-Referenced Class-AB Headphone Amplifiers

- DirectPath<sup>TM</sup> Technology Eliminates Large Output DC-Blocking Capacitors

- Outputs Biased at 0 V

- Improves Low Frequency Audio Fidelity

- I<sup>2</sup>C Volume Control

- 59 dB to +4 dB Gain

- Active Click and Pop Suppression

- Fully Differential Inputs Reduce System Noise

- Also Configurable as Single-Ended Inputs

- SGND Pin Eliminates Ground Loop Noise

- Wide Power Supply Range: 2.5 V to 5.5 V

- 100 dB Power Supply Noise Rejection

- Short-Circuit Current Limiter

- Thermal-Overload Protection

- Software Compatible with TPA6130A2

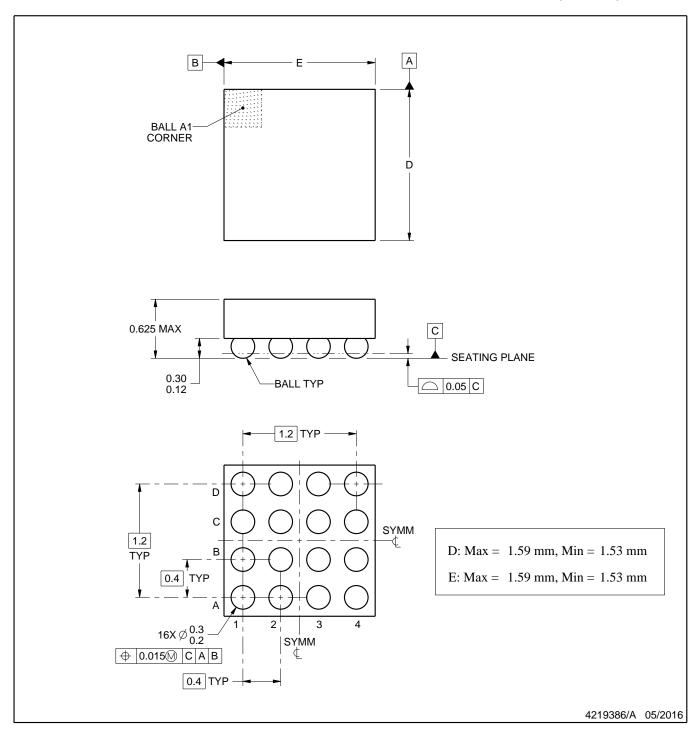

- 0,4 mm Pitch, 1,6 mm x 1,6 mm WCSP Package

#### **APPLICATIONS**

- Cellular Phones / Music Phones

- Portable Media / MP3 Players

- Portable CD / DVD Players

#### DESCRIPTION

The TPA6140A2 (also known as TPA6140) is a Class-G DirectPath<sup>™</sup> stereo headphone amplifier with built-in I<sup>2</sup>C volume control. Class-G technology maximizes battery life by adjusting the voltage supplies of the headphone amplifier based on the audio signal level. At low level audio signals, the internal supply voltage is reduced to minimize power dissipation. DirectPath<sup>™</sup> technology eliminates external DC-blocking capacitors.

The device operates from a 2.5 V to 5.5 V supply voltage. Class-G operation keeps total supply current below 5.0 mA while delivering 500  $\mu$ W per channel into 32  $\Omega$ . Shutdown mode reduces the supply current to less than 3  $\mu$ A and is activated through the  $I^2$ C interface.

The TPA6140A2 (TPA6140) I<sup>2</sup>C register map is compatible to the TPA6130A2, simplifying software development.

The amplifier outputs have short-circuit and thermal-overload protection along with ±8 kV HBM ESD protection, simplifying end equipment compliance to the IEC 61000-4-2 ESD standard.

The TPA6140A2 (TPA6140) is available in a 0,4 mm pitch, 16-bump 1,6 mm  $\times$  1,6 mm WCSP (YFF) package.

**A**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Class-G DirectPath, DirectPath are trademarks of Texas Instruments.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

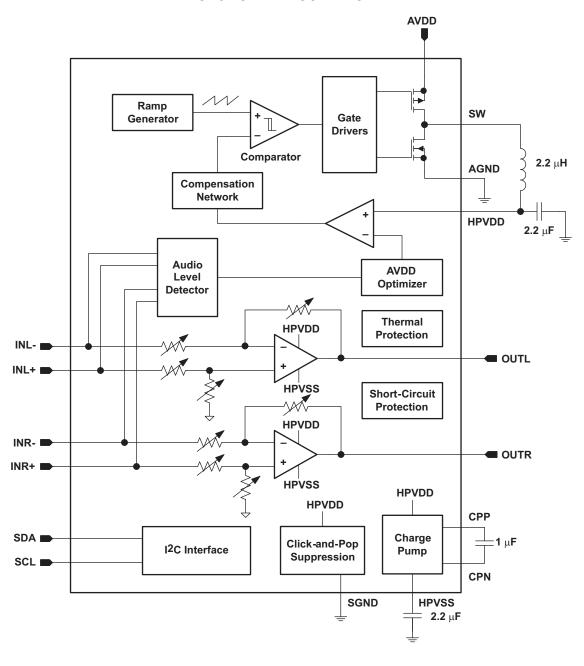

#### **FUNCTIONAL BLOCK DIAGRAM**

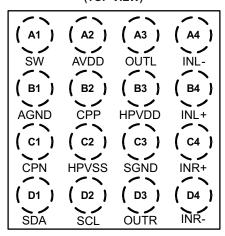

#### **DEVICE PINOUT**

#### WCSP PACKAGE (TOP VIEW)

#### **TERMINAL FUNCTIONS**

| TER   | MINAL        | INPUT /                      |                                                                                                                                          |

|-------|--------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | BALL<br>WCSP | OUTPUT /<br>POWER<br>(I/O/P) | DESCRIPTION                                                                                                                              |

| INL-  | A4           | I                            | Inverting left input for differential signals; connect to left input signal through 1 µF capacitor for single-ended input applications   |

| INL+  | B4           | I                            | Non-inverting left input for differential signals; connect to ground through 1 µF capacitor for single-ended input applications          |

| INR-  | D4           | I                            | Inverting right input for differential signals; connect to right input signal through 1 µF capacitor for single-ended input applications |

| INR+  | C4           | I                            | Non-inverting right input for differential signals; connect to ground through 1 µF capacitor for single-ended input applications         |

| SGND  | C3           | I                            | Sense Ground; connect to shield terminal of headphone jack or to AGND                                                                    |

| SDA   | D1           | I/O                          | I <sup>2</sup> C Data; 1.8 V logic compliant                                                                                             |

| SCL   | D2           | I                            | I <sup>2</sup> C Clock; 1.8 V logic compliant                                                                                            |

| OUTL  | А3           | 0                            | Left headphone amplifier output; connect to left terminal of headphone jack                                                              |

| OUTR  | D3           | 0                            | Right headphone amplifier output; connect to right terminal of headphone jack                                                            |

| CPP   | B2           | Р                            | Charge pump positive flying cap; connect to positive side of capacitor between CPP and CPN                                               |

| CPN   | C1           | Р                            | Charge pump negative flying cap; connect to negative side of capacitor between CPP and CPN                                               |

| SW    | A1           | Р                            | Buck converter switching node                                                                                                            |

| AVDD  | A2           | Р                            | Primary power supply for device                                                                                                          |

| HPVDD | В3           | Р                            | Power supply for headphone amplifier (DC/DC output node)                                                                                 |

| AGND  | B1           | Р                            | Main Ground for headphone amplifiers, DC/DC converter, and charge pump                                                                   |

| HPVSS | C2           | Р                            | Charge pump output; connect 2.2 µF capacitor to GND                                                                                      |

# **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGED DEVICES (1)          | PART NUMBER (2) | SYMBOL |

|----------------|-------------------------------|-----------------|--------|

| 4000 1 - 0500  | 16-ball, 1,6 mm × 1,6 mm WCSP | TPA6140A2YFFR   | AIFI   |

| –40°C to 85°C  | 16-ball, 1,6 mm × 1,6 mm WCSP | TPA6140A2YFFT   | AIFI   |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

Copyright © 2009, Texas Instruments Incorporated

<sup>(2)</sup> YFF packages are only available taped and reeled. The suffix "R" indicates a reel of 3000, the suffix "T" indicates a reel of 250.

## ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range, T<sub>A</sub> = 25°C (unless otherwise noted)

|           |                                           |                  | VALUE / UNIT                       |

|-----------|-------------------------------------------|------------------|------------------------------------|

|           | Supply voltage, AVDD                      |                  | –0.3 V to 6.0 V                    |

|           | Amplifier supply voltage, HPVDD           | -0.3 V to 2.0 V  |                                    |

| $V_{I}$   | Input voltage                             |                  | –0.3 V to HPV <sub>DD</sub> +0.3 V |

|           | I <sup>2</sup> C voltage                  |                  | −0.3 V to AVDD                     |

|           | Output continuous total power dissipation |                  | See Dissipation Rating Table       |

| $T_A$     | Operating free-air temperature range      |                  | -40°C to 85°C                      |

| $T_J$     | Operating junction temperature range      |                  | -40°C to 150°C                     |

| $T_{stg}$ | Storage temperature range                 |                  | -65°C to 85°C                      |

|           | ESD Protection – HBM                      | OUTL, OUTR, SGND | 8 kV                               |

|           | ESD Protection – HBM                      | All other pins   | 2 kV                               |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

## DISSIPATION RATINGS TABLE(1) (2)

| PACKAGE    | T <sub>A</sub> < 25°C<br>POWER RATING | OPERATING<br>FACTOR<br>ABOVE T <sub>A</sub> =<br>25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------|---------------------------------------|-------------------------------------------------------|---------------------------------------|---------------------------------------|

| YFF (WCSP) | 1.25 W                                | 10 mW/°C                                              | 800 mW                                | 650 mW                                |

- Derating factor measured with JEDEC High K board: 1S0P One signal layer and zero plane layers. See JEDEC Standard 51-3 for Low-K board, JEDEC Standard 51-7 for High-K board, and JEDEC Standard 51-12 for using package thermal information. See JEDEC document page for downloadable copies: http://www.jedec.org/download/default.cfm.

# RECOMMENDED OPERATING CONDITIONS

| .,_             | CHINICIADED OF ER                | ATING CONDITIONS                                                    |      |      |      |

|-----------------|----------------------------------|---------------------------------------------------------------------|------|------|------|

|                 |                                  |                                                                     | MIN  | MAX  | UNIT |

|                 | Supply voltage, AV <sub>DD</sub> |                                                                     | 2.5  | 5.5  | V    |

| $V_{\text{IH}}$ | High-level input voltage         | SDA, SCL                                                            | 1.3  |      | V    |

| $V_{IL}$        | Low-level input voltage          | SDA, SCL                                                            |      | 0.35 | V    |

|                 | Voltage applied to Output        | ; OUTR, OUTL (when SWS = 1, device disabled)                        | -0.3 | 3.6  | V    |

|                 | Voltage applied to Output        | ; OUTR, OUTL (when SWS = 0, HiZ_L = HiZ_R = 1, device in HI-Z mode) | -1.8 | 1.8  | V    |

| T <sub>A</sub>  | Operating free-air temper        | ature                                                               | -40  | 85   | °C   |

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

$T_A = 25$ °C (unless otherwise noted)

|                 | PARAMETER                    | TEST CONDITIONS                                                                                             |                       | MIN | TYP | MAX | UNIT |

|-----------------|------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| PSRR            | Power supply rejection ratio | AV <sub>DD</sub> = 2.5 V to 5.5 V, inputs grounded, GAIN = 0 dB                                             |                       |     | 105 |     | dB   |

| CMRR            | Common-mode rejection ratio  | HPV <sub>DD</sub> = 1.3 V to 1.8 V, GAIN = 0 dB                                                             |                       |     | 68  |     | dB   |

| I <sub>IH</sub> | High-level input current     | $AV_{DD} = 2.5 \text{ V to } 5.5 \text{ V}, V_{I} = AV_{DD}$                                                | SCL, SDA              |     |     | 1   | μA   |

| I <sub>IL</sub> | Low-level input current      | $AV_{DD} = 2.5 \text{ V to } 5.5 \text{ V}, V_{I} = 0 \text{ V}$                                            | SCL, SDA              |     |     | 1   | μΑ   |

| I <sub>SD</sub> | Soft shutdown current        | SW Shutdown mode, V <sub>DD</sub> = 2.5 V to 5.5 V, S                                                       | WS bit = 1            |     | 1   | 3   | μA   |

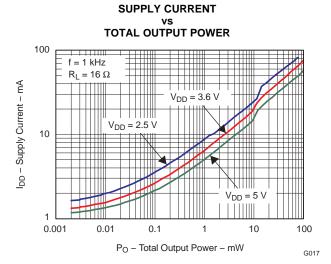

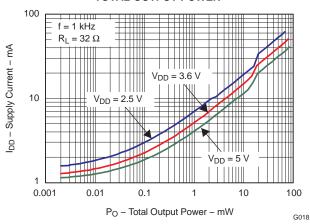

|                 |                              | AV <sub>DD</sub> = 3.6 V HPVDD = 1.3 V, Amplifiers acti input signal                                        | ive, no load, no      |     | 1.2 | 2.0 |      |

|                 |                              | $AV_{DD} = 3.6 \text{ V}, P_{OUT} = 100 \mu\text{W} \text{ into } 32 \Omega^{(1)}, f_{AUD} = 1 \text{ kHz}$ |                       |     | 2.5 |     |      |

| $I_{DD}$        | Total supply current         | $AV_{DD} = 3.6 \text{ V}, P_{OUT} = 500 \mu\text{W} \text{ into } 32 \Omega^{(1)}, f_A$                     | <sub>UD</sub> = 1 kHz |     | 4.0 |     | mA   |

|                 |                              | $AV_{DD} = 3.6 \text{ V}, P_{OUT} = 1 \text{ mW into } 32 \Omega^{(1)}, f_{AUD} = 1 \text{ kHz}$            |                       |     | 6.8 |     |      |

|                 |                              | $AV_{DD}$ = 3.6 V, HiZ_L = HiZ_R = HIGH (High output impedance mode)                                        |                       |     | 1.0 | 2.0 |      |

<sup>(1)</sup> Per channel output power assuming a 10 dB crest factor

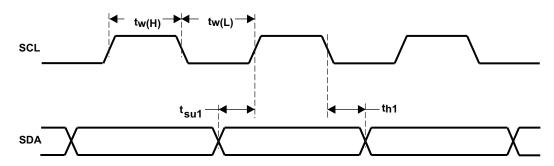

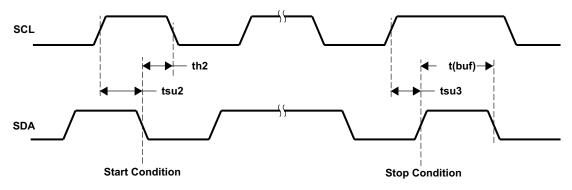

## **TIMING CHARACTERISTICS**

For I<sup>2</sup>C interface signals over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------------------------|-----------------|-----|-----|-----|------|

| f <sub>SCL</sub>   | Frequency, SCL                                 | No wait states  |     |     | 400 | kHz  |

| t <sub>W(H)</sub>  | Pulse duration, SCL high                       |                 | 0.6 |     |     | μs   |

| t <sub>W(L)</sub>  | Pulse duration, SCL low                        |                 | 1.3 |     |     | μs   |

| t <sub>SU1</sub>   | Setup time, SDA to SCL                         |                 | 100 |     |     | μs   |

| t <sub>H1</sub>    | Hold time, SCL to SDA                          |                 | 10  |     |     | ns   |

| t <sub>(BUF)</sub> | Bus free time between stop and start condition |                 | 1.3 |     |     | μs   |

| t <sub>SU2</sub>   | Setup time, SCL to start condition             |                 | 0.6 |     |     | μs   |

| t <sub>H2</sub>    | Hold time, start condition to SCL              |                 | 0.6 |     |     | μs   |

| t <sub>SU3</sub>   | Setup time, SCL to stop condition              |                 | 0.6 |     |     | μs   |

Figure 1. SCL and SDA Timing

Figure 2. Start and Stop Conditions Timing

## **OPERATING CHARACTERISTICS**

$AV_{DD} = 3.6 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , GAIN = 0 dB,  $R_L = 32 \Omega$  (unless otherwise noted)

|                    | PARAMETER                                      | TEST CONDITIONS                                              | MIN  | TYP   | MAX | UNIT          |  |

|--------------------|------------------------------------------------|--------------------------------------------------------------|------|-------|-----|---------------|--|

|                    |                                                | AV <sub>DD</sub> = 2.7V, THD = 1%, f = 1 kHz                 |      | 26    |     |               |  |

| Po                 | Output power <sup>(1)</sup> (Outputs in Phase) | AV <sub>DD</sub> = 2.7V, THD = 10%, f = 1 kHz                |      | 32    |     | mW            |  |

| . 0                | Culput power (Culpute III Triace)              | $AV_{DD}$ = 2.7V, THD = 1%, f = 1 kHz, $R_L$ = $16\Omega$    |      | 25    |     | 11100         |  |

| THD+N              | Total harmonic distortion plus noise (2)       | $P_O = 10 \text{ mW}$ into $16 \Omega$ , $f = 1 \text{ kHz}$ |      | 0.02% |     |               |  |

| I HD+N             | Total Harmonic distortion plus hoise           | $P_O = 20$ mW into 32 $\Omega$ , $f = 1$ kHz                 |      | 0.01% |     |               |  |

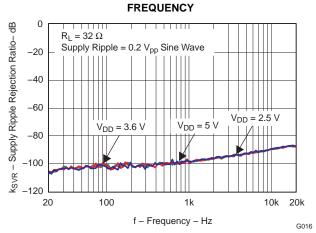

| le.                | AC Down ownship rejection ratio                | 200 mVpp ripple, f = 217 Hz                                  | 80   | 100   |     | ٩D            |  |

| k <sub>SVR</sub>   | AC-Power supply rejection ratio                | 200 mVpp ripple, f = 4 kHz                                   | 90   |       |     | dB            |  |

| $\Delta A_V$       | Gain matching                                  | Between left and right channels                              |      | 1%    |     |               |  |

| Vos                | Output offset voltage                          | AV <sub>DD</sub> = 2.5 V to 5.5 V, inputs grounded           | -0.5 | 0     | 0.5 | mV            |  |

| En                 | Noise output voltage                           | A-weighted                                                   |      | 5.3   |     | $\mu V_{RMS}$ |  |

| f <sub>BUCK</sub>  | Buck converter switching frequency             | $P_O = 0.5$ mW into 32 $\Omega$ , f = 1 kHz                  |      | 600   |     | kHz           |  |

| f <sub>PUMP</sub>  | Charge numb quitaking frequency                | $P_O = 0.5$ mW into 32 $\Omega$ , f = 1 kHz                  | 315  |       |     | kHz           |  |

|                    | Charge pump switching frequency                | $P_O$ = 15 mW into 32 $\Omega$ , f = 1 kHz                   | 1260 |       |     | KΠZ           |  |

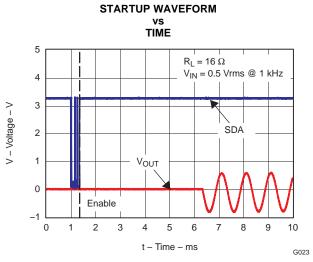

|                    | Start-up time from shutdown                    |                                                              |      | 5     |     | ms            |  |

| R <sub>IN,SE</sub> | Single Ended Input impedance                   | Gain = 4 dB, per input node                                  |      | 15.6  |     | kΩ            |  |

| R <sub>IN,DF</sub> | Differential input impedance                   | Gain = 4 dB, per input node                                  |      | 31.2  |     | kΩ            |  |

| SNR                | Signal-to-noise ratio                          | V <sub>OUT</sub> = 1 V <sub>RMS</sub> , GAIN = 4 dB, no load |      | 105   |     | dB            |  |

|                    | Thermal shutdown                               | Threshold                                                    |      | 165   |     | °C            |  |

|                    | mermai shuldown                                | Hysteresis                                                   | 35   |       |     |               |  |

| Z <sub>O,SD</sub>  | Output impedance in shutdown                   | SWS = 1, DC value                                            |      | 8     |     | kΩ            |  |

|                    |                                                | 40 kHz, 1.8 V <sub>PEAK</sub> signal max                     |      | 8.5   |     | kΩ            |  |

| $Z_{O,HI-Z}$       | Output impedance in Hi-Z mode                  | 6 MHz, 1.8 V <sub>PEAK</sub> signal max                      |      | 600   |     | Ω             |  |

|                    |                                                | 13 MHz, 1.8 V <sub>PEAK</sub> signal max                     | 400  |       | Ω   |               |  |

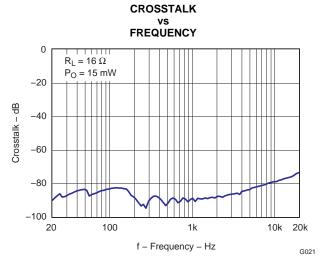

|                    | Crosstalk                                      | P <sub>O</sub> = 15 mW, f = 1 kHz                            |      | -80   |     | dB            |  |

| V <sub>CM</sub>    | Input common-mode voltage range                |                                                              | 0    |       | 1.4 | V             |  |

<sup>(1)</sup> Per channel output power

<sup>(2)</sup> A-weighted

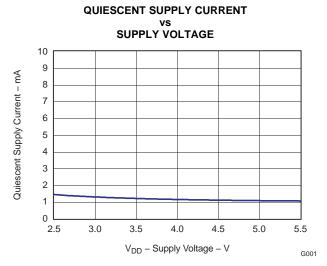

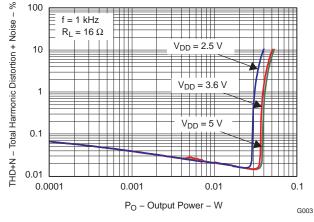

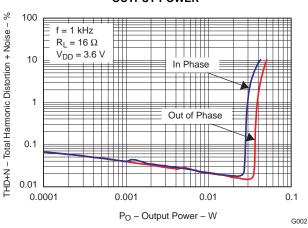

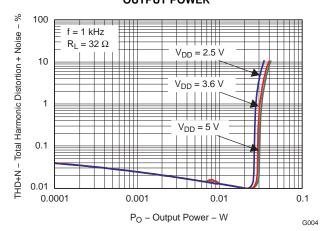

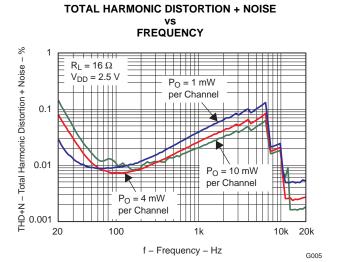

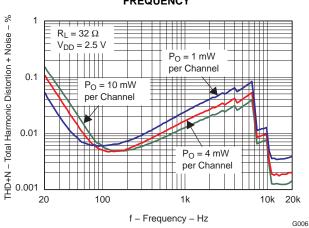

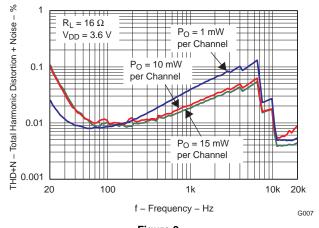

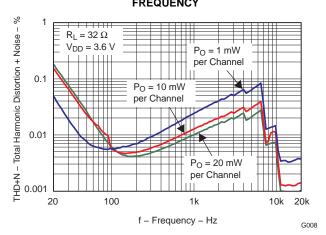

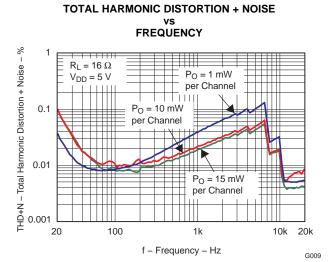

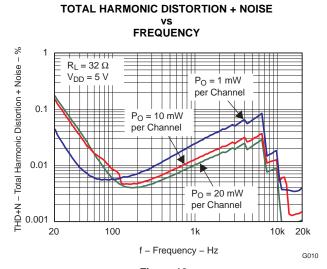

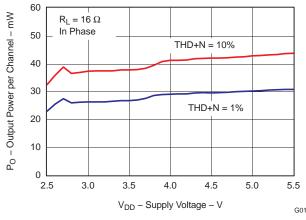

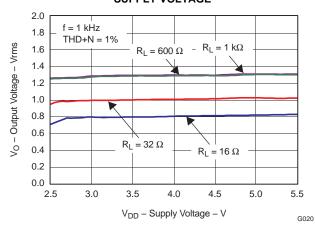

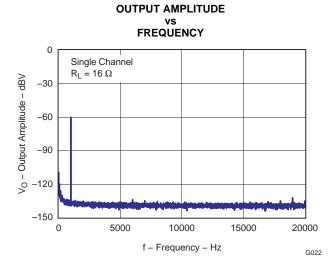

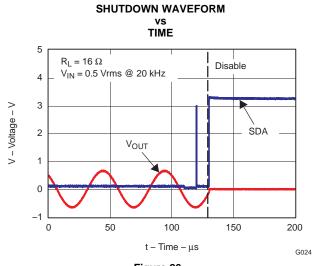

## **TYPICAL CHARACTERISTICS**

$T_{\text{A}} = 25^{\circ}\text{C}, \ \text{AV}_{\text{DD}} \ (\text{V}_{\text{DD}}) = 3.6 \ \text{V}, \ \text{GAIN} = 0 \ \text{dB}, \ C_{\text{HPVDD}} = C_{\text{HPVSS}} = 2.2 \ \mu\text{F}, \ C_{\text{INPUT}} = C_{\text{FLYING}} = 1 \ \mu\text{F}, \ \text{Outputs out of phase}$

#### Figure 3.

# TOTAL HARMONIC DISTORTION + NOISE vs OUTPUT POWER

Figure 5.

# TOTAL HARMONIC DISTORTION + NOISE vs OUTPUT POWER

Figure 4.

# TOTAL HARMONIC DISTORTION + NOISE vs OUTPUT POWER

Figure 6.

$T_{A} = 25^{\circ}C, \ AV_{DD} \ (V_{DD}) = 3.6 \ V, \ GAIN = 0 \ dB, \ C_{HPVDD} = C_{HPVSS} = 2.2 \ \mu F, \ C_{INPUT} = C_{FLYING} = 1 \ \mu F, \ Outputs \ out \ of \ phase$

TOTAL HARMONIC DISTORTION + NOISE

VS

FREQUENCY

Figure 7.

TOTAL HARMONIC DISTORTION + NOISE

vs

FREQUENCY

Figure 9.

TOTAL HARMONIC DISTORTION + NOISE vs FREQUENCY

Figure 8.

Figure 10.

8

$T_{\text{A}} = 25^{\circ}\text{C}, \text{ AV}_{\text{DD}} \text{ (V}_{\text{DD}}) = 3.6 \text{ V}, \text{ GAIN} = 0 \text{ dB}, C_{\text{HPVDD}} = C_{\text{HPVSS}} = 2.2 \text{ } \mu\text{F}, C_{\text{INPUT}} = C_{\text{FLYING}} = 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase } 1 \text{ } \mu\text{F}, \text{ Outputs out of phase }$

Figure 11.

Figure 12.

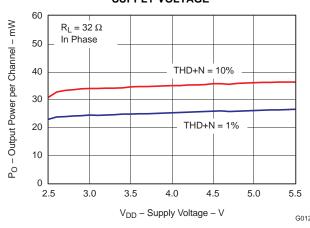

# OUTPUT POWER PER CHANNEL vs SUPPLY VOLTAGE

Figure 13.

# OUTPUT POWER PER CHANNEL vs SUPPLY VOLTAGE

Figure 14.

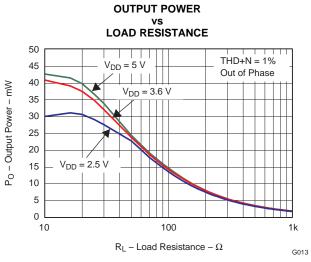

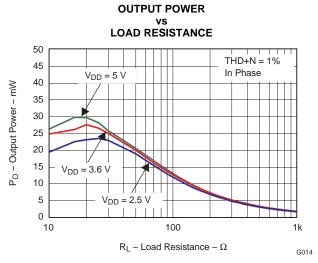

$T_{A}=25^{\circ}C,\ AV_{DD}\ (V_{DD})=3.6\ V,\ GAIN=0\ dB,\ C_{HPVDD}=C_{HPVSS}=2.2\ \mu F,\ C_{INPUT}=C_{FLYING}=1\ \mu F,\ Outputs\ out\ of\ phase$

Figure 15.

Figure 16.

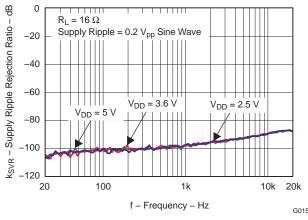

# SUPPLY RIPPLE REJECTION RATIO vs FREQUENCY

Figure 17.

# SUPPLY RIPPLE REJECTION RATIO vs

Figure 18.

10

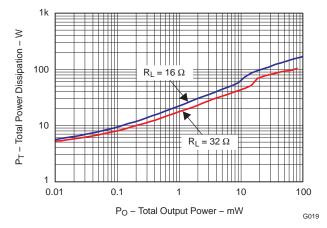

$T_{A}=25^{\circ}C,\ AV_{DD}\ (V_{DD})=3.6\ V,\ GAIN=0\ dB,\ C_{HPVDD}=C_{HPVSS}=2.2\ \mu F,\ C_{INPUT}=C_{FLYING}=1\ \mu F,\ Outputs\ out\ of\ phase$

Figure 19.

# TOTAL POWER DISSIPATION vs TOTAL OUTPUT POWER

Figure 21.

# SUPPLY CURRENT vs TOTAL OUTPUT POWER

Figure 20.

#### OUTPUT VOLTAGE vs SUPPLY VOLTAGE

Figure 22.

$T_{A}=25^{\circ}C,\ AV_{DD}\ (V_{DD})=3.6\ V,\ GAIN=0\ dB,\ C_{HPVDD}=C_{HPVSS}=2.2\ \mu F,\ C_{INPUT}=C_{FLYING}=1\ \mu F,\ Outputs\ out\ of\ phase$

Figure 23.

Figure 24.

Figure 25.

Figure 26.

12

#### **APPLICATION INFORMATION**

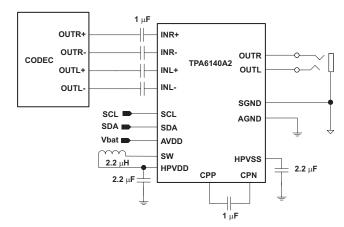

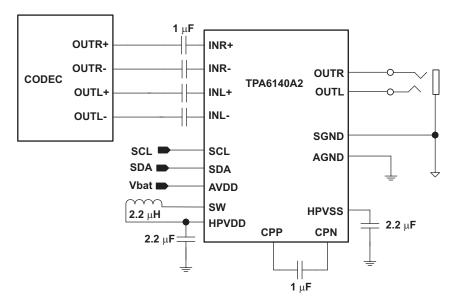

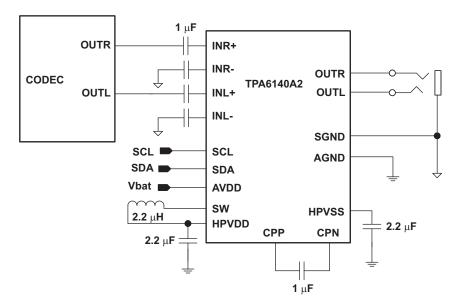

#### **APPLICATION CIRCUIT**

Figure 27. Typical Apps Configuration with Differential Input Signals

Figure 28. Typical Apps Configuration with Single-Ended Input Signals

#### **CLASS-G HEADPHONE AMPLIFIER**

Class-G amplifiers use adaptive supply rails. The TPA6140A2 includes a built-in step-down converter to create the headphone amplifier positive supply voltage, HPVDD. A charge pump inverts HPVDD and creates the amplifier negative supply voltage, HPVSS. This allows the headphone amplifier output to be centered at 0 V and eliminates DC blocking capacitors.

When audio signal amplitude is low, the step-down converter generates a low HPVDD voltage. This minimizes TPA6140A2 power consumption while playing low amplitude, high fidelity audio. If audio amplitude increases, either due to louder music or a transient peak, then the step-down converter generates a higher HPVDD voltage. The HPVDD rise rate is faster than the audio peak rise time. This prevents audio distortion or clipping. Audio quality and noise floor are not affected by HPVDD.

This adaptive HPVDD minimizes TPA6140A2 supply current while avoiding clipping and distortion. Because normal listening levels are below 200 mV<sub>RMS</sub>, HPVDD is most often at its lowest voltage. Thus, the TPA6140A2 has higher efficiency than traditional Class-AB headphone amplifiers.

The following equations compare a Class-AB amplifier to a Class-G amplifier. Both operate with identical battery voltage, load impedance, and output voltage swing. For this study case, we assume a normal listening level of  $200 \text{ mV}_{RMS}$  with no DirectPath<sup>TM</sup> in order to simplify the calculations.

- P<sub>SUP</sub>: Supplied power

- V<sub>SUP</sub>: Supply voltage

- I<sub>SUP</sub>: Supply current

- V<sub>REG</sub>: DC/DC converter output voltage

- P<sub>RFG</sub>: DC/DC converter output power

- V<sub>I OAD</sub>: Voltage across the load

- R<sub>LOAD</sub>: Load impedance

- PLOAD: Power dissipated at the load

- I<sub>LOAD</sub>: Current supplied to the load

Given an amplifier driving 200 mV<sub>RMS</sub> into a 32  $\Omega$  load, the output current to the load is:

$$I_{LOAD} = \frac{V_{LOAD}}{R_{LOAD}} = \frac{200 \text{ mV}_{RMS}}{32 \Omega} = 6.25 \text{ mA}$$

(1)

Assuming a quiescent current of 1 mA (I<sub>DDQ</sub>) the total current supplied to the amplifier is:

$$I_{SUP} = I_{LOAD} + I_{DDQ} = 7.25 \text{ mA}$$

(2)

The total power supplied to a Class-AB amplifier is then calculated as:

$$P_{SUP} = V_{SUP} \times I_{SUP} = 4.2 \text{ V} \times 7.25 \text{ mA} = 30.45 \text{ mW}$$

(3)

For a Class-G amplifier where the voltage rails are generated by a switching DC/DC converter, the supplied power will depend on the DC/DC converter output voltage and efficiency. Assuming the DC/DC converter output voltage is 1.3 V:

$$P_{REG} = V_{REG} \times I_{SUP} = 1.3 \text{ V} \times 7.25 \text{ mA} = 9.425 \text{ mW}$$

(4)

The total supplied power will be the DC/DC converter output power divided by the efficiency of the DC/DC converter. Assuming 90% step-down efficiency, total power supplied to the Class-G amplifier is:

$$P_{SUP} = \frac{P_{REG}}{90\%} = 11.09 \text{ mW}$$

(5)

Class-G headphone amplifiers achieve much higher efficiency than equivalent Class-AB amplifiers.

www.ti.com

#### INDUCTOR SELECTION

The TPA6140A2 requires one inductor for its DC/DC converter. The following table lists recommended inductors. Inductors not shown on this table can be be used if they have similar performance characteristics.

When selecting an inductor observe the following rules:

- Lower DCR increases DC/DC converter efficiency.

- The minimum working inductance should never be below 1 μH.

- Include temperature and aging derating factors into the inductor value calculations.

| MANUFACTURER | PART NUMBER    |

|--------------|----------------|

| токо         | MDT2012-CH2R2A |

| Murata       | LQM21PN2R2MC0D |

| Murata       | LQH2MCN2R2M02L |

| Taina Vindan | BRL2012T2R2M   |

| Taiyo Yuden  | BRC1608T2R2M   |

#### **GROUND SENSE FUNCTION**

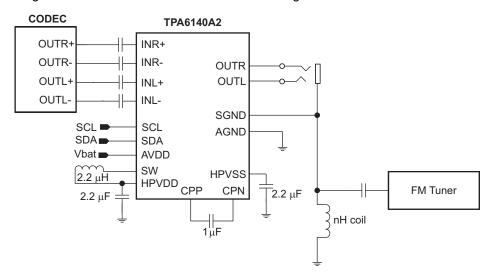

The ground sense pin, SGND, reduces ground-loop noise when the audio output jack is connected to a different ground reference than codec and amplifier ground. Always connect the SGND pin to the headphone jack. This reduces output offset voltage and eliminates turn-on pop. Figure 29 shows how to connect SGND when an FM radio antenna function is implemented on the headphone wire. The nH coil and capacitor separate the RF signal from the audio GND signal. In this case, SGND is used to eliminate the offset voltage that is generated from the audio signal current and the RF coil low-frequency impedance.

The voltage difference between SGND and AGND cannot be greater than ±300 mV. The amplifier performance degrades if the voltage difference between SGND and AGND is greater than ±300 mV.

Figure 29. Sense Ground

Copyright © 2009, Texas Instruments Incorporated

#### HIGH OUTPUT IMPEDANCE

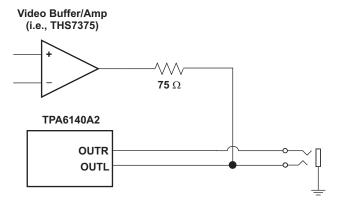

The TPA6140A2 has a HI-Z bit option that increases output impedance while muting the amplifier. Set the HiZ\_L and HiZ\_R bits (register 3, bits 1 and 0) to HIGH to activate the HI-Z mode. This feature allows the headphone output jack to be shared for other functions besides audio. For example, sharing of a headphone jack between audio and video as shown in Figure 30. In HI-Z mode, the TPA6140A2 output impedance is high enough to prevent video signal attenuation.

| SWS BIT | HI-Z BIT | OUTPUT<br>IMPEDANCE | SUPPLY<br>CURRENT | MAXIMUM EXTERNAL<br>VOLTAGE ALLOWED ON<br>OUTPUT PINS | COMMENTS      |

|---------|----------|---------------------|-------------------|-------------------------------------------------------|---------------|

| 1       | 0        | 8 kΩ                | . 2 4             | -0.3 V to 3.3 V <sup>(1)</sup>                        | Chutdawa mada |

| 1       | 1        | 8.5 kΩ              | < 3 μΑ            | -0.3 V 10 3.3 V V                                     | Shutdown mode |

| 0       | 0        | ≤1Ω                 | 1.2 mA            | -                                                     | Active mode   |

|         |          | 8.5 kΩ @ 40kHz      |                   |                                                       |               |

| 0       | 1        | 600 Ω @ 6 MHz       | 1 mA              | –1.8 V to 1.8 V                                       | HI-Z mode     |

|         |          | 400 Ω @ 13 MHz      |                   |                                                       |               |

(1) If  $AV_{DD}$  is < 3.3 V, then maximum allowed external voltage applied is  $AV_{DD}$  in this mode

Figure 30. Sharing One Connector Between Audio and Video Signals Example

#### **HEADPHONE AMPLIFIERS**

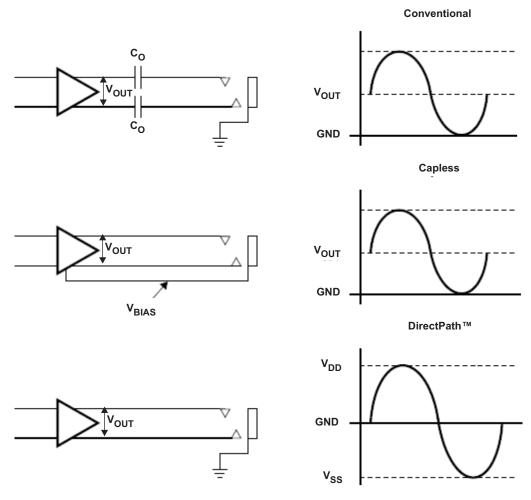

Single-supply headphone amplifiers typically require dc-blocking capacitors to remove dc bias from their output voltage. The top drawing in Figure 31 illustrates this connection. If dc bias is not removed, large dc current will flow through the headphones which wastes power, clips the output signal, and potentially damages the headphones.

These dc-blocking capacitors are often large in value and size. Headphone speakers have a typical resistance between 16  $\Omega$  and 32  $\Omega$ . This combination creates a high-pass filter with a cutoff frequency as shown in Equation 6, where R<sub>L</sub> is the load impedance, C<sub>O</sub> is the dc-blocking capacitor, and f<sub>C</sub> is the cutoff frequency.

$$f_{C} = \frac{1}{2\pi R_{L} C_{O}} \tag{6}$$

For a given high-pass cutoff frequency and load impedance, the required dc-blocking capacitor is found as:

$$C_{O} = \frac{1}{2\pi f_{C} R_{L}} \tag{7}$$

Reducing  $f_C$  improves low frequency fidelity and requires a larger dc-blocking capacitor. To achieve a 20 Hz cutoff with 16  $\Omega$  headphones,  $C_O$  must be at least 500  $\mu$ F. Large capacitor values require large packages, consuming PCB area, increasing height, and increasing cost of assembly. During start-up or shutdown the dc-blocking capacitor has to be charged or discharged. This causes an audible pop on start-up and power-down. Large dc-blocking capacitors also reduce audio output signal fidelity.

www.ti.com

Two different headphone amplifier architectures are available to eliminate the need for dc-blocking capacitors. The Capless amplifier architecture provides a reference voltage to the headphone connector shield pin as shown in the middle drawing of Figure 31. The audio output signals are centered around this reference voltage, which is typically half of the supply voltage to allow symmetrical output voltage swing.

When using a Capless amplifier do not connect the headphone jack shield to any ground reference or large currents will result. This makes Capless amplifiers ineffective for plugging non-headphone accessories into the headphone connector. Capless amplifiers are useful only with floating GND headphones.

Figure 31. Amplifier Applications

The DirectPath™ amplifier architecture operates from a single supply voltage and uses an internal charge pump to generate a negative supply rail for the headphone amplifier. The output voltages are centered around 0 V and are capable of positive and negative voltage swings as shown in the bottom drawing of Figure 31. DirectPath amplifiers require no output dc-blocking capacitors. The headphone connector shield pin connects to ground and will interface with headphones and non-headphone accessories. The TPA6140A2 is a DirectPath amplifier.

#### **ELIMINATING TURN-ON POP AND POWER SUPPLY SEQUENCING**

The TPA6140A2 has excellent noise and turn-on / turn-off pop performance. It uses an integrated click-and-pop suppression circuit to allow fast start-up and shutdown without generating any voltage transients at the output pins. Typical start-up time from shutdown is 5 ms.

DirectPath technology keeps the output dc voltage at 0 V even when the amplifier is powered up. The DirectPath technology together with the active pop-and-click suppression circuit eliminates audible transients during start up and shutdown.

Use input coupling capacitors to ensure inaudible turn-on pop. Activate the TPA6140A2 after all audio sources have been activated and their output voltages have settled. During power-down, deactivate the TPA6140A2 before deactivating the audio input source.

#### RF AND POWER SUPPLY NOISE IMMUNITY

The TPA6140A2 employs a new differential amplifier architecture to achieve high power supply noise rejection and RF noise rejection. RF and power supply noise are common in modern electronics. Although RF frequencies are much higher than the 20 kHz audio band, signal modulation often falls in-band. This, in turn, modulates the supply voltage, allowing a coupling path into the audio amplifier. A common example is the 217 Hz GSM frame-rate buzz often heard from an active speaker when a cell phone is placed nearby during a phone call.

The TPA6140A2 has excellent rejection of power supply and RF noise, preventing audio signal degradation.

#### INPUT COUPLING CAPACITORS

Input coupling capacitors block any dc bias from the audio source and ensure maximum dynamic range. Input coupling capacitors also minimize TPA6140A2 turn-on pop to an inaudible level.

The input capacitors are in series with TPA6140A2 internal input resistors, creating a high-pass filter. Equation 8 calculates the high-pass filter corner frequency. The input impedance,  $R_{\rm IN}$ , is dependent on device gain. Larger input capacitors decrease the corner frequency. See the Operating Characteristics table for input impedance values.

$$f_{C} = \frac{1}{2\pi R_{IN} C_{IN}} \tag{8}$$

For a given high-pass cutoff frequency, the minimum input coupling capacitor is found as:

$$C_{\mathsf{IN}} = \frac{1}{2\pi f_{\mathsf{C}} R_{\mathsf{IN}}} \tag{9}$$

Example: Design for a 20 Hz corner frequency with a TPA6140A2 gain of +6 dB. The Operating Characteristics table gives  $R_{IN}$  as 13.2 k $\Omega$ . Equation 9 shows the input coupling capacitors must be at least 0.6  $\mu$ F to achieve a 20 Hz high-pass corner frequency. Choose a 0.68  $\mu$ F standard value capacitor for each TPA6140A2 input (X5R material or better is required for best performance).

Input capacitors can be removed provided the TPA6140A2 inputs are driven differentially with less than  $\pm 1~V_{RMS}$  and the common-mode voltage is within the input common-mode range of the amplifier. Without input capacitors turn-on pop performance may be degraded and should be evaluated in the system.

#### CHARGE PUMP FLYING CAPACITOR AND HPVSS CAPACITOR

The TPA6140A2 uses a built-in charge pump to generate a negative voltage supply for the headphone amplifiers. The charge pump flying capacitor connects between CPP and CPN. It transfers charge to generate the negative supply voltage. The HPVSS capacitor must be at least equal in value to the flying capacitor to allow maximum charge transfer. Use low equivalent-series-resistance (ESR) ceramic capacitors (X5R material or better is required for best performance) to maximize charge pump efficiency. Typical values are 1  $\mu$ F to 2.2  $\mu$ F for the HPVSS and flying capacitors. Although values down to 0.47  $\mu$ F can be used, total harmonic distortion (THD) will increase.

www.ti.com

#### POWER SUPPLY AND HPVDD DECOUPLING CAPACITORS AND CONNECTIONS

The TPA6140A2 DirectPath headphone amplifier requires adequate power supply decoupling to ensure that output noise and total harmonic distortion (THD) remain low. Use good low equivalent-series-resistance (ESR) ceramic capacitors (X5R material or better is required for best performance). Place a 2.2 µF capacitor within 5 mm of the AVDD pin. Reducing the distance between the decoupling capacitor and AVDD minimizes parasitic inductance and resistance, improving TPA6140A2 supply rejection performance. Use 0402 or smaller size capacitors if possible. Ensure that the ground connection of each of the capacitors has a minimum length return path to the device. Failure to properly decouple the TPA6140A2 may degrade audio or EMC performance.

For additional supply rejection, connect an additional 10  $\mu$ F or higher value capacitor between AVDD and ground. This will help filter lower frequency power supply noise. The high power supply rejection ratio (PSRR) of the TPA6140A2 makes the 10  $\mu$ F capacitor unnecessary in most applications.

Connect a 2.2 µF capacitor between HPVDD and ground. This ensures the amplifier internal bias supply remains stable and maximizes headphone amplifier performance.

DO NOT connect HPVDD directly to AVDD or an external supply voltage. The voltage at HPVDD is generated internally. Connecting HPVDD to an external voltage can damage the device.

#### LAYOUT RECOMMENDATIONS

#### **GND CONNECTIONS**

The SGND pin is an input reference and must be connected to the headphone ground connector pin. This ensures no turn-on pop and minimizes output offset voltage. Do not connect more than ±0.3 V to SGND.

AGND is a power ground. Connect supply decoupling capacitors for AVDD, HPVDD, and HPVSS to AGND.

#### GENERAL I<sup>2</sup>C OPERATION

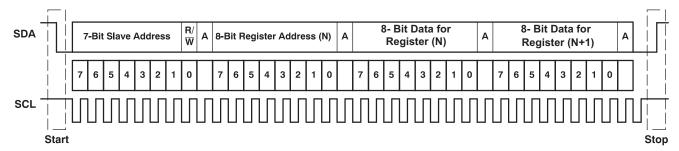

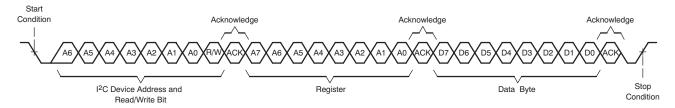

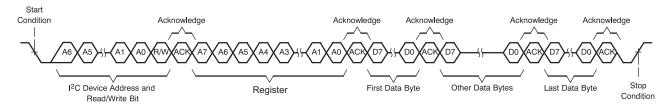

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The bus transfers data serially one bit at a time. The address and data 8-bit bytes are transferred most significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions bust occur within the low time of the clock period. Figure 32 shows a typical sequence. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TPA6140A2 holds SDA low during the acknowledge clock period to indicate acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection.

The TPA6140A2 operates as an  $I^2C$  slave. The  $I^2C$  voltage can not exceed the TPA6140A2 supply voltage, AVDD.

An external pull-up resistor must be used for the SDA and SCL signals to set the logic high level for the bus. When the bus level is 3.3 V, use pull-up resistors between 660  $\Omega$  and 1.2 k $\Omega$ .

Copyright © 2009, Texas Instruments Incorporated

Figure 32. Typical I<sup>2</sup>C Sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 32.

#### SINGLE-AND MULTIPLE-BYTE TRANSFERS

The serial control interface supports both single-byte and multi-byte read/write operations for all registers.

During multiple-byte read operations, the TPA6140A2 responds with data, a byte at a time, starting at the register assigned, as long as the master device continues to respond with acknowledges.

The TPA6140A2 supports sequential I<sup>2</sup>C addressing. For write transactions, if a register is issued followed by data for that register and all the remaining registers that follow, a sequential I<sup>2</sup>C write transaction has taken place. For I<sup>2</sup>C sequential write transactions, the register issued then serves as the starting point, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines to how many registers are written.

#### SINGLE-BYTE WRITE

As shown in Figure 33, a single-byte data write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the TPA6140A2 responds with an acknowledge bit. Next, the master transmits the register byte corresponding to the TPA6140A2 internal memory address being accessed. After receiving the register byte, the TPA6140A2 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data write transfer.

Figure 33. Single-Byte Write Transfer

#### MULTIPLE-BYTE WRITE AND INCREMENTAL MULTIPLE-BYTE WRITE

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the TPA6140A2 as shown in Figure 34. After receiving each data byte, the TPA6140A2 responds with an acknowledge bit.

Figure 34. Multiple-Byte Write Transfer

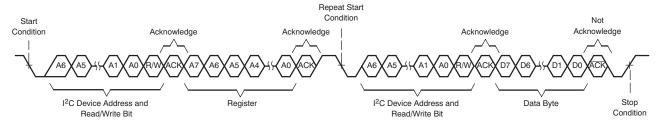

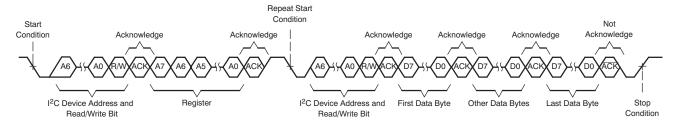

#### SINGLE-BYTE READ

As shown in Figure 35, a single-byte data read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte of the internal memory address to be read. As a result, the read/write bit is set to a 0.

After receiving the TPA6140A2 address and the read/write bit, the TPA6140A2 responds with an acknowledge bit. The master then sends the internal memory address byte, after which the TPA6140A2 issues an acknowledge bit. The master device transmits another start condition followed by the TPA6140A2 address and the read/write bit again. This time, the read/write bit is set to 1, indicating a read transfer. Next, the TPA6140A2 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer.

Figure 35. Single-Byte Read Transfer

#### **MULTIPLE-BYTE READ**

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes are transmitted by the TPA6140A2 to the master device as shown in Figure 36. With the exception of the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 36. Multiple-Byte Read Transfer

#### **REGISTER MAP**

#### Table 1. Register Map

| REGISTER | BIT 7   | BIT 6   | BIT 5     | BIT 4     | BIT 3      | BIT 2      | BIT 1      | BIT 0      |

|----------|---------|---------|-----------|-----------|------------|------------|------------|------------|

| 1        | HP_EN_L | HP_EN_R | 0         | 0         | 0          | 0          | Thermal    | SWS        |

| 2        | Mute_L  | Mute_R  | Volume[4] | Volume[3] | Volume[2]  | Volume[1]  | Volume[0]  | 0          |

| 3        | 0       | 0       | 0         | 0         | 0          | 0          | HiZ_L      | HiZ_R      |

| 4        | 0       | 0       | 0         | 0         | Version[3] | Version[2] | Version[1] | Version[0] |

| 5        | RFT     | RFT     | RFT       | RFT       | RFT        | RFT        | RFT        | RFT        |

| 6        | RFT     | RFT     | RFT       | RFT       | RFT        | RFT        | RFT        | RFT        |

| 7        | RFT     | RFT     | RFT       | RFT       | RFT        | RFT        | RFT        | RFT        |

| 8        | RFT     | RFT     | RFT       | RFT       | RFT        | RFT        | RFT        | RFT        |

Bits labeled "Reserved" are reserved for future enhancements. They may not be written to. When read, they will show a "0" value.

Bits labeled "RFT" are reserved for TI testing. Under no circumstances must any data be written to these registers. If read, these bits may assume any value.

The TPA6140A2 I<sup>2</sup>C address is 0xC0 (binary 11000000) for writing an 0xC1 (binary 11000001) for reading. If a different I<sup>2</sup>C address is required, please contact your local TI representative.

#### Fault Register (Address: 1)

| BIT         | 7       | 6       | 5 | 4 | 3 | 2 | 1       | 0   |

|-------------|---------|---------|---|---|---|---|---------|-----|

| Function    | HP_EN_L | HP_EN_R | 0 | 0 | 0 | 0 | Thermal | SWS |

| Reset Value | 0       | 0       | 0 | 0 | 0 | 0 | 0       | 1   |

HP\_EN\_L Enable bit for the left-channel amplifier. Amplifier is active when bit is high.

HP\_EN\_R Enable bit for the right-channel amplifier. Amplifier is active when bit is high.

Thermal Bit sets to 1 to indicate thermal shutdown. Once temperature decreases below a safe level, the

TPA6140A2 re-activates regardless of previous bit status. This bit is clear-on-read.

SWS Software shutdown control. Set bit to 1 to initiate software shutdown. Set bit to 0 to activate

charge-pump. SWS must remain at 0 for normal operation. Use SWS instead of HP\_EN\_L and HP\_EN\_R to ensure lowest current consumption and highest input to output signal attenuation

when disabling the amplifier.

#### Volume and Mute Register (Address: 2)

| BIT            | 7      | 6      | 5         | 4         | 3         | 2         | 1         | 0 |

|----------------|--------|--------|-----------|-----------|-----------|-----------|-----------|---|

| Function       | Mute_L | Mute_R | Volume[4] | Volume[3] | Volume[2] | Volume[1] | Volume[0] | 0 |

| Reset<br>Value | 1      | 1      | 0         | 0         | 0         | 0         | 0         | 0 |

Mute\_L Left channel mute. Set bit to 1 to mute left channel.

Mute R Right channel mute. Set bit to 1 to mute right channel.

Volume[5:0] Volume control byte. Set to 111110 for highest gain, 4 dB; set to 000000 for lowest gain, -59 dB

22

www.ti.com

#### **Output Impedance Register (Address: 3)**

| BIT         | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0     |

|-------------|---|---|---|---|---|---|-------|-------|

| Function    | 0 | 0 | 0 | 0 | 0 | 0 | HiZ_L | HiZ_R |

| Reset Value | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0     |

Reserved These bits are reserved for future enhancements. Do not write to these bits as writing to these bits may change device function. If read these bits may assume any value.

HiZ\_L Set to 1 to put left channel amplifier output in three-state high impedance mode.

HiZ\_R Set to 1 to put right channel amplifier output in three-state high impedance mode.

## I<sup>2</sup>C Address and Version Register (Address: 4)

| BIT         | 7 | 6 | 5 | 4 | 3          | 2          | 1          | 0          |

|-------------|---|---|---|---|------------|------------|------------|------------|

| Function    | 0 | 0 | 0 | 0 | Version[3] | Version[2] | Version[1] | Version[0] |

| Reset Value | 0 | 0 | 0 | 0 | 0          | 0          | 0          | 0          |

Version[3:0] The version bits track the revision of the silicon. Valid values are 0000 for the first silicon TPA6140A2.

#### Reserved for Test (Addresses: 5-8)

| BIT         | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Function    | RFT |

| Reset Value | x   | х   | х   | х   | х   | х   | x   | х   |

RFT Reserved for Test. Do NOT write to these registers.

#### **VOLUME CONTROL**

Set the TPA6140A2 volume control through the I<sup>2</sup>C interface. Write to the Volume[5:0] byte at Register 2, Bits 5-0. Although the gain byte is a 6-bit word, only 32 steps are available. The least significant bit of the Volume[5:0] byte is treated as a don't care bit.

| GAIN CONTROL BYTE: MUTE<br>[7:6],<br>VOLUME[5:0] | NOMINAL GAIN | GAIN CONTROL BYTE: MUTE [7:6],<br>VOLUME[5:0] | NOMINAL GAIN |

|--------------------------------------------------|--------------|-----------------------------------------------|--------------|

| 11XXXXXX                                         | -80 dB       | 0010000x                                      | –11 dB       |

| 000000x                                          | –59 dB       | 0010001x                                      | –10 dB       |

| 000001x                                          | –55 dB       | 0010010x                                      | −9.0 dB      |

| 0000010x                                         | –51 dB       | 0010011x                                      | -8.0 dB      |

| 0000011x                                         | –47 dB       | 0010100x                                      | -7.0 dB      |

| 0000100x                                         | –43 dB       | 0010101x                                      | −6.0 dB      |

| 0000101x                                         | –39 dB       | 0010110x                                      | -5.0dB       |

| 0000110x                                         | −35 dB       | 0010111x                                      | -4.0 dB      |

| 0000111x                                         | –31 dB       | 0011000x                                      | −3.0 dB      |

| 0001000x                                         | –27 dB       | 0011001x                                      | −2.0 dB      |

| 0001001x                                         | –25 dB       | 0011010x                                      | −1.0 dB      |

| 0001010x                                         | –23 dB       | 0011011x                                      | +0.0 dB      |

| 0001011x                                         | –21 dB       | 0011100x                                      | +1.0 dB      |

| 0001100x                                         | –19 dB       | 0011101x                                      | +2.0 dB      |

| 0001101x                                         | –17 dB       | 0011110x                                      | +3.0 dB      |

| 0001110x                                         | –15 dB       | 0011111x                                      | +4.0 dB      |

| 0001111x                                         | –13 dB       |                                               |              |

Copyright © 2009, Texas Instruments Incorporated

#### **OPERATING MODES**

#### HARDWARE SHUTDOWN

Hardware shutdown is not available in the TPA6140A2. The SWS register (Software Shutdown) must be used to shutdown the amplifier.

#### **SOFTWARE SHUTDOWN**

Set software shutdown by writing a logic 1 in register 1, bit 0 (SWS bit). Software shutdown places the device in the lowest power state (see the Electrical Characteristics Table for values). Engaging software shutdown turns off the buck regulator and charge pump and disables the amplifier outputs. Write a logic 0 to the SWS bit to reactivate the device.

Note that when the device is in SWS mode all registers will maintain their values. The HP\_EN\_L and HP\_EN\_R bits can be reset because a full word must be used when writing just one bit to the register.

To ensure lowest current consumption and highest input to output signal attenuation, SWS must be used instead of HP\_EN\_L and HP\_EN\_R (set HP\_EN\_L and HP\_EN\_R to logic 1) when disabling both channels of the amplifier simultaneously. Set HP\_EN\_L and HP\_EN\_R to logic 1 before changing SWS from logic 0 to logic 1.

#### **MUTE MODE**

Set the Mute\_L bit to 1 to mute the left channel output. Set the Mute\_R bit to 1 to mute the right channel output. They are respectively located at Register 2, Bits 7 and 6. Mute attenuation is -80 dB, typical. Mute attenuation can only be guaranteed when the amplifier is operational (SWS = 0) and enabled (HP\_EN\_L or HP\_EN\_R = 1)

#### **HI-Z MODE**

HI-Z mode mutes the device and puts the amplifier outputs into a high impedance state. Use this configuration when the outputs of the TPA6140A2 share traces with other devices whose outputs may be active. Write a logic 1 in register 3, bits 0 and 1 to enable Hi-Z mode for the left and right outputs. Place a logic 0 in register 3, bits 0 and 1 to disable the Hi-Z state. The left and right outputs can be placed into a Hi-Z state individually.

Note that to use the Hi-Z mode, the SWS bit must be equal to logic 0 (amplifier operational) and the output headphone amplifiers must NOT be enabled (HP EN L and HP EN R = 0).

#### **DEFAULT MODE AT START-UP**

On power-up, the TPA6140A2 initializes in the following conditions:

- SWS = 1 (Shutdown mode)

- HP\_EN\_L = HP\_EN\_R = 0 (Outputs disabled)

- Hi-Z\_L = Hi-Z\_R = 0 (Hi-Z off)

- Mute\_L = Mute\_R = 1 (Amplifiers muted)

- VOLUME = −59 dB

#### **PACKAGE INFORMATION**

#### Package Dimensions

The package dimensions for this YFF package are shown in the table below. See the package drawing at the end of this data sheet for more details.

#### Table 2. YFF Package Dimensions

| Packaged Devices | D                            | E                            |

|------------------|------------------------------|------------------------------|

| TPA6140A2YFF     | Min = 1530μm<br>Max = 1590μm | Min = 1530μm<br>Max = 1590μm |

24

#### www.ti.com

# **REVISION HISTORY**

| CI | hanges from Original (March 2009) to Revision A        | Pag | е |

|----|--------------------------------------------------------|-----|---|

| •  | Changed C4 to D4 in terminal functions                 |     | 3 |

| •  | Changed D4 to C4 in terminal functions                 | :   | 3 |

| •  | Deleted lead temperature from absolute maximum ratings |     | 4 |

Product Folder Link(s): TPA6140A2

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TPA6140A2YFFR    | ACTIVE | DSBGA        | YFF                | 16   | 3000           | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | AIFI                    | Samples |

| TPA6140A2YFFT    | ACTIVE | DSBGA        | YFF                | 16   | 250            | RoHS & Green | SNAGCU                        | Level-1-260C-UNLIM | -40 to 85    | AIFI                    | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

www.ti.com 18-Jun-2020

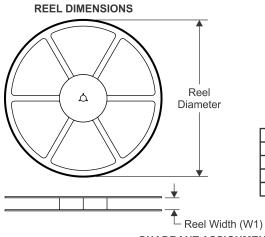

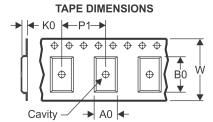

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

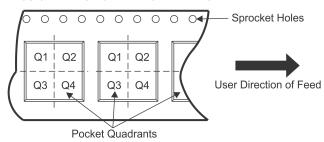

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA6140A2YFFR | DSBGA           | YFF                | 16 | 3000 | 180.0                    | 8.4                      | 1.71       | 1.71       | 0.81       | 4.0        | 8.0       | Q1               |

| TPA6140A2YFFT | DSBGA           | YFF                | 16 | 250  | 180.0                    | 8.4                      | 1.71       | 1.71       | 0.81       | 4.0        | 8.0       | Q1               |

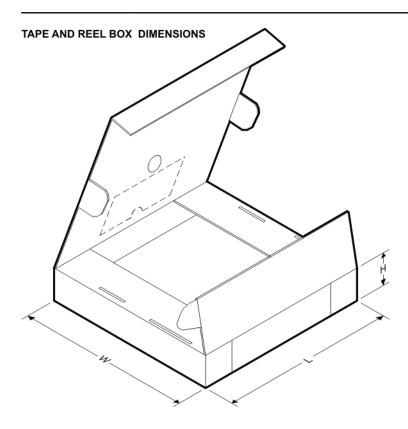

www.ti.com 18-Jun-2020

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA6140A2YFFR | DSBGA        | YFF             | 16   | 3000 | 182.0       | 182.0      | 20.0        |

| TPA6140A2YFFT | DSBGA        | YFF             | 16   | 250  | 182.0       | 182.0      | 20.0        |

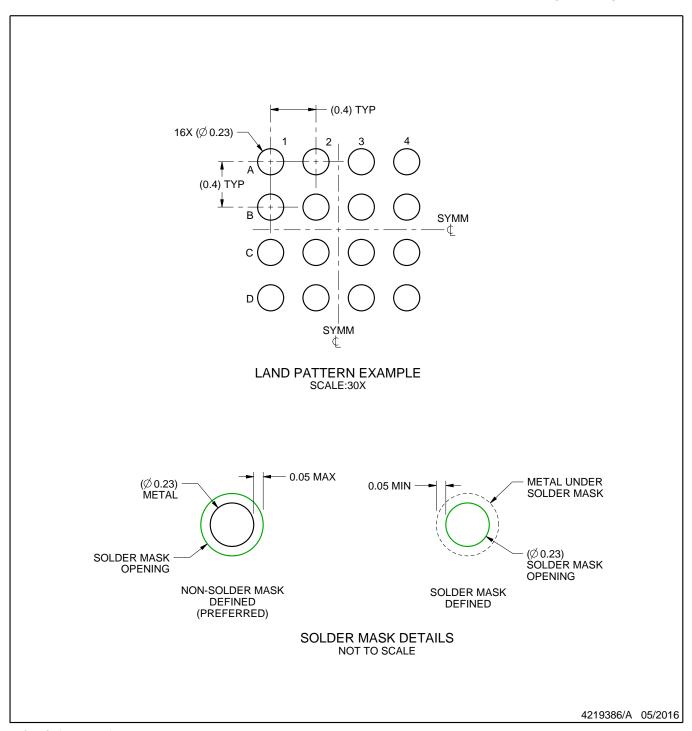

DIE SIZE BALL GRID ARRAY

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

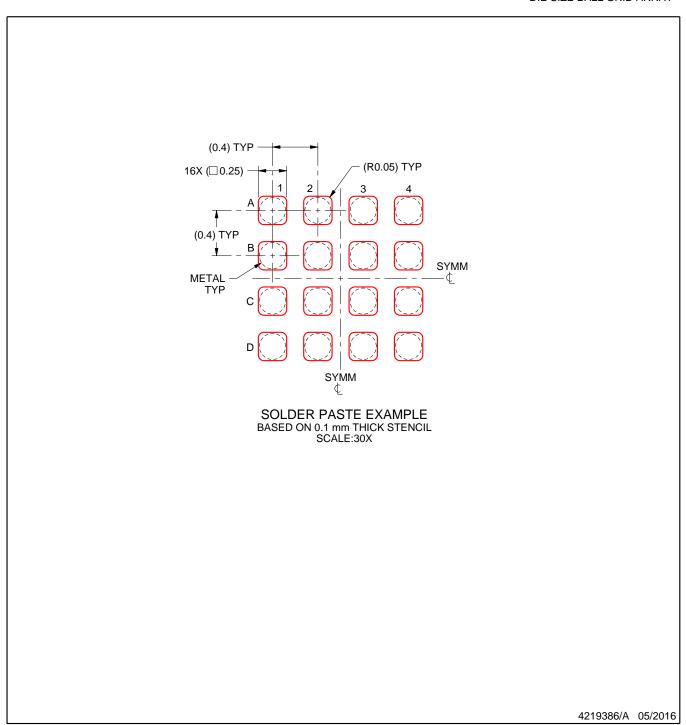

3. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. For more information, see Texas Instruments literature number SNVA009 (www.ti.com/lit/snva009).

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated