# LM49251 Boomer® Audio Power Amplifier Series Stereo Audio Subsystem with Class G Headphone Amplifier and Class D Speaker Amplifier with Speaker Protection

Check for Samples: LM49251

#### **FEATURES**

- **Class G Ground Referenced Headphone Outputs**

- E<sup>2</sup>S Class D Amplifier

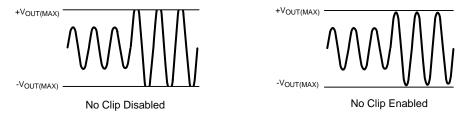

- **No Clip Function**

- **Power Limiter Speaker Protection**

- I<sup>2</sup>C Volume and Mode Control

- **Advanced Click-and-Pop Suppression**

- Micro-Power Shutdown

#### **APPLICATIONS**

- **Feature Phones**

- **Smart Phones**

#### **KEY SPECIFICATIONS**

- Class G Headphone Amplifier, HPV<sub>DD</sub> = 1.8V,  $R_L = 32\Omega$

- IDDQ<sub>HP</sub>: 1.15 mA (Typ)

- Output Power, THD+N ≤ 1%: 20 mW (Typ)

- Stereo Class D Speaker Amplifier  $R_L = 8\Omega$

- Output Power, THD+N ≤ 1%, LSV<sub>DD</sub> = 5.0V: 1.37 W (Typ)

- Output Power, THD+N ≤ 1%, LSV<sub>DD</sub> = 3.6V: 680 mW (Typ)

- Efficiency: 90% (Typ)

#### DESCRIPTION

The LM49251 is a fully integrated audio subsystem designed for portable handheld applications such as cellular phones. Part of TI's PowerWise family of products, the LM49251 utilizes a high efficiency class G headphone amplifier topology as well as a high efficiency class D loudspeaker.

The headphone amplifiers feature TI's class G ground referenced architecture that creates a groundreferenced output with dynamic supply rails for optimum efficiency. The stereo class D speaker amplifier provides both a no-clip feature and speaker protection. The Enhanced Emission Suppression (E<sup>2</sup>S) outputs feature a patented, ultra low EMI PWM architecture that significantly reduces RF emissions.

The LM49251 features separate volume controls for the mono and stereo inputs. Mode selection, shutdown control, and volume are controlled through an I<sup>2</sup>C compatible interface.

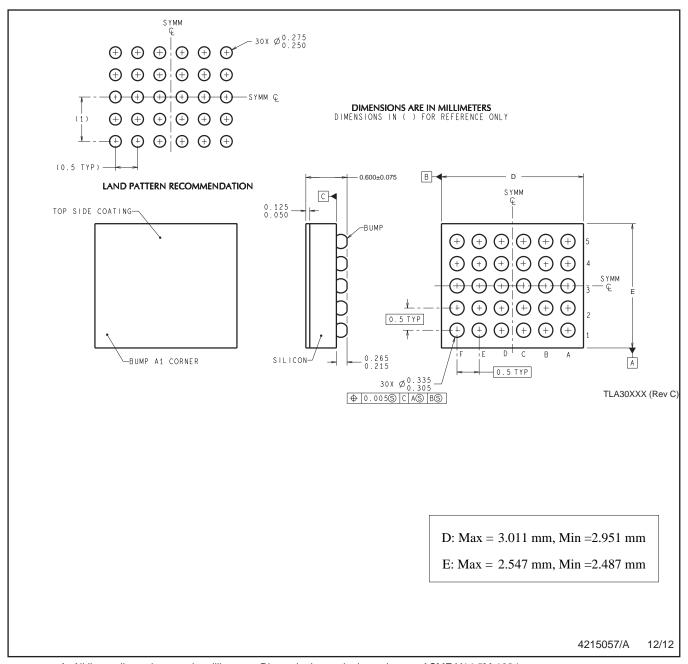

Click and pop suppression eliminates audible transients on power-up/down and during shutdown. The LM49251 is available in an ultra-small 30-bump DSBGA package (2.55mmx3.02mm)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

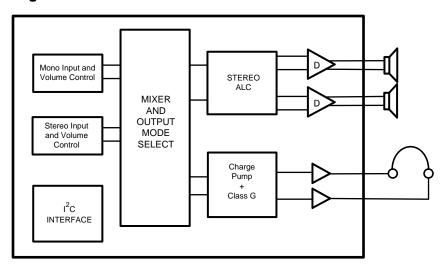

# **Simplified Block Diagram**

Figure 1. LM49251 Simplified Block Diagram

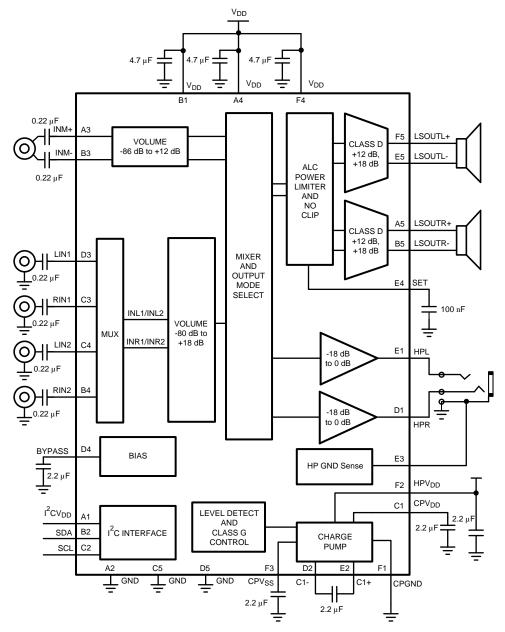

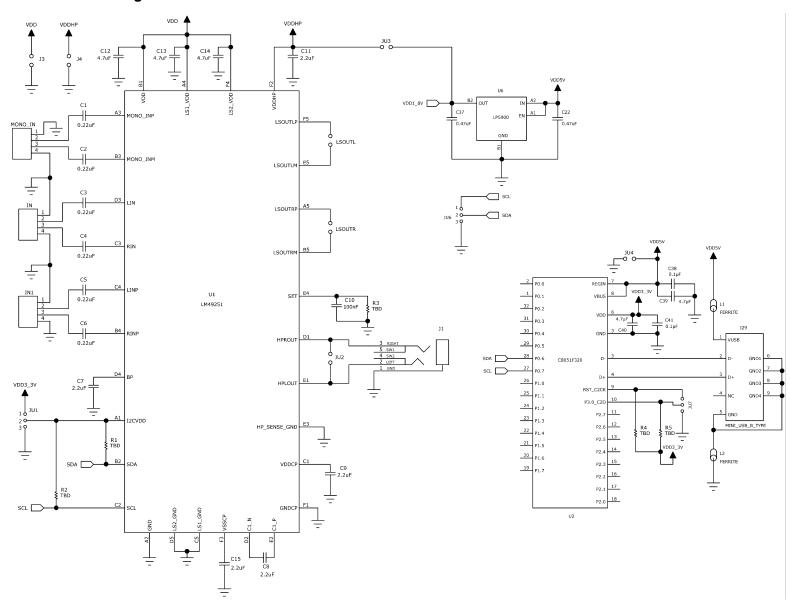

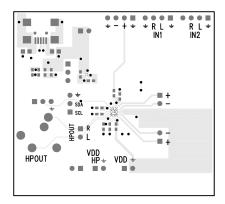

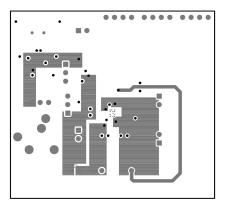

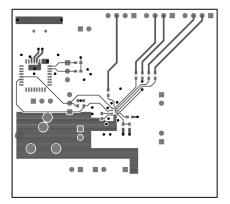

# **Typical Application**

Figure 2. Typical Audio Amplifier Application Circuit

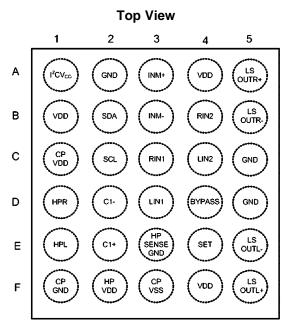

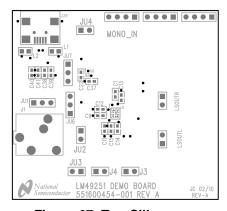

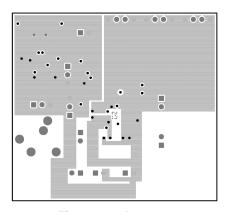

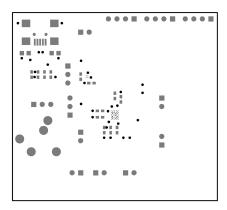

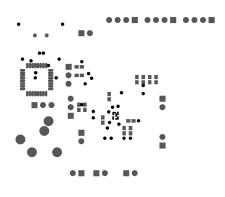

# **Connection Diagram**

Figure 3. DSBGA Package See Package Number YZR0030

**Table 1. Bump Description**

|      | Table 1: Bullip Description     |                                                |  |  |  |  |  |  |

|------|---------------------------------|------------------------------------------------|--|--|--|--|--|--|

| Bump | Name                            | Description                                    |  |  |  |  |  |  |

| A1   | I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C Power Supply                  |  |  |  |  |  |  |

| A2   | GND                             | Ground                                         |  |  |  |  |  |  |

| A3   | INM+                            | Mono Channel Non-Inverting Input               |  |  |  |  |  |  |

| A4   | $V_{DD}$                        | Loudspeaker Power Supply                       |  |  |  |  |  |  |

| A5   | LSOUTR+                         | Right Loudspeaker Non-Inverting Output         |  |  |  |  |  |  |

| B1   | $V_{DD}$                        | Loudspeaker Power Supply                       |  |  |  |  |  |  |

| B2   | SDA                             | I <sup>2</sup> C Serial Data Input             |  |  |  |  |  |  |

| В3   | INM-                            | Mono Channel Inverting Input                   |  |  |  |  |  |  |

| B4   | RIN2                            | Right Channel Input 2                          |  |  |  |  |  |  |

| B5   | LSOUTR-                         | Right Loudspeaker Inverting Output             |  |  |  |  |  |  |

| C1   | CPV <sub>DD</sub>               | Charge Pump Supply (internally generated)      |  |  |  |  |  |  |

| C2   | SCL                             | I <sup>2</sup> C Serial Clock Input            |  |  |  |  |  |  |

| C3   | RIN1                            | Right Channel Input 1                          |  |  |  |  |  |  |

| C4   | LIN2                            | Left Channel Input 2                           |  |  |  |  |  |  |

| C5   | GND                             | Ground                                         |  |  |  |  |  |  |

| D1   | HPR                             | Right Channel Headphone Output                 |  |  |  |  |  |  |

| D2   | C1-                             | Charge Pump Flying Capacitor Negative Terminal |  |  |  |  |  |  |

| D3   | LIN1                            | Left Channel Input 1                           |  |  |  |  |  |  |

| D4   | BYPASS                          | Mid-Rail Bias Bypass Node                      |  |  |  |  |  |  |

| D5   | GND                             | Ground                                         |  |  |  |  |  |  |

| E1   | HPL                             | Left Channel Headphone Output                  |  |  |  |  |  |  |

| E2   | C1+                             | Charge Pump Flying Capacitor Positive Terminal |  |  |  |  |  |  |

| E3   | HP SENSE GND                    | Headphone Ground Sense                         |  |  |  |  |  |  |

| E4   | SET                             | ALC Timing Set                                 |  |  |  |  |  |  |

#### **Table 1. Bump Description (continued)**

| Bump | Name              | Description                           |

|------|-------------------|---------------------------------------|

| E5   | LSOUTL-           | Left Loudspeaker Inverting Output     |

| F1   | CPGND             | Charge Pump Ground                    |

| F2   | HPV <sub>DD</sub> | Headphone Power Supply                |

| F3   | CPV <sub>SS</sub> | Charge Pump Output                    |

| F4   | $V_{DD}$          | Loudspeaker Power Supply              |

| F5   | LSOUTL+           | Left Loudspeaker Non-Inverting Output |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| Supply Voltage <sup>(1)</sup>     | V <sub>DD</sub> , I <sup>2</sup> CV <sub>DD</sub> | 6V                             |  |  |

|-----------------------------------|---------------------------------------------------|--------------------------------|--|--|

| Supply Voltage (**)               | HPV <sub>DD</sub>                                 | 3V                             |  |  |

| Storage Temperature               | re                                                |                                |  |  |

| Input Voltage                     |                                                   | -0.3V to V <sub>DD</sub> +0.3V |  |  |

| Power Dissipation (4)             |                                                   | Internally Limited             |  |  |

| ESD HBM <sup>(5)</sup>            |                                                   | 2000V                          |  |  |

| ESD MM <sup>(6)</sup>             |                                                   | 150V                           |  |  |

| ESD CDM <sup>(7)</sup>            |                                                   | 750V                           |  |  |

| Junction Temperature              |                                                   | 150°C                          |  |  |

| Thermal Resistance                | θ <sub>JA</sub> (TLA30B1A)                        | 90°C/W                         |  |  |

| Soldering Information: See AN-111 | 12 (Literature Number SNVA009)                    |                                |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified

- (2) The Electrical Characteristics tables list specified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (4) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>) / θ<sub>JA</sub> or the number given in *Absolute Maximum Ratings*, whichever is lower.

- Human body model, applicable std. JESD22-A114C.

- (6) Machine model, applicable std. JESD22-A115-A.

- (7) Charge device model, applicable std. JESD22-C101D.

# **Operating Ratings**

| Temperature Range $(T_{MIN} \le T_A \le T_{MAX})$ | $-40$ °C $\leq T_A \leq +85$ °C |                                 |

|---------------------------------------------------|---------------------------------|---------------------------------|

|                                                   | $V_{DD}$                        | $2.7V \le V_{DD} \le 5.5V$      |

| Supply Voltage                                    | HPV <sub>DD</sub>               | 1.6V ≤ HPV <sub>DD</sub> ≤ 2.0V |

|                                                   | $I^2C_{DD}$                     | $1.7V \le I^2CV_{DD} \le 5.5V$  |

### Electrical Characteristics (1)(2)(3)

The following specifications apply for  $A_V$  = 0dB,  $R_L$  = 15 $\mu$ H+8 $\Omega$ +15 $\mu$ H (Loudspeaker),  $R_L$  = 32 $\Omega$  (Headphone),  $C_{SET}$  = 100nF, f = 1kHz, ALC off, unless otherwise specified. Limits apply for  $T_A$  = 25°C.

|                     | Danamatan                                           | Took Conditions                                                                                                                                             | LM4                                     | Units      |                                              |  |  |

|---------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|----------------------------------------------|--|--|

| Parameter           |                                                     | Test Conditions                                                                                                                                             | Typ <sup>(4)</sup> Limit <sup>(5)</sup> |            | (Limits)                                     |  |  |

|                     |                                                     | V <sub>IN</sub> = 0, No Load                                                                                                                                | V <sub>IN</sub> = 0, No Load            |            |                                              |  |  |

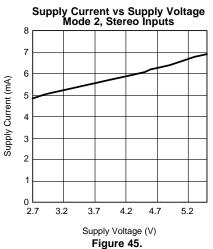

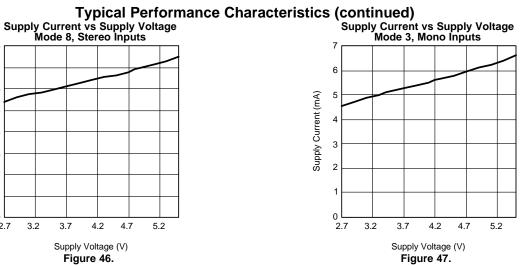

|                     |                                                     | LS Mode (stereo input), mode 2                                                                                                                              | 5.6                                     | 6.25       | mA (max)                                     |  |  |

|                     |                                                     | LS Mode (mono input), mode 3                                                                                                                                | 5.3                                     | 6.0        | mA (max)                                     |  |  |

|                     | Quiescent Power Supply Current                      | HP Mode (stereo input), mode 6                                                                                                                              | 2.1                                     | 2.4        | mA (max)                                     |  |  |

| I <sub>DD</sub>     | (LSV <sub>DD</sub> + V <sub>DD</sub> )              | HP Mode (mono input), mode 4                                                                                                                                | 1.8                                     | 2.0        | mA (max)                                     |  |  |

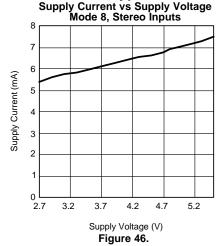

|                     |                                                     | LS+HP Mode (stereo input), mode 8                                                                                                                           | 6.1                                     | 6.8        | mA (max)                                     |  |  |

|                     |                                                     | LS+HP Mode (mono input), mode 5                                                                                                                             | 5.8                                     | 6.5        | mA (max)                                     |  |  |

|                     |                                                     | LS Mode (stereo input, ALC on), mode 2                                                                                                                      | 5.9                                     |            |                                              |  |  |

|                     | Quiescent Power Supply Current (HPV <sub>DD</sub> ) | V <sub>IN</sub> = 0, No Load, Mode 6                                                                                                                        | 1.15                                    | 1.45       | mA (max)                                     |  |  |

| IDD <sub>(HP)</sub> | Operating Power Supply Current                      | $P_{OUT} = 0.5$ mW, $GAMP\_SD = 0$ , $R_L = 32\Omega$ , $Mode 6$                                                                                            | 4.3                                     | 4.6        | mA (max)                                     |  |  |

|                     | (HPV <sub>DD</sub> )                                | $P_{OUT}$ = 1mW, GAMP_SD = 0,<br>R <sub>L</sub> = 32 $\Omega$ , Mode 6                                                                                      | 5.8                                     | 6.15       | mA (max)                                     |  |  |

| I <sub>SD</sub>     | Shutdown Current                                    |                                                                                                                                                             | 0.02                                    | 1          | μA (max)                                     |  |  |

| Vos                 | Output Offset Voltage                               | V <sub>IN</sub> = 0<br>Mode 3, mono input, A <sub>V</sub> = 6dB<br>Mode 4, mono input<br>Mode 2, stereo input, A <sub>V</sub> = 6dB<br>Mode 6, stereo input | 12<br>1.1<br>12<br>1.1                  |            | mV (max)<br>mV (max)<br>mV (max)<br>mV (max) |  |  |

|                     |                                                     | HP mode, $C_{BYPASS} = 2.2\mu F$                                                                                                                            |                                         |            |                                              |  |  |

| $T_WU$              | Wake Up Time                                        | Normal turn on time                                                                                                                                         | 31                                      |            | ms                                           |  |  |

|                     |                                                     | Fast turn on time                                                                                                                                           | 16                                      |            | ms                                           |  |  |

|                     |                                                     | Minimum Gain Setting (mono input),<br>Mode 3                                                                                                                | -86                                     |            | dB (max)<br>dB (min)                         |  |  |

| ٨                   | Values Control                                      | Maximum Gain Setting (mono input),<br>Mode 3                                                                                                                | 12                                      | 13<br>11.5 | dB (max)<br>dB (min)                         |  |  |

| A <sub>VOL</sub>    | Volume Control                                      | Minimum Gain Setting (stereo input),<br>Mode 6                                                                                                              | -80                                     |            | dB (max)<br>dB (min)                         |  |  |

|                     |                                                     | Maximum Gain Setting (stereo input),<br>Mode 6                                                                                                              | 18                                      | 19<br>17.5 | dB (max)<br>dB (min)                         |  |  |

|                     | Volume Control Step Error                           |                                                                                                                                                             | ±0.2                                    |            | dB                                           |  |  |

Product Folder Links: LM49251

<sup>(1)</sup> Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified

<sup>(2)</sup> The Electrical Characteristics tables list specified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

<sup>(3)</sup> Loudspeaker  $R_L$  is a resistive load in series with two inductors to simulate an actual speaker load. For  $R_L = 8\Omega$ , the load is  $15\mu H + 8\Omega$ +15 $\mu$ H. For R<sub>L</sub> = 4 $\Omega$ , the load is 15 $\mu$ H + 4 $\Omega$  + 15 $\mu$ H.

Typical values represent most likely parametric norms at  $T_A = +25$ °C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

Datasheet min/max specification limits are ensured by test or statistical analysis. (5)

# Electrical Characteristics(1)(2)(3) (continued)

The following specifications apply for  $A_V = 0 dB$ ,  $R_L = 15 \mu H + 8 \Omega + 15 \mu H$  (Loudspeaker),  $R_L = 32 \Omega$  (Headphone),  $C_{SET} = 100 nF$ , f = 1 kHz, ALC off, unless otherwise specified. Limits apply for  $T_A = 25 ^{\circ}C$ .

|                      | Danis and an                        | Total Constitution of                                                             | LM49251            |                      | Units                                                                             |  |  |

|----------------------|-------------------------------------|-----------------------------------------------------------------------------------|--------------------|----------------------|-----------------------------------------------------------------------------------|--|--|

|                      | Parameter                           | Test Conditions                                                                   | Typ <sup>(4)</sup> | Limit <sup>(5)</sup> | (Limits)                                                                          |  |  |

|                      |                                     | LS Mode                                                                           |                    |                      |                                                                                   |  |  |

|                      |                                     | Gain 0                                                                            | 12                 | 11.5<br>12.5         | dB (min)<br>dB (max)                                                              |  |  |

|                      |                                     | Gain 1                                                                            | 18                 | 17.5<br>19           | dB (min)<br>dB (max)                                                              |  |  |

|                      |                                     | HP Mode                                                                           |                    |                      |                                                                                   |  |  |

|                      |                                     | Gain 0                                                                            | 0                  | -0.5<br>0.5          | dB (min)<br>dB (max)                                                              |  |  |

| $A_V$                | Gain                                | Gain 1                                                                            | -1.7               |                      | dB                                                                                |  |  |

|                      |                                     | Gain 2                                                                            | -3                 |                      | dB                                                                                |  |  |

|                      |                                     | Gain 3                                                                            | -6                 |                      | dB                                                                                |  |  |

|                      |                                     | Gain 4                                                                            | -9                 |                      | dB                                                                                |  |  |

|                      |                                     | Gain 5                                                                            | -12                |                      | dB                                                                                |  |  |

|                      |                                     | Gain 6                                                                            | -15                |                      | dB                                                                                |  |  |

|                      |                                     | Gain 7                                                                            | -18                | -18.5<br>-17.5       | dB (min)<br>dB (max)                                                              |  |  |

| A <sub>V(MUTE)</sub> | Mute Attenuation                    | LS Output<br>HP Output                                                            | -93<br>-98         |                      | dB<br>dB                                                                          |  |  |

|                      |                                     | MONO, R <sub>IN</sub> , L <sub>IN</sub> inputs                                    |                    |                      |                                                                                   |  |  |

| R <sub>IN</sub>      | Input Resistance                    | Maximum Gain Setting                                                              | 13                 | 9.5<br>15.5          | $\begin{array}{c} k\Omega \text{ min)} \\ k\Omega \text{ (max)} \end{array}$      |  |  |

|                      |                                     | Minimum Gain Setting                                                              | 110                | 97<br>122            | $\begin{array}{c} k\Omega \; (\text{min}) \\ k\Omega \; (\text{max}) \end{array}$ |  |  |

|                      | Output Power                        | Mode 3, $A_V = 18dB$ , $R_L = 8\Omega$                                            |                    |                      |                                                                                   |  |  |

|                      |                                     | $LSV_{DD} = 3.3V$                                                                 | 570                |                      | mW                                                                                |  |  |

|                      |                                     | $LSV_{DD} = 3.6V$                                                                 | 680                | 600                  | mW (min)                                                                          |  |  |

| Po                   |                                     | $LSV_{DD} = 4.2V$                                                                 | 955                |                      | mW                                                                                |  |  |

| O                    | Output i owei                       | $LSV_{DD} = 5.0V$                                                                 | 1370               |                      | mW                                                                                |  |  |

|                      |                                     | Mode 6                                                                            |                    |                      |                                                                                   |  |  |

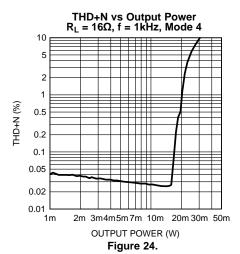

|                      |                                     | $R_L = 16\Omega$                                                                  | 20                 |                      | mW                                                                                |  |  |

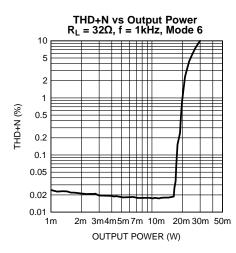

|                      |                                     | $R_L=32\Omega$                                                                    | 20                 | 16                   | mW (min)                                                                          |  |  |

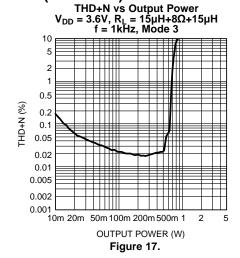

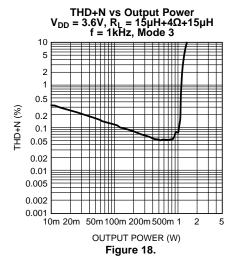

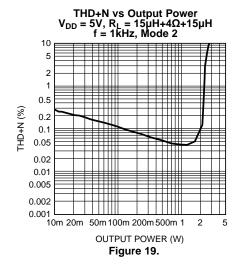

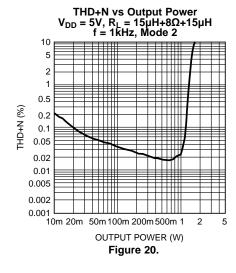

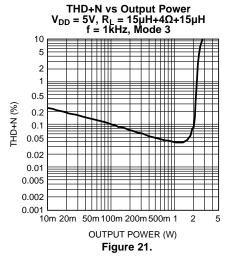

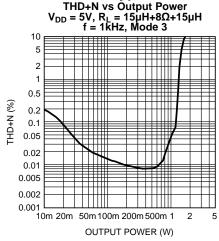

| THD+N                | Total Harmonic Distortion + Noise   | f = 1kHz, Mode 3<br>Mono Input, P <sub>O</sub> = 250mW                            | 0.02               |                      | %                                                                                 |  |  |

| וו+∪ווו              | 1 Stal Hallionic Distortion + NOISE | f = 1kHz, Mode 6<br>Stereo Input, P <sub>O</sub> = 12mW                           | 0.02               |                      | %                                                                                 |  |  |

|                      |                                     | $f = 217Hz$ , $V_{RIPPLE} = 200mV_{P-P}$ , Inputs AC GND, $C_B = 2.2\mu F$        |                    |                      |                                                                                   |  |  |

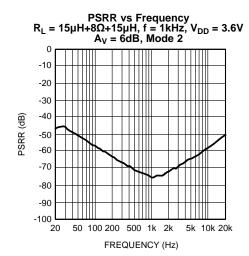

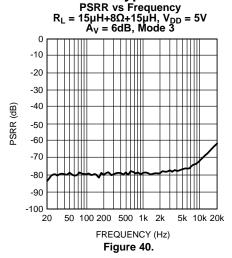

|                      |                                     | Mode 3, mono input, $A_V = 6dB$                                                   | 77                 |                      | dB                                                                                |  |  |

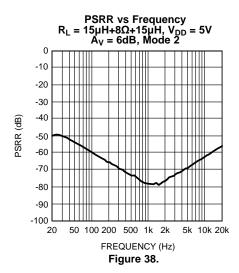

|                      |                                     | Mode 2, stereo input, $A_V = 6dB$                                                 | 65                 |                      | dB                                                                                |  |  |

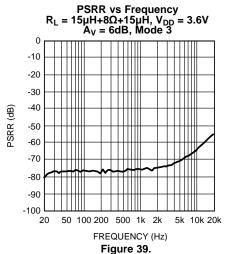

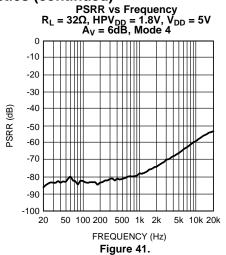

| PSRR                 | Power Supply Rejection Ratio        | Mode 4, ripple on V <sub>DD</sub> , mono input                                    | 93                 |                      | dB                                                                                |  |  |

|                      |                                     | Mode 4, ripple on $HPV_{DD}$ , mono input                                         | 83                 |                      | dB                                                                                |  |  |

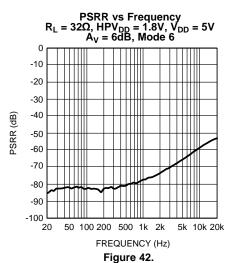

|                      |                                     | Mode 6, ripple on V <sub>DD</sub> , stereo input                                  | 80                 |                      | dB                                                                                |  |  |

|                      |                                     | Mode 6, ripple on HPV <sub>DD</sub> , stereo input                                | 80                 |                      | dB                                                                                |  |  |

|                      |                                     | V <sub>RIPPLE</sub> = 1V <sub>P-P</sub> , f <sub>RIPPLE</sub> = 217Hz, mono input |                    |                      |                                                                                   |  |  |

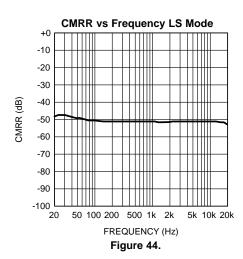

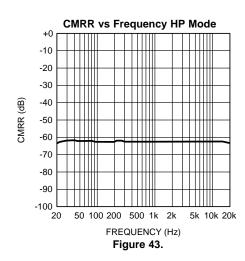

| CMRR                 | Common Mode Rejection Ratio         | Mode 3<br>Mode 4                                                                  | 52<br>63           |                      | dB<br>dB                                                                          |  |  |

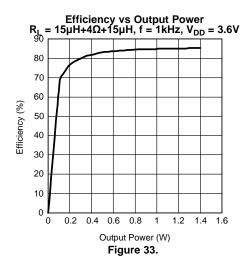

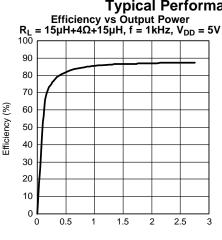

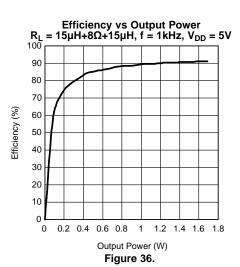

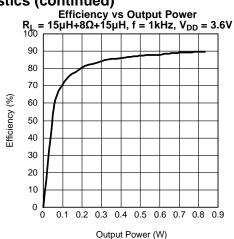

| η                    | Efficiency                          | LS Mode, P <sub>O</sub> = 680mW                                                   | 90                 |                      | %                                                                                 |  |  |

| X <sub>TALK</sub>    | Crosstalk                           | P <sub>O</sub> = 12mW, f = 1kHz, Mode 6                                           | 84                 |                      | dB                                                                                |  |  |

# Electrical Characteristics(1)(2)(3) (continued)

The following specifications apply for  $A_V = 0 dB$ ,  $R_L = 15 \mu H + 8 \Omega + 15 \mu H$  (Loudspeaker),  $R_L = 32 \Omega$  (Headphone),  $C_{SET} = 100 nF$ , f = 1 kHz, ALC off, unless otherwise specified. Limits apply for  $T_A = 25 ^{\circ}C$ .

| Parameter                    |                       | Total Constitutions                                                                                       | LM4                                    | LM49251              |                                                                                                  |  |  |

|------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|--------------------------------------------------------------------------------------------------|--|--|

|                              |                       | Test Conditions                                                                                           | Typ <sup>(4)</sup>                     | Limit <sup>(5)</sup> | (Limits)                                                                                         |  |  |

| ∈ <sub>OS</sub> Output Noise |                       | A-weighted, Inputs AC GND Mode 3, mono input Mode 2, stereo input Mode 4, mono input Mode 6, stereo input | 44<br>45<br>8<br>10.2                  | 45<br>8              | μV<br>μV<br>μV<br>μV                                                                             |  |  |

| SNR                          | Signal-To-Noise-Ratio | Mode 3, P <sub>O</sub> = 680mW<br>Mode 6, P <sub>O</sub> = 20mW                                           | 94<br>98                               |                      | dB<br>dB                                                                                         |  |  |

| t <sub>A</sub>               | Attack Time           | Step 1, Mode 1                                                                                            | 0.75                                   |                      | ms                                                                                               |  |  |

| t <sub>R</sub>               | Release Time          | Step 1, Mode 1                                                                                            | 1                                      |                      | s                                                                                                |  |  |

|                              |                       | Mode 3, THD+N ≤ 1% <sup>(6)</sup>                                                                         |                                        |                      |                                                                                                  |  |  |

| $V_{LIMIT}$                  | Output Voltage Limit  | Voltage Level Step 1 001 Step 2 010 Step 3 011 Step 4 100 Step 5 101 Step 6 110                           | 3.9<br>4.7<br>5.4<br>6.2<br>7.0<br>7.8 |                      | V <sub>P-P</sub><br>V <sub>P-P</sub><br>V <sub>P-P</sub><br>V <sub>P-P</sub><br>V <sub>P-P</sub> |  |  |

<sup>(6)</sup> The LM49251 ALC limits the output power to which ever is lower, the supply voltage or output power limit.

# I<sup>2</sup>C Interface Characteristics $V_{DD} = 5V$ , $2.2V \le I^{2}CV_{DD} \le 5.5V^{(1)(2)}$

The following specifications apply for  $A_V = 0$ dB,  $R_L = 8\Omega$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                 | Danamatan.           | Total Constitions | LM                 | LM49251                             |          |  |

|-----------------|----------------------|-------------------|--------------------|-------------------------------------|----------|--|

|                 | Parameter            | Test Conditions   | Typ <sup>(3)</sup> | Limit <sup>(4)</sup>                | (Limits) |  |

| t <sub>1</sub>  | SCL Period           |                   |                    | 2.5                                 | μs (min) |  |

| t <sub>2</sub>  | SDA Set-up Time      |                   |                    | 100                                 | ns (min) |  |

| t <sub>3</sub>  | SDA Stable Time      |                   |                    | 0                                   | ns (min) |  |

| t <sub>4</sub>  | Start Condition Time |                   |                    | 100                                 | ns (min) |  |

| t <sub>5</sub>  | Stop Condition Time  |                   |                    | 100                                 | ns (min) |  |

| t <sub>6</sub>  | SDA Hold time        |                   |                    | 100                                 | ns (min) |  |

| V <sub>IH</sub> | Input High Voltage   |                   |                    | 0.7*I <sup>2</sup> CV <sub>DD</sub> | V (min)  |  |

| V <sub>IL</sub> | Input Low Voltage    |                   |                    | 0.3*I <sup>2</sup> CV <sub>DD</sub> | V (max)  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified

- (2) The Electrical Characteristics tables list specified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (3) Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (4) Datasheet min/max specification limits are ensured by test or statistical analysis.

# I<sup>2</sup>C Interface Characteristics $V_{DD} = 5V$ , $1.8V \le I^2CV_{DD} \le 2.2V^{(1)(2)}$

The following specifications apply for  $A_V = 0$ dB,  $R_L = 8\Omega$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C.

|                 | B                          | Tank Oam distance | LM                 | LM49251                             |          |  |

|-----------------|----------------------------|-------------------|--------------------|-------------------------------------|----------|--|

|                 | Parameter                  | Test Conditions   | Typ <sup>(3)</sup> | Limit <sup>(4)</sup>                | (Limits) |  |

| t <sub>1</sub>  | SCL Period                 |                   |                    | 2.5                                 | μs (min) |  |

| t <sub>2</sub>  | SDA Set-up Time            |                   |                    | 250                                 | ns (min) |  |

| t <sub>3</sub>  | SDA Stable Time            |                   |                    | 0                                   | ns (min) |  |

| t <sub>4</sub>  | Start Condition Time       |                   |                    | 250                                 | ns (min) |  |

| t <sub>5</sub>  | Stop Condition Time        |                   |                    | 250                                 | ns (min) |  |

| t <sub>6</sub>  | SDA Hold Time              |                   |                    | 250                                 | ns (min) |  |

| V <sub>IH</sub> | Digital Input High Voltage |                   |                    | 0.7*I <sup>2</sup> CV <sub>DD</sub> | V (min)  |  |

| $V_{IL}$        | Digital Input Low Voltage  |                   |                    | 0.3*I <sup>2</sup> CV <sub>DD</sub> | V (max)  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified

- (2) The Electrical Characteristics tables list specified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

- (3) Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not ensured.

- (4) Datasheet min/max specification limits are ensured by test or statistical analysis.

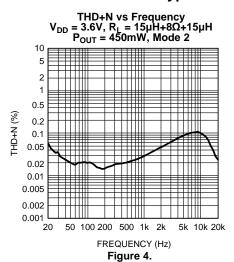

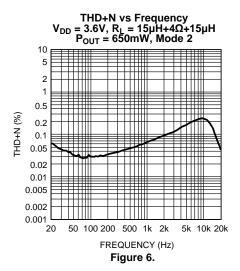

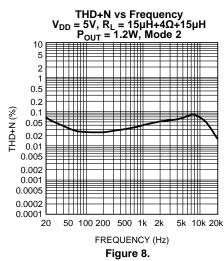

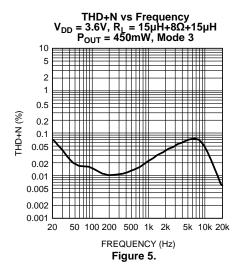

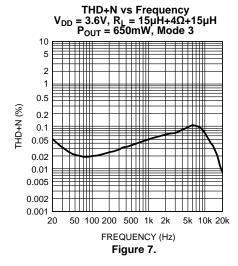

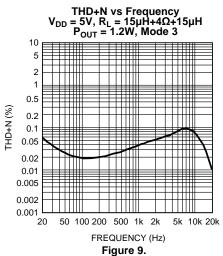

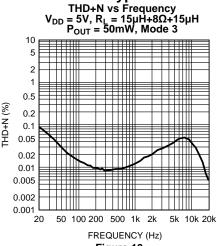

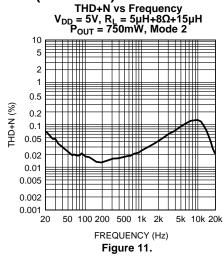

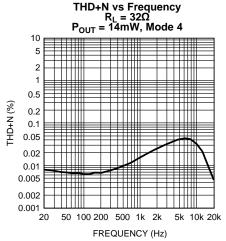

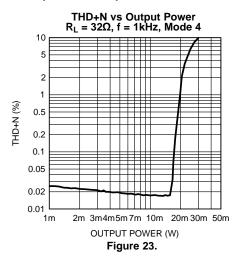

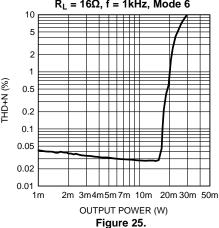

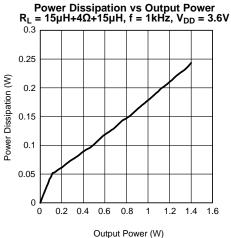

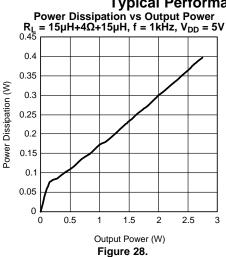

### **Typical Performance Characteristics**

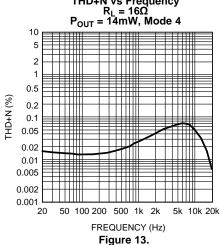

THD+N vs Frequency

Figure 12.

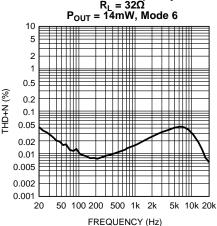

THD+N vs Frequency

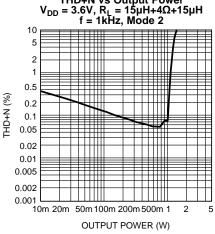

THD+N vs Output Power  $V_{DD} = 3.6V$ ,  $R_L = 15\mu H + 4\Omega + 15\mu H$

Figure 14.

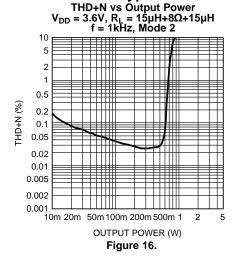

Figure 15.

Figure 22.

Figure 26.

Product Folder Links: LM49251

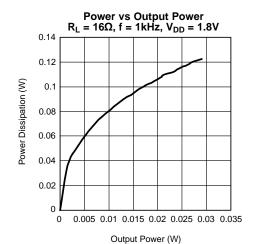

THD+N vs Output Power  $R_L = 16\Omega$ , f = 1kHz, Mode 6

Figure 27.

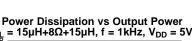

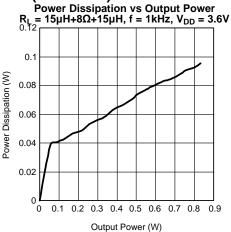

Output Power (W) Figure 30.

Figure 29.

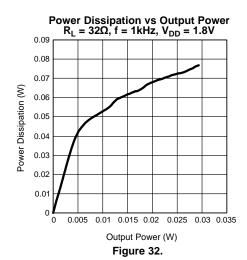

Figure 31.

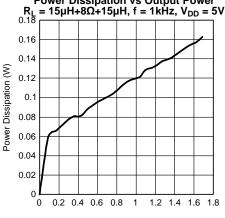

Output Power (W) **Figure 34.**

Figure 35.

Figure 37.

3.....

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

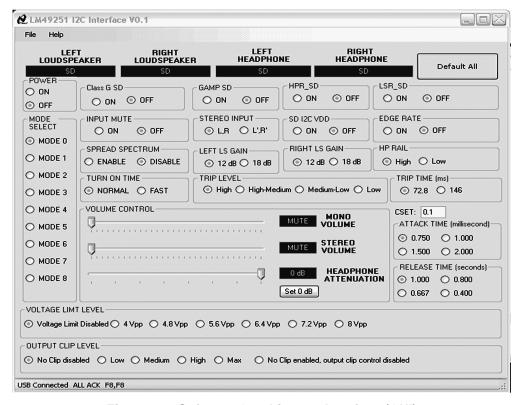

### **System Control**

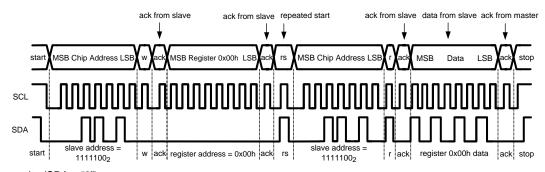

# I<sup>2</sup>C SIGNALS

In I<sup>2</sup>C mode the LM49251 pin SCL is used for the I<sup>2</sup>C clock SCL and the pin SDA is used for the I<sup>2</sup>C data signal SDA. Both of these signals need a pull-up resistor according to I<sup>2</sup>C specification. The 7-bits I<sup>2</sup>C slave address for LM49251 is 1111100.

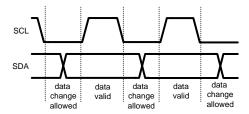

#### I<sup>2</sup>C DATA VALIDITY

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

Figure 48. I<sup>2</sup>C Signals: Data Validity

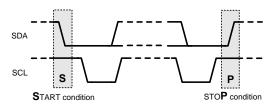

# I<sup>2</sup>C START AND STOP CONDITIONS

START and STOP bits classify the beginning and the end of the I<sup>2</sup>C session. START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP bits. The I<sup>2</sup>C bus is considered to be busy after START condition and free after STOP condition. During data transmission, I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 49. I<sup>2</sup>C Start and Stop Conditions

#### TRANSFERRING DATA

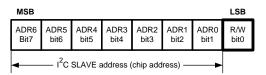

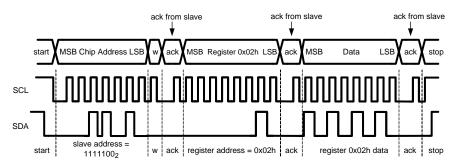

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) being transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received. After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eight bit which is a data direction bit (R/W). The LM49251 address is 11111000. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data will be written. The third byte contains data to write to the selected register.

Figure 50. I<sup>2</sup>C Chip Address

Figure 51. Example I<sup>2</sup>C Write Cycle

When a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in the Read Cycle waveform.

w = write (SDA = "0")

r = read (SDA = "1")

ack = acknowledge (SDA pulled down by slave)

rs = repeated start

Figure 52. Example I<sup>2</sup>C Read Cycle

#### **Table 2. Device Address**

|                | В7 | В6 | B5 | B4 | В3 | B2 | B1 | В0 |

|----------------|----|----|----|----|----|----|----|----|

| Device Address | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

# Table 3. I<sup>2</sup>C Control Registers

| Register Name               | В7 | В6 | B5 | B4      | В3      | B2       | B1          | В0      |

|-----------------------------|----|----|----|---------|---------|----------|-------------|---------|

| SHUTDOWN<br>CONTROL         | 0  | 0  | 0  | 1       | GAMP_ON | HPR_SD   | Class G _SD | SD      |

| MODE<br>CONTROL             | 0  | 0  | 1  | HP_ST   | HP_M    | SPK_ L+R | SPK_ST      | SPK_M   |

| POWER<br>LIMITER<br>CONTROL | 0  | 1  | 0  | ATK1    | ATK0    | PLEV2    | PLEV1       | PLEV0   |

| NO CLIP<br>CONTROL          | 0  | 1  | 1  | RLT1    | RLT0    | OCP2     | OCP1        | ОСР0    |

| GAIN<br>CONTROL             | 1  | 0  | 0  | LSGAINL | LSGAINR | HPGAIN2  | HPGAIN1     | HPGAIN0 |

| MONO<br>VOLUME<br>CONTROL   | 1  | 0  | 1  | MG4     | MG3     | MG2      | MG1         | MG0     |

| STEREO<br>VOLUME<br>CONTROL | 1  | 1  | 0  | SG4     | SG3     | SG2      | SG1         | SG0     |

# Table 3. I<sup>2</sup>C Control Registers (continued)

| Register Name      | В7 | В6 | B5 | B4 | В3 | B2                                 | B1       | В0              |

|--------------------|----|----|----|----|----|------------------------------------|----------|-----------------|

| CLASS D<br>CONTROL | 1  | 1  | 1  | 0  | 0  | 0                                  | ER_CNTRL | SS_EN           |

| LS CONTROL         | 1  | 1  | 1  | 0  | 1  | 0                                  | ST_SEL   | LSR_SD          |

| CLASS G<br>CONTROL | 1  | 1  | 1  | 1  | 0  | 0                                  | TLEV1    | TLEV2           |

| OTHER<br>CONTROL   | 1  | 1  | 1  | 1  | 1  | I <sup>2</sup> CV <sub>DD</sub> SD | RAIL_SW  | TURN_ON<br>TIME |

# **Table 4. Shutdown Control**

| BIT | NAME       | VALUE                 | DESCRIPTION                                                     |

|-----|------------|-----------------------|-----------------------------------------------------------------|

|     |            | This disables the ga  | in amplifiers that are not in use to minimize I <sub>DD</sub> . |

| В3  | GAMP_ON    | 0                     | Normal Operation                                                |

|     |            | 1                     | Unused gain amplifiers disabled                                 |

|     |            | This disables the rig | ht headphone output.                                            |

| B2  | HPR_SD     | 0                     | Normal operation                                                |

|     |            | 1                     | Right headphone amplifier disabled                              |

|     |            | This disables the Cla | ass G.                                                          |

| B1  | Class G_SD | 0                     | Class G enabled                                                 |

|     |            | 1                     | Class G disabled                                                |

|     |            | LM49251 Shutdown      |                                                                 |

| В0  | SD         | 0                     | LM49251 Disabled                                                |

|     |            | 1                     | LM49251 Enabled                                                 |

# **Table 5. Output Mode Selection**

| HP (ST) | HP (M) | SPK<br>(L+R) | SPK<br>(ST) | SPK<br>(M) | SPK(L)        | SPK(R)        | HP(L)  | HP(R)   | Datasheet |

|---------|--------|--------------|-------------|------------|---------------|---------------|--------|---------|-----------|

| 0       | 0      | 0            | 0           | 0          | SD            | SD            | SD     | SD      | Mode 0    |

| 0       | 0      | 1            | 1           | 0          | GST X (L + R) | GST X (L + R) | SD     | SD      | Mode 1    |

| 0       | 0      | 0            | 1           | 0          | GST X L       | GST X R       | SD     | SD      | Mode 2    |

| 0       | 0      | 0            | 0           | 1          | GM X M        | GM X M        | SD     | SD      | Mode 3    |

| 0       | 1      | 0            | 0           | 0          | SD            | SD            | GM X M | GM X M  | Mode 4    |

| 0       | 1      | 0            | 0           | 1          | GM X M        | GM X M        | GM X M | GM X M  | Mode 5    |

| 1       | 0      | 0            | 0           | 0          | SD            | SD            | GSTX L | GST X R | Mode 6    |

| 1       | 0      | 1            | 1           | 0          | GST X (L + R) | GST X (L + R) | GSTX L | GST X R | Mode 7    |

| 1       | 0      | 0            | 1           | 0          | GST X L       | GST X R       | GSTX L | GST X R | Mode 8    |

# **Table 6. Voltage Limit Control Register**

| BIT   | NAME         |    | VALUE |    | DESCRIPTION                                                     |                               |

|-------|--------------|----|-------|----|-----------------------------------------------------------------|-------------------------------|

|       |              | B4 |       | В3 | Sets Attack Time based on C <sub>SET</sub> and R <sub>SET</sub> |                               |

|       |              | 0  |       | 0  | t <sub>ATK</sub>                                                |                               |

| B4:B3 | ATK1<br>ATK2 | 0  |       | 1  | 1.3 x t <sub>ATK</sub>                                          |                               |

|       | ,,,,,,       | 1  |       | 0  | 2 x t <sub>ATK</sub>                                            |                               |

|       |              | 1  |       | 1  | 2.7 x t <sub>ATK</sub>                                          |                               |

|       |              |    | B2    | B1 | В0                                                              | Sets output power limit level |

|       |              | 0  | 0     | 0  | Voltage Limit disabled                                          |                               |

|       |              | 0  | 0     | 1  | $V_{TH(VLIM)} = 3.9V_{P-P}$                                     |                               |

|       | PLEV2        | 0  | 1     | 0  | $V_{TH(VLIM)}) = 4.7V_{P-P}$                                    |                               |

| B2:B0 | PLEV1        | 0  | 1     | 1  | $V_{TH(VLIM)} = 5.4V_{P-P}$                                     |                               |

|       | PLEV0        | 1  | 0     | 0  | $V_{TH(VLIM)} = 6.2V_{P-P}$                                     |                               |

|       |              | 1  | 0     | 1  | $V_{TH(VLIM)} = 7.0V_{P-P}$                                     |                               |

|       |              | 1  | 1     | 0  | $V_{TH(VLIM)} = 7.8V_{P-P}$                                     |                               |

|       |              | 1  | 1     | 1  | Voltage Limit disabled                                          |                               |

# **Table 7. No Clip Control Register**

|       |      |    | опр   |    | 9                                                                    |

|-------|------|----|-------|----|----------------------------------------------------------------------|

| BIT   | NAME |    | VALUE |    | DESCRIPTION                                                          |

|       |      | B2 | B1    | В0 | This sets the output clip limit level                                |

|       |      | 0  | 0     | 0  | NO_CLIP = disabled, OUTPUT_CLIP = disabled                           |

|       |      | 0  | 0     | 1  | Test Mode                                                            |

|       | OCP2 | 0  | 1     | 0  | NO_CLIP = enabled, OUTPUT_CLIP = disabled                            |

| B2:B0 | OCP1 | 0  | 1     | 1  | low                                                                  |

|       | OCP0 | 1  | 0     | 0  | medium                                                               |

|       |      | 1  | 0     | 1  | medium high                                                          |

|       |      | 1  | 1     | 0  | high                                                                 |

|       |      | 1  | 1     | 1  | maximum                                                              |

|       |      | B1 | В0    |    | This sets the release time of the automatic limiter control circuit. |

|       | RLT1 | 0  | 0     |    | 1s                                                                   |

| B4:B3 | RTL0 | 0  | 1     |    | 0.8s                                                                 |

|       |      | 1  | 0     |    | 0.65s                                                                |

|       |      | 1  | 1     |    | 0.4s                                                                 |

|       |      |    |       |    |                                                                      |

# **Table 8. Gain Control Register**

| BIT | NAME        | VALUE | DESCRIPTION           |                      |

|-----|-------------|-------|-----------------------|----------------------|

| B4  | D4 LCCAINII | 0     |                       | 6dB Loudspeaker gain |

| D4  | LSGAINL     | 1     | 12dB Loudspeaker gain |                      |

| D2  | DO LOCAIND  | 0     | 6dB Loudspeaker gain  |                      |

| B3  | LSGAINR     | 1     | 12dB Loudspeaker gain |                      |

# **Table 8. Gain Control Register (continued)**

| BIT   | NAME         | VALUE |    |    | DESCRIPTION    |

|-------|--------------|-------|----|----|----------------|

|       |              | B2    | B1 | В0 | Headphone Gain |

|       |              | 0     | 0  | 0  | 0dB            |

|       |              | 0     | 0  | 1  | -1.5db         |

|       | HPGAIN2 (B2) | 0     | 1  | 0  | -3dB           |

| B2:B0 | HPGAIN1 (B1) | 0     | 1  | 1  | -6dB           |

|       | HPGAIN0 (B0) | 1     | 0  | 0  | -9dB           |

|       |              | 1     | 0  | 1  | -12dB          |

|       |              | 1     | 1  | 0  | -15dB          |

|       |              | 1     | 1  | 1  | -18dB          |

# **General Amplifier Function**

#### **Table 9. Volume Control Table**

|             |     | iable | . J. Volullie | Control lab | IE  |           |

|-------------|-----|-------|---------------|-------------|-----|-----------|

| VOLUME STEP | _G4 | _G3   | _G2           | _G1         | _G0 | GAIN (dB) |

| 1           | 0   | 0     | 0             | 0           | 0   | -80       |

| 2           | 0   | 0     | 0             | 0           | 1   | -46.5     |

| 3           | 0   | 0     | 0             | 1           | 0   | -40.5     |

| 4           | 0   | 0     | 0             | 1           | 1   | -34.5     |

| 5           | 0   | 0     | 1             | 0           | 0   | -30       |

| 6           | 0   | 0     | 1             | 0           | 1   | -27       |

| 7           | 0   | 0     | 1             | 1           | 0   | -24       |

| 8           | 0   | 0     | 1             | 1           | 1   | -21       |

| 9           | 0   | 1     | 0             | 0           | 0   | -18       |

| 10          | 0   | 1     | 0             | 0           | 1   | -15       |

| 11          | 0   | 1     | 0             | 1           | 0   | -13.5     |

| 12          | 0   | 1     | 0             | 1           | 1   | -12       |

| 13          | 0   | 1     | 1             | 0           | 0   | -10.5     |

| 14          | 0   | 1     | 1             | 0           | 1   | -9        |

| 15          | 0   | 1     | 1             | 1           | 0   | -7.5      |

| 16          | 0   | 1     | 1             | 1           | 1   | -6        |

| 17          | 1   | 0     | 0             | 0           | 0   | -4.5      |

| 18          | 1   | 0     | 0             | 0           | 1   | -3        |

| 19          | 1   | 0     | 0             | 1           | 0   | 1.5       |

| 20          | 1   | 0     | 0             | 1           | 1   | 0         |

| 21          | 1   | 0     | 1             | 0           | 0   | 1.5       |

| 22          | 1   | 0     | 1             | 0           | 1   | 3         |

| 23          | 1   | 0     | 1             | 1           | 0   | 4.5       |

| 24          | 1   | 0     | 1             | 1           | 1   | 6         |

| 25          | 1   | 1     | 0             | 0           | 0   | 7.5       |

| 26          | 1   | 1     | 0             | 0           | 1   | 9         |

| 27          | 1   | 1     | 0             | 1           | 0   | 10.5      |

| 28          | 1   | 1     | 0             | 1           | 1   | 12        |

| 29          | 1   | 1     | 1             | 0           | 0   | X         |

| 30          | 1   | 1     | 1             | 0           | 1   | X         |

| 31          | 1   | 1     | 1             | 1           | 0   | X         |

| 32          | 1   | 1     | 1             | 1           | 1   | Х         |

#### Table 10. Class D Control

| BIT | NAME     | VALUE                | DESCRIPTION                |

|-----|----------|----------------------|----------------------------|

|     |          | This enables edge ra | te control.                |

| B1  | ER_CNTRL | 0                    | Edge Rate Control Disabled |

|     |          | 1                    | Edge Rate Control Enabled  |

|     |          | This enables Spread  | Spectrum.                  |

| В0  | SS_EN    | 0                    | Spread Spectrum Disabled   |

|     |          | 1                    | Spread Spectrum Enabled    |

# Table 11. Loudspeaker (LS) Control

| BIT | NAME   | VALUE                                            | DESCRIPTION               |  |  |  |

|-----|--------|--------------------------------------------------|---------------------------|--|--|--|

|     |        | This allows selection between two Stereo Inputs. |                           |  |  |  |

| B1  | ST_SEL | 0                                                | LIN1/RIN1                 |  |  |  |

|     |        | 1                                                | LIN2/RIN2                 |  |  |  |

|     |        |                                                  | Loudspeaker.              |  |  |  |

| В0  | LSR_SD | 0                                                | Left Loudspeaker enabled  |  |  |  |

|     |        | 1                                                | Left Loudspeaker disabled |  |  |  |

# **Table 12. Class G Control**

| BIT   | NAME                 | VALUE |    | DESCRIPTION               |

|-------|----------------------|-------|----|---------------------------|

|       | B1:B0 TLEV1<br>TLEV0 | B1    | В0 | This sets the Trip Level. |

|       |                      | 0     | 0  | High (default)            |

| B1:B0 |                      | 0     | 1  | High-Medium               |

|       |                      | 1     | 0  | Low-Medium                |

|       |                      | 1     | 1  | Low                       |

# **Table 13. Other Control**

| BIT | NAME         | VALUE                         | DESCRIPTION                                               |  |  |

|-----|--------------|-------------------------------|-----------------------------------------------------------|--|--|

|     |              |                               | This switches between two HP voltage rails <sup>(1)</sup> |  |  |

| B1  | RAIL_SW      | 0                             | High Rail                                                 |  |  |

|     |              | 1                             | Low Rail                                                  |  |  |

|     |              | This allows fast turn on time |                                                           |  |  |

| В0  | TURN_ON_TIME | 0                             | Normal Turn-On Time                                       |  |  |

|     |              | 1                             | Fast Turn-On Time                                         |  |  |

(1) This option is only available when the Class G is disabled.

#### APPLICATION INFORMATION

#### **DIFFERENTIAL AMPLIFIER EXPLANATION**

The LM49251 features a differential input stage, which offers improved noise rejection compared to a single-ended input amplifier. Because a differential input amplifier amplifies the difference between the two input signals, any component common to both signals is cancelled. An additional benefit of the differential input structure is the possible elimination of the DC input blocking capacitors. Since the DC component is common to both inputs, and thus cancelled by the amplifier, the LM49251 can be used without input coupling capacitors when configured with a differential input signal.

#### **INPUT MIXER/MULTIPLEXER**

The LM49251 includes a comprehensive mixer multiplexer controlled through the I<sup>2</sup>C interface. The mixer/multiplexer allows any input combination to appear on any output of LM49251. Table 5 (MODE CONTROL) shows how the input signals are routed together for each possible input selection.

### SHUTDOWN FUNCTION

The LM49251 features the following shutdown controls: Bit B4 (GAMP\_SD) of the SHUTDOWN CONTROL register controls the gain amplifiers. When GAMP\_SD = 1, it disables the gain amplifiers that are not in use. For example, in Modes 1, 4 and 5, the Mono inputs are in use, so the Left and Right input gain amplifiers are disabled, causing the  $I_{DD}$  to be minimized. Bit B0 (PWR\_ON) of the SHUTDOWN CONTROL register is the global shutdown control for the entire device. Set PWR\_ON = 0 for normal operation. PWR\_ON = 1 overrides any other shutdown control bit.

#### **CLASS D AMPLIFIER**

The LM49251 features a mono class D audio power amplifier with a filterless modulation scheme that reduces external component count, conserving board space and reducing system cost. With no signal applied, the outputs (LSOUT+ and LSOUT-) switch between VDD and GND with 50% duty cycle, in phase, causing the two outputs to cancel. This cancellation results in no net voltage across the speaker, thus there is no current to the load in the idle state.

With an input signal applied, the duty cycle (pulse width) of the class D output changes. For increasing output voltage, the duty cycle of LSOUT+ increases, while the duty cycle of LSOUT- decreases. For decreasing output voltages, the converse occurs. The difference between the two pulse widths yields the differential output voltage.

#### ENHANCED EMISSIONS SUPPRESSION (E<sup>2</sup>S)

The LM49251 class D amplifier features TI's patent-pending E<sup>2</sup>S system that reduces EMI, while maintaining high quality audio reproduction and efficiency. The E<sup>2</sup>S system features selectable spread spectrum and advanced edge rate control (ERC). The LM49251 class D ERC greatly reduces the high frequency components of the output square waves by controlling the output rise and fall times, slowing the transitions to reduces RF emissions, while maximizing THD+N and efficiency performance.

#### **FIXED FREQUENCY**

The LM49251 class D amplifier features two modulation schemes, a fixed frequency mode and a spread spectrum mode. Select the fixed frequency mode by setting bit B0 (SS\_EN) of the SS Control register to 0. In fixed frequency mode, the loudspeaker outputs switch at a constant 300kHz. The output spectrum consists of the 300kHz fundamental and its associated harmonics.

#### SPREAD SPECTRUM

The selectable spread spectrum mode minimizes the need for output filters, ferrite beads or chokes. In spread spectrum mode, the switching frequency varies randomly by 30% about a 300kHz center frequency, reducing the wideband spectral content, improving EMI emission radiated by the speaker and associated cables and traces. Where a fixed frequency class D exhibits large amounts of spectral energy at multiples of the switching frequency, the spread spectrum architecture spreads that energy over a larger bandwidth. The cycle-to-cycle variation of the switching period does not affect the audio reproduction, efficiency, or PSRR. Set bit B0 (SS\_EN) of the SS Control register to 1 to enable spread spectrum mode.

#### GROUND REFERENCED HEADPHONE AMPLIFIER

The LM49251 features a low noise inverting charge pump that generates an internal negative supply voltage. This allows the headphone outputs to be biased about GND instead of a nominal DC voltage, like traditional headphone amplifiers. Because there is no DC component, the large DC blocking capacitors (typically 220µF) at the headphone outputs are not necessary. The coupling capacitors are replaced by two small ceramic charge pump capacitors, saving board space and cost. Eliminating the output coupling capacitors also improves low frequency response. In traditional headphone amplifiers, the headphone impedance and the output capacitor form a high-pass filter that not only blocks the DC component of the output, but also attenuates low frequencies, impacting the bass response. Because the LM49251 does not require the output coupling capacitors, the low frequency response of the device is not degraded by external components. In addition to eliminating the output coupling capacitors, the ground referenced output nearly doubles the available dynamic range of the LM49251 headphone amplifiers when compared to a traditional headphone amplifier operating from the same supply voltage.

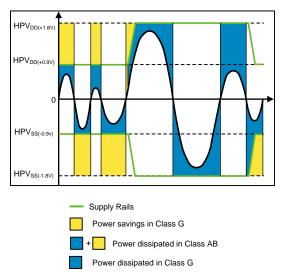

#### **CLASS G OPERATION**

The LM49251 features a ground referenced class G headphone amplifier for increased efficiency and decreased power dissipation. This particular architecture creates a ground-referenced output with dynamic supply rails for optimum efficiency. Music and voice signals have a high peak-to-mean ratio with the majority of the signal content at low levels, class G amplifiers take advantage of this behavior. Class G amplifiers have multiple voltage supplies to decrease power dissipation. The LM49251 has two discrete supply rails: ±0.9V and ±1.8V. The device switches from ±0.9V to ±1.8V when the output signal reaches the selectable threshold level to switch to the higher voltage rails. When the output falls below the required voltage for a set period of time, it will switch back to the lower rail until the next time the threshold is reached. The threshold level has 4 selectable levels that can be set through the Class G Control I<sup>2</sup>C control register <B1:B2>. With this topology power dissipation is reduced for typical music or voice sources. Figure 53 below shows how a music output may look.

Figure 53. Class G Operation

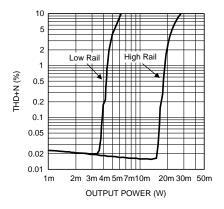

# Disabling the Class G

The Class G feature can be disabled via  $I^2C$  Shutdown Control Register B1. When the Class G is disabled the headphone supply rails are selectable. In the Other Control register B1 = 0 sets the headphone supply rails at  $\pm 1.8V$  (high) and B1 = 1 sets the supply to  $\pm 0.9V$  (low). Figure 54 below shows a curve of THD+N vs Output Power for the two supply rails.

Figure 54. Class G Disabled (Low/High Supply Rails)

# **AUTOMATIC LIMITER CONTROL (ALC)**

When enabled, the ALC continuously monitors and adjusts the gain of the loudspeaker amplifier signal path if necessary. The ALC serves two functions: voltage limiter/speaker protection and output clip prevention (No-Clip) with three clip controls levels. The voltage limiter/speaker protection prevents an output overload condition by maintaining the loudspeaker output signal below a preset amplitude (See VOLTAGE LIMITER section). The No Clip feature monitors the output signal and maintains audio quality by preventing the loudspeaker output from exceeding the amplifier's headroom (see NO CLIP/OUTPUT CLIP CONTROL section). The voltage limiter thresholds, clip control levels, attack and release times are configured through the I<sup>2</sup>C interface.

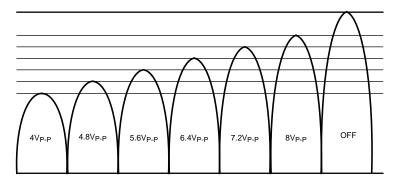

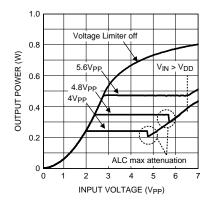

#### **VOLTAGE LIMITER**

The voltage limiter function of the ALC monitors and prevents the audio signal from exceeding the voltage limit threshold. The voltage limit threshold ( $V_{TH(VLIM)}$ ) is set by bits B2:B0 in the "Voltage Limit Threshold Register" (see Table 6). Although the ALC reduces the gain of the speaker path to maintain the audio signal below the voltage limit threshold, it is still possible to overdrive the speaker output in which case loudspeaker output will exceed the voltage limit threshold and cause clipping on the output, and speaker damage is possible. Please see the ALC HEADROOM section for further details.

Figure 55. Voltage Limit Output Level

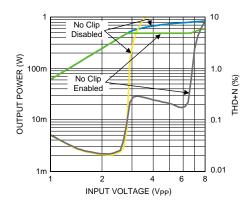

#### NO CLIP/OUTPUT CLIP CONTROL

The LM49251 No Clip circuitry detects when the loudspeaker output is near clipping and reduces the signal gain to prevent output clipping and preserve audio quality (Figure 54). Although the ALC reduces the gain of the speaker path to prevent output clipping, it is still possible to overdrive the speaker output. Please see the ALC HEADROOM section for further details.

Figure 56. No Clip Function

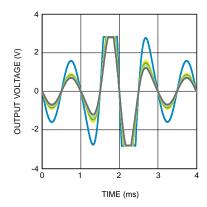

The LM49251 also features an output clip control that allows a certain amount of clipping at the output in order to increase the loudspeaker output power. The clip level is set by B2:B0 in the No Clip Control Register (see Table 7). The clip control works by allowing the output to enter clipping before the ALC turns on and maintains the output level. The clip control has three levels: low, medium, and high. The low and max clip level control settings give the lowest distortion and highest distortion respectively on the output (see Figure 57). The actual output level of the device will depend upon the supply voltage, and the output power will depend upon the load impedance.

Figure 57. Clip Control Levels  $V_{DD}=3.3V,\,V_{IN}=8V_{PP}$  Shaped Burst, 1kHz Blue = No Clip Disabled, Gray = Low, Light Green = Medium Green = High, Yellow = Max

### **ALC HEADROOM**

When either voltage limiter or no clip is enabled, it is still possible to drive LM49251 into clipping by over driving the input volume stage of the signal path beyond its output dynamic range. In this case, clipping occurs at the input volume stage, and although ALC is active, the gain reduction will have no effect on the output clipping. The maximum input that can safely pass through the input volume stage can be calculated by following formula:

$$V_{IN} \le \frac{V_{DD}}{Av \text{ (volume gain)}}$$

(1)

So in the case of 0 dB volume gain, audio input has to be less than  $V_{DD}$  for both voltage limiter or No clip settings.

When voltage limiter is enabled, ALC can reach its max attenuation for lower voltage limit levels as shown in Figure 58. Typically, after the ALC started working, with 6 dB of audio input change ALC is well within its regulation. Voltage limiter Input headroom can be increased by switching to the LS\_GAIN to 18dB in the Gain Control Register (see Table 8).

Figure 58. Voltage Limiter Function  $V_{DD} = 3.3V$ ,  $R_L = 15\mu H + 8\Omega + 15\mu H$   $f_{IN} = 1kHz$ ,  $LS\_GAIN = 0$

Figure 59. No Clip Function  $V_{DD}=3.3V,\,R_L=15\mu H+8\Omega+15\mu H$   $f_{IN}=1kHz,\,LS\_GAIN=0$  Blue, Green = Output Power vs Input Voltage Gray, Yellow = THD+N vs Input Voltage

When No Clip is enabled, class D speaker output reduces when it's about to enter clipping region and power stay constant as long as  $V_{IN}$  is less than  $V_{DD}$  for 0 dB volume gain (see Figure 58). For example, in the case of  $V_{DD}$  = 3.3V, there is a 6 dB of headroom for the change in input. Please see the ALC typical performance curves for additional plots relating to different supply voltages and LS\_GAIN settings for specific application parameters.

#### **ATTACK TIME**

Attack time ( $t_{ATK}$ ) is the time it takes for the gain to be reduced by 6dB (LS\_GAIN=0) once the audio signal exceeds the ALC threshold. Fast attack times allow the ALC to react quickly and prevent transients such as symbol crashes from being distorted. However, fast attack times can lead to volume pumping, where the gain reduction and release becomes noticeable, as the ALC cycles quickly. Slower attack times cause the ALC to ignore the fast transients, and instead act upon longer, louder passages. Selecting an attack time that is too slow can lead to increased distortion in the case of the No Clip function, and possible output overload conditions in the case of the Voltage limiter. The attack time is set by a combination of the value of  $C_{SET}$  and the attack time coefficient as given by Equation 2:

$$t_{ATK} = 20k\Omega C_{SET} / \alpha_{ATK}(s)$$

(2)

Where  $\alpha_{ATK}$  is the attack time coefficient (Table 14) set by bits B4:B3 in the Voltage Limit Control Register (see Table 6). The attack time coefficient allows the user to set a nominal attack time. The internal  $20k\Omega$  resistor is subject to temperature change, and it has tolerance between -11% to +20%.

**Table 14. Attack Time Coefficient**

| B4 | В3 | α <sub>ATK</sub> |

|----|----|------------------|

| 0  | 0  | 2.667            |

| 0  | 1  | 2                |

| 1  | 0  | 1.333            |

| 1  | 1  | 1                |

#### **RELEASE TIME**

Release time ( $t_{RL}$ ) is the time it takes for the gain to return from 6dB (LS\_GAIN=0) to its normal level once the audio signal returns below the ALC threshold. A fast release time allows the ALC to react quickly to transients, preserving the original dynamics of the audio source. However, similar to a fast attack time, a fast release time contributes to volume pumping. A slow release time reduces the effect of volume pumping. The release time is set by a combination of the value of  $C_{SET}$  and release time coefficient as given by Equation 3:

$$t_{RL} = 20M\Omega C_{SET} / \alpha_{RL}(s)$$

(3)

where  $\alpha_{RL}$  is the release time coefficient (Table 15) set by bits B4:B3 in the No Clip Control Register. The release time coefficient allows the user to set a nominal release time. The internal  $20M\Omega$  is subject to temperature change, and it has tolerance between -11% to +20%.

#### **Table 15. Release Time Coefficient**

| B4 | В3 | $\alpha_{RL}$ |

|----|----|---------------|

| 0  | 0  | 2             |

| 0  | 1  | 2.5           |

| 1  | 0  | 3             |

| 1  | 1  | 5             |

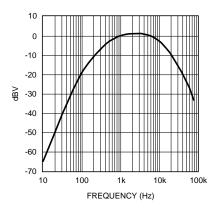

#### **A-WEIGHTED FILTER**

The human ear is sensitive for acoustic signals within a frequency range from about 20Hz to 20kHz. Within this range the sensitivity of the human ear is not equal for each frequency. To approach the hearing response, weighting filters are introduced. One of those filters is the A-weighted filter.

The A-weighted filter is used in signal to noise measurements, where the wanted audio signal is compared to device noise and distortion.

The use of this filter improves the correlation of the measured values to the way these ratios are perceived by the human ear.

Figure 60. A-Weighted Filter

### PROPER SELECTION OF EXTERNAL COMPONENTS

# ALC Timing (C<sub>SET</sub>) Capacitor Selection

The recommended range value of  $C_{SET}$  is between .01 $\mu$ F to 1 $\mu$ F. Lowering the value below .01 $\mu$ F can increase the attack time but LM49251 ALC ability to regulate its output can be disrupted and approaches the hard limiter circuit. This in turn increases the THD+N and audio quality will be severely affected.

### **Charge Pump Capacitor Selection**

Use low ESR ceramic capacitors (less than  $100m\Omega$ ) for optimum performance.

#### Charge Pump Flying Capacitor (C<sub>1</sub>)

The flying capacitor ( $C_1$ ), see Figure 2, affects the load regulation and output impedance of the charge pump. A C1 value that is too low results in a loss of current drive, leading to a loss of amplifier headroom. A higher valued C1 improves load regulation and lowers charge pump output impedance to an extent. Above  $2.2\mu F$ , the RDS<sub>(ON)</sub> of the charge pump switches and the ESR of C1 and CPV<sub>SS</sub> dominate the output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

#### Charge Pump Hold Capacitor (CPV<sub>SS</sub>)

The value and ESR of the hold capacitor ( $CPV_{SS}$ ) directly affects the ripple on  $CPV_{SS}$  (see Figure 2). Increasing the value of  $CPV_{SS}$  reduces output ripple. Decreasing the ESR of  $CPV_{SS}$  reduces both output ripple and charge pump output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

Copyright © 2011–2013, Texas Instruments Incorporated

#### **Input Capacitor Selection**