# L6386AD

## High voltage high and low-side driver

Datasheet - production data

### Features

- High voltage rail up to 600 V

- dV/dt immunity ± 50 V/nsec in full temperature range

- Driver current capability

- 400 mA source

- 650 mA sink

- Switching times 50/30 nsec rise/fall with 1 nF load

- CMOS/TTL Schmitt trigger inputs with hysteresis and pull-down

- Undervoltage lockout on lower and upper driving section

- Integrated bootstrap diode

- Outputs in phase with inputs

## Applications

- Home appliances

- Induction heating

- Industrial applications and drives

- Motor drivers

- SR motors,

- DC, AC, PMDC and PMAC motors

- Asymmetrical half-bridge topologies

- HVAC

- Lighting applications

- Factory automation

- Power supply systems

#### March 2016

DocID14914 Rev 3

This is information on a product in full production.

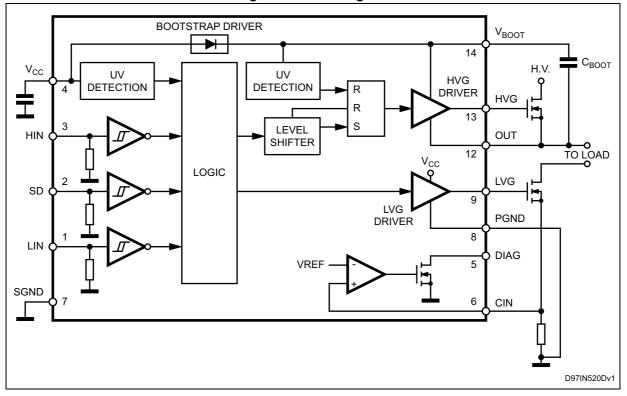

# Description

The L6386AD is a high voltage gate driver, manufactured with the BCD ™ "offline" technology, and able to drive simultaneously one high and one low-side power MOSFET or IGBT device. The high-side (floating) section is able to work with voltage rail up to 600 V. Both device outputs can independently sink and source 650 mA and 400 mA respectively and can be simultaneously driven high in order to drive asymmetrical half-bridge configurations.

The L6386AD device provides two input pins, two output pins and an enable pin (SD), and guarantees the outputs switch in phase with inputs. The logic inputs are CMOS/TTL compatible to ease the interfacing with controlling devices.

The L6386AD integrates a comparator (inverting input internally referenced to 0.5 V) that can be used to protect the device against fault events, like overcurrent. The DIAG output is a diagnostic pin, driven by the comparator, and used to signal a fault event occurrence to the controlling device.

The bootstrap diode is integrated in the driver allowing a more compact and reliable solution.

The L6386AD device features the UVLO protection on both supply voltages (V<sub>CC</sub> and V<sub>BOOT</sub>) ensuring greater protection against voltage drops on the supply lines.

The device is available in a SO-14 package, in tube, and tape and reel packaging.

1/17 www.st.com

# Contents

| 1 | Bloc | k diagram                           |

|---|------|-------------------------------------|

| 2 | Elec | trical data                         |

|   | 2.1  | Absolute maximum ratings 4          |

|   | 2.2  | Thermal data                        |

|   | 2.3  | Recommended operating conditions4   |

|   | 2.4  | Pin connection                      |

| 3 | Elec | trical characteristics6             |

|   | 3.1  | AC operation                        |

|   | 3.2  | DC operation                        |

|   | 3.3  | Timing diagram                      |

| 4 | Boot | strap driver                        |

|   | CBOC | <sub>T</sub> selection and charging |

| 5 | Турі | cal characteristic                  |

| 6 | Pack | age information                     |

|   | 6.1  | SO-14 package information 14        |

| 7 | Orde | er codes                            |

| 8 | Revi | sion history                        |

# 1 Block diagram

# 2 Electrical data

### 2.1 Absolute maximum ratings

| Symbol                | Parameter                                        | Value                        | Unit |

|-----------------------|--------------------------------------------------|------------------------------|------|

| V <sub>OUT</sub>      | Output voltage                                   | -3 to V <sub>BOOT</sub> - 18 | V    |

| V <sub>CC</sub>       | Supply voltage                                   | - 0.3 to +18                 | V    |

| V <sub>BOOT</sub>     | Floating supply voltage                          | -1 to 618                    | V    |

| V <sub>hvg</sub>      | High-side gate output voltage                    | - 1 to V <sub>BOOT</sub>     | V    |

| V <sub>Ivg</sub>      | Low-side gate output voltage                     | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Vi                    | Logic input voltage                              | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>DIAG</sub>     | Open drain forced voltage                        | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>CIN</sub>      | Comparator input voltage                         | -0.3 to 10 V                 | V    |

| dV <sub>out</sub> /dt | Allowed output slew rate                         | 50                           | V/ns |

| P <sub>tot</sub>      | Total power dissipation (T <sub>J</sub> = 85 °C) | 750                          | mW   |

| Тj                    | Junction temperature                             | 150                          | °C   |

| T <sub>stg</sub>      | Storage temperature                              | -50 to 150                   | °C   |

### Table 1. Absolute maximum ratings

## 2.2 Thermal data

### Table 2. Thermal data

|   | Symbol       | Parameter                              | SO-14 | Unit |

|---|--------------|----------------------------------------|-------|------|

| Ī | $R_{th(JA)}$ | Thermal resistance junction to ambient | 165   | °C/W |

### 2.3 Recommended operating conditions

### Table 3. Recommended operating conditions

| Symbol                         | Pin | Parameter                                              | Test condition | Min. | Тур. | Max. | Unit |

|--------------------------------|-----|--------------------------------------------------------|----------------|------|------|------|------|

| V <sub>OUT</sub>               | 12  | Output voltage                                         |                | (1)  |      | 580  | V    |

| V <sub>BS</sub> <sup>(2)</sup> | 14  | Floating supply voltage                                |                | (1)  |      | 17   | V    |

| f <sub>sw</sub>                |     | Switching frequency HVG, LVG load C <sub>L</sub> = 1 r |                |      |      | 400  | kHz  |

| V <sub>CC</sub>                | 4   | Supply voltage                                         |                |      |      | 17   | V    |

| TJ                             |     | Junction temperature                                   |                | -45  |      | 125  | °C   |

1. If the condition  $V_{BOOT}$  -  $V_{OUT}$  < 18 V is guaranteed,  $V_{OUT}$  can range from -3 to 580 V.

2.  $V_{BS} = V_{BOOT} - V_{OUT}$ .

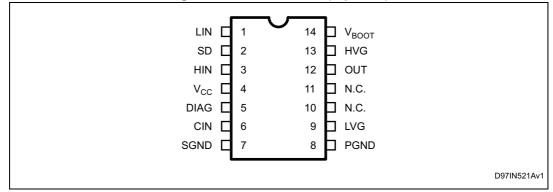

### 2.4 Pin connection

12

13

14

OUT

HVG<sup>(1)</sup>

VBOOT

Ρ

0

Ρ

Figure 2. Pin connection (top view)

|        |                    |      | •                            |  |  |  |

|--------|--------------------|------|------------------------------|--|--|--|

| No.    | Pin                | Туре | Function                     |  |  |  |

| 1      | LIN                | I    | Low-side driver logic input  |  |  |  |

| 2      | SD <sup>(1)</sup>  | I    | Shutdown logic input         |  |  |  |

| 3      | HIN                | I    | ligh-side driver logic input |  |  |  |

| 4      | V <sub>CC</sub>    | Р    | Low voltage supply           |  |  |  |

| 5      | DIAG               | 0    | Open drain diagnostic output |  |  |  |

| 6      | CIN                | I    | Comparator input             |  |  |  |

| 7      | SGND               | Р    | Ground                       |  |  |  |

| 8      | PGND               | Р    | Power ground                 |  |  |  |

| 9      | LVG <sup>(1)</sup> | 0    | Low-side driver output       |  |  |  |

| 10, 11 | N.C.               |      | Not connected                |  |  |  |

#### Table 4. Pin description

The circuit guarantees 0.3 V maximum on the pin (at I<sub>sink</sub> = 10 mA), with V<sub>CC</sub> > 3 V. This allows to omit the "bleeder" resistor connected between the gate and the source of the external MOSFET normally used to hold the pin low; the gate driver assures low impedance also in SD condition.

High-side driver floating driver

Bootstrapped supply voltage

High-side driver output

# **3** Electrical characteristics

### 3.1 AC operation

| Symbol           | Pin            | Parameter                                         | Test condition           | Min. | Тур. | Max. | Unit |

|------------------|----------------|---------------------------------------------------|--------------------------|------|------|------|------|

| t <sub>on</sub>  | 1, 3 vs. 9, 13 | High/low-side driver turn-on<br>propagation delay |                          |      | 110  | 150  | ns   |

| t <sub>off</sub> | 1, 3 vs. 9, 13 | High/low-side driver turn-off propagation delay   | V <sub>OUT</sub> = 0 V   |      | 110  | 150  | ns   |

| t <sub>sd</sub>  | 2 vs. 9,13     | Shutdown to high/low-side<br>propagation delay    |                          |      | 105  | 150  |      |

| t <sub>r</sub>   | 9, 13          | Rise time                                         | C <sub>L</sub> = 1000 pF |      | 50   |      | ns   |

| t <sub>f</sub>   | 9, 10          | Fall time                                         | C <sub>L</sub> = 1000 pF |      | 30   |      | ns   |

### Table 5. AC operation electrical characteristics (V<sub>CC</sub> = 15 V; T<sub>J</sub> = 25 °C)

## 3.2 DC operation

Table 6. DC operation electrical characteristics (V<sub>CC</sub> = 15 V;  $T_J$  = 25 °C)

| Symbol              | Pin                     | Parameter                                     | Test condition                                   | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------|-----------------------------------------------|--------------------------------------------------|------|------|------|------|

| Low sup             | oly volt                | age section                                   |                                                  |      |      |      |      |

| V <sub>CCth1</sub>  |                         | V <sub>CC</sub> UV turn-on threshold          |                                                  | 9.1  | 9.6  | 10.1 | V    |

| V <sub>CCth2</sub>  |                         | V <sub>CC</sub> UV turn-off threshold         |                                                  | 7.9  | 8.3  | 8.8  | V    |

| V <sub>CChys</sub>  | 4                       | V <sub>CC</sub> UV hysteresis                 |                                                  |      | 1.3  |      | V    |

| I <sub>QCCU</sub>   |                         | Undervoltage quiescent supply current         | $V_{CC} \le 9 V$                                 |      | 200  |      | μA   |

| I <sub>QCC</sub>    |                         | Quiescent current                             | V <sub>CC</sub> = 15 V                           |      | 250  | 320  | μA   |

| Bootstra            | oped su                 | upply section                                 |                                                  |      |      |      |      |

| V <sub>BTh1</sub>   |                         | V <sub>BOOT</sub> UV turn-on threshold        |                                                  | 8.5  | 9.5  | 10.5 | V    |

| V <sub>BTh2</sub>   |                         | V <sub>BOOT</sub> UV turn-off threshold       |                                                  | 7.2  | 8.2  | 9.2  | V    |

| V <sub>BHys</sub>   | 14                      | V <sub>BOOT</sub> UV hysteresis               |                                                  |      | 1.3  |      | V    |

| I <sub>QBOOT</sub>  |                         | V <sub>BOOT</sub> quiescent current           | HVG ON                                           |      |      | 200  | μA   |

| I <sub>LK</sub>     |                         | High voltage leakage current                  | $V_{hvg} = V_{OUT} = V_{BOOT} = 600 V$           |      |      | 10   | μA   |

| R <sub>DS(on)</sub> |                         | Bootstrap driver on-resistance <sup>(1)</sup> | $V_{CC} \ge 12.5 \text{ V} \text{ V}_{IN}$ = 0 V |      | 125  |      | Ω    |

| Driving b           | Driving buffers section |                                               |                                                  |      |      |      |      |

| I <sub>so</sub>     | 9, 13                   | High/low-side source short-circuit current    | $V_{IN} = V_{ih} (t_p < 10 \ \mu s)$             | 300  | 400  |      | mA   |

| I <sub>si</sub>     | 9, 13                   | High/low-side sink short-circuit current      | $V_{IN} = V_{il} (t_p < 10 \ \mu s)$             | 500  | 650  |      | mA   |

| Symbol           | Pin     | Parameter                           | Parameter Test condition  |      | Тур  | Max  | Unit |

|------------------|---------|-------------------------------------|---------------------------|------|------|------|------|

| Logic inp        | outs    |                                     |                           |      |      |      |      |

| V <sub>il</sub>  |         | Low level logic voltage             |                           |      |      | 1.5  | V    |

| V <sub>ih</sub>  | 1, 2, 3 | High level logic voltage            |                           | 3.6  |      |      | V    |

| l <sub>ih</sub>  | 1, 2, 3 | High level logic input current      | V <sub>IN</sub> = 15 V    |      | 50   | 70   | μA   |

| l <sub>il</sub>  |         | Low level logic input current       | V <sub>IN</sub> = 0 V     |      |      | 1    | μA   |

| Sense co         | omparat | or                                  |                           |      |      |      |      |

| V <sub>io</sub>  |         | Input offset voltage                |                           | -10  |      | 10   | mV   |

| I <sub>io</sub>  | 6       | Input bias current                  | $V_{CIN} \geq 0.5$        |      | 0.2  |      | μA   |

| V <sub>ol</sub>  | 2       | Open drain low level output voltage | l <sub>od</sub> = -2.5 mA |      |      | 0.8  | V    |

| V <sub>ref</sub> |         | Comparator reference voltage        |                           | 0.46 | 0.50 | 0.54 | V    |

Table 6. DC operation electrical characteristics (continued) ( $V_{CC}$  = 15 V;  $T_{J}$  = 25 °C)

1.  $R_{DS(on)}$  is tested in the following way:

$$\mathsf{R}_{\mathsf{DSON}} = \frac{(\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOT1}}) - (\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOT2}})}{\mathsf{I}_1(\mathsf{V}_{\mathsf{CC}}, \mathsf{V}_{\mathsf{BOOT1}}) - \mathsf{I}_2(\mathsf{V}_{\mathsf{CC}}, \mathsf{V}_{\mathsf{BOOT2}})}$$

where  $I_1$  is the pin 14 current when  $V_{BOOT} = V_{BOOT1}$ ,  $I_2$  when  $V_{BOOT} = V_{BOOT2}$ .

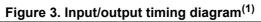

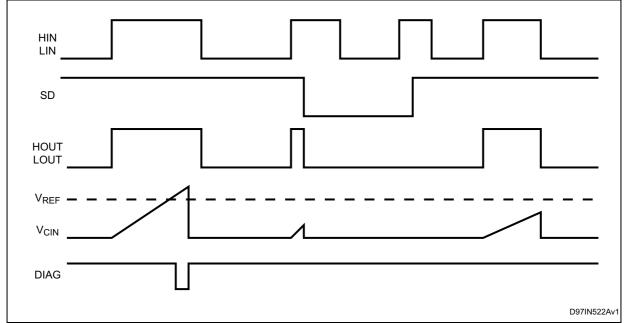

# 3.3 Timing diagram

1. If the SD is set low, each output remains in the shutdown condition also after the rising edge of the SD, until the first rising edge of the input signal occurs.

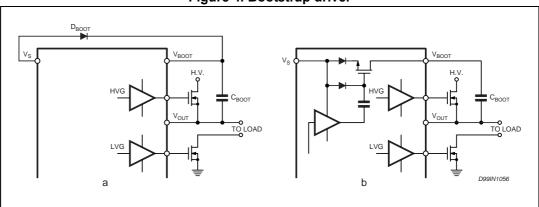

### 4 Bootstrap driver

A bootstrap circuitry is needed to supply the high voltage section. This function is normally accomplished by a high voltage fast recovery diode (*Figure 4* a). In the L6386AD device a patented integrated structure replaces the external diode. It is realized by a high voltage DMOS, driven synchronously with the low-side driver (LVG), with a diode in series, as shown in *Figure 4* b. An internal charge pump (*Figure 4* b) provides the DMOS driving voltage. The diode connected in series to the DMOS has been added to avoid undesirable turn-on.

### C<sub>BOOT</sub> selection and charging

To choose the proper  $C_{BOOT}$  value, the external MOSFET can be seen as an equivalent capacitor. This capacitor  $C_{EXT}$  is related to the MOSFET total gate charge:

#### **Equation 1**

$$C_{EXT} = \frac{Q_{gate}}{V_{gate}}$$

The ratio between the capacitors  $C_{EXT}$  and  $C_{BOOT}$  is proportional to the cyclical voltage loss. It has to be:

E.g.: if  $Q_{gate}$  is 30 nC and  $V_{gate}$  is 10 V,  $C_{EXT}$  is 3 nF. With  $C_{BOOT}$  = 100 nF the drop would be 300 mV.

If HVG has to be supplied for a long time, the  $C_{BOOT}$  selection has to take into account also the leakage losses.

E.g.: HVG steady state consumption is lower than 200  $\mu A$ , so if HVG T<sub>ON</sub> is 5 ms, C<sub>BOOT</sub> has to supply 1  $\mu C$  to C<sub>EXT</sub>. This charge on a 1  $\mu F$  capacitor means a voltage drop of 1 V.

The internal bootstrap driver gives great advantages: the external fast recovery diode can be avoided (it usually has a great leakage current).

This structure can work only if  $V_{OUT}$  is close to GND (or lower) and in the meanwhile the LVG is on. The charging time ( $T_{charge}$ ) of the  $C_{BOOT}$  is the time in which both conditions are fulfilled and it has to be long enough to charge the capacitor.

The bootstrap driver introduces a voltage drop due to the DMOS  $R_{DS(on)}$  (typical value: 125  $\Omega$ ). At low frequency this drop can be neglected. Anyway increasing the frequency it must be taken into account.

The following equation is useful to compute the drop on the bootstrap DMOS:

#### **Equation 2**

$$V_{drop} = I_{charge}R_{dson} \rightarrow V_{drop} = \frac{Q_{gate}}{T_{charge}}R_{dson}$$

where *Qgate* is the gate charge of the external power MOSFET,  $R_{dson}$  is the on-resistance of the bootstrap DMOS, and  $T_{charge}$  is the charging time of the bootstrap capacitor.

For example: using a power MOSFET with a total gate charge of 30 nC, the drop on the bootstrap DMOS is about 1 V, if the  $T_{charge}$  is 5 ms. In fact:

### **Equation 3**

$$V_{drop} = \frac{30nC}{5\mu s} \cdot 125\Omega \sim 0.8V$$

$V_{drop}$  has to be taken into account when the voltage drop on  $C_{BOOT}$  is calculated: if this drop is too high, or the circuit topology doesn't allow a sufficient charging time, an external diode can be used.

@ Vcc = 15V\_

100 125

50 75

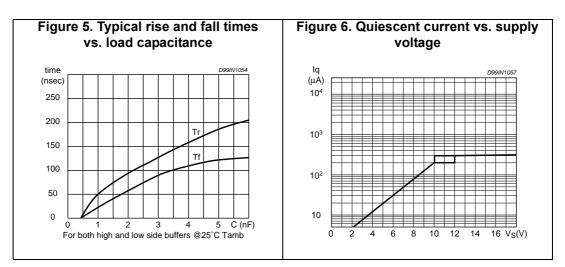

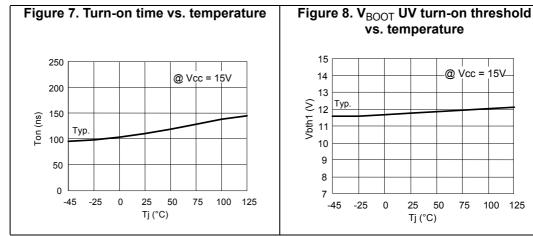

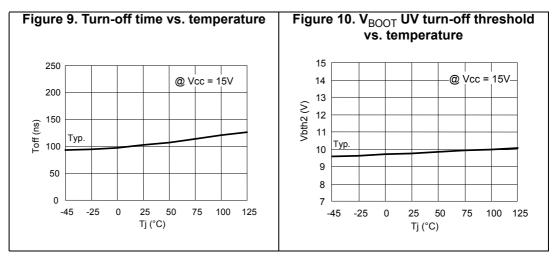

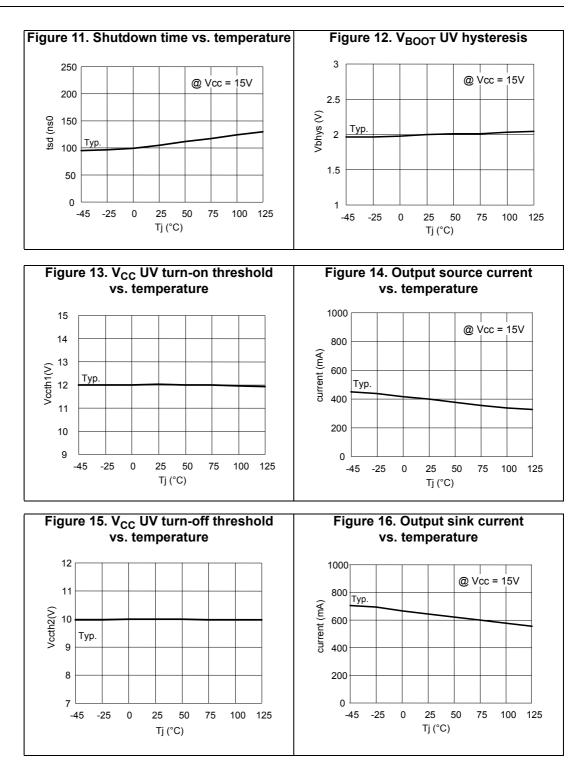

#### **Typical characteristic** 5

DocID14914 Rev 3

DocID14914 Rev 3

Figure 17.  $V_{\text{CC}}$  UV hysteresis vs. temperature

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at:*www.st.com*. ECOPACK is an ST trademark.

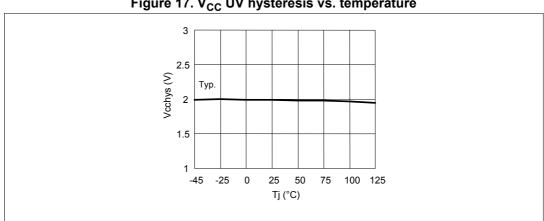

## 6.1 SO-14 package information

### Figure 18. SO-14 package outline

### Table 7. SO-14 package mechanical data

| Symbol           | Dimensions (mm) |      |              | Dimensions (inch) |       |       |

|------------------|-----------------|------|--------------|-------------------|-------|-------|

| Symbol           | Min.            | Тур. | Max.         | Min.              | Тур.  | Max.  |

| А                | 1.35            |      | 1.75         | 0.053             |       | 0.069 |

| A1               | 0.10            |      | 0.30         | 0.004             |       | 0.012 |

| A2               | 1.10            |      | 1.65         | 0.043             |       | 0.065 |

| В                | 0.33            |      | 0.51         | 0.013             |       | 0.020 |

| С                | 0.19            |      | 0.25         | 0.007             |       | 0.01  |

| D <sup>(1)</sup> | 8.55            |      | 8.75         | 0.337             |       | 0.344 |

| E                | 3.80            |      | 4.0          | 0.150             |       | 0.157 |

| е                |                 | 1.27 |              |                   | 0.050 |       |

| Н                | 5.8             |      | 6.20         | 0.228             |       | 0.244 |

| h                | 0.25            |      | 0.50         | 0.01              |       | 0.02  |

| L                | 0.40            |      | 1.27         | 0.016             |       | 0.050 |

| k                |                 |      | 0° (min.), 8 | ° (max.)          |       |       |

| ddd              |                 |      | 0.10         |                   |       | 0.004 |

1. "D" dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per side.

# 7 Order codes

| Table | 8. Device | summary |

|-------|-----------|---------|

|-------|-----------|---------|

| Order codes  | Package | Packaging     |  |

|--------------|---------|---------------|--|

| L6386AD      | SO-14   | Tube          |  |

| L6386AD013TR | SO-14   | Tape and reel |  |

# 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Jul-2008 | 1        | First release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20-Jun-2014 | 2        | Added Section : Applications on page 1.<br>Updated Section : Description on page 1 (replaced by new<br>description).<br>Updated Table 1: Device summary on page 1 (moved "Table 9 Order<br>codes" from page 15 to page 1, renamed title of Table 1).<br>Updated Figure 1: Block diagram on page 3 (moved to page 3,<br>added Section 1: Block diagram on page 3).<br>Updated Section 2.1: Absolute maximum ratings on page 4<br>(removed note below Table 1: Absolute maximum ratings).<br>Updated Table 4: Pin description on page 5 (updated "Type" of<br>several pins).<br>Numbered Equation 1 on page 8, Equation 2 on page 8 and<br>Equation 3 on page 9.<br>Updated Section 6: Package information on page 13 (updated<br>ECOPACK text, updated/added titles, reversed order of Figure 18<br>and Table 7 (numbered Table 7), removed 3D package figure, minor<br>modifications].<br>Minor modifications throughout document. |

| 29-Mar-2016 | 3        | Updated Section : Description on page 1 (updated text and replaced "power MOS" by "power MOSFET").<br>Updated Table 1 on page 4, Table 3 on page 4, Table 4 on page 5 to Table 6 on page 6 (updated "Symbol", "Parameter", "Pin", and "Test condition", and note 1. below Table 6 (replaced " $V_{CBOOTx}$ " by " $V_{BOOTx}$ ").<br>Updated Figure 3 on page 7 (replaced by new figure, added note 1.).<br>Moved Table 8 on page 15 (moved from page 1 to page 15, added title of Section 7: Order codes on page 15).<br>Minor modifications throughout document.                                                                                                                                                                                                                                                                                                                                                                 |

### Table 9. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID14914 Rev 3