# ADA4622-1/ADA4622-2/ADA4622-4

30 V, 8 MHz, Low Bias Current, Single Supply, RRO, Precision Op Amp

#### **FEATURES**

- ▶ Next generation of the AD820/AD822/AD824

- ▶ Wide gain bandwidth product: 8 MHz typical

- ▶ High slew rate

- ▶ 23 V/µs typical (low to high)

- ► -18 V/µs typical (high to low)

- ▶ Low input bias current: ±10 pA maximum at T<sub>A</sub> = 25°C

- ▶ Low offset voltage

- A grade: ±0.8 mV maximum at T<sub>A</sub> = 25°C

- ▶ B grade: ±0.35 mV maximum at T<sub>A</sub> = 25°C

- ► Low offset voltage drift

- ► A grade: ±4 µV/°C maximum

- ▶ B grade: ±2 µV/°C maximum (ADA4622-2 only)

- B grade: ±1 μV/°C maximum (ADA4622-1 only)

- ▶ Input voltage range includes Pin V-

- ▶ Rail-to-rail output

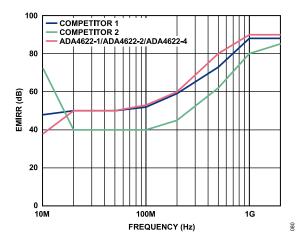

- ► Electromagnetic interference rejection ratio (EMIRR)

- ▶ 90 dB typical at f = 1000 MHz and f = 2400 MHz

- Industry-standard package and pinouts

### **APPLICATIONS**

- ▶ High output impedance sensor interfaces

- ▶ Photodiode sensor interfaces

- ▶ Transimpedance amplifiers

- ADC drivers

- ▶ Precision filters and signal conditioning

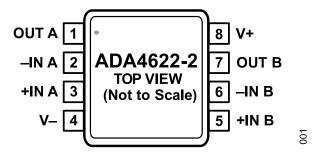

## **PIN CONFIGURATION**

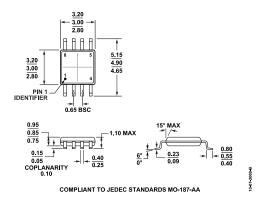

Figure 1. 8-Lead Mini Small Outline Package [MSOP] Pin Configuration (See the Pin Configurations and Function Descriptions Section for Additional Pin Configurations)

#### **GENERAL DESCRIPTION**

The ADA4622-1/ADA4622-2/ADA4622-4 are the next generation of the AD820/AD822/AD824 single-supply, rail-to-rail output (RRO), precision junction field effect transistors (JFET) input op amps. The ADA4622-1/ADA4622-2/ADA4622-4 include many improvements that make them desirable as upgrades without compromising the flexibility and ease of use that makes the AD820/AD822/AD824 useful for a wide variety of applications.

The input voltage range includes the negative supply and the output swings rail-to-rail. Input EMI filters increase the signal robustness in the face of closely located switching noise sources.

The speed, in terms of bandwidth and slew rate, increases along with a strong output drive to improve settling time performance and enables the devices to drive the inputs of modern single-ended, successive approximation register (SAR) analog-to-digital converters (ADCs).

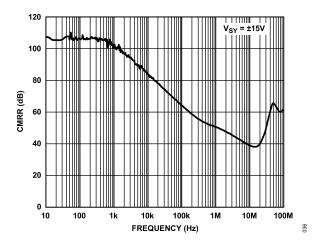

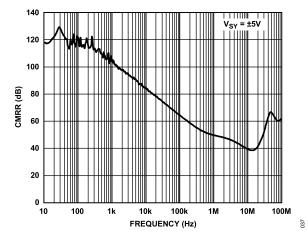

Voltage noise is reduced; although the supply current remains the same as the AD820/AD822/AD824, broadband noise is reduced by 25%, and 1/f is reduced by half. DC precision in the ADA4622-1/ADA4622-2/ADA4622-4 improved from the AD820/AD822/AD824 with half the offset and a maximum thermal drift specification added to the ADA4622-1/ADA4622-2/ADA4622-4. The common-mode rejection ratio (CMRR) is improved from the AD820/AD822/AD824 to make the ADA4622-1/ADA4622-2/ADA4622-4 more suitable when used in noninverting gain and difference amplifier configurations.

The ADA4622-1/ADA4622-2/ADA4622-4 are specified for operation over the extended industrial temperature range of  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , and operate from 5 V to 30 V, with specifications at +5 V,  $\pm5$  V, and  $\pm15$  V. The ADA4622-1 is available in a 5-lead SOT-23 package and an 8-lead LFCSP package. The ADA4622-2 is available in an 8-lead SOIC\_N package, an 8-lead MSOP package, and an 8-lead LFCSP package. The ADA4622-4 is available in a 14-lead SOIC\_N and a 16-lead,  $4\times4$  mm LFCSP.

# **TABLE OF CONTENTS**

| Features1                                              | Input Characteristics            | 26 |

|--------------------------------------------------------|----------------------------------|----|

| Applications1                                          | Output Characteristics           | 27 |

| Pin Configuration1                                     | Shutdown Operation               |    |

| General Description1                                   | Applications Information         |    |

| Specifications3                                        | Recommended Power Solution       |    |

| Electrical Characteristics, V <sub>SY</sub> = ±15 V    | Maximum Power Dissipation        |    |

| Electrical Characteristics, V <sub>SY</sub> = ±5 V 5   | Second-Order Low-Pass Filter     |    |

| Electrical Characteristics, V <sub>SY</sub> = 5 V 7    | Wideband Photodiode Preamplifier |    |

| Absolute Maximum Ratings10                             | Peak Detector                    |    |

| Thermal Resistance10                                   | Multiplexing Inputs              |    |

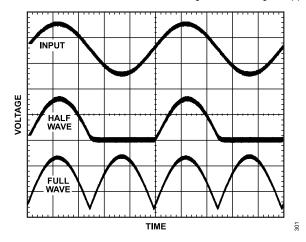

| ESD Caution10                                          | Full Wave Rectifier              |    |

| Pin Configurations and Function Descriptions11         | Outline Dimensions               |    |

| Typical Performance Characteristics14                  | Ordering Guide                   |    |

| Theory Of Operation                                    |                                  |    |

|                                                        |                                  |    |

|                                                        |                                  |    |

| REVISION HISTORY                                       |                                  |    |

| 9/2022—Rev. E to Rev. F                                |                                  |    |

| Changes to Features Section                            |                                  | 1  |

| Changes to Offset Voltage Drift, B Grade Parameter, Ta |                                  |    |

| Changes to Offset Voltage Drift, B Grade Parameter, Ta |                                  |    |

| Changes to Offset Voltage Drift, B Grade Parameter, Ta |                                  |    |

| Changes to Figure 12 to Figure 14                      |                                  |    |

# **ELECTRICAL CHARACTERISTICS, V<sub>SY</sub> = ±15 V**

Supply voltage  $(V_{SY}) = \pm 15 \text{ V}$ , common-mode voltage  $(V_{CM}) = \text{output voltage } (V_{OUT}) = 0 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

Table 1.

| Parameter                   | Symbol               | Test Conditions/Comments                                                  | Min   | Тур              | Max     | Unit  |

|-----------------------------|----------------------|---------------------------------------------------------------------------|-------|------------------|---------|-------|

| INPUT CHARACTERISTICS       |                      |                                                                           |       |                  |         |       |

| Offset Voltage              | Vos                  |                                                                           |       |                  |         |       |

| A Grade                     |                      |                                                                           |       | +0.04            | ±0.8    | mV    |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±2      | mV    |

| B Grade                     |                      | ,                                                                         |       | +0.04            | ±0.35   | mV    |

| ADA4622-1                   |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±1      | mV    |

| ADA4622-2                   |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±0.8    | mV    |

| Offset Voltage Match        |                      | , A                                                                       |       |                  | ±1      | mV    |

| Offset Voltage Drift        | ΔV <sub>OS</sub> /ΔΤ |                                                                           |       |                  |         |       |

| A Grade                     |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±4      | μV/°C |

| B Grade                     |                      | 10 C 11A 1120 C                                                           |       |                  |         | μι, σ |

| ADA4622-1                   |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±1      | μV/°C |

| ADA4622-2                   |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±2      | μV/°C |

| Input Bias Current          | I <sub>B</sub>       |                                                                           |       | +2               | ±10     | pA    |

| •                           |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±1.5    | nA    |

|                             |                      | V <sub>CM</sub> = -15 V                                                   |       | -15              |         | pA    |

| Input Offset Current        | I <sub>os</sub>      | · GWI                                                                     |       |                  | ±10     | pA    |

|                             | 105                  | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | ±0.5    | nA    |

| Input Voltage Range         | IVR                  | 10 0 1 1 <sub>A</sub> 1 1 120 0                                           | -15.2 |                  | +14     | V     |

| Common-Mode Rejection Ratio | CMRR                 |                                                                           | 10.2  |                  | ' 17    | •     |

| A Grade                     | Civilata             | V <sub>CM</sub> = -15 V to +12 V                                          | 84    | 100              |         | dB    |

| A Glade                     |                      | $-40^{\circ}\text{C} < T_{A} < +125^{\circ}\text{C}$                      |       | 100              |         | dВ    |

| B Grade                     |                      | **                                                                        | 81    | 400              |         |       |

| b Glade                     |                      | V <sub>CM</sub> = -15 V to +12 V                                          | 87    | 100              |         | dB    |

| Onen Leen Veltage Cain      |                      | -40°C < T <sub>A</sub> < +125°C                                           | 85    | 400              |         | dB    |

| Open-Loop Voltage Gain      | A <sub>VO</sub>      | $R_L = 10 \text{ k}\Omega, V_{OUT} = -14.5 \text{ V to } +14.5 \text{ V}$ | 117   | 122              |         | dB    |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           | 109   |                  |         | dB    |

|                             |                      | $R_L = 1 k\Omega$ , $V_{OUT} = -14 V to +14 V$                            | 102   | 110              |         | dB    |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           | 93    |                  |         | dB    |

| Input Capacitance           | C <sub>INDM</sub>    | Differential mode                                                         |       | 0.4              |         | pF    |

|                             | C <sub>INCM</sub>    | Common mode                                                               |       | 3.6              |         | pF    |

| Input Resistance            | R <sub>DIFF</sub>    | Differential mode                                                         |       | 10 <sup>13</sup> |         | Ω     |

|                             | R <sub>CM</sub>      | Common mode                                                               |       | 10 <sup>13</sup> |         | Ω     |

| DUTPUT CHARACTERISTICS      |                      |                                                                           |       |                  |         |       |

| Output Voltage              |                      |                                                                           |       |                  |         |       |

| High                        | V <sub>OH</sub>      | I <sub>SOURCE</sub> = 1 mA                                                | 14.95 | 14.97            |         | V     |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           | 14.9  |                  |         | V     |

|                             |                      | I <sub>SOURCE</sub> = 15 mA                                               | 14.3  | 14.5             |         | V     |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           | 14.1  |                  |         | V     |

| Low                         | V <sub>OL</sub>      | I <sub>SINK</sub> = 1 mA                                                  |       | -14.955          | -14.935 | V     |

|                             |                      | -40°C < T <sub>A</sub> < +125°C                                           |       |                  | -14.88  | V     |

|                             |                      | I <sub>SINK</sub> = 15 mA                                                 |       | -14.685          | -14.55  | V     |

analog.com Rev. F | 3 of 36

Table 1.

| Parameter                               | Symbol             | Test Conditions/Comments                                                                 | Min | Тур     | Max        | Unit   |

|-----------------------------------------|--------------------|------------------------------------------------------------------------------------------|-----|---------|------------|--------|

|                                         |                    | -40°C < T <sub>A</sub> < +125°C                                                          |     |         | -14.25     | ٧      |

| Output Current                          | I <sub>OUT</sub>   | V <sub>DROPOUT</sub> < 1 V                                                               |     | 20      |            | mA     |

| Short-Circuit Current                   | I <sub>SC</sub>    | Sourcing                                                                                 |     | 42      |            | mA     |

|                                         |                    | Sinking                                                                                  |     | -51     |            | mA     |

| Closed-Loop Output Impedance            | Z <sub>OUT</sub>   | f = 1 kHz, gain (A <sub>V</sub> ) = 1                                                    |     | 0.1     |            | Ω      |

|                                         | 001                | A <sub>V</sub> = 10                                                                      |     | 0.4     |            | Ω      |

|                                         |                    | A <sub>V</sub> = 100                                                                     |     | 3       |            | Ω      |

| POWER SUPPLY                            |                    |                                                                                          |     |         |            |        |

| Power Supply Rejection Ratio            | PSRR               | V <sub>SY</sub> = ±4 V to ±18 V                                                          | 87  | 103     |            | dB     |

| ,                                       |                    | -40°C < T <sub>A</sub> < +125°C                                                          | 81  |         |            | dB     |

| Supply Current per Amplifier            | I <sub>SY</sub>    |                                                                                          |     |         |            |        |

| ADA4622-1/ADA4622-4                     | 101                |                                                                                          |     | 715     | 750        | μA     |

|                                         |                    | -40°C < T <sub>A</sub> < +125°C                                                          |     | 7.10    | 775        | μA     |

| ADA4622-2                               |                    | 10 0 1 1 <sub>A</sub> 11 120 0                                                           |     | 665     | 700        | μA     |

| ADIATOLL L                              |                    | -40°C < T <sub>A</sub> < +125°C                                                          |     | 003     | 700<br>725 | μA     |

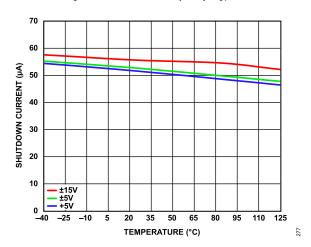

| Shutdown Current                        |                    | ADA4622-1 only                                                                           |     | 60      | 123        | 1 -    |

| OYNAMIC PERFORMANCE                     |                    | ADA4622-1 Only                                                                           |     | 00      |            | μA     |

| Slew Rate                               | SR                 | V = ±12.5 V B = 2 kO load conceitor (C ) =                                               |     |         |            |        |

| SIEW Nate                               | SK                 | $V_{OUT}$ = ±12.5 V, $R_L$ = 2 kΩ, load capacitor ( $C_L$ ) = 100 pF, $A_V$ = 1          |     |         |            |        |

|                                         |                    | Low to high transition                                                                   |     | 23      |            | V/µs   |

|                                         |                    | High to low transition                                                                   |     | -18     |            | V/µs   |

| Gain Bandwidth Product                  | GBP                | $A_V = 100, C_L = 35 pF$                                                                 |     | 8       |            | MHz    |

| Unity-Gain Crossover                    | UGC                | A <sub>V</sub> = 1                                                                       |     | 7       |            | MHz    |

| −3 dB Bandwidth                         | -3 dB              | A <sub>V</sub> = 1                                                                       |     | 15.5    |            | MHz    |

| Phase Margin                            | ФМ                 |                                                                                          |     | 53      |            | Degree |

| Settling Time                           | t <sub>S</sub>     | Input voltage ( $V_{IN}$ ) = 10 V step, $R_L$ = 2 k $\Omega$ , $C_L$ = 15 pF, $A_V$ = -1 |     |         |            |        |

| To 0.1%                                 |                    | 10 β1,7 λγ - 1                                                                           |     | 1.5     |            | μs     |

| To 0.01%                                |                    |                                                                                          |     | 2       |            |        |

| EMI REJECTION RATIO                     | EMIRR              | V <sub>IN</sub> = 100 mV p-p                                                             |     |         |            | μs     |

| f = 1000 MHz                            | LIVIIKK            | VIN - 100 IIIV p-p                                                                       |     | 00      |            | 4D     |

|                                         |                    |                                                                                          |     | 90      |            | dB     |

| f = 2400 MHz                            |                    |                                                                                          |     | 90      |            | dB     |

| NOISE PERFORMANCE                       |                    | 0.4.11=4-40.11=                                                                          |     | 0.75    |            |        |

| Voltage Noise                           | e <sub>N</sub> p-p | 0.1 Hz to 10 Hz                                                                          |     | 0.75    |            | μV p-p |

| Voltage Noise Density                   | e <sub>N</sub>     | f = 10 Hz                                                                                |     | 30      |            | nV/√Hz |

|                                         |                    | f = 100 Hz                                                                               |     | 15      |            | nV/√Hz |

|                                         |                    | f = 1 kHz                                                                                |     | 12.5    |            | nV/√Hz |

|                                         |                    | f = 10 kHz                                                                               |     | 12      |            | nV/√Hz |

| Current Noise Density                   | i <sub>N</sub>     | f = 1 kHz                                                                                |     | 0.8     |            | fA/√Hz |

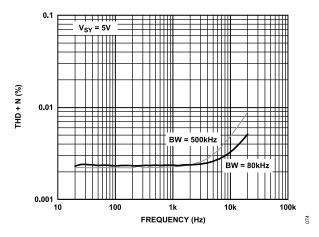

| Total Harmonic Distortion + Noise       | THD + N            | $A_V$ = 1, f = 10 Hz to 20 kHz, $V_{IN}$ = 7 V rms at 1 kHz                              |     |         |            |        |

| Bandwidth (BW) = 80 kHz                 |                    |                                                                                          |     | 0.0003  |            | %      |

| BW = 500 kHz                            |                    |                                                                                          |     | 0.00035 |            | %      |

| MATCHING SPECIFICATIONS                 |                    |                                                                                          |     |         |            |        |

| Maximum Offset Voltage over Temperature |                    |                                                                                          |     | 0.5     |            | mV     |

analog.com Rev. F | 4 of 36

Table 1.

| Parameter                        | Symbol | Test Conditions/Comments             | Min | Тур  | Max | Unit  |

|----------------------------------|--------|--------------------------------------|-----|------|-----|-------|

| Offset Voltage Temperature Drift |        |                                      |     | 0.25 |     | μV/°C |

| Input Bias Current               |        |                                      |     | 0.5  | 5   | pA    |

| CROSSTALK                        | Cs     | $R_L = 5 k\Omega, V_{IN} = 20 V p-p$ |     |      |     |       |

| ADA4622-1/ADA4622-2              |        | f = 1 kHz                            |     | -112 |     | dB    |

|                                  |        | f = 100 kHz                          |     | -72  |     | dB    |

| ADA4622-4                        |        | f = 1 kHz                            |     | -106 |     | dB    |

|                                  |        | f = 100 kHz                          |     | -66  |     | dB    |

# **ELECTRICAL CHARACTERISTICS, V<sub>SY</sub> = ±5 V**

$V_{SY}$  = ±5 V,  $V_{CM}$  =  $V_{OUT}$  = 0 V,  $T_A$  = 25°C, unless otherwise noted.

Table 2.

| arameter                    | Symbol                   | Test Conditions/Comments                                          | Min  | Тур              | Max   | Unit  |

|-----------------------------|--------------------------|-------------------------------------------------------------------|------|------------------|-------|-------|

| NPUT CHARACTERISTICS        |                          |                                                                   |      |                  |       |       |

| Offset Voltage              | V <sub>OS</sub>          |                                                                   |      |                  |       |       |

| A Grade                     |                          |                                                                   |      | +0.04            | ±0.8  | mV    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±2    | mV    |

| B Grade                     |                          |                                                                   |      | +0.04            | ±0.35 | mV    |

| ADA4622-1                   |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±1    | mV    |

| ADA4622-2                   |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±0.8  | mV    |

| Offset Voltage Match        |                          |                                                                   |      |                  | ±1    | mV    |

| Offset Voltage Drift        | $\Delta V_{OS}/\Delta T$ |                                                                   |      |                  |       |       |

| A Grade                     |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±4    | μV/°C |

| B Grade                     |                          |                                                                   |      |                  |       |       |

| ADA4622-1                   |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±1    | μV/°C |

| ADA4622-2                   |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±2    | μV/°C |

| Input Bias Current          | I <sub>B</sub>           |                                                                   |      | +2               | ±10   | pA    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±1.5  | nA    |

|                             |                          | V <sub>CM</sub> = V-                                              |      | -5               |       | pA    |

| Input Offset Current        | Ios                      |                                                                   |      |                  | ±10   | pA    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   |      |                  | ±0.5  | nA    |

| Input Voltage Range         | IVR                      |                                                                   | -5.2 |                  | +4    | V     |

| Common-Mode Rejection Ratio | CMRR                     |                                                                   |      |                  |       |       |

| A Grade                     |                          | V <sub>CM</sub> = -5 V to +2 V                                    | 75   | 91               |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   | 73   |                  |       | dB    |

| B Grade                     |                          | V <sub>CM</sub> = -5 V to +2 V                                    | 78   | 91               |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   | 75   |                  |       | dB    |

| Open-Loop Voltage Gain      | A <sub>VO</sub>          | $R_L = 10 \text{ k}\Omega$ , $V_{OUT} = -4.4 \text{ V}$ to +4.4 V | 113  | 118              |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   | 105  |                  |       | dB    |

|                             |                          | $R_L = 1 k\Omega$ , $V_{OUT} = -4.4 V to +4.4 V$                  | 100  | 105              |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                                   | 91   |                  |       | dB    |

| Input Capacitance           | C <sub>INDM</sub>        | Differential mode                                                 |      | 0.4              |       | pF    |

|                             | C <sub>INCM</sub>        | Common mode                                                       |      | 3.6              |       | pF    |

| Input Resistance            | R <sub>DIFF</sub>        | Differential mode                                                 |      | 10 <sup>13</sup> |       | Ω     |

| -                           | R <sub>CM</sub>          | Common mode                                                       |      | 10 <sup>13</sup> |       | Ω     |

analog.com Rev. F | 5 of 36

Table 2.

| Parameter                    | Symbol             | Test Conditions/Comments                                                            | Min  | Тур          | Max    | Unit    |

|------------------------------|--------------------|-------------------------------------------------------------------------------------|------|--------------|--------|---------|

| OUTPUT CHARACTERISTICS       |                    |                                                                                     |      |              |        |         |

| Output Voltage               |                    |                                                                                     |      |              |        |         |

| High                         | V <sub>OH</sub>    | I <sub>SOURCE</sub> = 1 mA                                                          | 4.95 | 4.97         |        | V       |

|                              |                    | -40°C < T <sub>A</sub> < +125°C                                                     | 4.9  |              |        | V       |

|                              |                    | I <sub>SOURCE</sub> = 15 mA                                                         | 4.3  | 4.51         |        | V       |

|                              |                    | -40°C < T <sub>A</sub> < +125°C                                                     | 4.1  |              |        | V       |

| Low                          | V <sub>OL</sub>    | I <sub>SINK</sub> = 1 mA                                                            |      | -4.955       | -4.935 | V       |

|                              |                    | -40°C < T <sub>A</sub> < +125°C                                                     |      |              | -4.88  | V       |

|                              |                    | I <sub>SINK</sub> = 15 mA                                                           |      | -4.685       | -4.55  | V       |

|                              |                    | -40°C < T <sub>A</sub> < +125°C                                                     |      |              | -4.25  | V       |

| Output Current               | I <sub>OUT</sub>   | V <sub>DROPOUT</sub> < 1 V                                                          |      | 20           |        | mA      |

| Short-Circuit Current        | I <sub>SC</sub>    | Sourcing                                                                            |      | 31           |        | mA      |

|                              | 30                 | Sinking                                                                             |      | -40          |        | mA      |

| Closed-Loop Output Impedance | Z <sub>OUT</sub>   | f = 1 kHz, A <sub>V</sub> = 1                                                       |      | 0.1          |        | Ω       |

| •·····                       | -001               | A <sub>V</sub> = 10                                                                 |      | 0.4          |        | Ω       |

|                              |                    | A <sub>V</sub> = 100                                                                |      | 4            |        | Ω       |

| POWER SUPPLY                 |                    | Αγ - 100                                                                            |      | <del>_</del> |        | 122     |

| Power Supply Rejection Ratio | PSRR               | V <sub>SY</sub> = ±4 V to ±18 V                                                     | 87   | 103          |        | dB      |

| Tower ouppry regional reason | TORK               | -40°C < T <sub>A</sub> < +125°C                                                     | 81   | 100          |        | dB      |

| Supply Current per Amplifier | la                 | 40 0 × 1 <sub>A</sub> × 1123 0                                                      | 01   |              |        | ub      |

| ADA4622-1/ADA4622-4          | I <sub>SY</sub>    |                                                                                     |      | 660          | 725    | μA      |

| ADA4022-1/ADA4022-4          |                    | 40°C < T < 1405°C                                                                   |      | 000          |        | 1.      |

| ADA4622 2                    |                    | -40°C < T <sub>A</sub> < +125°C                                                     |      | 040          | 750    | μA      |

| ADA4622-2                    |                    | 40°0 . T 405°0                                                                      |      | 610          | 675    | μA      |

| Charledoure Commont          |                    | -40°C < T <sub>A</sub> < +125°C                                                     |      | 50           | 700    | μA      |

| Shutdown Current             |                    | ADA4622-1 only                                                                      |      | 50           |        | μA      |

| DYNAMIC PERFORMANCE          | 25                 | V                                                                                   |      |              |        |         |

| Slew Rate                    | SR                 | $V_{OUT} = \pm 3 \text{ V}, R_L = 2 \text{ k}\Omega, C_L = 100 \text{ pF}, A_V = 1$ |      | •            |        | ,,      |

|                              |                    | Low to high transition                                                              |      | 21           |        | V/µs    |

|                              |                    | High to low transition                                                              |      | -16          |        | V/µs    |

| Gain Bandwidth Product       | GBP                | $A_V = 100, C_L = 35 pF$                                                            |      | 7.8          |        | MHz     |

| Unity-Gain Crossover         | UGC                | A <sub>V</sub> = 1                                                                  |      | 6.5          |        | MHz     |

| −3 dB Bandwidth              | −3 dB              | A <sub>V</sub> = 1                                                                  |      | 10           |        | MHz     |

| Phase Margin                 | ΦМ                 |                                                                                     |      | 50           |        | Degrees |

| Settling Time                | t <sub>S</sub>     | $V_{IN} = 8 \text{ V step}, R_L = 2 \text{ k}\Omega, C_L = 15 \text{ pF}, A_V = -1$ |      |              |        |         |

| To 0.1%                      |                    |                                                                                     |      | 1.5          |        | μs      |

| To 0.01%                     |                    |                                                                                     |      | 2            |        | μs      |

| EMI REJECTION RATIO          | EMIRR              | V <sub>IN</sub> = 100 mV p-p                                                        |      |              |        |         |

| f = 1000 MHz                 |                    |                                                                                     |      | 90           |        | dB      |

| f = 2400 MHz                 |                    |                                                                                     |      | 90           |        | dB      |

| NOISE PERFORMANCE            |                    |                                                                                     |      |              |        |         |

| Voltage Noise                | e <sub>N</sub> p-p | 0.1 Hz to 10 Hz                                                                     |      | 0.75         |        | μV p-p  |

| Voltage Noise Density        | e <sub>N</sub>     | f = 10 Hz                                                                           |      | 30           |        | nV/√Hz  |

|                              |                    | f = 100 Hz                                                                          |      | 15           |        | nV/√Hz  |

|                              |                    | f = 1 kHz                                                                           |      | 12.5         |        | nV/√Hz  |

|                              |                    | f = 10 kHz                                                                          |      | 12           |        | nV/√Hz  |

analog.com Rev. F | 6 of 36

Table 2.

| Parameter                                                        | Symbol         | Test Conditions/Comments                                      | Min | Тур         | Max | Unit   |

|------------------------------------------------------------------|----------------|---------------------------------------------------------------|-----|-------------|-----|--------|

| Current Noise Density                                            | i <sub>N</sub> | f = 1 kHz                                                     |     | 0.8         |     | fA/√Hz |

| Total Harmonic Distortion + Noise                                | THD + N        | $A_V$ = 1, f = 10 Hz to 20 kHz, $V_{IN}$ = 1.5 V rms at 1 kHz |     |             |     |        |

| BW = 80 kHz                                                      |                |                                                               |     | 0.0005      |     | %      |

| BW = 500 kHz                                                     |                |                                                               |     | 0.0008      |     | %      |

| MATCHING SPECIFICATIONS  Maximum Offset Voltage over Temperature |                |                                                               |     | 0.5         |     | mV     |

| Offset Voltage Temperature Drift                                 |                |                                                               |     | 0.25        |     | μV/°C  |

| Input Bias Current                                               |                |                                                               |     | 0.5         | 5   | pA     |

| CROSSTALK                                                        | Cs             | $R_L = 5 k\Omega$ , $V_{IN} = 6 V p-p$                        |     |             |     |        |

| ADA4622-1/ADA4622-2                                              |                | f = 1 kHz                                                     |     | -112        |     | dB     |

|                                                                  |                | f = 100 kHz                                                   |     | <b>-</b> 72 |     | dB     |

| ADA4622-4                                                        |                | f = 1 kHz                                                     |     | -106        |     | dB     |

|                                                                  |                | f = 100 kHz                                                   |     | -66         |     | dB     |

# ELECTRICAL CHARACTERISTICS, $V_{SY} = 5 V$

$V_{SY}$  = 5 V,  $V_{CM}$  = 0 V,  $V_{OUT}$  =  $V_{SY}/2$ ,  $T_A$  = 25°C, unless otherwise noted.

Table 3.

| Parameter                   | Symbol                   | Test Conditions/Comments                                | Min  | Тур   | Max   | Unit  |

|-----------------------------|--------------------------|---------------------------------------------------------|------|-------|-------|-------|

| INPUT CHARACTERISTICS       |                          |                                                         |      |       |       |       |

| Offset Voltage              | Vos                      |                                                         |      |       |       |       |

| A Grade                     |                          |                                                         |      | +0.04 | ±0.8  | mV    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±2    | mV    |

| B Grade                     |                          |                                                         |      | +0.04 | ±0.35 | mV    |

| ADA4622-1                   |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±1    | mV    |

| ADA4622-2                   |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±0.8  | mV    |

| Offset Voltage Match        |                          |                                                         |      |       | ±1    | mV    |

| Offset Voltage Drift        | $\Delta V_{OS}/\Delta T$ |                                                         |      |       |       |       |

| A Grade                     |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±4    | μV/°C |

| B Grade                     |                          |                                                         |      |       |       |       |

| ADA4622-1                   |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±1    | μV/°C |

| ADA4622-2                   |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±2    | μV/°C |

| Input Bias Current          | I <sub>B</sub>           |                                                         |      | 2     | ±10   | pА    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±1.5  | nA    |

| Input Offset Current        | I <sub>OS</sub>          |                                                         |      |       | ±10   | pA    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         |      |       | ±0.5  | nA    |

| Input Voltage Range         | IVR                      |                                                         | -0.2 |       | +4    | V     |

| Common-Mode Rejection Ratio | CMRR                     |                                                         |      |       |       |       |

| A Grade                     |                          | V <sub>CM</sub> = 0 V to 2 V                            | 70   | 87    |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         | 67   |       |       | dB    |

| B Grade                     |                          | V <sub>CM</sub> = 0 V to 2 V                            | 73   | 87    |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         | 70   |       |       | dB    |

| Open-Loop Voltage Gain      | A <sub>VO</sub>          | $R_L$ = 10 k $\Omega$ to V-, $V_{OUT}$ = 0.2 V to 4.6 V | 110  | 115   |       | dB    |

|                             |                          | -40°C < T <sub>A</sub> < +125°C                         | 99   |       |       | dB    |

analog.com Rev. F | 7 of 36

Table 3.

| Parameter                    | Symbol            | Test Conditions/Comments                                                            | Min  | Тур              | Max | Unit    |

|------------------------------|-------------------|-------------------------------------------------------------------------------------|------|------------------|-----|---------|

|                              |                   | $R_L$ = 1 k $\Omega$ to V-, $V_{OUT}$ = 0.2 V to 4.6 V                              | 96   | 104              |     | dB      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     | 87   |                  |     | dB      |

| Input Capacitance            | C <sub>INDM</sub> | Differential mode                                                                   |      | 0.4              |     | pF      |

|                              | C <sub>INCM</sub> | Common mode                                                                         |      | 3.6              |     | pF      |

| Input Resistance             | R <sub>DIFF</sub> | Differential mode                                                                   |      | 10 <sup>13</sup> |     | Ω       |

|                              | R <sub>CM</sub>   | Common mode                                                                         |      | 10 <sup>13</sup> |     | Ω       |

| DUTPUT CHARACTERISTICS       |                   |                                                                                     |      |                  |     |         |

| Output Voltage               |                   |                                                                                     |      |                  |     |         |

| High                         | V <sub>OH</sub>   | I <sub>SOURCE</sub> = 1 mA                                                          | 4.95 | 4.97             |     | V       |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     | 4.9  |                  |     | V       |

|                              |                   | I <sub>SOURCE</sub> = 15 mA                                                         | 4.3  | 4.5              |     | V       |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     | 4.1  |                  |     | V       |

| Low                          | V <sub>OL</sub>   | I <sub>SINK</sub> = 1 mA                                                            |      | 45               | 65  | mV      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     |      |                  | 120 | mV      |

|                              |                   | I <sub>SINK</sub> = 15 mA                                                           |      | 310              | 450 | mV      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     |      |                  | 750 | mV      |

| Output Current               | I <sub>OUT</sub>  | V <sub>DROPOUT</sub> < 1 V                                                          |      | 20               |     | mA      |

| Short-Circuit Current        | I <sub>SC</sub>   | Sourcing                                                                            |      | 27               |     | mA      |

|                              |                   | Sinking                                                                             |      | -35              |     | mA      |

| Closed-Loop Output Impedance | Z <sub>OUT</sub>  | f = 1 kHz, A <sub>V</sub> = 1                                                       |      | 0.1              |     | Ω       |

|                              |                   | A <sub>V</sub> = 10                                                                 |      | 0.6              |     | Ω       |

|                              |                   | A <sub>V</sub> = 100                                                                |      | 5                |     | Ω       |

| OWER SUPPLY                  |                   |                                                                                     |      |                  |     |         |

| Power Supply Rejection Ratio | PSRR              | V <sub>SY</sub> = 4 V to 15 V                                                       | 80   | 95               |     | dB      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     | 74   |                  |     | dB      |

| Supply Current per Amplifier | I <sub>SY</sub>   |                                                                                     |      |                  |     |         |

| ADA4622-1/ADA4622-4          |                   |                                                                                     |      | 650              | 700 | μA      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     |      |                  | 725 | μA      |

| ADA4622-2                    |                   |                                                                                     |      | 600              | 650 | μA      |

|                              |                   | -40°C < T <sub>A</sub> < +125°C                                                     |      |                  | 675 | μA      |

| Shutdown Current             |                   | ADA4622-1 only                                                                      |      | 50               |     | μA      |

| YNAMIC PERFORMANCE           |                   | •                                                                                   |      |                  |     | '       |

| Slew Rate                    | SR                | $V_{OUT}$ = 0.5 V to 3.5 V, $R_L$ = 2 k $\Omega$ , $C_L$ = 100 pF, $A_V$ = 1        |      |                  |     |         |

|                              |                   | Low to high transition                                                              |      | 20               |     | V/µs    |

|                              |                   | High to low transition                                                              |      | -15              |     | V/µs    |

| Gain Bandwidth Product       | GBP               | A <sub>V</sub> = 100, C <sub>L</sub> = 35 pF                                        |      | 7.2              |     | MHz     |

| Unity-Gain Crossover         | UGC               | A <sub>V</sub> = 1                                                                  |      | 6                |     | MHz     |

| -3 dB Bandwidth              | -3 dB             | A <sub>V</sub> = 1                                                                  |      | 9                |     | MHz     |

| Phase Margin                 | ФМ                |                                                                                     |      | 50               |     | Degrees |

| Settling Time                | t <sub>S</sub>    | $V_{IN} = 4 \text{ V step}, R_L = 2 \text{ k}\Omega, C_L = 15 \text{ pF}, A_V = -1$ |      |                  |     | 3.250   |

| To 0.1%                      | 3                 | 1, L                                                                                |      | 1.5              |     | μs      |

| To 0.01%                     |                   |                                                                                     |      | 2.0              |     | μs      |

| EMI REJECTION RATIO          | EMIRR             | V <sub>IN</sub> = 100 mV p-p                                                        |      |                  |     |         |

| f = 1000 MHz                 | LIVIII (I (       | VIII 100 III V P P                                                                  |      | 90               |     | dB      |

analog.com Rev. F | 8 of 36

Table 3.

| Parameter                               | Symbol             | Test Conditions/Comments                                      | Min Ty | p N  | Vlax | Unit   |

|-----------------------------------------|--------------------|---------------------------------------------------------------|--------|------|------|--------|

| f = 2400 MHz                            |                    |                                                               | 90     |      |      | dB     |

| NOISE PERFORMANCE                       |                    |                                                               |        |      |      |        |

| Voltage Noise                           | e <sub>N</sub> p-p | 0.1 Hz to 10 Hz                                               | 0.7    | 75   |      | μV p-p |

| Voltage Noise Density                   | e <sub>N</sub>     | f = 10 Hz                                                     | 30     |      |      | nV/√Hz |

|                                         |                    | f = 100 Hz                                                    | 15     |      |      | nV/√Hz |

|                                         |                    | f = 1 kHz                                                     | 12     | .5   |      | nV/√Hz |

|                                         |                    | f = 10 kHz                                                    | 12     |      |      | nV/√Hz |

| Current Noise Density                   | i <sub>N</sub>     | f = 1 kHz                                                     | 3.0    | 3    |      | fA/√Hz |

| Total Harmonic Distortion + Noise       | THD + N            | $A_V$ = 1, f = 10 Hz to 20 kHz, $V_{IN}$ = 0.5 V rms at 1 kHz |        |      |      |        |

| BW = 80 kHz                             |                    |                                                               | 0.0    | 0025 |      | %      |

| BW = 500 kHz                            |                    |                                                               | 0.0    | 0025 |      | %      |

| MATCHING SPECIFICATIONS                 |                    |                                                               |        |      |      |        |

| Maximum Offset Voltage over Temperature |                    |                                                               | 0.5    | 5    |      | mV     |

| Offset Voltage Temperature Drift        |                    |                                                               | 0.2    | 25   |      | μV/°C  |

| Input Bias Current                      |                    |                                                               | 0.5    | 5 5  | 5    | pA     |

| CROSSTALK                               | Cs                 | $R_L = 5 k\Omega$ , $V_{IN} = 3 V p-p$                        |        |      |      |        |

| ADA4622-1/ADA4622-2                     |                    | f = 1 kHz                                                     | -1     | 12   |      | dB     |

|                                         |                    | f = 100 kHz                                                   | -7     | 2    |      | dB     |

| ADA4622-4                               |                    | f = 1 kHz                                                     | -1     | 06   |      | dB     |

|                                         |                    | f = 100 kHz                                                   | -6     | 6    |      | dB     |

analog.com Rev. F | 9 of 36

#### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                            | Rating                     |

|--------------------------------------|----------------------------|

| Supply Voltage                       | 36 V                       |

| Input Voltage                        | (V-) -0.3 V to (V+) +0.2 V |

| Differential Input Voltage           | 36 V                       |

| Storage Temperature Range            | -65°C to +150°C            |

| Operating Temperature Range          | -40°C to +125°C            |

| Junction Temperature Range           | -65°C to +150°C            |

| Lead Temperature, Soldering (10 sec) | 300°C                      |

| ESD Rating, Human Body Model (HBM)   | 4 kV                       |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

Table 5. Thermal Resistance

| Package Type <sup>1, 2</sup>        | $\theta_{JA}$ | $\theta_{\text{JC}}^{3}$ | Unit |

|-------------------------------------|---------------|--------------------------|------|

| 8-Lead SOIC_N                       |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 63                       | °C/W |

| 2-Layer JEDEC Board                 | 120           | N/A                      | °C/W |

| 8-Lead MSOP                         |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 115                      | °C/W |

| 2-Layer JEDEC Board                 | 185           | N/A                      | °C/W |

| 8-Lead LFCSP                        |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 63                       | °C/W |

| 2-Layer JEDEC Board                 | 145           | N/A                      | °C/W |

| 2-Layer JEDEC Board with 2 × 2 Vias | 55            | N/A                      | °C/W |

| 5-Lead SOT-23                       |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 82                       | °C/W |

| 2-Layer JEDEC Board                 | 339           | N/A                      | °C/W |

| 14-Lead SOIC_N                      |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 42                       | °C/W |

| 2-Layer JEDEC Board                 | 72            | N/A                      | °C/W |

| 16-Lead, 4 × 4 mm LFCSP             |               |                          |      |

| 1-Layer JEDEC Board                 | N/A           | 2.2                      | °C/W |

| 2-Layer JEDEC Board                 | 48            | N/A                      | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC thermal test board. See JEDEC JESD51.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. F | 10 of 36

<sup>&</sup>lt;sup>2</sup> N/A means not applicable.

$<sup>^3~</sup>$  For  $\theta_{JC}$  test, 100  $\mu m$  thermal interface material (TIM) is used. TIM is assumed to have 3.6 W/mK.

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

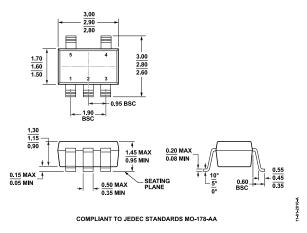

Figure 2. 5-Lead SOT-23 Pin Configuration, ADA4622-1

Table 6. 5-Lead SOT-23 Pin Function Descriptions, ADA4622-1

| Pin No. | Mnemonic | Description              |

|---------|----------|--------------------------|

| 1       | OUT      | Output.                  |

| 2       | V-       | Negative Supply Voltage. |

| 3       | +IN      | Noninverting Input.      |

| 4       | -IN      | Inverting Input.         |

| 5       | V+       | Positive Supply Voltage. |

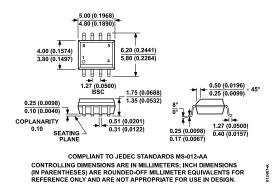

Figure 3. 8-Lead SOIC\_N Pin Configuration, ADA4622-1

Table 7. 8-Lead SOIC\_N Pin Function Descriptions, ADA4622-1

| Pin No. | Mnemonic | Description                 |

|---------|----------|-----------------------------|

| 1, 5    | NIC      | Not Internally Connected.   |

| 2       | -IN      | Inverting Input.            |

| 3       | +IN      | Noninverting Input.         |

| 4       | V-       | Negative Supply Voltage.    |

| 6       | OUT      | Output.                     |

| 7       | V+       | Positive Supply Voltage.    |

| 8       | DISABLE  | Disable Input (Active Low). |

analog.com Rev. F | 11 of 36

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 4. 8-Lead MSOP Pin Configuration, ADA4622-2

Figure 5. 8-Lead SOIC\_N Pin Configuration, ADA4622-2

Table 8. 8-Lead MSOP and 8-Lead SOIC\_N Pin Function Descriptions, ADA4622-2

| Pin No. | Mnemonic | Description                    |

|---------|----------|--------------------------------|

| 1       | OUT A    | Output, Channel A.             |

| 2       | -IN A    | Inverting Input, Channel A.    |

| 3       | +IN A    | Noninverting Input, Channel A. |

| 4       | V-       | Negative Supply Voltage.       |

| 5       | +IN B    | Noninverting Input, Channel B. |

| 6       | −IN B    | Inverting Input, Channel B.    |

| 7       | OUT B    | Output, Channel B.             |

| 8       | V+       | Positive Supply Voltage.       |

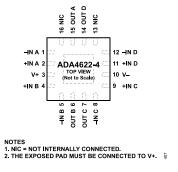

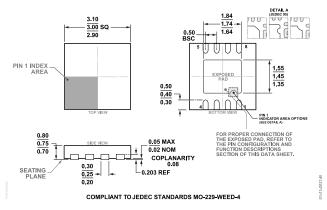

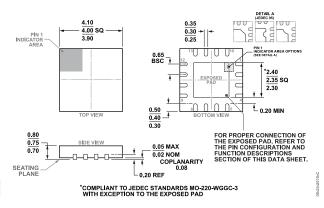

Figure 6. 8-Lead LFCSP Pin Configuration, ADA4622-2

Table 9. 8-Lead LFCSP Pin Function Descriptions, ADA4622-2

| Pin No. | Mnemonic | Description                                                              |  |

|---------|----------|--------------------------------------------------------------------------|--|

| 1       | OUT A    | Output, Channel A.                                                       |  |

| 2       | -IN A    | Inverting Input, Channel A.                                              |  |

| 3       | +IN A    | Noninverting Input, Channel A.                                           |  |

| 4       | V-       | Negative Supply Voltage.                                                 |  |

| 5       | +IN B    | Noninverting Input, Channel B.                                           |  |

| 6       | -IN B    | Inverting Input, Channel B.                                              |  |

| 7       | OUT B    | Output, Channel B.                                                       |  |

| 8       | V+       | Positive Supply Voltage.                                                 |  |

|         | EPAD     | Exposed Pad. It is recommended to connect the exposed pad to the V+ pin. |  |

Figure 7. 16-Lead LFCSP Pin Configuration, ADA4622-4

analog.com Rev. F | 12 of 36

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Table 10. 16-Lead LFCSP Pin Function Descriptions, ADA4622-4

| Pin No. | Mnemonic | Description                                                   |

|---------|----------|---------------------------------------------------------------|

| 1       | -IN A    | Inverting Input, Channel A.                                   |

| 2       | +IN A    | Noninverting Input, Channel A.                                |

| 3       | V+       | Positive Supply Voltage.                                      |

| 4       | +IN B    | Noninverting Input, Channel B.                                |

| 5       | -IN B    | Inverting Input, Channel B.                                   |

| 6       | OUT B    | Output, Channel B.                                            |

| 7       | OUT C    | Output, Channel C.                                            |

| 8       | -IN C    | Inverting Input, Channel C.                                   |

| 9       | +IN C    | Noninverting Input, Channel C.                                |

| 10      | V-       | Negative Supply Voltage.                                      |

| 11      | +IN D    | Noninverting Input, Channel D.                                |

| 12      | -IN D    | Inverting Input, Channel D.                                   |

| 13, 16  | NIC      | Not Internally Connected.                                     |

| 14      | OUT D    | Output, Channel D.                                            |

| 15      | OUT A    | Output, Channel A.                                            |

|         | EPAD     | Exposed Pad. The exposed pad must be connected to the V+ pin. |

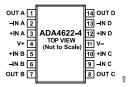

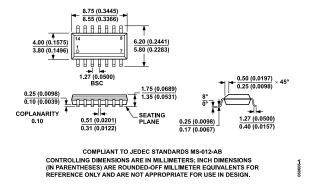

Figure 8. 14-Lead SOIC\_N Pin Configuration, ADA4622-4

Table 11. 14-Lead SOIC\_N Pin Function Descriptions, ADA4622-4

| Pin No. | Mnemonic | Description                    |

|---------|----------|--------------------------------|

| 1       | OUT A    | Output, Channel A.             |

| 2       | -IN A    | Inverting Input, Channel A.    |

| 3       | +IN A    | Noninverting Input, Channel A. |

| 4       | V+       | Positive Supply Voltage.       |

| 5       | +IN B    | Noninverting Input, Channel B. |

| 6       | -IN B    | Inverting Input, Channel B.    |

| 7       | OUT B    | Output, Channel B.             |

| 8       | OUT C    | Output, Channel C.             |

| 9       | -IN C    | Inverting Input, Channel C.    |

| 10      | +IN C    | Noninverting Input, Channel C. |

| 11      | V-       | Negative Supply Voltage.       |

| 12      | +IN D    | Noninverting Input, Channel D. |

| 13      | -IN D    | Inverting Input, Channel D.    |

| 14      | OUT D    | Output, Channel D.             |

analog.com Rev. F | 13 of 36

$T_A = 25$ °C, unless otherwise noted.

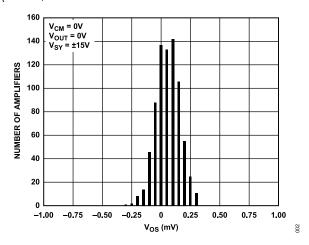

Figure 9. Input Offset Voltage ( $V_{OS}$ ) Distribution,  $V_{SY} = \pm 15 \text{ V}$

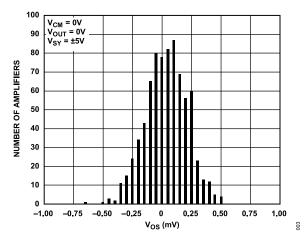

Figure 10. Input Offset Voltage ( $V_{OS}$ ) Distribution,  $V_{SY} = \pm 5 \text{ V}$

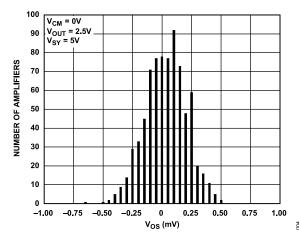

Figure 11. Input Offset Voltage ( $V_{OS}$ ) Distribution,  $V_{SY} = 5 \text{ V}$

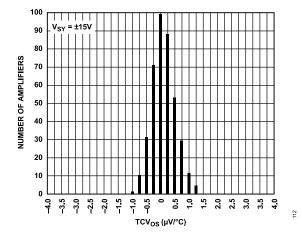

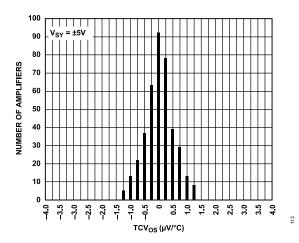

Figure 12. Input Offset Voltage Drift (TCV $_{

m OS}$ ) Distribution (-40°C to +125°C),  $V_{

m SY}$  = ±15 V

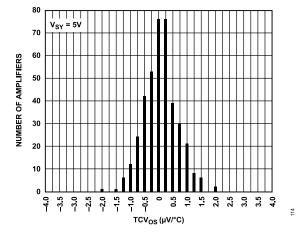

Figure 13. Input Offset Voltage Drift (TCV $_{OS}$ ) Distribution (-40°C to +125°C),  $V_{SY}$  = ±5 V

Figure 14. Input Offset Voltage Drift (TCV<sub>OS</sub>) Distribution (-40°C to +125°C),  $V_{SV} = 5 \text{ V}$

analog.com Rev. F | 14 of 36

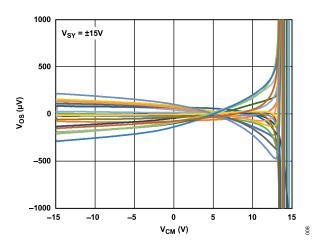

Figure 15. Input Offset Voltage ( $V_{OS}$ ) vs. Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$  =  $\pm 15~V$

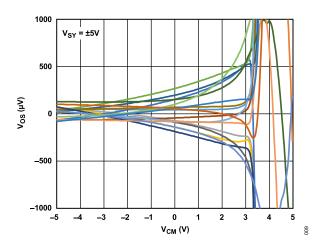

Figure 16. Input Offset Voltage ( $V_{OS}$ ) vs. Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$  =  $\pm 5 \text{ V}$

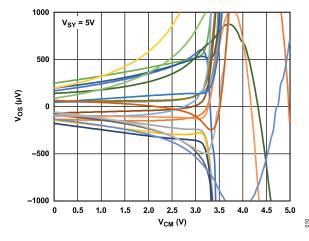

Figure 17. Input Offset Voltage ( $V_{OS}$ ) vs. Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$  = 5 V

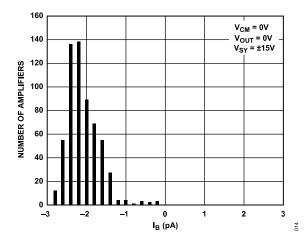

Figure 18. Input Bias Current (I<sub>B</sub>) Distribution,  $V_{SY} = \pm 15 \text{ V}$

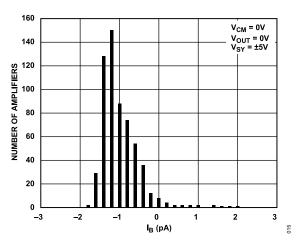

Figure 19. Input Bias Current (IB) Distribution, VSY = ±5 V

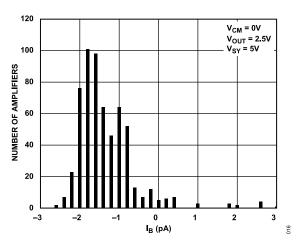

Figure 20. Input Bias Current ( $I_B$ ) Distribution,  $V_{SY} = 5 \text{ V}$

analog.com Rev. F | 15 of 36

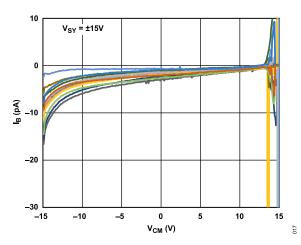

Figure 21. Input Bias Current (I<sub>B</sub>) vs. Input Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$  = ±15 V

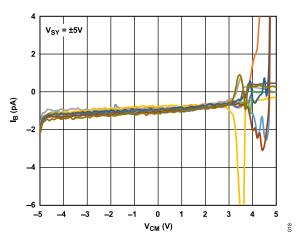

Figure 22. Input Bias Current ( $I_B$ ) vs. Input Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$ = ±5 V

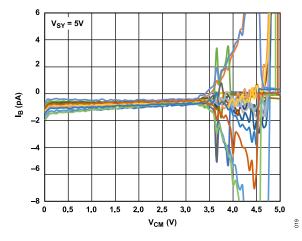

Figure 23. Input Bias Current ( $I_B$ ) vs. Input Common-Mode Voltage ( $V_{CM}$ ),  $V_{SY}$ = 5 V

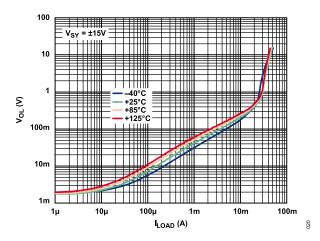

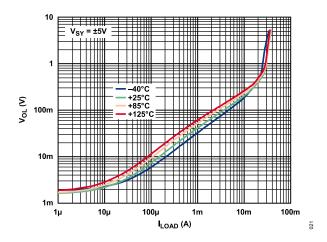

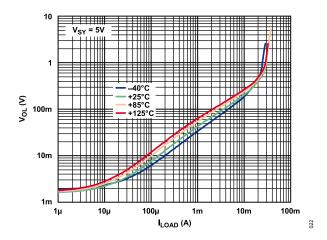

Figure 24. Output Voltage Low ( $V_{OL}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY}$  = ±15 V

Figure 25. Output Voltage Low ( $V_{OL}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY} = \pm 5 \text{ V}$

Figure 26. Output Voltage Low ( $V_{OL}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY} = 5 \text{ V}$

analog.com Rev. F | 16 of 36

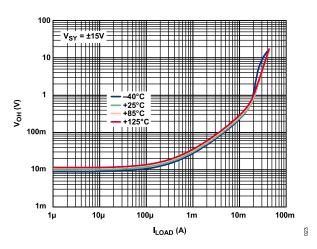

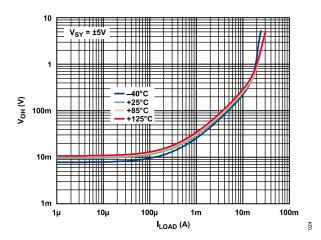

Figure 27. Output Voltage High ( $V_{OH}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY} = \pm 15 \text{ V}$

Figure 28. Output Voltage High ( $V_{OH}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY} = \pm 5 \text{ V}$

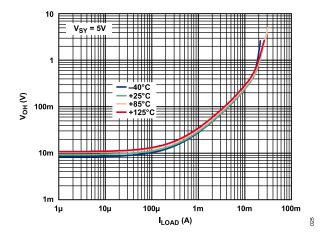

Figure 29. Output Voltage High ( $V_{OH}$ ) to Supply Rail vs. Load Current ( $I_{LOAD}$ ) over Temperature,  $V_{SY} = 5 \text{ V}$

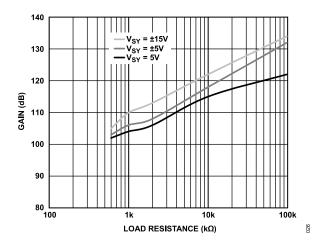

Figure 30. Open-Loop Voltage Gain (A<sub>VO</sub>) vs. Load Resistance

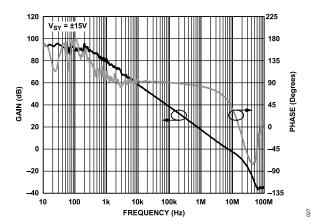

Figure 31. Open-Loop Voltage Gain ( $A_{VO}$ ) and Phase vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

Figure 32. Open-Loop Voltage Gain ( $A_{VO}$ ) and Phase vs. Frequency,  $V_{SY} = \pm 5$

analog.com Rev. F | 17 of 36

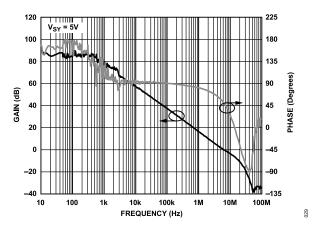

Figure 33. Open-Loop Voltage Gain ( $A_{VO}$ ) and Phase vs. Frequency,  $V_{SY} = 5 \text{ V}$

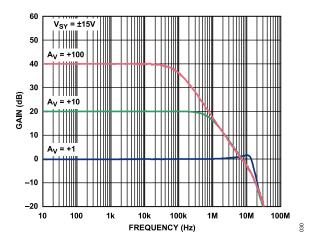

Figure 34. Closed-Loop Gain (A<sub>V</sub>) vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

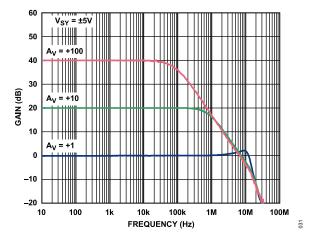

Figure 35. Closed-Loop Gain (A<sub>V</sub>) vs. Frequency,  $V_{SY} = \pm 5 \text{ V}$

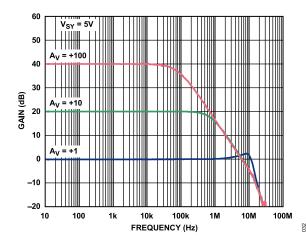

Figure 36. Closed-Loop Gain (A<sub>V</sub>) vs. Frequency,  $V_{SY} = 5 V$

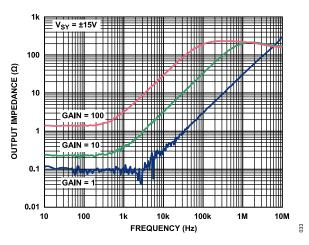

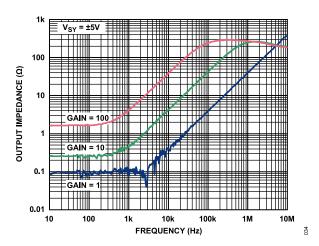

Figure 37. Output Impedance vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

Figure 38. Output Impedance vs. Frequency,  $V_{SY} = \pm 5 \text{ V}$

analog.com Rev. F | 18 of 36

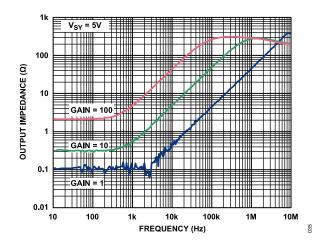

Figure 39. Output Impedance vs. Frequency, V<sub>SY</sub> = 5 V

Figure 40. CMRR vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

Figure 41. CMRR vs. Frequency, V<sub>SY</sub> = ±5 V

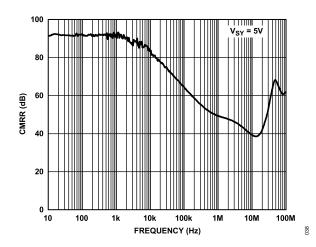

Figure 42. CMRR vs. Frequency,  $V_{SY} = 5 \text{ V}$

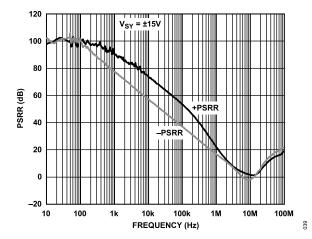

Figure 43. PSRR vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

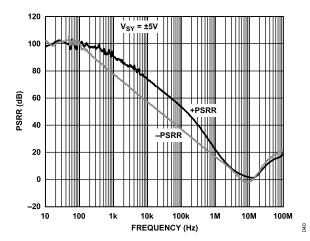

Figure 44. PSRR vs. Frequency,  $V_{SY} = \pm 5 V$

analog.com Rev. F | 19 of 36

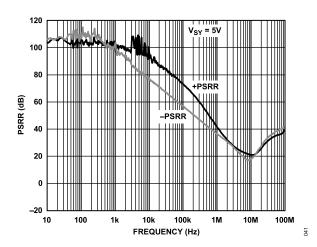

Figure 45. PSRR vs. Frequency, V<sub>SY</sub> = 5 V

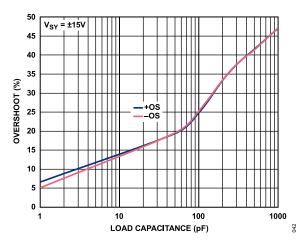

Figure 46. Small Signal Overshoot (OS) vs. Load Capacitance,  $V_{SY} = \pm 15 \text{ V}$

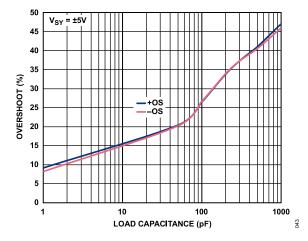

Figure 47. Small Signal Overshoot (OS) vs. Load Capacitance,  $V_{SY} = \pm 5 V$

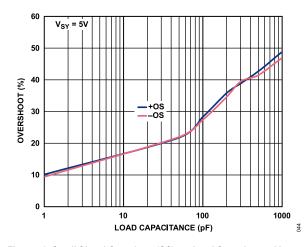

Figure 48. Small Signal Overshoot (OS) vs. Load Capacitance,  $V_{SY} = 5 \text{ V}$

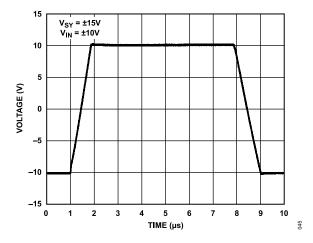

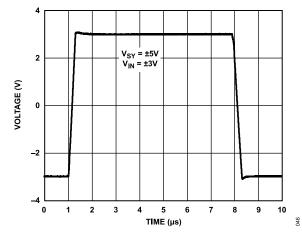

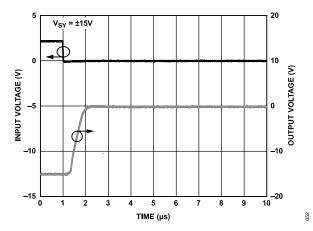

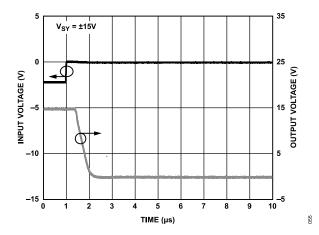

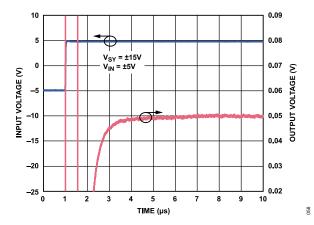

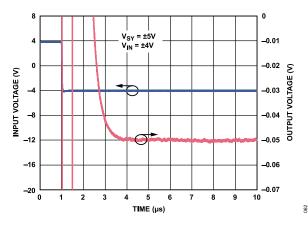

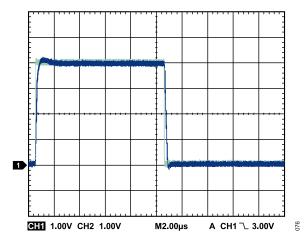

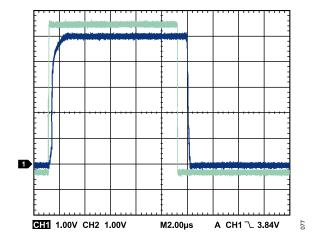

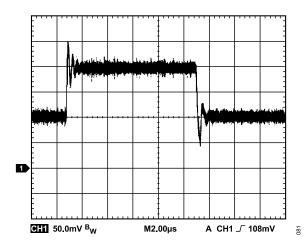

Figure 49. Large Signal Transient Response,  $V_{SY} = \pm 15 \text{ V}$

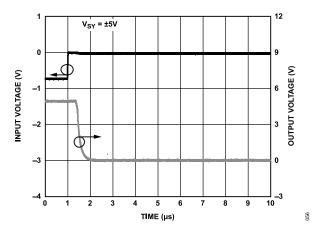

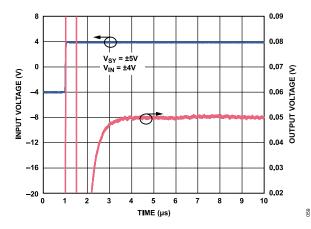

Figure 50. Large Signal Transient Response,  $V_{SY} = \pm 5 V$

analog.com Rev. F | 20 of 36

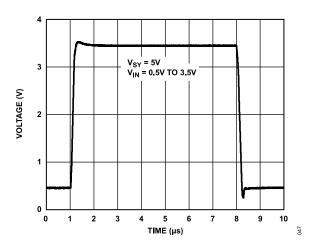

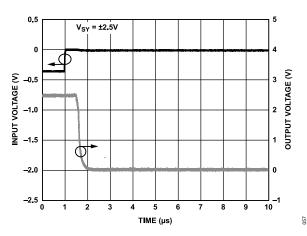

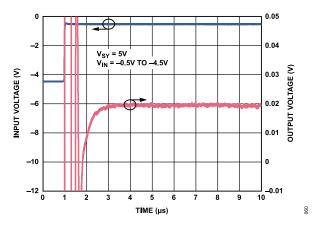

Figure 51. Large Signal Transient Response, V<sub>SY</sub> = 5 V

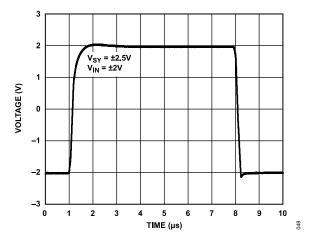

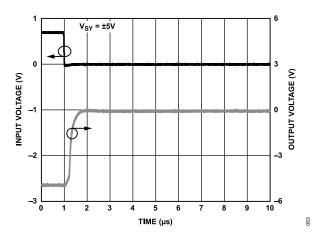

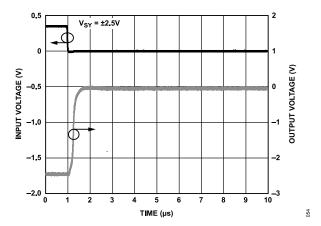

Figure 52. Large Signal Transient Response, V<sub>SY</sub> = ±2.5 V

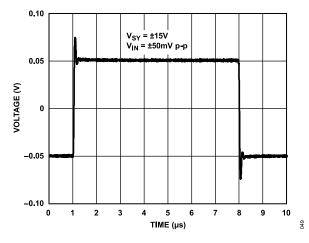

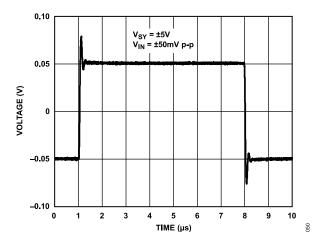

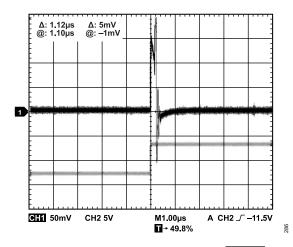

Figure 53. Small Signal Transient Response,  $V_{SY} = \pm 15 \text{ V}$

Figure 54. Small Signal Transient Response, V<sub>SY</sub> = ±5 V

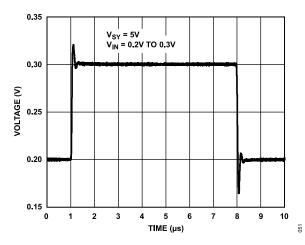

Figure 55. Small Signal Transient Response, V<sub>SY</sub> = 5 V

Figure 56. Negative Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 15 \text{ V}$

analog.com Rev. F | 21 of 36

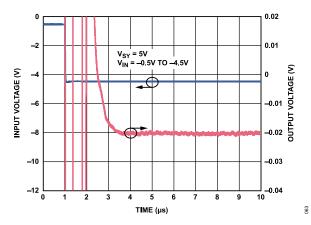

Figure 57. Negative Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 5$  V

Figure 58. Negative Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 2.5 \text{ V}$

Figure 59. Positive Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 15 \text{ V}$

Figure 60. Positive Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 5 \text{ V}$

Figure 61. Positive Overload Recovery,  $A_V = -10$ ,  $V_{SY} = \pm 2.5 \text{ V}$

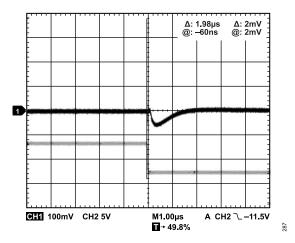

Figure 62. Positive Settling Time,  $A_V = -10$ ,  $V_{SY} = \pm 15 \text{ V}$

analog.com Rev. F | 22 of 36

Figure 63. Positive Settling Time,  $A_V = -10$ ,  $V_{SY} = \pm 5 V$

Figure 64. Positive Settling Time,  $A_V = -10$ ,  $V_{SY} = 5 \text{ V}$

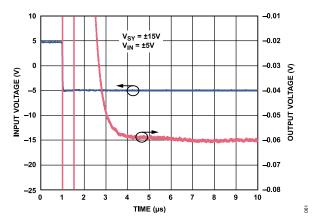

Figure 65. Negative Setting Time,  $A_V = -10$ ,  $V_{SY} = \pm 15 \text{ V}$

Figure 66. Negative Setting Time,  $A_V = -10$ ,  $V_{SY} = \pm 5 V$

Figure 67. Negative Setting Time,  $A_V = -10$ ,  $V_{SY} = 5$  V

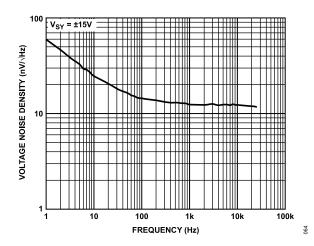

Figure 68. Voltage Noise Density,  $V_{SY} = \pm 15 \text{ V}$

analog.com Rev. F | 23 of 36

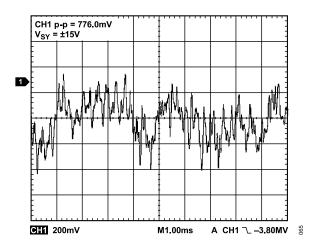

Figure 69. 0.1 Hz to 10 Hz Noise,  $V_{SY} = \pm 15 \text{ V}$ , Gain = 1 Million

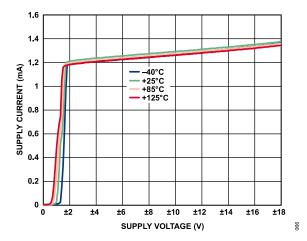

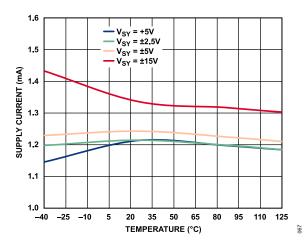

Figure 70. Supply Current ( $I_{SY}$ ) vs. Supply Voltage ( $V_{SY}$ ) for Various Temperatures (ADA4622-2)

Figure 71. Supply Current (I<sub>SY</sub>) vs. Temperature for Various Supply Voltages (ADA4622-2)

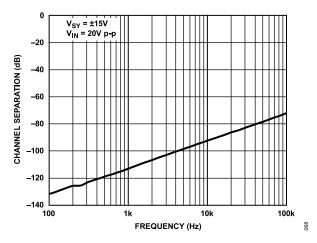

Figure 72. Channel Separation vs. Frequency, V<sub>SY</sub> = ±15 V

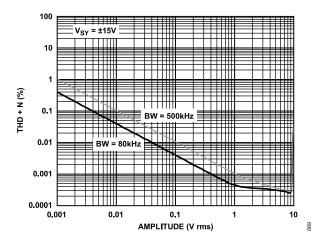

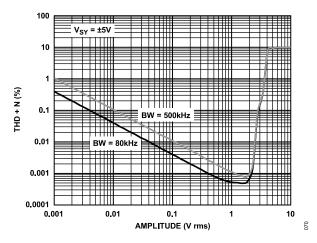

Figure 73. THD + N vs. Amplitude,  $V_{SY} = \pm 15 \text{ V}$

Figure 74. THD + N vs. Amplitude,  $V_{SY} = \pm 5 \text{ V}$

analog.com Rev. F | 24 of 36

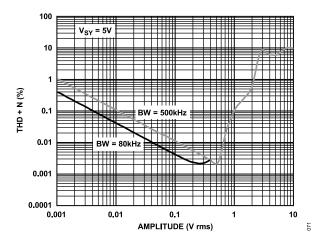

Figure 75. THD + N vs. Amplitude,  $V_{SY} = 5 \text{ V}$

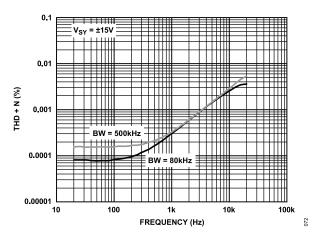

Figure 76. THD + N vs. Frequency,  $V_{SY} = \pm 15 \text{ V}$

Figure 77. THD + N vs. Frequency,  $V_{SY} = \pm 5 \text{ V}$

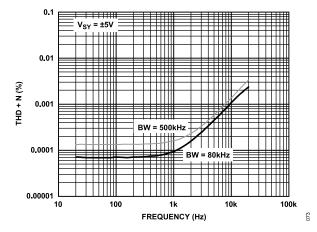

Figure 78. THD + N vs. Frequency,  $V_{SY} = 5 V$

Figure 79. Shutdown Current vs. Temperature

analog.com Rev. F | 25 of 36

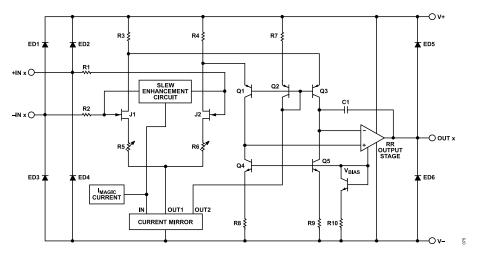

#### THEORY OF OPERATION

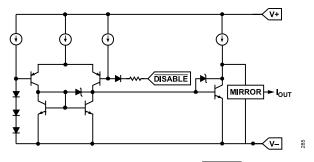

Figure 80. Simplified Circuit Diagram

#### INPUT CHARACTERISTICS

The ADA4622-1/ADA4622-2/ADA4622-4 input stage consists of N-channel JFETs that provide low offset, low noise, and high impedance. The minimum input common-mode voltage extends from -0.2 mV below V- to 1 V less than V+. Driving the input closer to the positive rail causes loss of amplifier bandwidth and increased common-mode voltage error. Figure 81 shows the rounding of the output due to the loss of bandwidth. The input and output are superimposed.

Figure 81. Bandwidth Limiting due to Headroom Requirements

The ADA4622-1/ADA4622-2/ADA4622-4 do not exhibit phase reversal for input voltages up to V+. For input voltages greater than V+, a 10 k $\Omega$  resistor in series with the noninverting input prevents phase reversal at the expense of higher noise (see Figure 82).

Figure 82. No Phase Reversal

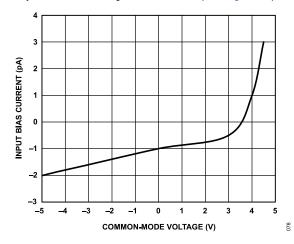

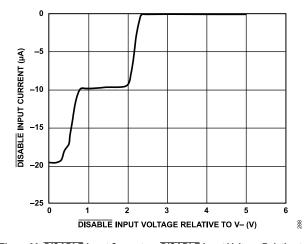

Because the input stage uses N-channel JFETs, the input current during normal operation is negative. However, the input bias current changes direction as the input voltage approaches V+ due to internal junctions becoming forward-biased (see Figure 83).

Figure 83. Input Bias Current vs. Common-Mode Voltage with ±5 V Supply

analog.com Rev. F | 26 of 36

#### THEORY OF OPERATION

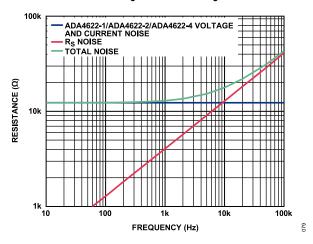

The ADA4622-1/ADA4622-2/ADA4622-4 are designed for 12 nV/ $\sqrt{\text{Hz}}$  wideband input voltage noise density and maintain low noise performance at low frequencies (see Figure 84). This noise performance, along with the low input current as well as low current noise, means that the ADA4622-1/ADA4622-2/ADA4622-4 contribute negligible noise for applications with a source resistance greater than 10 k $\Omega$  and at signal bandwidths greater than 1 kHz.

Figure 84. Total Noise vs. Source Resistance and Frequency

### **Input Overvoltage Protection**

The ADA4622-1/ADA4622-2/ADA4622-4 have internal protective circuitry that allows voltages as high as 0.3 V beyond the supplies applied at the input of either terminal without causing damage. Use a current-limiting resistor in series with the input of the ADA4622-1/ADA4622-2/ADA4622-4 if the input voltage exceeds 0.3 V beyond the supply rails of the amplifiers. If the overvoltage condition persists for more than a few seconds, damage to the amplifiers can result.

For higher input voltages, determine the resistor value by

$$\frac{V_{IN} - V_{SY}}{R_S} \le 10 \text{ mA} \tag{1}$$

where:

$V_{IN}$  is the input voltage.

$V_{SY}$  is the voltage of either the V+ pin or the V- pin.

$R_S$  is the series resistor.

With a very low input bias current of  $\pm 1.5$  nA maximum up to  $125^{\circ}$ C, higher resistor values can be used in series with the inputs without introducing large offset errors. A 1 k $\Omega$  series resistor allows the ADA4622-1/ADA4622-2/ADA4622-4 to withstand 10 V of continuous overvoltage and increases the noise by a negligible amount. A 5 k $\Omega$  resistor protects the inputs from voltages as high as 25 V beyond the supplies and adds less than 10  $\mu$ V to the offset voltage of the amplifiers.

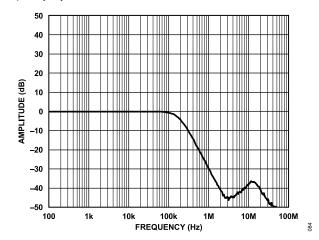

## **EMI Rejection Ratio**

Figure 85 shows the EMI rejection ratio (EMIRR) vs. the frequency for the ADA4622-1/ADA4622-2/ADA4622-4.

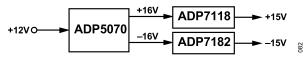

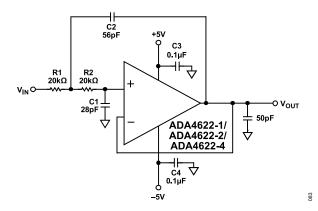

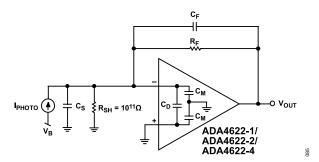

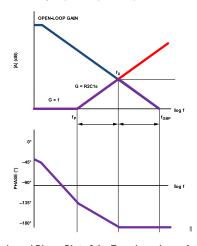

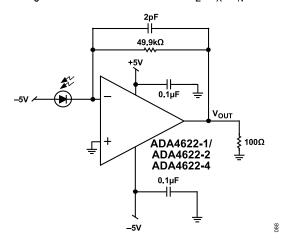

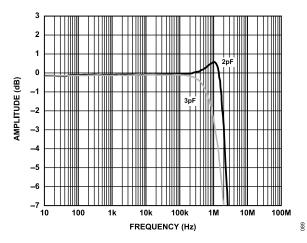

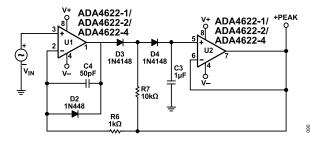

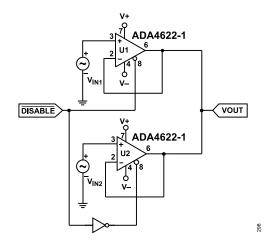

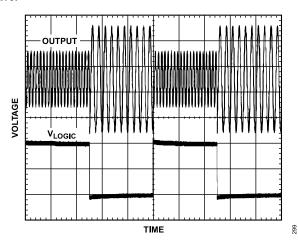

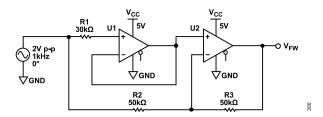

Figure 85. EMIRR vs. Frequency