#### **UNITRODE**

UC1852 UC2852 UC3852

# High Power-Factor Preregulator

### **FEATURES**

- Low-Cost Power Factor Correction

- Power Factor Greater Than 0.99

- Few External Parts Required

- Controlled On-Time Boost PWM

- Zero-Current Switching

- Limited Peak Current

- Min and Max Frequency Limits

- Starting Current Less Than 1mA

- High-Current FET Drive Output

- Under-Voltage Lockout

### **DESCRIPTION**

The UC1852 provides a low-cost solution to active power-factor correction (PFC) for systems that would otherwise draw high peak current pulses from AC power lines. This circuit implements zero-current switched boost conversion, producing sinusoidal input currents with a minimum of external components, while keeping peak current substantially below that of fully-discontinuous converters.

The UC1852 provides controlled switch on-time to regulate the output bulk DC voltage, an off-time defined by the boost inductor, and a zero-current sensing circuit to reactivate the switch cycle. Even though switching frequency varies with both load and instantaneous line voltage, it can be maintained within a reasonable range to minimize noise generation.

While allowing higher peak switch currents than continuous PFCs such as the UC1854, this device offers less external circuitry and smaller inductors, yet better performance and easier line-noise filtering than discontinuous current PFCs with no sacrifice in complexity or cost. The ability to obtain a power factor in excess of 0.99 makes the UC1852 an optimum choice for low-cost applications in the 50 to 500 watt power range. Protection features of these devices include under-voltage lockout, output clamping, peak-current limiting, and maximum-frequency clamping.

The UC1852 family is available in 8-pin plastic and ceramic dual in-line packages, and in the 8-pin small outline IC package (SOIC). The UC1852 is specified for operation from -55°C to +125°C, the UC2852 is specified for operation from -40°C to +85°C, and the UC3852 is specified for operation from 0°C to +70°C.

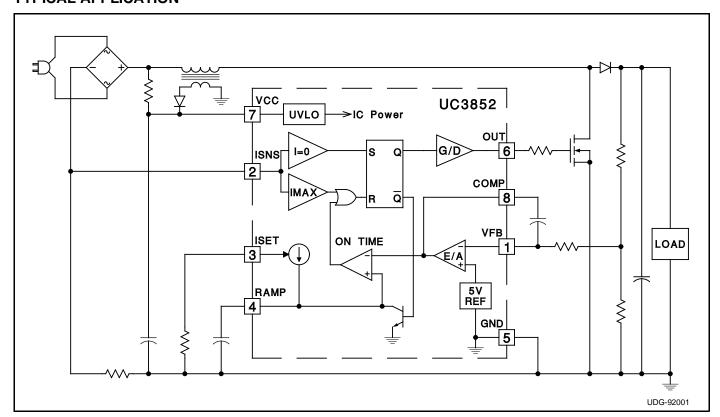

## TYPICAL APPLICATION

UDG-92002

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (Low-impedance Source)30.0V                        |

|-------------------------------------------------------------------|

| Supply Current (High-impedance Source)30.0mA                      |

| OUT Current, Peak±1.0A                                            |

| OUT Energy, Capacitive Load 5.0µJ                                 |

| Input Voltage, ISNS±5.0V                                          |

| Input Voltage, VFB0.3V to +10.0V                                  |

| COMP Current±10.0mA                                               |

| ISET Current10.0mA                                                |

| Power Dissipation at Ta≤25°C (Note 3)1.0W                         |

| Storage Temperature—65°C to +150°C                                |

| Lead Temperature (Soldering, 10 Seconds)+300°C                    |

| Note 1: All voltages with respect to GND (Pin 1).                 |

| Note 2: All currents are positive into the specified terminal.    |

| Note 3: Refers to DIL-8 Package. Consult Packaging Section of     |

| Unitrode Integrated Circuits databook for thermal limitations and |

| considerations of package.                                        |

#### DIL-8 (TOP VIEW) SOIC-8 (TOP VIEW) J or N Package D Package VFB 1 8 СОМР VFB 1 8 СОМР ISNS 2 7 vcc 7 vcc ISNS 2 6 ООТ 6 OUT ISET 3 ISET 3 RAMP 4 5 GND RAMP 4 5 GND

**ELECTRICAL CHARACTERISTICS** Unless otherwise stated, VCC=24V, ISET=50k $\Omega$  to GND, RAMP=1nF to GND, ISNS= -0.1V, VFB connected to COMP, no load on OUT, -55°C<Ta<+125°C for the UC1852, -40°C<Ta<+85°C for the UC2852, and 0°C<Ta<+70°C for the UC3852, and Ta=Tj.

**CONNECTION DIAGRAM**

| PARAMETER                          | TEST CONDITIONS                | MIN.  | TYP.  | MAX.  | UNITS |

|------------------------------------|--------------------------------|-------|-------|-------|-------|

| Timer Section                      |                                | •     |       |       |       |

| ISET Voltage                       |                                | 4.5   | 5.0   | 5.5   | V     |

| RAMP Charge Current                | RAMP=2.5V                      | 88    | 98    | 108   | μΑ    |

| RAMP Discharge Current             | ISNS= -1.0V, RAMP=1.0V         | 12    | 28    | 50    | mA    |

| RAMP Saturation Voltage            | ISNS= -1.0V, IRAMP=100μA       |       | 0.006 | 0.200 | V     |

| RAMP Threshold - Maximum Frequency | VFB=10V, COMP open             | 0.92  | 1.02  | 1.12  | V     |

| RAMP Threshold - PWM Comparator    |                                | 3.9   | 4.3   | 4.8   | V     |

| Current Sense Comparator           |                                |       |       |       |       |

| ISNS Restart Threshold             |                                | -18   | -10   | -4    | mV    |

| ISNS Fault Threshold               |                                | -550  | -450  | -350  | mV    |

| ISNS Input Current                 |                                | -100  | -30   | 100   | μΑ    |

| Error Amplifier Section            |                                |       |       |       |       |

| VFB Input Voltage                  |                                | 4.6   | 5.0   | 5.3   | V     |

| VFB Input Bias Current             |                                | -5.00 | -0.03 | 5.00  | μΑ    |

| COMP Sink Current                  | COMP=7.5V                      | 10    |       |       | mA    |

| COMP Source Current                | COMP=2.5V                      | -300  | -175  | -100  | μΑ    |

| COMP Clamp Voltage                 | VFB=0.0V, COMP open            | 9.2   | 10.0  | 10.6  | V     |

| OUT Output                         |                                |       |       |       |       |

| OUT Saturation Voltage High        | VCC=13V, lout= -200mA, RAMP=2V | 0.5   | 1.7   | 2.5   | V     |

| OUT Saturation Voltage Low         | Io∪T=200mA, ISNS= −1.0V        | 0.5   | 1.6   | 2.2   | V     |

| OUT Saturation Voltage Low @ 10mA  | IOUT=10mA, ISNS=-1.0V          |       | 0.05  | 0.40  | V     |

| OUT Clamp Voltage                  | IOUT= -200mA, RAMP=2V          | 10.0  | 12.0  | 14.5  | V     |

| OUT Voltage during UVLO            | IOUT=100mA, VCC=0V             | 0.5   | 1.0   | 2.2   | V     |

| Overall Section                    | ,                              |       |       |       |       |

| Inactive Supply Current            | VCC=10V                        | 0.2   | 0.4   | 1.0   | mA    |

| Active Supply Current              |                                | 3.0   | 6.0   | 10.0  | mA    |

| VCC Clamp Voltage                  | ICC=25mA                       | 30    | 33    | 36    | V     |

| VCC Turn-On Threshold              |                                | 14.5  | 16.3  | 17.5  | V     |

| VCC Turn-Off Threshold             |                                | 10.5  | 11.5  | 13.0  | V     |

| VCC Threshold Hysteresis           |                                | 3     | 5     | 7     | V     |

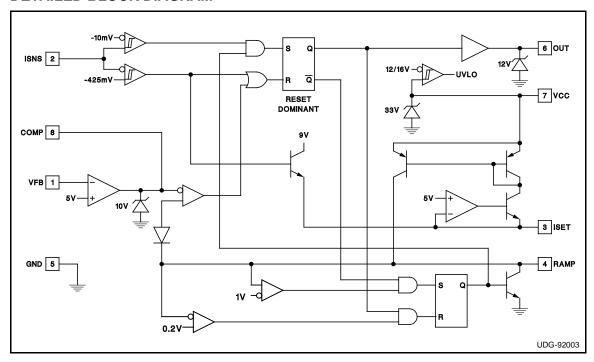

#### **DETAILED BLOCK DIAGRAM**

#### PIN DESCRIPTIONS

**COMP**: COMP is the output of the error amplifier and the input of the PWM comparator. To limit PWM on-time, this pin is clamped to approximately 10V. To implement soft start, the COMP pin can be pulled low and ramped up with a PNP transistor, a capacitor, and a resistor.

**GND**: Ground for all functions is through this pin.

**ISET**: The dominant function is of this pin is to program RAMP charging current. RAMP charging current is approximately 5V divided by the external resistor placed from ISET to ground. Resistors in the range of  $10k\Omega$  to  $50k\Omega$  are recommended, producing currents in the range of  $100\mu\text{A}$  to  $500\mu\text{A}$ .

A second function of ISET is as reference output. The ISET pin is normally regulated to  $5V \pm 10\%$ . It is critical that this pin only see the loading of the RAMP programming resistor, but a high input-impedance comparator or amplifier may be connected to this pin or to a tap on the RAMP programming resistor if required.

The third function of the ISET pin is as a FAULT output. In the event of an over-current fault, the ISET pin is forced to approximately 9V by the fault comparator. This can be used to trip an external protection circuit which can disable the load or start a fault restart cycle.

**ISNS**: This input to the zero and over current comparators is specially built to allow operation over a ±5V dynamic range. In noisy systems or systems with very high Q inductors, it is desirable to filter the signal entering the ISNS input to prevent premature restart or fault cycles. For best

accuracy, ISNS should be connected to a current sense resistor through no more than 200 ohms.

**OUT**: The output of a high-current power driver capable of driving the gate of a power MOSFET with peak currents exceeding ±500mA. To prevent damage to the power MOSFET, the OUT pin is internally driven by a 12V supply. However, lead inductance between the OUT pin and the load can cause overshoot and ringing. External current boost transistors will increase this overshoot and ringing. If there is any significant distance between the IC and the MOSFET, external clamp diodes and/or series damping resistors may be required. OUT is actively held low when the VCC is below the UVLO threshold.

**RAMP**: A controlled on-time PWM requires a timer whose time can be modulated by an external voltage. The timer current is programmed by a resistor from ISET to GND. A capacitor from RAMP to GND sets the on time in conjunction with the voltage on COMP. Recommended values for the timer capacitors are between 100pF and 1nF.

**VCC**: VCC is the logic and control power connection for this device. VCC current is the sum of active device supply current and the average OUT current. Knowing the maximum operating frequency and the MOSFET gate charge (Qg), average OUT current can be estimated by:

$$I_{OUT} = Q_q \times F$$

To prevent noise problems, bypass VCC to GND with both a ceramic and an electrolytic capacitor.

**VFB**: VFB is the error amplifier inverting input. This input serves as both the voltage sense input to the error amplifier

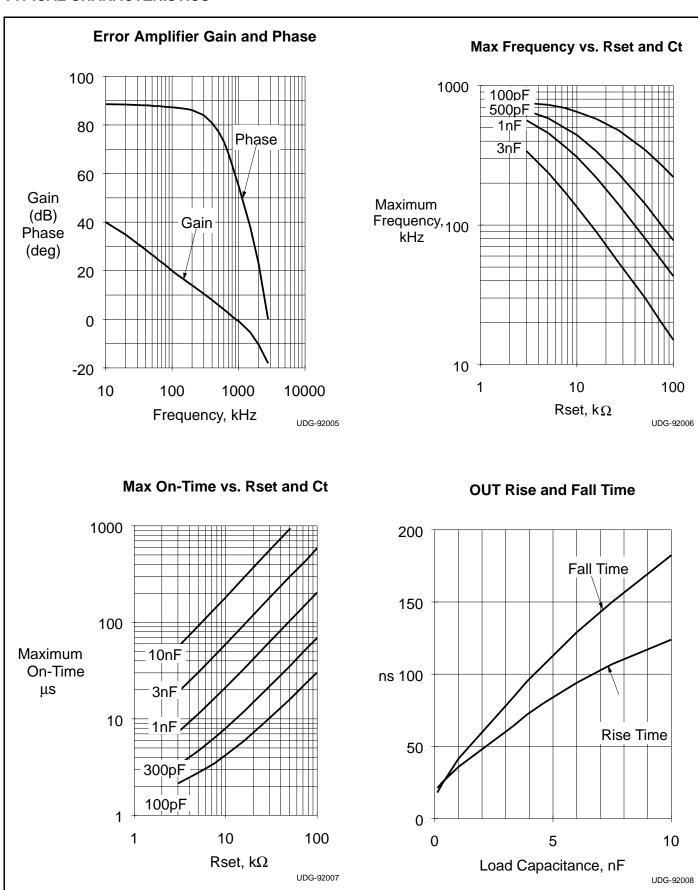

# TYPICAL CHARACTERISTICS

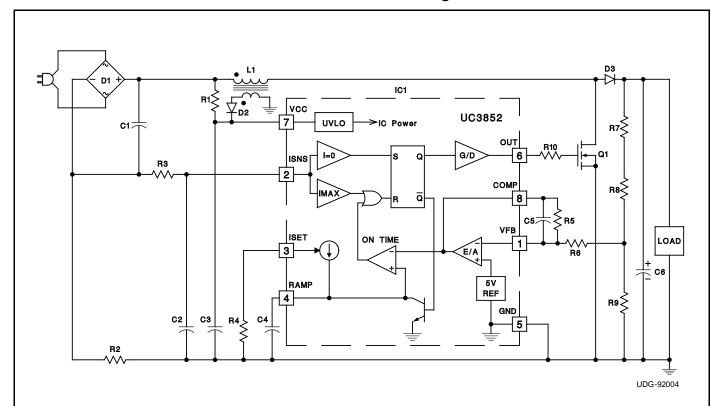

This circuit demonstrates a complete power factor preregulator based on the UC3852. This preregulator will supply up to 100 watts at 400VDC and exhibit power factor greater than 0.995 with less than 10% total harmonic distortion. Operating input range is 90V to 160V RMS at 50Hz to 60Hz.

This design is intentionally simple, yet fully functional. The UC3852 can also be used in designs featuring soft start, over-voltage protection, wide power-line voltage operation, and fault latching. For more information on applying the UC3852, refer to Unitrode Application Note U–132.

#### **PARTS LIST**

| C1  | 0.47μF/250VAC X2 Class Polyester                       | Q1 | IRF830 4.5A/500V 1.5 $\Omega$ Power FET         |

|-----|--------------------------------------------------------|----|-------------------------------------------------|

| C2  | 1nF/16V Ceramic                                        | L1 | 680μH (Renco RL3792 with                        |

| C3  | 68μF/35V Aluminum Electrolytic                         |    | 10 Turn 24 AWG Secondary)                       |

| C4  | 180pF/16V Ceramic                                      | R1 | 150kΩ, ½W                                       |

| C5  | 0.1μF/16V Polyester or Ceramic                         | R2 | $0.2\Omega$ , $\frac{1}{2}W$ Carbon Composition |

| C6  | 82μF/450V Aluminum Electrolytic                        | R3 | 10Ω, ½W                                         |

| D1  | 2A/500V Bridge Rectifier (Collmer                      | R4 | 13.3kΩ, ½W                                      |

|     | KBPC106 or Powertex MB11A02V60)                        | R5 | 1MΩ, ½W                                         |

| D2  | 100mA/50V Switching Diode (1N4148)                     | R6 | 20kΩ, ½W                                        |

| D3  | 2A/500V 250ns Recovery-Time Rectifier (Motorola MR856) | R7 | 200kΩ, ½W                                       |

| IC1 | UC3852N Power Factor Controller IC                     | R8 | 200kΩ, ½W                                       |

www.ti.com 13-Aug-2021

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| UC2852D          | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | UC2852D              | Samples |

| UC2852DTR        | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | UC2852D              | Samples |

| UC2852N          | ACTIVE | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type  | -40 to 85    | UC2852N              | Samples |

| UC3852D          | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3852D              | Samples |

| UC3852DTR        | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | 0 to 70      | UC3852D              | Samples |

| UC3852N          | ACTIVE | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type  | 0 to 70      | UC3852N              | Samples |

| UC3852NG4        | ACTIVE | PDIP         | Р                  | 8    | 50             | RoHS & Green | NIPDAU                        | N / A for Pkg Type  | 0 to 70      | UC3852N              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 13-Aug-2021

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 18-Nov-2020

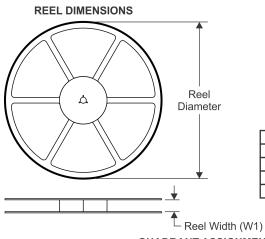

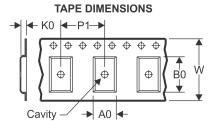

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

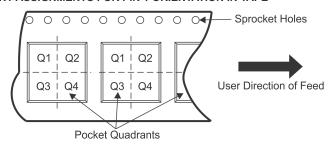

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| 7 til diritoriolorio aro mominar |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----------------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                           | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| UC2852DTR                        | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| UC3852DTR                        | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 18-Nov-2020

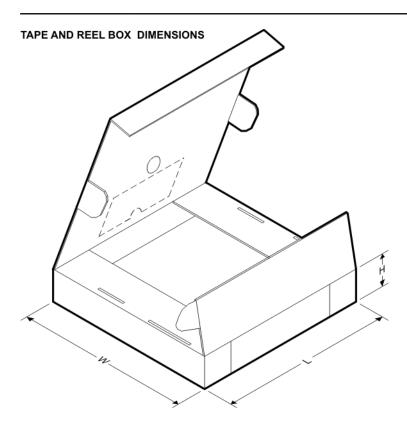

#### \*All dimensions are nominal

| Device    | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2852DTR | SOIC         | D               | 8    | 2500 | 853.0       | 449.0      | 35.0        |

| UC3852DTR | SOIC         | D               | 8    | 2500 | 853.0       | 449.0      | 35.0        |

# **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated