### **ZSSC3123**

cLite<sup>™</sup> Capacitive Sensor Signal Conditioner

### **Description**

The ZSSC3123 is a CMOS integrated circuit for accurate capacitance-to-digital conversion and sensor-specific correction of capacitive sensor signals. Digital compensation of sensor offset, sensitivity, and temperature drift is accomplished via an internal digital signal processor running a correction algorithm with calibration coefficients stored in a non-volatile EEPROM.

The ZSSC3123 is configurable for capacitive sensors with capacitances up to 260pF and a sensitivity of 125aF/LSB to 1pF/LSB depending on resolution, speed, and range settings. It is compatible with both single capacitive sensors (both terminals must be accessible) and differential capacitive sensors. Measured and corrected sensor values can be output as I2C, SPI, pulse density modulation (PDM), or alarms.

The I2C interface can be used for a simple PC-controlled calibration procedure to program a set of calibration coefficients into an on-chip EEPROM. The calibrated ZSSC3123 and a specific sensor are mated digitally: fast, precise, and without the cost overhead of trimming by external devices or laser.

# **Available Support**

- ZSSC3123 SSC Evaluation Kit available: SSC Evaluation Board, samples, software, documentation.

- Support for industrial mass calibration available.

- Quick circuit customization option for large production volumes.

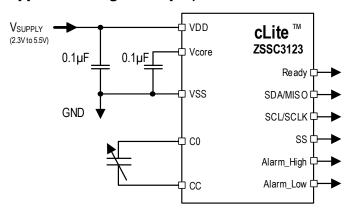

#### **Application: Digital Output, Alarms**

### **Features**

- Maximum target input capacitance: 260pF

- Sampling rates as fast as 0.7ms at 8-bit resolution; 1.6ms at 10-bit; 5.0ms at 12-bit; 18.5ms at 14-bit

- Digital compensation of sensor: piece-wise 1st and 2nd order sensor compensation or up to 3rd order single-region sensor compensation

- Digital compensation of 1st and 2nd order temperature gain and offset drift

- Internal temperature compensation reference (no external components)

- Programmable capacitance span and offset

- Layout customized for die-die bonding with sensor for lowcost, high-density chip-on-board assembly

- Accuracy as high as ±0.25% FSO at -40°C to 125°C, 3V, 5V, Vsupply ±10% (see data sheet section 5 for restrictions)

- Minimized calibration costs: no laser trimming, one-pass calibration using a digital interface

- Wide capacitance range to support a broad portfolio of different sensor elements

- Excellent for low-power battery applications

- I2C or SPI interface—easy connection to a microcontroller

- PDM outputs (Filtered Analog Ratiometric) for both capacitance and temperature

- Up to two alarms that can act as full push-pull or open-drain switches

- Supply voltage: 2.3V to 5.5V

- Typical current consumption 750μA down to 60μA depending on configuration

- Typical Sleep Mode current: ≤ 1µA at 85°C

- Operation temperature: –40°C to +125°C depending on part code

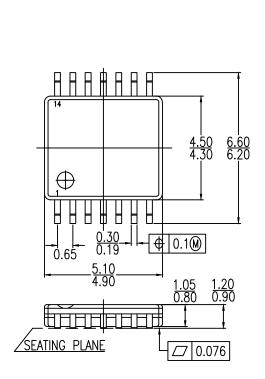

- Die or 4.4 × 5.0 mm 14-TSSOP package

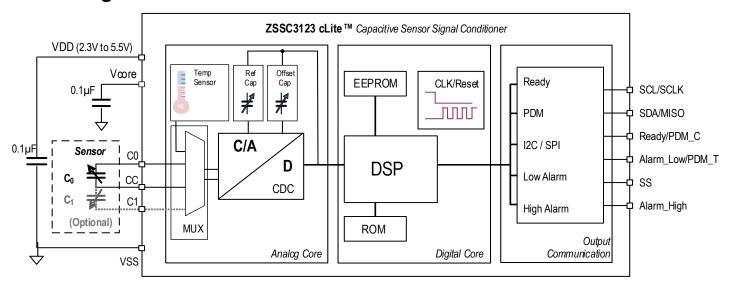

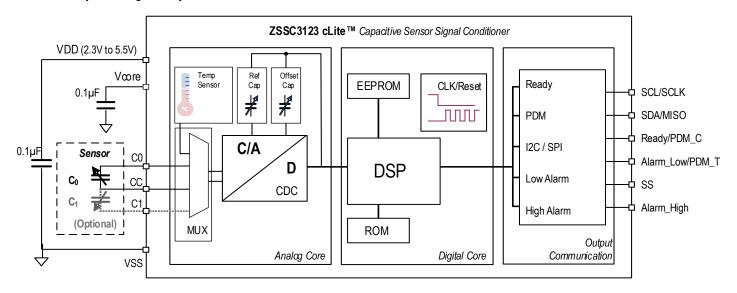

### **Block Diagram**

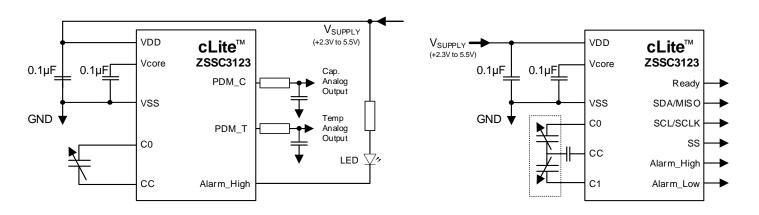

### **Application: Analog Output**

### **Application: Differential Capacitance Input**

# **Contents**

| 1.  | Pin <i>F</i>             | Assignme                | ents                                  | 7  |  |  |

|-----|--------------------------|-------------------------|---------------------------------------|----|--|--|

| 2.  | Pin [                    | Descriptio              | ons                                   | 7  |  |  |

| 3.  | Absolute Maximum Ratings |                         |                                       |    |  |  |

| 4.  | Reco                     | ommende                 | ed Operating Conditions               | 9  |  |  |

| 5.  | Elec                     | trical Cha              | aracteristics                         | 10 |  |  |

| 6.  | Curr                     | ent Consi               | umption Graphs                        | 12 |  |  |

|     | 6.1                      | Update                  | Mode Current Consumption              | 12 |  |  |

|     | 6.2                      | Sleep M                 | lode Current Consumption              | 13 |  |  |

| 7.  | Outp                     | out Pad D               | rive Strength                         | 14 |  |  |

| 8.  | Tem                      | perature                | Sensor Nonlinearity                   | 15 |  |  |

| 9.  | Circu                    | uit Descri <sub>l</sub> | ption                                 | 16 |  |  |

|     | 9.1                      | Signal F                | Flow and Block Diagram                | 16 |  |  |

|     | 9.2                      | Analog I                | Front End                             | 16 |  |  |

|     |                          | 9.2.1                   | Capacitance-to-Digital Converter      | 16 |  |  |

|     |                          | 9.2.2                   | Temperature Measurement               | 20 |  |  |

|     | 9.3                      | Digital C               | Core                                  | 21 |  |  |

| 10. | Norn                     | nal Opera               | ation Mode                            | 22 |  |  |

|     | 10.1                     | Power-C                 | On Sequence                           | 23 |  |  |

|     | 10.2                     | Measure                 | ement Cycle                           | 23 |  |  |

|     | 10.3                     | Measure                 | ement Modes                           | 24 |  |  |

|     |                          | 10.3.1                  | Update Mode                           | 24 |  |  |

|     |                          | 10.3.2                  | Sleep Mode                            | 27 |  |  |

|     | 10.4                     | Status a                | and Diagnostics                       | 29 |  |  |

|     |                          | 10.4.1                  | EEPROM Error Detection and Correction | 30 |  |  |

|     |                          | 10.4.2                  | Alarm Diagnostics                     | 30 |  |  |

|     | 10.5                     | Output N                | Modes                                 | 31 |  |  |

|     | 10.6                     | I2C and                 | SPI                                   | 31 |  |  |

|     |                          | 10.6.1                  | I2C Features and Timing               | 31 |  |  |

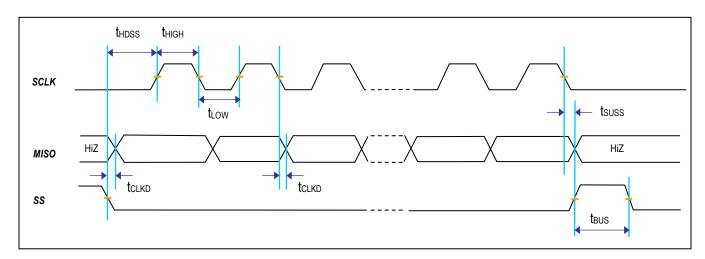

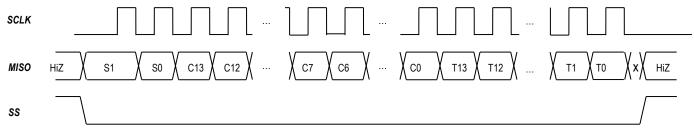

|     |                          | 10.6.2                  | SPI Features and Timing               | 32 |  |  |

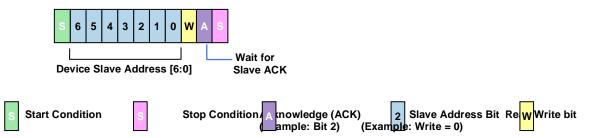

|     |                          | 10.6.3                  | I2C and SPI Commands                  | 33 |  |  |

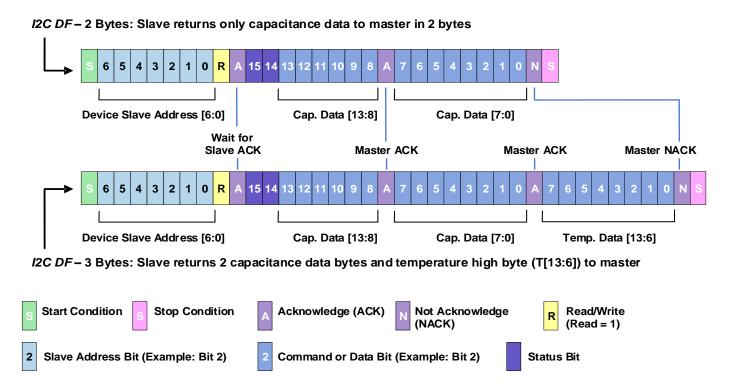

|     |                          | 10.6.4                  | Data Fetch (DF)                       | 33 |  |  |

|     |                          | 10.6.5                  | Measurement Request (MR)              | 35 |  |  |

|     |                          | 10.6.6                  | Ready Pin                             | 36 |  |  |

|     | 10.7                     | Pulse D                 | ensity Modulation (PDM)               | 37 |  |  |

|     | 10.8                     | Alarm O                 | Output                                | 37 |  |  |

|     |                          | 10.8.1                  | Alarm Registers                       | 38 |  |  |

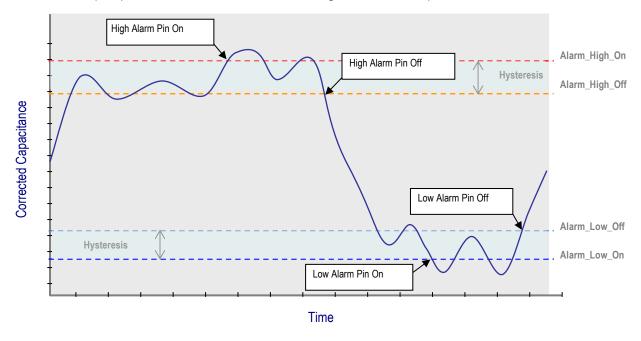

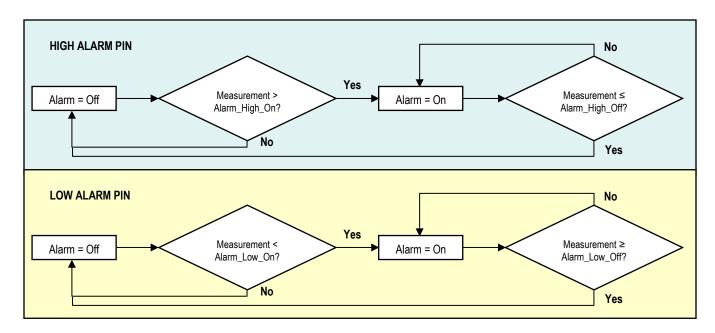

|     |                          | 10.8.2                  | Alarm Operation                       | 38 |  |  |

|     |                          | 10.8.3                  | Alarm Output Configuration            | 39 |  |  |

|     |                          | 10.8.4                  | Alarm Polarity                        | 39 |  |  |

|     |                          |                         |                                       |    |  |  |

| 11. | Con   | nmand Mode                                                                              | 40 |

|-----|-------|-----------------------------------------------------------------------------------------|----|

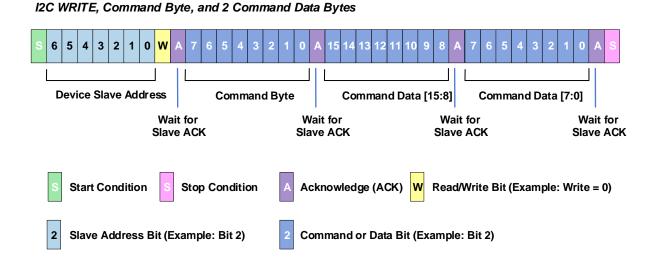

|     | 11.1  | Command Format                                                                          | 40 |

|     | 11.2  | 2 Command Encodings                                                                     | 41 |

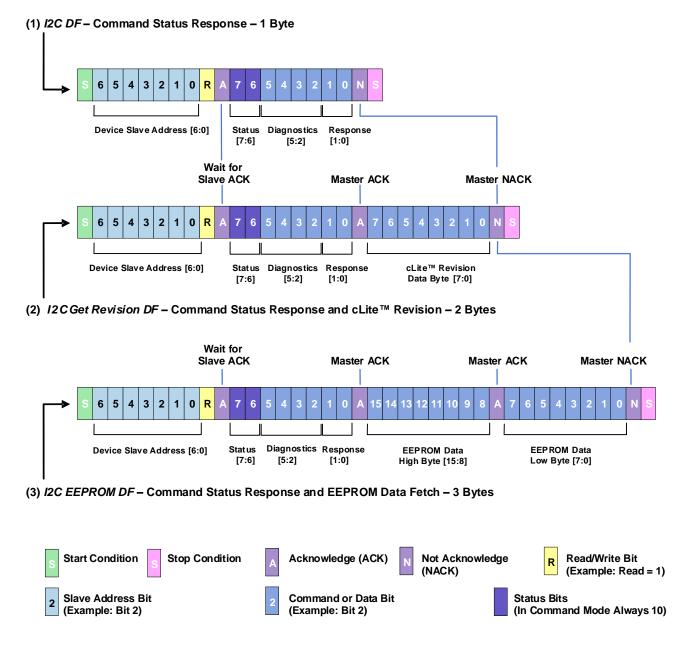

|     | 11.3  | 3 Command Response and Data Fetch                                                       | 41 |

| 12. | EEF   | 44                                                                                      |    |

|     | 12.1  | Renesas Configuration Register (ZMDI_Config, EEPROM Word 02HEX)                         | 46 |

|     | 12.2  | 2 Capacitance Analog Front-End Configuration (C_Config, EEPROM Word 06HEX)              | 46 |

|     | 12.3  | B Temperature Analog Front End Configuration (T_Config, EEPROM Word 11 <sub>HEX</sub> ) | 47 |

|     | 12.4  | Customer Configuration Register (Cust_Config, EEPROM Word 1CHEX)                        | 48 |

| 13. | Cali  | bration and Signal Conditioning Math                                                    | 49 |

|     | 13.1  | Capacitance Signal Conditioning                                                         | 49 |

|     | 13.2  | 2 Temperature Signal Compensation                                                       | 50 |

|     | 13.3  | B Limits on Coefficient Ranges                                                          | 50 |

| 14. | App   | lication Circuit Examples                                                               | 51 |

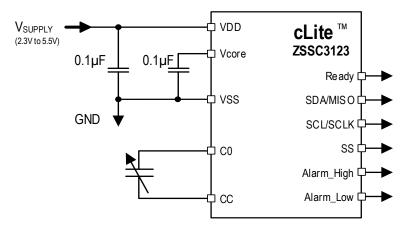

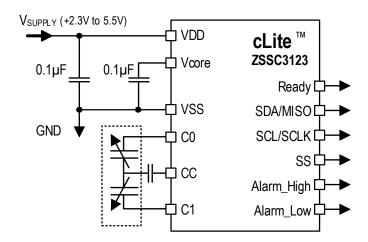

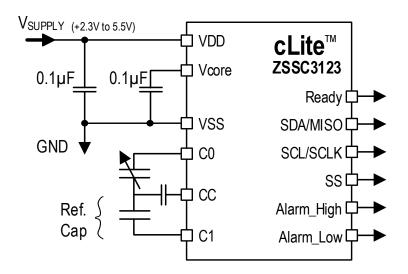

|     | 14.1  | Digital Output with Optional Alarms                                                     | 51 |

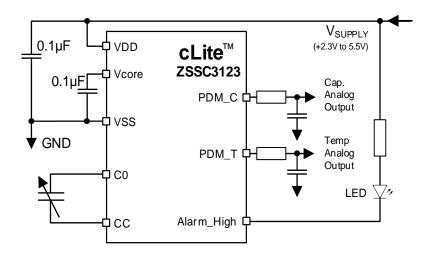

|     | 14.2  | 2 Analog Output with Optional Alarms                                                    | 52 |

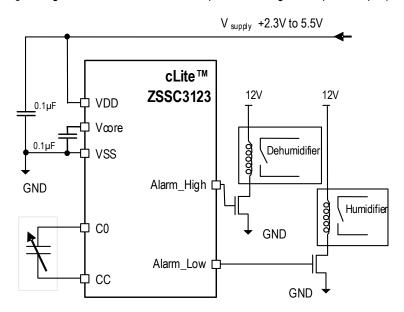

|     | 14.3  | Bang-Bang Control System                                                                | 53 |

|     | 14.4  | Differential Input Capacitance                                                          | 54 |

|     | 14.5  | 5 External Reference Capacitor                                                          | 55 |

| 15. | ESE   | D/Latch-Up-Protection                                                                   | 55 |

| 16. | Test  | t                                                                                       | 56 |

| 17. | Reli  | ability                                                                                 | 56 |

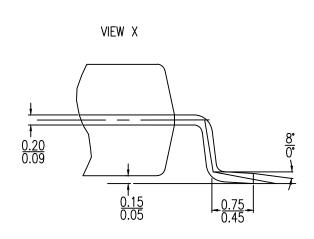

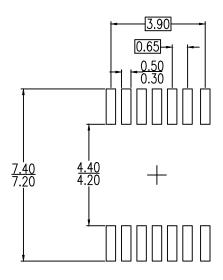

| 18. | Pac   | kage Outline Drawings                                                                   | 56 |

| 19. | Exa   | mple Marking Diagram for TSSOP14 Parts                                                  | 56 |

| 20. | Stor  | age and Soldering Conditions                                                            | 56 |

| 21. | Glos  | ssary                                                                                   | 57 |

| 22. | Orde  | ering Information                                                                       | 57 |

| 23. | Rev   | ision History                                                                           | 58 |

|     |       |                                                                                         |    |

| Lis | st c  | of Figures                                                                              |    |

|     |       | Pin Assignments for 4.4mm × 5.0mm 14-TSSOP – Top View                                   | 7  |

|     | re 2. | Best Case Settings (Typical Part)                                                       |    |

| •   | re 3. |                                                                                         |    |

| _   | re 4. | ,                                                                                       |    |

| •   | re 5. | Output High Drive Strength Graph                                                        |    |

| •   | re 6. | Output Low Drive Strength Graph                                                         |    |

| _   | re 7. | First Order Fit (Typical Part)                                                          |    |

| _   |       | Second Order Fit (Typical Part)                                                         |    |

| -   |       | ZSSC3123 Block Diagram                                                                  |    |

| 5.5 |       | •                                                                                       |    |

### **ZSSC3123 Datasheet**

| Figure 10  | General Operation                                                                                                | 22 |

|------------|------------------------------------------------------------------------------------------------------------------|----|

| •          | Power-On Sequence with Fast Startup Bit Set in EEPROM                                                            |    |

| _          | Measurement Cycle Timing                                                                                         |    |

| •          | Measurement Sequence in Update Mode                                                                              |    |

| _          | I2C and SPI Data Fetching in Update Mode                                                                         |    |

| •          | Measurement Sequence in Sleep Mode (Only I2C, SPI, or Alarms)                                                    |    |

| _          | I2C and SPI Data Fetching in Sleep Mode                                                                          |    |

| •          | I2C Timing Diagram                                                                                               |    |

| •          | SPI Timing Diagram                                                                                               |    |

| •          | I2C Measurement Packet Reads                                                                                     |    |

| •          | SPI Output Packet with Positive Edge Sampling                                                                    |    |

| -          | 12C MR                                                                                                           |    |

| •          | SPI MR                                                                                                           |    |

| •          | Example of Alarm Function                                                                                        |    |

| •          | Alarm Output Flow Chart                                                                                          |    |

| •          | I2C Command Format                                                                                               |    |

| •          | Command Mode Data Fetch                                                                                          |    |

| •          | Digital Output with Optional Alarms Example                                                                      |    |

| _          | Analog Output with Optional Alarms Example                                                                       |    |

| •          | Bang-Bang Control System Example                                                                                 |    |

| •          | Differential Input Capacitance Example                                                                           |    |

| Figure 31. | External Reference Input Capacitance Example                                                                     | 55 |

|            |                                                                                                                  |    |

| List o     | f Tables                                                                                                         |    |

| Table 1.   | Pin Descriptions                                                                                                 | 7  |

| Table 2.   | Absolute Maximum Ratings                                                                                         | 8  |

| Table 3.   | Recommend Operating Conditions                                                                                   | 9  |

| Table 4.   | Electrical Characteristics                                                                                       |    |

| Table 5.   | CDC Multiplier                                                                                                   | 18 |

| Table 6.   | Mult 1: Sensor Capacitors Ranging from 2pF to 10pF (Full Scale Values)                                           | 19 |

| Table 7.   | Mult 2: Sensor Capacitors Ranging from 8pF to 32pF (Full Scale Values)                                           | 19 |

| Table 8.   | Mult 4: Sensor Capacitors Ranging from 32pF to 130pF (Full Scale Values)                                         | 20 |

| Table 9.   | Mult 8: Sensor Capacitors Ranging from 130pF to 260pF (Full Scale Values)                                        | 20 |

| Table 10.  | CDC Resolution and Conversion Times                                                                              | 24 |

| Table 11.  | Update Rate Settings (Power_Down_Period Bit Field in ZMDI_Config)                                                | 25 |

| Table 12.  | Time Periods between Capacitance and Temperature Measurements for Mult1, Different Resolutions, and Update Rates | 25 |

| Table 13.  | Time Periods between Capacitance and Temperature Measurements for Mult2, Different Resolutions, and Update Rates | 26 |

| Table 14.  | Time Periods between Capacitance and Temperature Measurements for Mult4, Different Resolutions, and Update Rates | 26 |

| Table 15.  | Time Periods between Capacitance and Temperature Measurements for Mult8, Different Resolutions, and Update Rates | 26 |

### **ZSSC3123 Datasheet**

| Table 16. | Status Bit Definitions                      | 29 |

|-----------|---------------------------------------------|----|

| Table 17. | Diagnostic Detection                        | 30 |

| Table 18. | Normal Operation Diagnostic Table           | 30 |

| Table 19. | Output Modes                                | 31 |

| Table 20. | Pin Assignment for Output Selections        | 31 |

| Table 21. | I2C Parameters                              | 32 |

| Table 22. | SPI Parameters                              | 33 |

| Table 23. | I2C and SPI Command Types                   | 33 |

| Table 24. | Low Pass Filter Example for R = $10k\Omega$ | 37 |

| Table 25. | Command List and Encodings                  | 41 |

| Table 26. | Response Bits                               | 42 |

| Table 27. | Command Diagnostic Bits                     | 42 |

| Table 28. | EEPROM Word Assignments                     | 44 |

| Table 29. | ZMDI_Config Bit Assignments                 | 46 |

| Table 30. | C_Config Bit Assignments                    | 46 |

| Table 31. | T_Config Bit Assignments                    | 47 |

| Table 32. | Cust_Config Bit Assignments                 | 48 |

| Table 33. | Limits on Coefficient Ranges                | 50 |

| Table 34. | Example 1: Configuration Settings           | 51 |

| Table 35. | Example 2: Configuration Settings           | 52 |

| Table 36. | Example 3: Configuration Settings           | 53 |

| Table 37. | Example 4: Configuration Settings           | 54 |

| Table 38. | Example 5: Configuration Settings           | 55 |

| Table 39. | Storage and Soldering Condition – TSSOP14   | 56 |

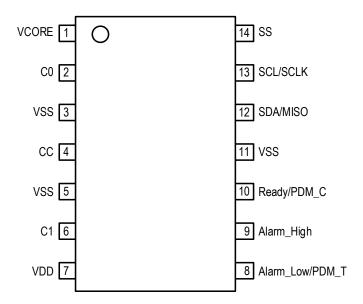

# 1. Pin Assignments

Figure 1. Pin Assignments for 4.4mm imes 5.0mm 14-TSSOP – Top View

# 2. Pin Descriptions

**Table 1. Pin Descriptions**

| Pin | Name            | Description                                                              | Notes                                                                                                                                                                                                                     |  |

|-----|-----------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | VCORE           | Core voltage                                                             | Always connect the VCORE pin to an external capacitor to ground that is within the specifications given in section 4 for Cvcore_sm and Cvcore_um. This is the only internal module pin.  For ESD details, see section 15. |  |

| 2   | C0              | Capacitor input 0                                                        |                                                                                                                                                                                                                           |  |

| 3   | VSS             | Ground supply                                                            |                                                                                                                                                                                                                           |  |

| 4   | CC              | Common capacitor input                                                   |                                                                                                                                                                                                                           |  |

| 5   | VSS             | Ground supply                                                            | Connecting to GND for shielding is strongly recommended.                                                                                                                                                                  |  |

| 6   | C1              | Capacitor input 1                                                        | If not used, must be unconnected.                                                                                                                                                                                         |  |

| 7   | VDD             | Supply voltage (1.8V to 5.5V)<br>2.3V to 5.5V for ZSSC3123               | VDD must be connected to V <sub>SUPPLY</sub> . See section 4.                                                                                                                                                             |  |

| 8   | Alarm_Low/PDM_T | Low alarm output Temperature PDM (see Table 20)                          | If not used, must be unconnected.                                                                                                                                                                                         |  |

| 9   | Alarm_High      | High alarm output                                                        | If not used, must be unconnected.                                                                                                                                                                                         |  |

| 10  | Ready/PDM_C     | Ready signal (conversion complete output) Capacitance PDM (see Table 20) | If not used, must be unconnected.                                                                                                                                                                                         |  |

| Pin | Name     | Description                                                               | Notes                             |

|-----|----------|---------------------------------------------------------------------------|-----------------------------------|

| 11  | VSS      | Ground supply                                                             | Must connect to GND.              |

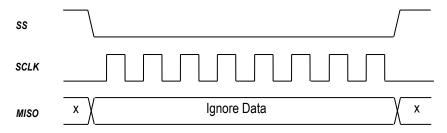

| 12  | SDA/MISO | I2C data if in I2C Mode Master-In-Slave-Out if in SPI Mode (see Table 20) | If not used, must connect to VDD. |

| 13  | SCL/SCLK | I2C clock if in I2C Mode<br>Serial clock if in SPI Mode (see Table 20)    | If not used, must connect to VDD. |

| 14  | SS       | Slave Select (input) if in SPI Mode (see Table 20)                        | If not used, must be unconnected. |

# 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed in Table 2 can cause permanent damage to the device. Functional operation of the device at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 2. Absolute Maximum Ratings**

| Symbol            | Parameter                        | Minimum | Typical | Maximum              | Units |

|-------------------|----------------------------------|---------|---------|----------------------|-------|

| V <sub>DD</sub>   | Analog Supply Voltage            | -0.3    |         | 6.0                  | V     |

| VINA              | Voltages at Analog I/O – In Pin  | -0.3    |         | V <sub>DD</sub> +0.3 | V     |

| V <sub>OUTA</sub> | Voltages at Analog I/O – Out Pin | -0.3    |         | V <sub>DD</sub> +0.3 | V     |

| Tstor             | Storage Temperature Range        | -55     |         | 150                  | °C    |

# 4. Recommended Operating Conditions

**Table 3. Recommend Operating Conditions**

| Symbol               | Parameter                                                                      | Minimum | Typical | Maximum | Units |

|----------------------|--------------------------------------------------------------------------------|---------|---------|---------|-------|

| VSUPPLY              | Supply Voltage to Ground                                                       | 2.3     |         | 5.5     | V     |

| Тамв                 | Ambient Temperature Range <sup>[a]</sup>                                       | -40     |         | 125     | °C    |

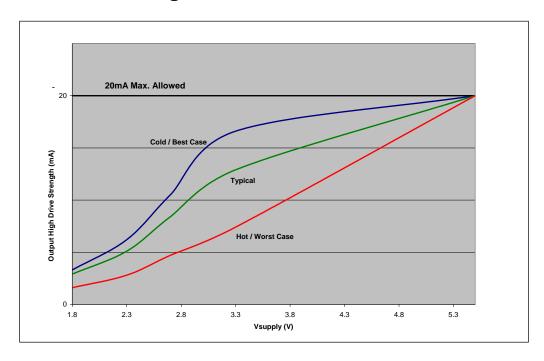

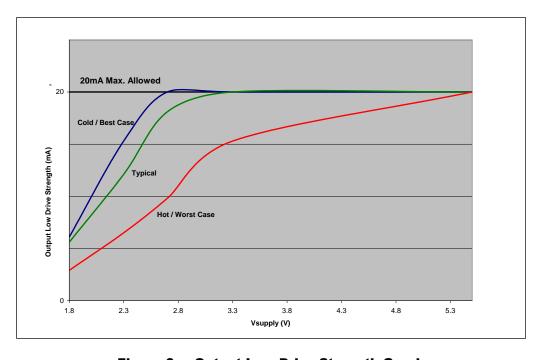

| l <sub>out</sub>     | Output Pads/Pins Drive Strength <sup>[b]</sup>                                 | 1.5     |         | 20      | mA    |

| C <sub>VSUPPLY</sub> | External Capacitance between V <sub>DD</sub> pin and Ground                    | 100     | 220     | 470     | nF    |

| CVCORE_SM            | External Capacitance between Vcore and Ground – Sleep Mode                     | 10      |         | 110     | nF    |

| Cvcore_um            | External Capacitance between Vcore and Ground – Update Mode                    | 90      |         | 330     | nF    |

| C <sub>0</sub>       | Input Capacitance Span (Full Scale Values)                                     | 2       |         | 260     | pF    |

| C <sub>1</sub>       | External Reference Capacitance                                                 | 2       |         | 260     | pF    |

| Ccc                  | External Isolating Capacitance (Mult1) (CC pin to sensor common node) [c], [d] |         |         | 16      | pF    |

| R <sub>PU</sub>      | I2C Pull-up Resistor                                                           | 1       | 2.2     |         | kΩ    |

| C <sub>SDA</sub>     | SDA/MISO Load Capacitance                                                      |         |         | 200     | pF    |

<sup>[</sup>a]Caution: If buying die, select the proper package to ensure that the maximum junction temperature is not exceeded.

<sup>[</sup>b]See section 7 for full details on output pad drive strengths.

<sup>[</sup>c]An external isolating capacitor allows a non-galvanic connection to special differential or external reference sensor types. Ccc could also be used to lower the overall capacitance level to a value that is supported by the ZSSC3123 because it limits the maximum capacitance seen by the ZSSC3123 input to CC even if C0 and C1 have higher values. See section 9.2.1.3 for more details.

<sup>[</sup>d]The series combination of sensor and CC must not exceed the maximum capacitance allowed for the chosen Mult setting.

# 5. Electrical Characteristics

**Table 4. Electrical Characteristics**

| Symbol                 | Parameter                                                         | Conditions                                                | Minimum | Typical             | Maximum | Units                |

|------------------------|-------------------------------------------------------------------|-----------------------------------------------------------|---------|---------------------|---------|----------------------|

| Supply Curre           | nt                                                                |                                                           |         |                     |         |                      |

| I <sub>DD</sub>        | Update Mode Current (varies with                                  | Best case settings: [b] Mult 1, 8-bit, 125ms Power Down   |         | 60                  | 100     |                      |

| טטו                    | part configuration) [a]                                           | Worst case settings:<br>Mult 1, 14-bit, 0ms Power Down    |         | 750                 | 1100    | μA                   |

| I <sub>PDM</sub>       | Extra Current with PDM enabled [b]                                |                                                           |         | 150                 |         | μΑ                   |

| I <sub>SLEEP</sub>     | Sleep Mode Current [a]                                            | -40 to 85°C                                               |         | 0.6                 | 1       | μΑ                   |

| ISLEEP                 | Sieep Mode Current M                                              | -40 to 125°C                                              |         | 1                   | 3       | μΑ                   |

| Voltage Level          | s                                                                 |                                                           |         |                     |         |                      |

| $V_{POR}$              | Power-On-Reset Level                                              |                                                           | 1.6     | 1.7                 | 2.2     | V                    |

| $V_{REG}$              | Active Regulated Voltage                                          | Note: Regulated voltage can be measured on the Vcore pin. | 2.4     | 2.55                | 2.7     | V                    |

| Capacitance-t          | to-Digital Converter (CDC)                                        |                                                           |         |                     |         |                      |

| REScoc                 | Resolution                                                        |                                                           | 8       |                     | 14      | Bits                 |

| f <sub>MULT1</sub>     |                                                                   | Mult 1                                                    |         | fsys/2              |         | kHz                  |

| f <sub>MULT2</sub>     | Excitation Frequency of External                                  | Mult 2                                                    |         | f <sub>SYS</sub> /4 |         | kHz                  |

| f <sub>MULT4</sub>     | Capacitances C0 and C1 (for a system frequency f <sub>SYS</sub> ) | Mult 4                                                    |         | fsys/8              |         | kHz                  |

| f <sub>MULT8</sub>     | (not a system frequency isis)                                     | Mult 8                                                    |         | fsys/16             |         | kHz                  |

| INLcpc                 | Integral Nonlinearity (INL) [c]                                   | Mult 1, 10% to 90% input, 14-bit                          |         |                     | 0.2     | %                    |

| DNLcdc                 | Differential Nonlinearity (DNL) [b]                               | Mult 1, 10% to 90% input, 14-bit                          |         |                     | 0.9     | LSB                  |

| EEPROM                 |                                                                   | ·                                                         |         |                     |         |                      |

| <b>N</b> WRI_EEP       | Number of Erase/Write Cycles                                      | At 85°C                                                   |         |                     | 100k    |                      |

| twri_eep               | Data Retention                                                    | At 100°C                                                  |         |                     | 10      | Year                 |

| Temperature            | Conversion                                                        |                                                           |         |                     |         |                      |

|                        |                                                                   | -40 to 125°C, 8-bit mode                                  | 0.64    | 0.96                | 1.6     | 00                   |

| RESTEMP                | Resolution in °C [b]                                              | -40 to 125°C, 14-bit mode                                 | 0.01    | 0.015               | 0.025   | °C                   |

| INLcdc                 | Nonlinearity First Order Fit [b], [d]                             | -40 to 125°C                                              |         | ±0.5                | ±1      | °C                   |

| INLcdc                 | Nonlinearity Second Order Fit [b], [e]                            | -40 to 125°C                                              |         | ±0.2                | ±0.4    | °C                   |

| PSRTEMP                | Voltage Dependency [b]                                            | V <sub>SUPPLY</sub> > V <sub>REG</sub> +0.25V             |         | 0.03                | 0.1     | °C/V                 |

| FORTEMP                | Voltage Dependency (%)                                            | $2.3V \le V_{SUPPLY} \le V_{REG} + 0.25V$                 |         | 1.25                | 2.25    | C/V                  |

| PDM Output             |                                                                   |                                                           |         |                     |         |                      |

| V <sub>PDM_Range</sub> | Output Range [b]                                                  |                                                           | 10      |                     | 90      | %V <sub>SUPPLY</sub> |

| f <sub>PDM</sub>       | PDM Frequency                                                     |                                                           |         | fsys/8              |         | kHz                  |

| tsett                  | Filter Settling Time [b], [f]                                     | 0% to 90% LP filter 10kΩ/400nF                            |         |                     | 9.2     | ms                   |

| V <sub>RIPP</sub>      | Ripple [b], [f]                                                   | 0% to 90% LP filter 10kΩ/400nF                            |         |                     | 1.0     | mV/V                 |

| Symbol               | Parameter                                                    | Conditions                                                               | Minimum | Typical | Maximum | Units               |

|----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|---------|---------|---------|---------------------|

| E <sub>PDM</sub>     | PDM Additional Error (Including Ratiometricity Error) [b]    | -40 to 125°C                                                             |         | 0.1     | 0.5     | %                   |

| Digital I/O          |                                                              |                                                                          |         |         |         |                     |

| V <sub>OL</sub>      | Voltage Output Level Low                                     |                                                                          |         | 0       | 0.2     | VSUPPLY             |

| VoH                  | Voltage Output Level High                                    |                                                                          | 0.8     | 1       |         | VSUPPLY             |

| $V_{\text{IL}}$      | Voltage Input Level Low                                      |                                                                          |         | 0       | 0.2     | V <sub>SUPPLY</sub> |

| VIH                  | Voltage Input Level High                                     |                                                                          | 0.8     | 1       |         | VSUPPLY             |

| C <sub>IN</sub>      | Communication Pin Input Capacitance [b]                      |                                                                          |         |         | 10      | pF                  |

| Total System         |                                                              |                                                                          |         |         |         |                     |

| C <sub>tol</sub>     | Capacitive Tolerance Between Parts [b]                       | All capacitive values in the specification are subject to this variation |         |         | ±10     | %                   |

| f <sub>SYS</sub>     | Trimmed System Frequency                                     | All timing in this specification is subject to this variation.           | 1.76    | 1.85    | 1.94    | MHz                 |

| f <sub>var</sub>     | Frequency Variation Over Voltage and Temperature             | All timing in this specification is subject to this variation.           |         |         | ±10     | %                   |

| <b>t</b> sta         | Start-Up-Time [b], [g], [h] Power-on (POR) to data ready     | Fastest and slowest settings                                             | 4.25    |         | 173     | ms                  |

| tresp_up             | Update Rate (Update Mode) [0], [g], [h]                      | Fastest and slowest settings                                             | 0.70    |         | 288     | ms                  |

| t <sub>RESP_SL</sub> | Response Time (Sleep Mode) [b], [g], [h]                     | Fastest and slowest settings                                             | 1.25    |         | 163     | ms                  |

|                      | Barrella to Our and Talances                                 | Mult 1                                                                   |         |         | 10      | pF                  |

|                      | Parasitic to Ground Tolerance Including package parasitics   | Mult 2                                                                   |         |         | 20      | pF                  |

|                      | (Pins C0, CC, and C1) [b]                                    | Mult 4                                                                   |         |         | 40      | pF                  |

|                      | (**************************************                      | Mult 8                                                                   |         |         | 80      | pF                  |

| $N_{OUT}$            | Peak-to-Peak Noise @ output (100 measurements in 14 bit) [b] | Mult 1, 2, 4, 8                                                          |         | 5       | 20      | LSB                 |

| ۸۲                   | F Mult 4 40 t- 40 500 ml m m m                               | 3V±10%, 3.3V±10%, 5V±10%                                                 |         | ±0.25   | ±0.75   | %FSO                |

| AE <sub>out</sub>    | Error Mult 1, -40 to 125°C D, D, D, D                        | 2.5V±10%                                                                 |         | ±0.50   | ±1.25   | %FSO                |

| ۸Ε .                 | Mult 2 4 9 40 to 125°C N III III N                           | 3V±10%, 3.3V±10%, 5V±10%                                                 |         | ±0.50   | ±1.25   | %FSO                |

| $AE_{out}$           | Mult 2, 4, 8, -40 to 125°C [b], [i], [i], [k]                | 2.5V±10%                                                                 |         | ±1.50   | ±3.00   | %FSO                |

<sup>[</sup>a]See section 6 for full details for current consumption in each mode.

<sup>[</sup>b]Parameter not tested during production but guaranteed by design.

<sup>[</sup>c]Parameter measured using internal test capacitors (0pF to 7pF in Mult 1).

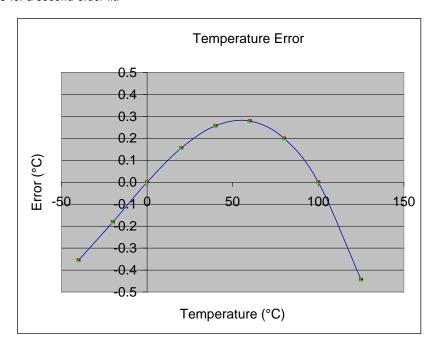

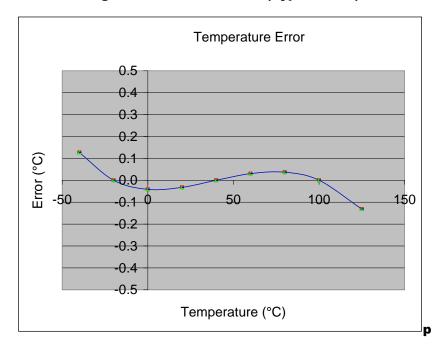

<sup>[</sup>d]Assumes optimal calibration points of 0°C and 100°C; see section 8 for more details.

<sup>[</sup>e]Assumes optimal calibration points of -20°C, 40°C and 100°C; see section 8 for more details.

<sup>[</sup>f] See section 10.7 for more details.

<sup>[</sup>g]See section 10 for more details.

<sup>[</sup>h]Timing values are for a nominal oscillator, for worst case, ±10% total frequency variation, multiply by 0.9 (minimum time) or 1.1 (maximum time).

<sup>[</sup>i] Accuracy specification includes a 2-point temperature calibration for correcting the internal TC.

<sup>[</sup>j] Accuracy specification assumes maximum parasitics of 10pF to ground.

<sup>[</sup>k]Accuracy specification does not include PDM errors; see the PDM Output electrical parameters for additional errors when using PDM.

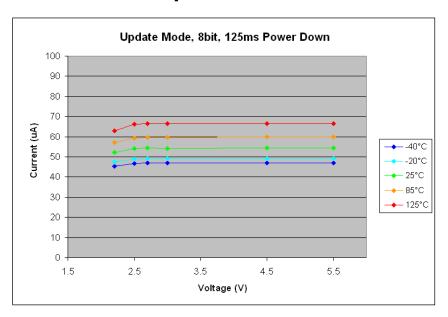

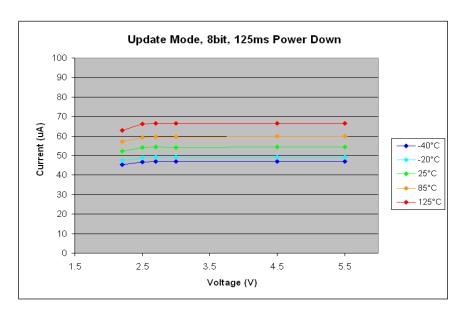

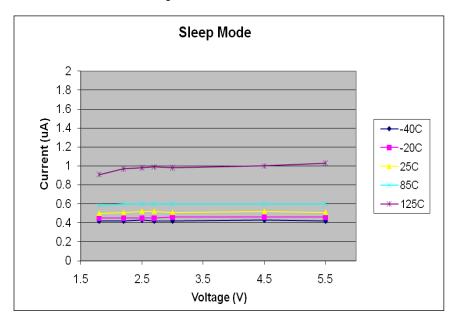

## 6. Current Consumption Graphs

Part current consumption depends on a number of different factors including voltage, temperature, capacitive input, Mult, resolution, and power down time. The best method for calculating the ZSSC3123's power consumption is to measure the current consumption with the actual setup. If measurement is not possible, then the graphs in this section can provide a starting point for estimating the current consumption.

### **6.1 Update Mode Current Consumption**

Figure 2. Best Case Settings (Typical Part)

Figure 3. Worst Case Settings (Typical Part)

# 6.2 Sleep Mode Current Consumption

Figure 4. Typical Current Consumption during Sleep Mode (No Measurements)

# 7. Output Pad Drive Strength

Figure 5. Output High Drive Strength Graph

Figure 6. Output Low Drive Strength Graph

### 8. Temperature Sensor Nonlinearity

Temperature sensor nonlinearity can vary depending on the type of calibration and the selected calibration points. It is highly recommended that a temperature calibration is done with calibration points at least 20°C apart from each other. The following figures show the resulting nonlinearity error for the full temperature range (-40°C to 125°C) using the optimal calibration points 0°C and 100°C for a first-order fit and -20°C, 40°C, and 100°C for a second-order fit.

Figure 7. First Order Fit (Typical Part)

Figure 8. Second Order Fit (Typical Part)

### 9. Circuit Description

### 9.1 Signal Flow and Block Diagram

As seen in the following figure, the ZSSC3123 comprises three main blocks: the analog core, digital core, and output communication. The capacitive input is first sampled by the analog core using a charge-balancing CDC and is adjusted for the appropriate capacitance range using the CDC\_Offset, CDC\_Reference, and CDC\_Mult settings. The digital core corrects the digital sample with an on-chip digital signal processor (DSP), which uses coefficients stored in EEPROM for precise conditioning. An internal temperature sensor can be used to compensate for temperature effects of the capacitive input. A temperature value can also be calibrated and output as a 14-bit reading.

The corrected capacitance value can be read using four different output types, I2C, SPI, PDM, and alarms. They can all be directly interfaced with a microcontroller, and optional filtering of the PDM output can provide a ratiometric analog output. The alarm pins can also be used to control a variety of analog circuitry.

Figure 9. ZSSC3123 Block Diagram

### 9.2 Analog Front End

#### 9.2.1 Capacitance-to-Digital Converter

A 1st-order charge-balancing capacitance-to-digital converter (CDC) is used to convert the input capacitance to the digital domain. The CDC uses a chopper-stabilized design to decrease any drift over temperature. The CDC interfaces to the sensor capacitor through the input multiplexer that controls whether the measurement is a capacitance or a temperature measurement. The input multiplexer also allows for two sensor capacitance configurations: a single-sensor capacitance or a two-sensor, ratio-based differential capacitance configuration, where the reference capacitor is part of the sensor.

As part of a switched-capacitor network, the reference capacitor C1 is driven by a square-wave voltage of the frequency fexc (see section 5). The sensor capacitance C0 is not exposed to DC voltages in order to prevent the aging effects of some sensor types. The configuration of the CDC is controlled by programming settings in EEPROM word *C\_Config.* (See Table 30 for settings.)

#### 9.2.1.1 Single Ended

In the case of a single-sensor capacitor, the CDC output is proportional to the ratio of the sensor capacitor to an internal reference capacitor (CREF). This internal reference capacitor value can be adjusted using the 3-bit trim CDC\_Reference and a 2-bit range selection CDC\_Mult (bit settings in Table 30). To optimize the measured end-resolution further, another internal capacitor (Coff) allows the subtraction of a defined offset capacitance using the 3-bit trim CDC\_Offset (bit setting in Table 30). Equation 1 and Equation 2 describe the CDC output for a single sensor capacitance measurement. For CMULT, use the multiplier in the "Total Capacitance Multiplier (CMULT)" column in Table 5. Select the values of CDC\_Offset, and CDC\_Reference by using the settings given in Table 6 to Table 9, depending on the Mult value. Note: Use the bit settings (0-7) and not the value in pF.

$$Z_{SENSOR} = \frac{(C_0 - C_{OFF})}{C_{REF}}$$

**Equation 1**

$$Z_{CDC} = 2^{RES} * Z_{SENSOR}$$

**Equation 2**

With

$$C_{OFF} = C_{MULT} * CDC_Offset * 1pF$$

**Equation 3**

And

$$C_{REF} = C_{MULT} * CDC_Reference * 1pF$$

**Equation 4**

Where:

| Symbol              | Description                                                                    |

|---------------------|--------------------------------------------------------------------------------|

| Z <sub>SENSOR</sub> | Measured sensor ratio, must be in the range [0 to 1]                           |

| C <sub>0</sub>      | Input sensor capacitance                                                       |

| Coff                | Zero shift of CDC                                                              |

| C <sub>REF</sub>    | Reference capacitance                                                          |

| Z <sub>CDC</sub>    | Digital raw converted capacitance value                                        |

| RES                 | Programmable CDC resolution of 8, 10, 12, or 14 bits (bit setting in Table 30. |

| C <sub>MULT</sub>   | Capacitance range multiplier (see Table 5)                                     |

| CDC_Offset          | CDC offset trim setting (see section 9.2.1.4 and bit setting see Table 30      |

| CDC_Reference       | CDC reference setting (see section 9.2.1.4 and bit setting see Table 30)       |

### 9.2.1.2 Single Ended with External Reference

Some sensors include an external reference capacitor as part of the sensor construction. If the external reference capacitance (C<sub>1</sub>) is constant or increases with increasing input sensor capacitance (C<sub>0</sub>), then use CDC output Equation 5 through Equation 7. In this case, the CDC\_Reference should be set to zero (bit setting in Table 30).

$$Z_{SENSOR} = \frac{(C_0 - C_{OFF})}{C_1}$$

**Equation 5**

$$Z_{CDC} = 2^{RES} * Z_{SENSOR}$$

**Equation 6**

$$C_{OFF} = C_{MULT} * CDC \_ Offset * 1pF$$

**Equation 7**

Where:

| Symbol                                                                   | Description                             |

|--------------------------------------------------------------------------|-----------------------------------------|

| Z <sub>SENSOR</sub> Measured sensor ratio; must be in the range [0 to 1] |                                         |

| C <sub>0</sub>                                                           | Input sensor capacitance                |

| C <sub>OFF</sub>                                                         | Zero shift of CDC                       |

| C <sub>1</sub>                                                           | External reference capacitance          |

| Z <sub>CDC</sub>                                                         | Digital raw converted capacitance value |

| Symbol            | Description                                                                    |

|-------------------|--------------------------------------------------------------------------------|

| RES               | Programmable CDC resolution of 8, 10, 12, or 14 bits (bit setting in Table 30) |

| C <sub>MULT</sub> | Capacitance range multiplier (see Table 5)                                     |

| CDC_Offset        | CDC offset trim setting (see section 9.2.1.4 and Table 30)                     |

#### 9.2.1.3 Differential

A differential capacitive sensor includes two capacitors  $C_0$  and  $C_1$  that are captured as a ratio. The differential sensor is built so that the sensor input capacitance  $C_0$  increases while the external reference capacitance  $C_1$  decreases over the input signal range, but the total sum always remains constant. Equation 8 and Equation 9 describe the CDC output for a differential sensor capacitance measurement. The CDC\_Reference and CDC\_Offset capacitor trim bits must be set to zero, and the Differential bit must be set to one. (See Table 30 for bit numbers and settings). The Mult bits should be set so that the total capacitance  $(C_0 + C_1)$  falls in the corresponding capacitance range (see Table 5). The sum of  $C_0$  and  $C_1$  must not be larger than the selected Mult's maximum input range, except when CC is used as a decoupling capacitor.

In differential mode special sensor types can allow a non-galvanic connection with an external isolating capacitor Ccc between the sensor and the CC pin to avoid wear caused by mechanical moving parts.

$$Z_{SENSOR} = \frac{C_0}{\left(C_0 + C_1\right)}$$

Equation 8

$$Z_{CDC} = 2^{RES} * Z_{SENSOR}$$

Equation 9

| Symbol         | Description                                                                         |

|----------------|-------------------------------------------------------------------------------------|

| Zsensor        | Measured sensor ratio; must be in the range [0 to 1]                                |

| C <sub>0</sub> | Input sensor capacitance (moves in the opposite direction of C <sub>1</sub> )       |

| C <sub>1</sub> | External reference capacitance (moves in the opposite direction of C <sub>0</sub> ) |

| Zcdc           | Digital raw converted capacitance value                                             |

| RES            | Programmable CDC resolution of 8, 10, 12, or 14 bits (bit setting in Table 30)      |

#### 9.2.1.4 Capacitive Range Selection

Whether the application uses a single-ended or a differential sensor, the correct capacitance range as defined in Table 5 must be selected using the Mult bits, which are configured in the  $C\_Config$  register (see Table 30). If using a single-ended sensor, then the minimum and maximum capacitance inputs should fall into the specified ranges. If using a differential sensor then the total capacitance ( $C_0 + C_1$ ) must fall into this range. The Mult range affects the conversion time (see section 10.2).

Note: If the externally applied capacitance exceeds the configured capacitance range, the converted output signal can still show an apparently correct value, which is not valid. The limit is about 500% of the selected maximum input value. For example, for a capacitance setting of Mult1, CDC\_Offset at zero, and CDC\_Reference at 7, an input value above 117pF will give a non-saturated input value.

Table 5. CDC Multiplier

| EEPROM Encoding (CDC_Mult) | Frequency Multiplier<br>(Mult) | Reference Multiplier | Total Capacitance<br>Multiplier (C <sub>MULT</sub> ) | Capacitance Range<br>(Full Scale Values) |

|----------------------------|--------------------------------|----------------------|------------------------------------------------------|------------------------------------------|

| 00 <sub>BIN</sub>          | 1                              | 1.44                 | 1.44                                                 | 2pF to 8pF                               |

| 01 <sub>BIN</sub>          | 2                              | 2.88                 | 5.76                                                 | 8pF to 32pF                              |

| 10 <sub>BIN</sub>          | 4                              | 5.76                 | 23.04                                                | 32pF to 130pF                            |

| 11 <sub>BIN</sub>          | 8                              | 11.52                | 92.16                                                | 130pF to 260pF                           |

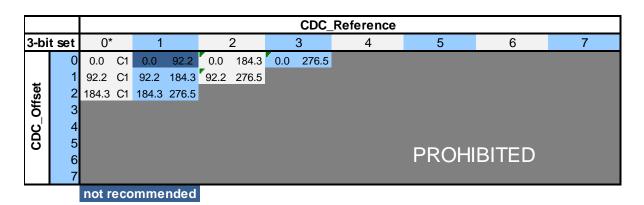

For single-ended sensors, use Table 6, Table 7, Table 8, and Table 9 as guidance for selecting appropriate values for the CDC ( $C_{OFF}$ ) and ( $C_{REF}$ ) for a particular capacitance input range. The CDC\_Offset and CDC\_Reference bits are found in EEPROM word C\_Config. (Refer to Table 30 for bit numbers). Using the tables, the CDC input range can be adjusted to optimize the coverage of the sensor signal and offset values to give the maximum sensor span that can be processed without losing resolution. Choose a range by fitting the input sensor span within the narrowest range in the table, but note that these tables are only approximate, so the range should be chosen experimentally with the actual setup. Also note that since internal capacitance values can vary over process (see specification  $C_{tol}$  in Table 4), the minimum and maximum sensor span should be at least  $\pm 10\%$  within the minimum and maximum of the chosen range respectively. Note: Take into consideration the effects of parasitics; if the parasitics for a particular Mult range exceed the parasitic to ground tolerance given in section 1, then the next Mult range should be considered since the CDC frequency is reduced by the Mult factor.

Note: A C<sub>REF</sub> setting of 0 (marked with \* in the following tables) is only supported with an external reference capacitor (C1) for single-ended sensors. C1 capacitance values should be within the defined range for each Mult setting.

Selection settings for CREF, and COFF, and Mult are given in the following tables (capacitance ranges are nominal values).

Table 6. Mult 1: Sensor Capacitors Ranging from 2pF to 10pF (Full Scale Values)

|           |   |      | CDC_Reference |      |      |      |      |     |      |     |      |     |      |     |      |     |      |

|-----------|---|------|---------------|------|------|------|------|-----|------|-----|------|-----|------|-----|------|-----|------|

| 3-bit set |   | 0    | *             | ,    | 1    | 2    | 2    | ;   | 3    | 4   | 4    | ļ   | 5    | (   | 6    | •   | 7    |

|           | 0 | 0.0  | C1            | 0.0  | 1.4  | 0.0  | 2.9  | 0.0 | 4.3  | 0.0 | 5.8  | 0.0 | 7.2  | 0.0 | 8.6  | 0.0 | 10.1 |

|           | 1 | 1.4  | C1            | 1.4  | 2.9  | 1.4  | 4.3  | 1.4 | 5.8  | 1.4 | 7.2  | 1.4 | 8.6  | 1.4 | 10.1 | 1.4 | 11.5 |

| Offset    | 2 | 2.9  | C1            | 2.9  | 4.3  | 2.9  | 5.8  | 2.9 | 7.2  | 2.9 | 8.6  | 2.9 | 10.1 | 2.9 | 11.5 |     | 18.0 |

| Off       | 3 | 4.3  | C1            | 4.3  | 5.8  | 4.3  | 7.2  | 4.3 | 8.6  | 4.3 | 10.1 | 4.3 | 11.5 |     |      |     | 14.4 |

|           | 4 | 5.8  | C1            | 5.8  | 7.2  | 5.8  | 8.6  | 5.8 | 10.1 | 5.8 | 11.5 |     |      |     |      |     | 15.3 |

| CDC       | 5 | 7.2  | C1            | 7.2  | 8.6  | 7.2  | 10.1 | 7.2 | 11.5 |     |      |     |      |     |      |     |      |

|           | 6 | 8.6  | C1            | 8.6  | 10.1 | 8.6  | 11.5 |     |      |     |      | PR  | OH   | BIT | ED   |     |      |

|           | 7 | 10.1 | C1            | 10.1 | 11.5 | 10.1 | 13.0 |     | 16.6 |     |      |     |      |     |      |     |      |

| -         |   |      |               |      |      |      |      |     |      |     |      |     |      |     |      |     |      |

not recommended

Table 7. Mult 2: Sensor Capacitors Ranging from 8pF to 32pF (Full Scale Values)

|           |   |      | CDC_Reference |      |      |      |      |      |      |      |      |      |               |     |      |     |      |

|-----------|---|------|---------------|------|------|------|------|------|------|------|------|------|---------------|-----|------|-----|------|

| 3-bit set |   | 0* 1 |               |      | 2    |      | 3    | 3    | 4    |      | 5    |      | 6             |     | 7    |     |      |

|           | 0 | 0.0  | C1            | 0.0  | 5.8  | 0.0  | 11.5 | 0.0  | 17.3 | 0.0  | 23.0 | 0.0  | 28.8          | 0.0 | 34.6 | 0.0 | 40.3 |

| <b>*</b>  | 1 | 5.8  | C1            | 5.8  | 11.5 | 5.8  | 17.3 | 5.8  | 23.0 | 5.8  | 28.8 | 5.8  | 34.6          | 5.8 | 40.3 |     |      |

| Offset    | 2 | 11.5 | C1            | 11.5 | 17.3 | 11.5 | 23.0 | 11.5 | 28.8 | 11.5 | 34.6 | 11.5 | 40.3          |     |      |     |      |

|           | 3 | 17.3 | C1            | 17.3 | 23.0 | 17.3 | 28.8 | 17.3 | 34.6 | 17.3 | 40.3 |      |               |     |      |     |      |

| CDC       | 4 | 23.0 | C1            | 23.0 | 28.8 | 23.0 | 34.6 | 23.0 | 40.3 |      |      |      |               |     |      |     |      |

| ᄗ         | 5 | 28.8 | C1            | 28.8 | 34.6 | 28.8 | 40.3 |      |      |      |      |      | <b>Ω</b> Ι.ΙΙ | БІТ |      |     |      |

|           | 6 | 34.6 | C1            | 34.6 | 40.3 |      |      |      |      |      |      | PR   | OHI           | BH  | FD   |     |      |

|           | 7 |      |               |      |      |      |      |      |      |      |      |      |               |     |      |     |      |

not recommended

Table 8. Mult 4: Sensor Capacitors Ranging from 32pF to 130pF (Full Scale Values)

|        |           |       | CDC_Reference |       |       |       |       |      |       |      |       |      |                 |      |       |     |       |

|--------|-----------|-------|---------------|-------|-------|-------|-------|------|-------|------|-------|------|-----------------|------|-------|-----|-------|

| 3-bi   | 3-bit set |       | 0*            |       | 1     |       | 2     |      | 3     |      | 4     |      | 5               | 6    |       | 7   |       |

|        | 0         | 0.0   | C1            | 0.0   | 23.0  | 0.0   | 46.1  | 0.0  | 69.1  | 0.0  | 92.2  | 0.0  | 115.2           | 0.0  | 138.2 | 0.0 | 161.3 |

| ٠,     | 1         | 23.0  | C1            | 23.0  | 46.1  | 23.0  | 69.1  | 23.0 | 92.2  | 23.0 | 115.2 | 23.0 | 138.2           | 23.0 | 161.3 |     |       |

| Offset | 2         | 46.1  | C1            | 46.1  | 69.1  | 46.1  | 92.2  | 46.1 | 115.2 | 46.1 | 138.2 | 46.1 | 161.3           |      |       |     |       |

| δ      | 3         | 69.1  | C1            | 69.1  | 92.2  | 69.1  | 115.2 | 69.1 | 138.2 | 69.1 | 161.3 |      |                 |      |       |     |       |

| CDC    | 4         | 92.2  | C1            | 92.2  | 115.2 | 92.2  | 138.2 | 92.2 | 161.3 |      |       |      |                 |      |       |     |       |

| ᄗ      | 5         | 115.2 | C1            | 115.2 | 138.2 | 115.2 | 161.3 |      |       |      |       |      | $\bigcirc$ L II | דוחו |       |     |       |

|        | 6         | 138.2 | C1            | 138.2 | 161.3 |       |       |      |       |      |       | PK   |                 | BH   | ED    |     |       |

|        | 7         |       |               |       |       |       |       |      |       |      |       |      |                 |      |       |     |       |

|        |           | not r | ecoi          | nmen  | ded   |       | •     |      |       | •    |       | •    | •               | •    |       | •   | •     |

Table 9. Mult 8: Sensor Capacitors Ranging from 130pF to 260pF (Full Scale Values)

#### 9.2.2 Temperature Measurement

The temperature signal comes from an internal PTAT (proportional to absolute temperature) circuit that is a measure of the die temperature. The PTAT (VPTAT) voltage is used in the CDC to charge an internal capacitor (CT), while the bandgap voltage (VBG) is used to charge the offset and the reference trimmable capacitors. The CDC temperature output (ZTEMP) is defined by Equation 10 through Equation 13:

$$Z_{TEMP} = 2^{RES} * \frac{(V_{PTAT} / V_{BG}) * C_T - C_{TOFF}}{C_{TREF}}$$

Equation 10 With

$$C_T = 1.44 * Temp\_Trim * 1pF$$

Equation 11 With

$$C_{TOFF} = 1.44 * CDC\_Offset * 1pF$$

And

$$C_{TREF} = 1.44 * CDC\_Reference * 1pF$$

Equation 13 Where:

| Symbol            | Description                                                                    |

|-------------------|--------------------------------------------------------------------------------|

| Z <sub>TEMP</sub> | Measured internal temperature                                                  |

| RES               | Programmable CDC resolution of 8, 10, 12, or 14 bits (bit setting in Table 31) |

| V <sub>PTAT</sub> | Internal PTAT voltage                                                          |

| $V_{BG}$          | Internal bandgap voltage                                                       |

| Symbol            | Description                                        |

|-------------------|----------------------------------------------------|

| Ст                | Temperature measurement capacitor                  |

| C <sub>TOFF</sub> | Temperature CDC zero shift                         |

| C <sub>TREF</sub> | Temperature reference capacitance                  |

| Temp_Trim         | Temperature trim setting (bit setting in Table 31) |

| CDC_Offset        | CDC offset trim setting (bit setting in Table 31)  |

| CDC_Reference     | CDC reference setting (bit setting in Table 31)    |

Note: The factory settings for Temp\_Trim, CDC\_Offset, and CDC\_Reference are optimized for the full temperature range of -40°C to 125°C guaranteeing a minimum effective resolution of 13 bits when 14 bits of resolution is selected. Unless a different temperature range is needed, it is strongly recommended that these settings not be changed.

### 9.3 Digital Core

The digital core provides control logic for the analog front-end, performs input signal conditioning, and handles external communication. A digital signal processor (DSP) is used for conditioning and correcting the converted sensor and temperature inputs. The DSP can correct for up to a two-region piece-wise non-linear sensor input, and up to a second-order non-linear temperature input. Alternatively a third-order correction of the sensor input for one region and up to a second-order, non-linear temperature input can be selected. Refer to section 13 for details on the signal conditioning and correction math. The analog front-end configuration and correction coefficients for both the capacitive sensor and the temperature sensor are stored in an on-chip EEPROM.

Four different types of outputs are available: I2C, SPI, PDM, and the Alarms. These output modes are used in combination with the two measurement modes: Update Mode and Sleep Mode. For a full description of normal operation in each mode, refer to section 10.

The ZSSC3123 has an internal 1.85MHz temperature-compensated oscillator that provides the time base for all operations. When VDD exceeds the POR level, the reset signal de-asserts and the clock generator starts. See section 10.1 for the subsequent power-on sequence. The exact clock frequency influences the measurement cycle time (see the frequency variation spec in section 5). To minimize the oscillator error as the VDD voltage changes, an on-chip regulator supplies the oscillator block.

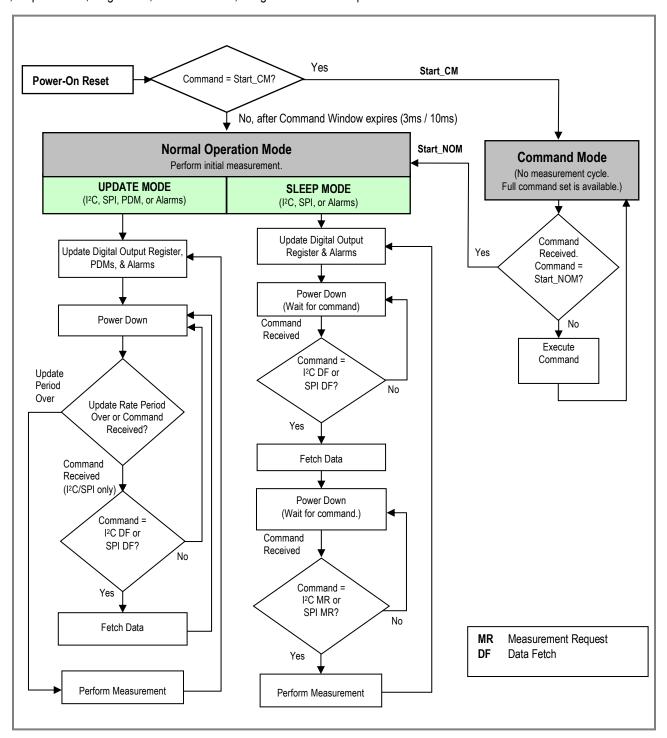

### 10. Normal Operation Mode

The following figure gives a general overview of ZSSC3123 operation. Details of operation, including the power-up sequence, measurement modes, output modes, diagnostics, and commands, are given in the subsequent sections.

Figure 10. General Operation

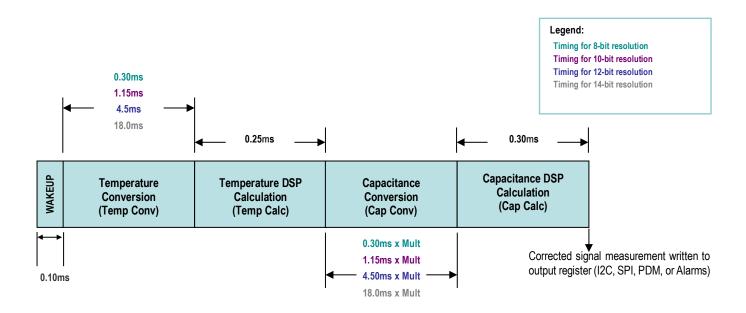

### 10.1 Power-On Sequence

The following figure shows the power-on sequence of the ZSSC3123. On system power-on reset (POR), the ZSSC3123 wakes as an I2C device regardless of the output protocol programmed in EEPROM. After power-on reset, the ZSSC3123 enters the command window. It then waits for a Start\_CM command for 3ms if the Fast\_Startup EEPROM bit is set or if the bit is not set, it waits10ms (see Table 32). If the ZSSC3123 receives the Start\_CM command during the command window, it enters and remains in Command Mode. Command Mode is primarily used in the calibration environment. See section 11 for details.

If during the power-on sequence, the command window expires without receiving a Start\_CM or if the part receives a Start\_NOM command in Command Mode, the device will immediately assume its programmed output mode and will perform one complete measurement cycle. Timing for the initial measurement is described in section 10.2. At the end of the capacitance DSP calculation, the first data is written to the output register. Beyond this point, conversions are performed according to the programmed measurement mode settings (see section 11.3).

Figure 11. Power-On Sequence with Fast Startup Bit Set in EEPROM

Note: See section 10.2 for timing of the measurement cycle. Timing values shown are typical; for the worst case values, multiply by 1.1 (nominal frequency  $\pm 10\%$ ).

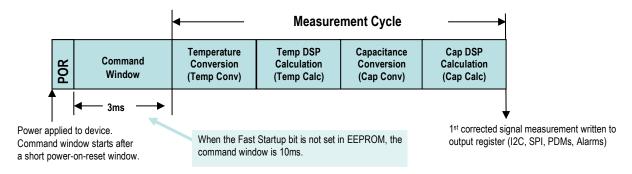

### 10.2 Measurement Cycle

Figure 12 shows a typical measurement cycle. At the start of a measurement, there is a small wakeup period and then an internal temperature conversion/temperature DSP calculation is performed followed by a capacitance conversion/capacitance DSP calculation. The length of these conversions depends on the settings for the two Resolution bits in the C\_Config and T\_Config EEPROM words (refer to Table 10, Table 30, and Table 31). For capacitance measurements, conversion time also depends on the Mult selected by the CDC\_Mult bits in C\_Config (see Table 5 and Table 30). Each conversion cycle is followed by a DSP calculation, which uses the programmed calibration coefficients to calculate corrected temperature and capacitance measurements. In Update Mode, a temperature conversion is not performed every measurement cycle because it is considered a slower moving quantity. In this case, the measurement cycle timing is the same as in the figure without the temperature conversion/ temperature DSP calculation (see section 10.3.1 for more information).

Figure 12. Measurement Cycle Timing

**Table 10. CDC Resolution and Conversion Times**

| Resolution Bits in C_Config and T_Config Words | CDC Resolution (Bits) | Temperature Conversion<br>Time <sup>[a]</sup> (ms) | Capacitance Conversion<br>Time া (ms) |

|------------------------------------------------|-----------------------|----------------------------------------------------|---------------------------------------|

| 00вім                                          | 8                     | 0.30                                               | 0.30 * Mult                           |

| 01вім                                          | 10                    | 1.15                                               | 1.15 * Mult                           |

| 10 <sub>BIN</sub>                              | 12                    | 4.50                                               | 4.50 * Mult                           |

| 11 <sub>BIN</sub>                              | 14                    | 18.0                                               | 18.0 * Mult                           |

[a]All time values shown are typical: for the worst case values, multiply by 1.1 (nominal frequency ±10%).

#### 10.3 Measurement Modes

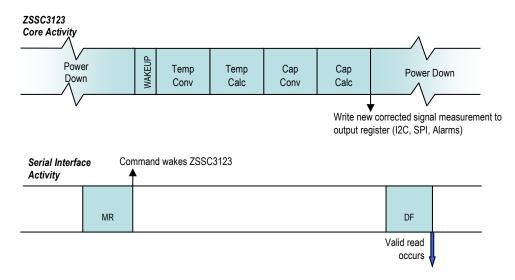

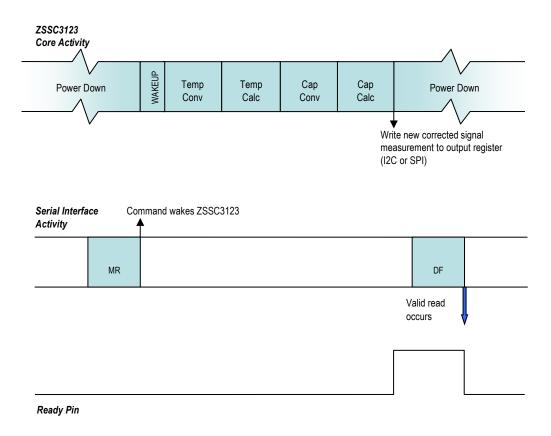

The ZSSC3123 can be programmed to operate in either Sleep Mode or Update Mode. The measurement mode is selected with the Measurement\_Mode bit in the ZMDI\_Config EEPROM word (see Table 29). In Update Mode, measurements are taken at a fixed, selectable rate (see section 10.3.1). In Sleep Mode, the part waits for commands from the master before taking measurements (refer to section 10.3.2).

Figure 10 shows the differences in operation between the two measurement modes.

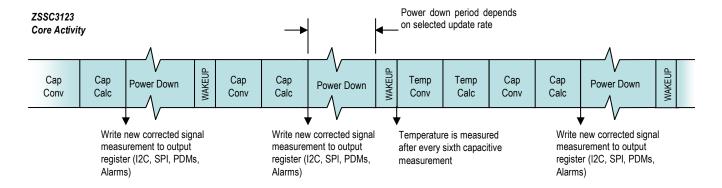

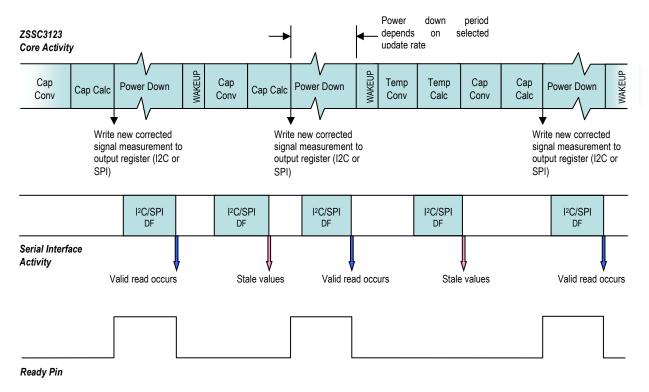

#### 10.3.1 Update Mode

In Update Mode, the digital core will perform conversions at an update rate selected with the Power\_Down\_Period bit field in the ZMDI\_Config EEPROM word (see Table 29). Table 11 shows the power-down periods between conversions for the four Power\_Down\_Period settings. The benefit of slower update rates is power savings. Update Mode is compatible with all the different output modes; I2C, SPI, PDMs, and the Alarms. As shown in the following figure, at the completion of a measurement cycle, the digital output register, PDMs, and/or Alarms will be updated before powering down. When the power-down period expires, the ZSSC3123 will wake up and perform another measurement cycle. If the part is programmed for the fastest update rate, there is no power-down period, and measurements happen continuously.

Table 11. Update Rate Settings (Power\_Down\_Period Bit Field in ZMDI\_Config)

Note: All time values shown are typical; for the worst case values, multiply by 1.1 (nominal frequency ±10%).

| Power_Down_Period Setting | Power Down Period (ms) |

|---------------------------|------------------------|

| 00 <sub>BIN</sub>         | 0                      |

| 01 <sub>BIN</sub>         | 5                      |

| 10 <sub>BIN</sub>         | 25                     |

| 11 <sub>BIN</sub>         | 125                    |

Note: See section 10.2 for measurement cycle timing.

Figure 13. Measurement Sequence in Update Mode

To calculate the total time between capacitive measurements in Update Mode, add the measurement cycle timing from section 10.2 and the power down timing from Table 11. For example, typical settings might be a capacitance measurement resolution of 12-bits with a Mult of 1. In this example, the time between measurements = (4.5 ms \* 1 + 0.1 ms + 0.3 ms) + (power down period). See Table 12 through Table 15 and

Figure 12 for the time between measurements for the different update rate settings and bit resolutions.

Temperature measurements are performed every six capacitive measurements. The actual frequency of temperature conversions varies with the update rate and AFE configuration settings. As shown in

Note: See section 10.2 for measurement cycle timing.

Figure 13, when a temperature measurement is performed, a capacitance measurement occurs immediately after, so the total measurement cycle time is increased by the length of the temperature conversion and temperature DSP calculation.

To calculate the total time between temperature measurements in Update Mode, take the time between capacitive measurements as calculated in the above text and multiply that number by six (there are six capacitive measurements to every temperature measurement) and then add the temperature conversion time/temperature DSP calculation time from Table 11 For example a temperature measurement with a resolution of 12-bits has a conversion time/DSP calculation time of 4.5ms +0.25ms (from Table 11) Continuing with the above example (12-bit capacitive measurement with a multiplier of 1) the time between temperature measurements is (capacitance update time \* 6) + 4.75ms.

Table 12. Time Periods between Capacitance and Temperature Measurements for Mult1,

Different Resolutions, and Update Rates

|                    | Mult1                         |                                  |                                  | otal Time betwe<br>ince Measureme |                                  | Total Time between<br>Temperature Measurements (ms) |                                  |                                  |  |

|--------------------|-------------------------------|----------------------------------|----------------------------------|-----------------------------------|----------------------------------|-----------------------------------------------------|----------------------------------|----------------------------------|--|

| CDC Res.<br>(Bits) | Update Rate 00 <sub>BIN</sub> | Update Rate<br>01 <sub>BIN</sub> | Update Rate<br>10 <sub>BIN</sub> | Update Rate<br>11 <sub>BIN</sub>  | Update Rate<br>00 <sub>BIN</sub> | Update Rate<br>01 <sub>BIN</sub>                    | Update Rate<br>10 <sub>BIN</sub> | Update Rate<br>11 <sub>BIN</sub> |  |

| 8                  | 0.70                          | 5.70                             | 25.70                            | 125.70                            | 4.75                             | 34.75                                               | 154.75                           | 754.75                           |  |

| 10 | 1.55  | 6.55  | 26.55 | 126.55 | 10.70  | 40.70  | 160.70 | 760.70 |

|----|-------|-------|-------|--------|--------|--------|--------|--------|

| 12 | 4.90  | 9.90  | 29.90 | 129.90 | 34.15  | 64.15  | 184.15 | 784.15 |

| 14 | 18.40 | 23.40 | 43.40 | 143.40 | 128.65 | 158.65 | 278.65 | 878.65 |

Table 13. Time Periods between Capacitance and Temperature Measurements for Mult2, Different Resolutions, and Update Rates

| Mult2              |                                  |                                  | Total Time between Capacitance Measurements (ms)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                  | Total Time between<br>Temperature Measurements (ms) |                                  |        |