TC642

\*Patent Granted

# PWM Fan Speed Controller with FanSense™\*

#### **FEATURES**

- Temperature Proportional Fan Speed for Acoustic Control and Longer Fan Life

- Efficient PWM Fan Drive

- 3.0V 5.5V Supply Range; Fan Voltage Independent of TC642 Supply Voltage Supports Any Fan Voltage!

- FanSense<sup>™</sup> Fault Detection Circuits Protect Against Fan Failure and Aid System Testing

- Shutdown Mode for "Green" Systems

- Supports Low Cost NTC/PTC Thermistors

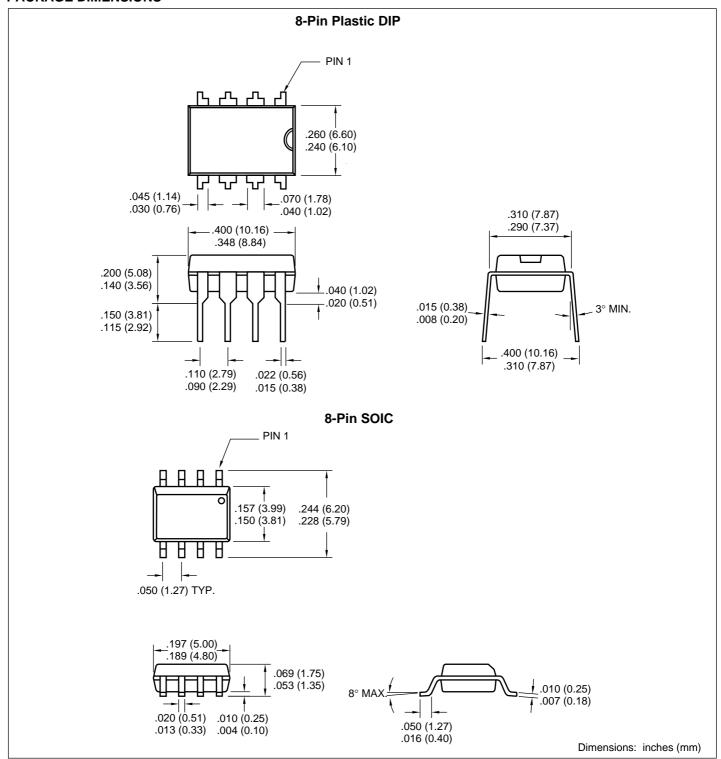

- Space-Saving 8-Pin PDIP and SOIC Packages

## **APPLICATIONS**

- Power Supplies

- Personal Computers

- File Servers

- Microchip Technology Equipment

- UPS's, Power Amps, etc.

- General Purpose Fan Speed Control

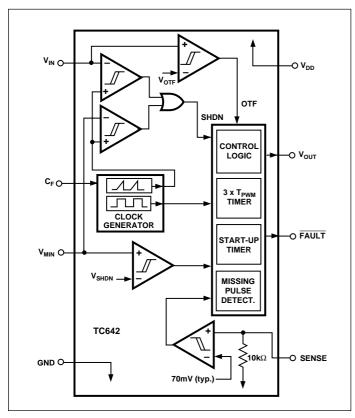

# **FUNCTIONAL BLOCK DIAGRAM**

# **GENERAL DESCRIPTION**

The TC642 is a switch mode fan speed controller for use with brushless DC motors. Temperature proportional speed control is accomplished using pulse width modulation. A thermistor (or other voltage output temperature sensor) connected to the  $V_{\rm IN}$  input furnishes the required control voltage of 1.25V to 2.65V (typical) for 0% to 100% PWM duty cycle. Minimum fan speed is set by a simple resistor divider on the  $V_{\rm MIN}$  input. An integrated Start-Up Timer ensures reliable motor start-up at turn-on, coming out of Shutdown Mode, or following a transient fault.

A logic low applied to  $V_{MIN}$ , pin 3, causes fan shutdown. The TC642 also features Microchip Technology's proprietary FanSense technology for increasing system reliability. In normal fan operation, a pulse train is present at SENSE, pin 5, indicating normal operation. A missing-pulse detector monitors this pin during normal fan operation. A stalled, open, or unconnected fan causes the TC642 to trigger its start-up timer once. If the fault persists, the FAULT output goes low, and the device is latched in its Shutdown Mode. FAULT is also asserted if the PWM reaches 100%

# **ORDERING INFORMATION**

| Part No. | Package                  | Temp. Range  |

|----------|--------------------------|--------------|

| TC642COA | 8-Pin SOIC               | 0°C to +70°C |

| TC642CPA | 8-Pin Plastic DIP        | 0°C to +70°C |

| TC642VOA | 8-Pin SOIC               | 0°C to +85°C |

| TC642VPA | 8-Pin Plastic DIP        | 0°C to +85°C |

| TC642EV  | Evaluation Kit for TC642 |              |

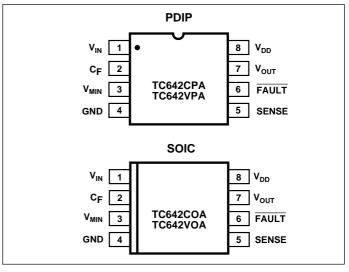

### PIN CONFIGURATIONS

© 2001 Microchip Technology Inc. DS21444A

# **TC642**

duty cycle, indicating a possible thermal runaway situation, although the fan continues to run. See the *Applications* section for more information and system design guidelines.

The TC642 is available in a standard 8-pin plastic DIP, and SOIC packages. Commercial and industrial temperature ranges are available in both package options.

## **ABSOLUTE MAXIMUM RATINGS\***

| Package Power Dissipation (T <sub>A</sub> ≤ 70°C)              |    |

|----------------------------------------------------------------|----|

| Plastic DIP730m\                                               | W  |

| Small Outline (SOIC)470m\                                      | W  |

| Derating Factors 8mW/°                                         | С  |

| Supply Voltage6                                                | ٧  |

| Input Voltage, Any Pin (GND – 0.3V) to (V <sub>CC</sub> + 0.3V | √) |

| Operating Temperature Range – 0°C to +125°                     | С  |

| Maximum Chip Temperature+150°                                  | С  |

| Storage Temperature Range – 65°C to +150°                      | С  |

| Lead Temperature (Soldering, 10 sec)+300°                      | С  |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS:** $T_{MIN} < T_A < T_{MAX}$ , $V_{DD} = 3.0 V$ to 5.5 V, unless otherwise specified.

| Symbol                                  | Parameter                                                                    | <b>Test Conditions</b>                                                            | Min                    | Тур  | Max                    | Units |

|-----------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------|------|------------------------|-------|

| $\overline{V_{DD}}$                     | Supply Voltage                                                               |                                                                                   | 3.0                    | _    | 5.5                    | V     |

| I <sub>DD</sub>                         | Supply Current, Operating                                                    | Pins 3, 5, 7 Open,<br>C <sub>F</sub> = 1μF, V <sub>IN</sub> = V <sub>(CMAX)</sub> | _                      | 0.5  | 1                      | mA    |

| I <sub>DD(SHDN)</sub>                   | Supply Current,<br>Shutdown Mode                                             | Pins 1,5, 6, 7 Open,<br>$C_F = 1 \mu F$ , $V_{MIN} = 0.35 V$ ,<br>Note 1          | _                      | 25   | _                      | μΑ    |

| I <sub>IN</sub>                         | V <sub>IN</sub> , V <sub>MIN</sub> Input Leakage                             | Note 1                                                                            | <b>– 1</b>             | _    | +1                     | μΑ    |

| V <sub>OUT</sub> Output                 |                                                                              |                                                                                   |                        |      |                        |       |

| t <sub>R</sub>                          | V <sub>OUT</sub> Rise Time                                                   | I <sub>OH</sub> = 5mA,<br>Note 1                                                  | _                      |      | 50                     | μsec  |

| t <sub>F</sub>                          | V <sub>OUT</sub> Fall Time                                                   | I <sub>OH</sub> = 1mA,<br>Note 1                                                  | _                      |      | 50                     | μѕес  |

| t <sub>SHDN</sub>                       | Pulse Width (On V <sub>MIN</sub> ) to Clear Fault Mode                       | V <sub>SHDN</sub> , V <sub>HYST</sub><br>Specifications                           | 30                     | _    | _                      | μsec  |

| I <sub>OL</sub>                         | Sink Current at V <sub>OUT</sub> Output                                      | $V_{OL}$ = 10% of $V_{DD}$                                                        | 1                      | _    | _                      | mA    |

| I <sub>OH</sub>                         | Source Current at V <sub>OUT</sub> Output                                    | $V_{OH} = 80\%$ of $V_{DD}$                                                       | 5                      | _    | _                      | mA    |

| V <sub>IN</sub> , V <sub>MIN</sub> Inpu | its                                                                          |                                                                                   |                        |      |                        |       |

| V <sub>C(MAX)</sub> , V <sub>OTF</sub>  | Input Voltage at V <sub>IN</sub> or V <sub>MIN</sub> for 100% PWM Duty Cycle |                                                                                   | 2.5                    | 2.65 | 2.8                    | V     |

| V <sub>C(SPAN)</sub>                    | $V_{C(MAX)} - V_{C(MIN)}$                                                    |                                                                                   | 1.3                    | 1.4  | 1.5                    | V     |

| V <sub>SHDN</sub>                       | Voltage Applied to V <sub>MIN</sub> to Shutdown Mode                         |                                                                                   | _                      | _    | V <sub>DD</sub> x 0.13 | V     |

| V <sub>REL</sub>                        | Voltage Applied to V <sub>MIN</sub> to Release Shutdown Mode                 | $V_{DD} = 5V$                                                                     | V <sub>DD</sub> x 0.19 | _    | _                      | V     |

| Pulse-Width                             | Modulator                                                                    |                                                                                   |                        |      |                        |       |

| F                                       | PWM Frequency                                                                | $C_F = 1.0 \mu F$                                                                 | 26                     | 30   | 34                     | Hz    |

| Sense Input                             |                                                                              | •                                                                                 |                        |      |                        |       |

| V <sub>TH</sub> (SENSE)                 | SENSE Input Threshold Voltage with Respect to GND                            |                                                                                   | 50                     | 70   | 90                     | mV    |

# **TC642**

# **ELECTRICAL CHARACTERISTICS (Cont.):** $T_{MIN} < T_A < T_{MAX}$ , $V_{DD} = 3.0 V$ to 5.5 V, unless otherwise specified.

| Symbol              | Parameter                      | Test Conditions         | Min  | Тур  | Max | Units |

|---------------------|--------------------------------|-------------------------|------|------|-----|-------|

| Fault Output        |                                |                         |      |      |     |       |

| $\overline{V_{OL}}$ | Output Low Voltage             | I <sub>OH</sub> = 2.5mA | _    | _    | 0.3 | V     |

| $\overline{t_{MP}}$ | Missing Pulse Detector Timeout | _                       | 32/F | _    | Sec |       |

| tstartup            | Startup Time                   |                         | _    | 32/F | _   | Sec   |

| T <sub>DIAG</sub>   | Diagnostic Timer Period        |                         | _    | 3/F  | _   | Sec   |

Note: 1. Guaranteed by design, not tested.

## PIN DESCRIPTION

| Pin No.<br>(PDIP/SOIC) | Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | V <sub>IN</sub>  | Analog input. The thermistor network (or other temperature sensor) connects to this input. A voltage range of 1.25V to 2.65V (typical) on this pin drives an active duty cycle of $0\%$ to $100\%$ on the $V_{OUT}$ pin.                                                                                                                                                                                                                                             |

| 2                      | C <sub>F</sub>   | Analog output. Positive terminal for the PWM ramp generator timing capacitor. The recommended $C_{\text{F}}$ is $1\mu\text{F}$ for 30Hz PWM operation.                                                                                                                                                                                                                                                                                                               |

| 3                      | V <sub>MIN</sub> | Analog input. An external resistor divider connected to this input sets the minimum fan speed by fixing the minimum PWM duty cycle (1.25V to 2.65V = 0% to 100%, typical). The TC642 enters Shutdown mode when $0 \le V_{MIN} \le V_{SHDN}$ . During Shutdown, the FAULT output is inactive, and supply current falls to $25\mu A$ (typical). The TC642 exits Shutdown mode when $V_{MIN} \ge V_{REL}$ . See <i>Applications</i> section for more details.           |

| 4                      | GND              | Ground Terminal.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5                      | SENSE            | Analog input. Pulses are detected at this pin as fan rotation chops the current through a sense resistor. The absence of pulses indicates a fault (FanSense $^{\text{TM}}$ ).                                                                                                                                                                                                                                                                                        |

| 6                      | FAULT            | Digital (open collector) output. This line goes low to indicate a fault condition. When FAULT goes low due to a fan fault, the device is latched in Shutdown Mode until deliberately cleared or until power is cycled. FAULT may be connected to V <sub>MIN</sub> if a hard shutdown is desired. FAULT will also be asserted when the PWM reaches 100% duty cycle, however the device will not latch itself off unless FAULT is tied to V <sub>MIN</sub> externally. |

| 7                      | V <sub>OUT</sub> | Digital output. This active high complimentary output connects to the base of an external NPN motor drive transistor. This output has asymmetrical drive See <i>Electrical Characteristics</i> section.                                                                                                                                                                                                                                                              |

| 8                      | $V_{DD}$         | Power Supply Input. May be independent of fan power supply. See <i>Electrical Characteristics</i> section.                                                                                                                                                                                                                                                                                                                                                           |

# DETAILED DESCRIPTION PWM

The PWM circuit consists of a ramp generator and threshold detector. The frequency of the PWM is determined by the value of the capacitor connected to the  $C_F$  input. A frequency of 30Hz is recommended ( $C_F = 1 \mu F$ ). The PWM is also the timebase for the startup and fault timer (see below). The PWM voltage control range is 1.25V to 2.65V (typical) for 0% to 100% output duty cycle.

# **V<sub>OUT</sub>** Output

The  $V_{OUT}$  pin is designed to drive a low-cost transistor or MOSFET as the low side power switching element in the system. Various examples of driver circuits will be shown below. This output has asymmetric complementary drive and is optimized for driving NPN transistors or N-channel MOSFET's. Since the system relies on PWM rather than linear power control, the dissipation in the power switch is kept to a minimum. Generally, very small devices (TO-92 or SOT package) will suffice.

## **TC642**

# **Start-Up Timer**

To ensure reliable fan start-up, the Start-Up Timer turns the  $V_{OUT}$  output on for 32 cycles of the PWM whenever the fan is started from the off state. This occurs at power-up and when coming out of Shutdown mode. If the PWM frequency is 30Hz ( $C_F=1\mu F$ ), the resulting start-up time will be about one second. If a Fault is detected (see below), the Diagnostic Timer is triggered once, followed by the Startup-Up Timer. If the fault persists, the device is shut down. See <code>FAULT Output</code> below.

# **Shutdown Control (Optional)**

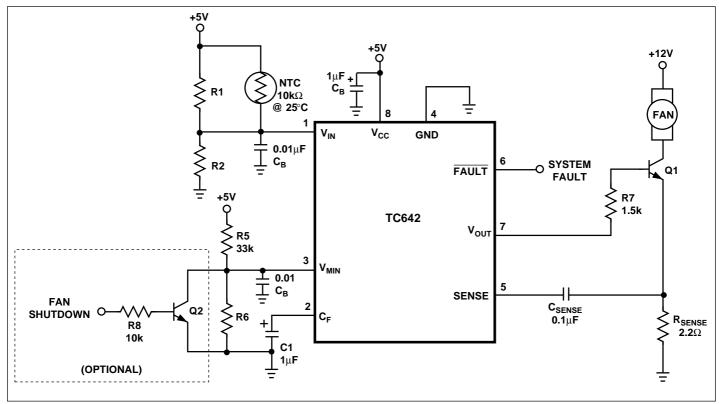

If  $V_{MIN}$ , pin 3, is pulled below  $V_{SHDN}$ , the TC642 will go into Shutdown mode. This can be accomplished by driving  $V_{MIN}$  with an open drain logic signal or using an external transistor as shown in Figure 1. All functions are suspended until the voltage on  $V_{MIN}$  becomes higher than  $V_{REL}$  (0.85V @  $V_{DD}$  = 5.0V). Pulling  $V_{MIN}$  below  $V_{SHDN}$  will always result in complete device shutdown and reset. The FAULT output is unconditionally inactive in Shutdown mode.

A small amount of hysteresis, typically one percent of  $V_{DD}$ , (50mV at  $V_{DD}$  = 5.0V) is designed into the  $V_{SHDN}/V_{REL}$  threshold. The levels specified for  $V_{SHDN}$  and  $V_{REL}$  in the *Electrical Characteristics* section include this hysteresis plus adequate margin to account for normal variations in the absolute value of the threshold and hysteresis.

**CAUTION:** Shutdown mode is unconditional. That is, the fan will not be activated regardless of the voltage on  $V_{\text{IN}}$ . The fan should not be shut down until all heat-producing activity in the system is at a negligible level.

# SENSE Input (FanSense<sup>™</sup>)

The SENSE input, pin 5, is connected to a low-value current sensing resistor in the ground return leg of the fan circuit. During normal fan operation, commutation occurs as each pole of the fan is energized. This causes brief interruptions in the fan current, seen as pulses across the sense resistor. If the device is not in Shutdown Mode and pulses are not appearing at the SENSE input, a fault exists.

The short, rapid change in fan current (high dl/dt) causes a corresponding dV/dt across the sense resistor,  $R_{\rm SENSE}$ . The waveform on  $R_{\rm SENSE}$  is differentiated and converted to a logic-level pulse-train by  $C_{\rm SENSE}$  and the internal signal processing circuitry. The presence and frequency of this pulse-train is a direct indication of fan operation. See the Applications section for more details.

# **FAULT Output**

The TC642 detects faults in two ways: (1) Pulses appearing at SENSE due to the PWM turning on

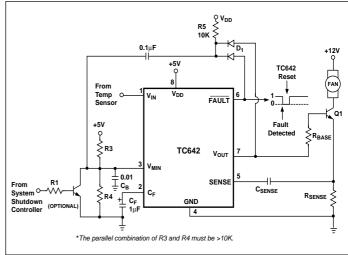

are blanked and the remaining pulses are filtered by a missing pulse detector. If consecutive pulses are not detected for 32 PWM cycles ( $\approx$ 1 Sec if C<sub>F</sub> = 1 $\mu$ F), the Diagnostic Timer is activated, and V<sub>OUT</sub> is driven continuously for three PWM cycles ( $\approx$ 100msec if C<sub>F</sub> = 1 $\mu$ F). If a pulse is not detected within this window, the Startup-Timer is triggered (see above). This should clear a transient fault condition. If the Missing Pulse Detector times out again, the PWM is stopped, and FAULT goes low. When FAULT is activated due to this condition, the device is latched in Shutdown mode and will remain off indefinitely. (Diodes D<sub>1</sub>, D<sub>2</sub> and resistor R5 are provided to ensure fan restarts are the result of a fan fault, and not an over-temperature fault. A CMOS logic OR gate may be substituted for these components if available).

When  $\overline{\text{FAULT}}$  is activated due to this condition, the device is latched in Shutdown mode and will remain off indefinitely. Important: At this point, action *must* be taken to restart the fan by momentarily pulling  $V_{\text{MIN}}$  below  $V_{\text{SHDN}}$ ; or cycling system power. In either case, the fan *cannot* remain disabled due to a fault condition as severe system damage could result. If the fan cannot be restarted, the system should be shut down. The TC642 may be configured to continuously attempt fan restarts if so desired.

Continuous restart mode is enabled by connecting the FAULT output to  $V_{\text{MIN}}$  through a 0.1µF capacitor as shown in Figure 1. When so connected, the TC642 automatically attempts to restart the fan whenever a fault condition occurs. When the fault output is driven low, the  $V_{\text{MIN}}$  input is momentarily pulled below  $V_{\text{SHDN}}$ , initiating a reset and clearing the fault condition, and normal fan startup is then attempted as previously described. The FAULT output may be connected to external logic (or the interrupt input of a microcontroller) to shut the TC642 down if multiple fault pulses are detected at approximately one second intervals.

Figure 1.

(2)  $\overline{\text{FAULT}}$  is also asserted when the PWM control voltage applied to  $V_{IN}$  becomes greater than that needed to drive 100% duty cycle (see *Electrical Characteristics*). This indicates that the fan is at maximum drive, and the potential exists for system overheating. Either heat dissipation in the system has gone beyond the cooling system's design limits, or some subtle fault exists such as fan bearing failure or an airflow obstruction. This output may be treated as a System Overheat warning and used to trigger system shutdown. However, in this case, the fan will continue to run even when  $\overline{\text{FAULT}}$  is asserted. If a shutdown is desired,  $\overline{\text{FAULT}}$  may be connected to  $V_{MIN}$  outside the device. This will latch the TC642 in Shutdown Mode when any fault occurs.

## SYSTEM BEHAVIOR

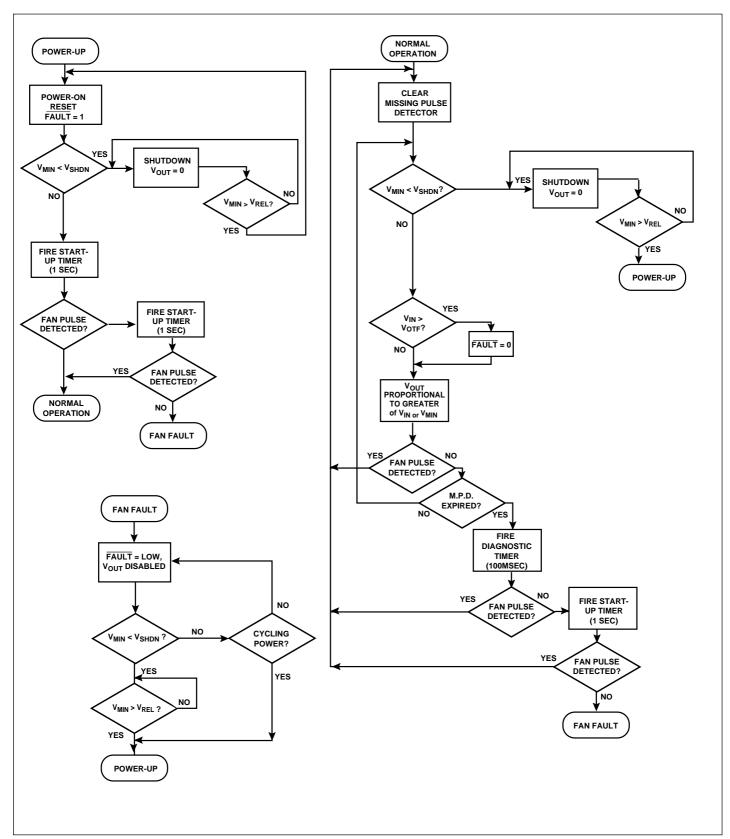

The flowcharts describing the TC642's behavioral algorithm are shown in Figure 3. They can be summarized as follows:

# Power-Up

- (1) Assuming the device is not being held in Shutdown mode ( $V_{MIN} > V_{REL}$ )...

- (2) Turn V<sub>OUT</sub> output on for 32 cycles of the PWM clock. This ensures that the fan will start from a dead stop.

- (3) During this Start-up Timer, if a fan pulse is detected, branch to Normal Operation; if none are received...

- (4) Activate the 32-cycle Start-up Timer one more time and look for fan pulse; if a fan pulse is detected, proceed to Normal Operation; if none are received...

- (5) Proceed to Fan Fault

- (6) End After this period elapses, the TC642 begins normal operation.

Figure 2. Typical Application Circuit

# **Normal Operation**

Normal Operation is an endless loop which may only be exited by entering Shutdown mode or Fan Fault. The loop can be thought of as executing at the frequency of the oscillator and PWM.

- (1) Reset the Missing Pulse Detector

- (2) Is TC642 in Shutdown? If so...

- a. V<sub>OUT</sub> duty-cycle goes to zero.

- b. FAULT is disabled.

- c. Exit the loop and wait for V<sub>MIN</sub> > V<sub>REL</sub> to resume operation (indistinguishable from Power-Up).

- (3) If an over-temperature fault occurs ( $V_{IN} > V_{OTF}$ ) then activate  $\overline{FAULT}$ ; release  $\overline{FAULT}$  when  $V_{IN} < V_{OTF}$ .

- (4) Drive  $V_{OUT}$  to a duty-cycle porportional to greater of  $V_{IN}$  and  $V_{MIN}$  on a cycle by cycle basis.

- (5) If a fan pulse is detected, branch back to the start of the loop (1).

- (6) If the missing pulse detector times out ...

- (7) Activate the 3-cycle Diagnostic Timer and look for pulses; if a fan pulse is detected, branch back to the start of the loop (1); if none are received...

- (8) Activate the 32-cycle Startup Timer and look for pulses; if a fan pulse is detected, branch back to the start of the loop (1); if none are received...

- (9) Quit Normal Operation and go to Fan Fault.

- (10) End

# **Fan Fault**

Fan Fault is essentially an infinite loop wherein the TC642 is latched in Shutdown Mode. This mode can only be released by a Reset, i.e.,  $V_{MIN}$  being brought below  $V_{SDHN}$ , then above  $V_{REL}$ , or by power-cycling.

- (1) While in this state,  $\overline{FAULT}$  is latched on (low), and the  $V_{OUT}$  output is disabled.

- (2) A Reset sequence applied to the  $V_{\text{MIN}}$  pin will exit the loop to Power Up.

- (3) End

# **TC642**

Figure 3. TC642 Behavioral Algorithm Flowchart

## APPLICATIONS INFORMATION

Designing with the TC642 involves the following:

- (1) The temp sensor network must be configured to deliver 1.25V to 2.65V on V<sub>IN</sub> for 0% to 100% of the temperature range to be regulated.

- (2) The minimum fan speed (V<sub>MIN</sub>) must be set.

- (3) The output drive transistor and associated circuitry must be selected.

- (4) The Sense Network, R<sub>SENSE</sub> and C<sub>SENSE</sub>, must be designed for maximum efficiency while delivering adequate signal amplitude.

- (5) If Shutdown capability is desired, the drive requirements of the external signal or circuit must be considered.

The TC642DEMO demonstration and prototyping board and the TC642EV Evaluation Kit provide working examples of TC642 circuits and prototyping aids. The TC642DEMO is a printed circuit board optimized for small size and ease of inclusion into system prototypes. The TC642EV is a larger board intended for benchtop development and analysis. At the very least, anyone contemplating a design using the TC642 should consult the documentation for both TC642EV and TC642DEMO.

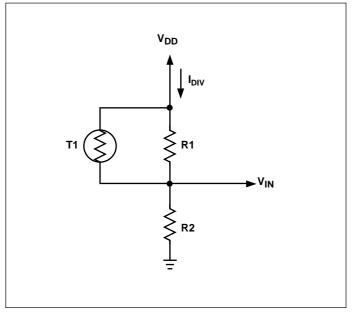

## **Temperature Sensor Design**

The temperature signal connected to  $V_{IN}$  must output a voltage in the range of 1.25V to 2.65V (typical) for 0% to 100% of the temperature range of interest. The circuit of Figure 4 is a convenient way to provide this signal.

Figure 4 illustrates a simple temperature dependent voltage divider circuit. T1 is a conventional NTC thermistor, and R1 and R2 are standard resistors. The supply voltage,  $V_{DD}$ , is divided between R2 and the parallel combination of T1 and R1. (For convenience, the parallel combination of T1 and R1 will be referred to as  $R_{TEMP}$ .) The resistance of the thermistor at various temperatures is obtained from the manufacturer's specifications. Thermistors are often referred to in terms of their resistance at 25°C. A thermistor with a 25°C resistance on the order of  $100k\Omega$  will result in reasonable values for R1, R2, and  $I_{DIV}$ . In order to determine R1 and R2, we must specify the fan duty-cycle, i.e.  $V_{IN}$ , at any two temperatures. Equipped with these two points on the system's operating curve and the thermistor data, we can write the defining equations:

$$\frac{V_{DD} \times R2}{R_{TEMP} (t1) + R2} = V(t1)$$

$$\frac{V_{DD} \times R2}{R_{TEMP} (t2) + R2} = V(t2)$$

Equaton 1.

Where t1 and t2 are the chosen temperatures and R<sub>TEMP</sub> is the parallel combination of the thermistor and R1. These two equations permit solving for the two unknown variables, R1 and R2. Note that resistor R1 is not absolutely necessary, but it helps to linearize the response of the network.

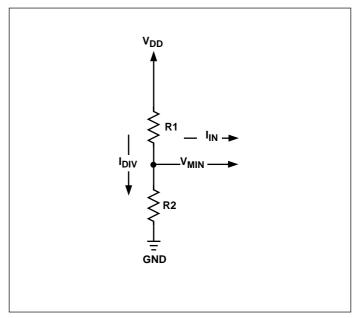

# Minimum Fan Speed

A voltage divider on  $V_{MIN}$  sets the minimum PWM duty cycle and, thus, the minimum fan speed. As with the  $V_{IN}$  input, 1.25V to 2.65V corresponds to 0% to 100% duty cycle. Assuming that fan speed is linearly related to duty-cycle, the minimum speed voltage is given by the equation:

$$V_{MIN} = \frac{Minimum\ Speed}{Full\ Speed} x (1.4V) + 1.25V$$

Equation 2.

For example, if 2500 RPM equates to 100% fan speed, and a minimum speed of 1000 RPM is desired, then the  $V_{\text{MIN}}$  voltage is:

$$V_{MIN} = \frac{1000}{2500} \times (1.4V) + 1.25V = 1.81V$$

## Equation 3.

The  $V_{MIN}$  voltage may be set using a simple resistor divider as shown in Figure 5. Per the *Electrical Characteristics*, the leakage current at the  $V_{MIN}$  pin is no more than 1 $\mu$ A. It would be very conservative to design for a divider current,  $I_{DIV}$ , of 100 $\mu$ A. If  $V_{DD}$  = 5.0V then...

$$I_{DIV} = 1e^{-4} A = \frac{5.0V}{R1 + R2}$$

, therefore

$$R1 + R2 = \frac{5.0V}{1e^{-4} A} = 50,000\Omega = 50k\Omega$$

Equation 4.

We can further specify R1 and R2 by the condition that the divider voltage is equal to our desired  $V_{\text{MIN}}$ . This yields the following equation:

# **TC642**

Figure 4. Temperature Sensing Circuit

Figure 5. V<sub>MIN</sub> Circuit

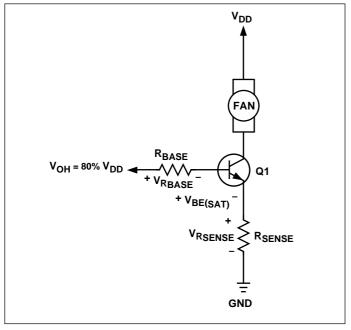

Figure 6. Circuit for Determining R<sub>BASE</sub>

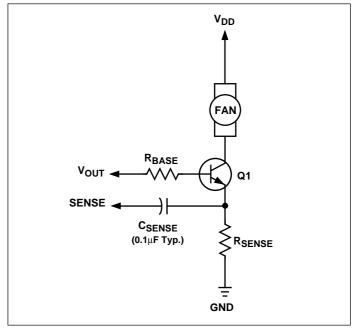

Figure 7. SENSE Network

$$V_{MIN} = V_{DD} x \frac{R2}{R1 + R2}$$

#### Equation 5.

Solving for the relationship between R1 and R2 results in the following equation:

$$R1 = R2 \times \frac{V_{DD} - V_{MIN}}{V_{MIN}}$$

### Equation 6.

In the case of this example, R1 = (1.762) R2. Substituting this relationship back into Equation 4 yields the resistor values:

R2 =18.1k

$$\Omega$$

, and R1 = 31.9k $\Omega$

In this case, the standard values of  $32k\Omega$  and  $18k\Omega$  are very close to the calculated values and would be more than adequate.

One boundary condition which may impact the selection of the minimum fan speed is the irregular activation of the Diagnostic Timer due to the TC642 "missing" fan commutation pulses at low speeds. Typically, this only occurs at very low duty-cycles (25% or less). It is a natural consequence of low PWM duty-cycles. Recall that the SENSE function detects commutation of the fan as disturbances in the current through  $R_{\text{SENSE}}$ . These can only occur when the fan is energized, i.e.,  $V_{\text{OUT}}$  is "on". At very low duty-cycles, the  $V_{\text{OUT}}$  output is "off" most of the time. The fan may be rotating normally, but the commutation events are occuring during the PWM's off-time.

The phase relationship between the fan's commutation and the PWM edges tends to "walk around" as the system operates. At certain points, the TC642 may fail to capture a pulse within the 32-cycle Missing Pulse Detector window. When this happens, the 3-cycle Diagnostic Timer will be activated, the  $V_{OUT}$  output will be active continuously for three cycles and, if the fan is operating normally, a pulse will be detected. If all is well, the system will return to normal operation. There is no harm in this behavior, but it may be audible to the user as the fan will accelerate briefly when the Diagnostic Timer fires. For this reason, it is recommended that  $V_{MIN}$  be set no lower than 1.8V.

# (FanSense<sup>™</sup>) Network (R<sub>SENSE</sub> and C<sub>SENSE</sub>)

The network comprised of  $R_{SENSE}$  and  $C_{SENSE}$  allow the TC642 to detect commutation of the fan motor (FanSense TM). This network can be thought of as a differentiator and threshold detector. The function of  $R_{SENSE}$  is to convert the © 2001 Microchip Technology Inc. DS21444A

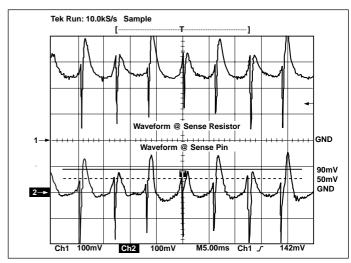

fan current into a voltage.  $C_{SENSE}$  serves to AC-couple this voltage signal and provide a ground-referenced input to the SENSE pin. Designing a proper SENSE Network is simply a matter of scaling  $R_{SENSE}$  to provide the necessary amount of gain, i.e., the current-to-voltage conversion ratio. A  $0.1\mu F$  ceramic capacitor is recommended for  $C_{SENSE}$ . Smaller values require larger sense resistors, and higher value capacitors are bulkier and more expensive. Using a  $0.1\mu F$  results in reasonable values for  $R_{SENSE}$ . Figure 7 illustrates a typical SENSE Network. Figure 8 shows the waveforms observed using a typical SENSE Network.

Table 1 lists the recommended values of  $R_{SENSE}$  according to the nominal operating current of the fan. Note that the current draw specified by the fan manufacturer may not be the fan's nominal operating current, but may be a worst-case rating for near-stall conditions. The values in the table refer to actual average operating current. If the fan current falls between two of the values listed, use the higher resistor value. The end result of employing Table 1 is that the signal developed across the sense resistor is approximately  $450 \, \text{mV}$  in amplitude.

Table 1. R<sub>SENSE</sub> vs. Fan Current

| Nominal Fan Current (mA) | $R_{SENSE}$ ( $\Omega$ ) |

|--------------------------|--------------------------|

| 50                       | 9.1                      |

| 100                      | 4.7                      |

| 150                      | 3.0                      |

| 200                      | 2.4                      |

| 250                      | 2.0                      |

| 300                      | 1.8                      |

| 350                      | 1.5                      |

| 400                      | 1.3                      |

| 450                      | 1.2                      |

| 500                      | 1.0                      |

Figure 8. SENSE Waveforms

# **TC642**

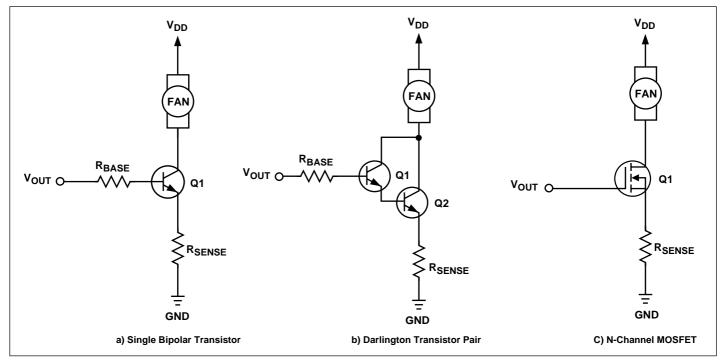

Figure 9. Output Drive Transistor Circuit Topologies

# **Output Drive Transistor Selection**

The TC642 is designed to drive an external transistor for modulating power to the fan. This is shown as "Q1" in Figures 2, 6, 7, 9, 10, and 11. The  $V_{OUT}$  pin has a minimum source current of 5mA and a minimum sink current of 1mA at  $V_{DD} = 5.0$ V. Bipolar transistors or MOSFET's may be used as the power switching element as shown below. When high current gain is needed to drive larger fans, two transistors may be used in a Darlington configuration. These circuit topologies are shown in Figure 9: (a) shows a single NPN transistor used as the switching element; (b) Illustrates the Darlington pair; and (c) shows an N-channel MOSFET.

One major advantage of the TC642's PWM control scheme versus linear speed control is that the dissipation in the pass element is kept very low. Generally, low-cost devices in very small packages such as TO-92 or SOT, can be used effectively. For fans with nominal operating currents of no more than 200mA, a single transistor usually suffices. Above 200mA, the Darlington or MOSFET solution is recommended. For the fan sensing function to work correctly, it is imperative that the pass transistor be fully saturated when "on". The minimum gain (hFE) of the transistor in question must be adequate to fully saturate the transistor when passing the full fan current and being driven within the 5mA  $I_{\rm OH}$  of the  $V_{\rm OUT}$  output.

Table 2 gives examples of some commonly available transistors. This table is a guide only. There are many

transistor types which might work as well as those listed. The only critical issues when choosing a device to use as Q1 are: (1) the breakdown voltage,  $V_{CE(BR)}$ , must be large enough to stand off the highest voltage applied to the fan (NOTE: this may be when the fan is off!); (2) the gain (hFE) must be high enough for the device to remain fully saturated while conducting the maximum expected fan current and being driven with no more than 5mA of base/gate drive at maximum temperature; (3) rated fan current draw must be within the transistor's current handling capability; and (4) power dissipation must be kept within the limits of the chosen device.

Table 2. Transistors for Q1

| 1 4 4 5 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 6 |                      |                     |                      |     |                       |  |

|-------------------------------------------|----------------------|---------------------|----------------------|-----|-----------------------|--|

| Device                                    | V <sub>BE(SAT)</sub> | MIN h <sub>FE</sub> | V <sub>BR(CEO)</sub> | Ic  | R <sub>BASE</sub> (Ω) |  |

| MPS2222                                   | 1.3                  | 100                 | 30                   | 150 | 800                   |  |

| MPS2222A                                  | 1.2                  | 100                 | 40                   | 150 | 800                   |  |

| 2N4400                                    | 0.95                 | 50                  | 40                   | 150 | 820                   |  |

| 2N4401                                    | 0.95                 | 100                 | 40                   | 150 | 820                   |  |

| MPS6601                                   | 1.2                  | 50                  | 25                   | 500 | 780                   |  |

| MPS6602                                   | 1.2                  | 50                  | 40                   | 500 | 780                   |  |

A base-current limiting resistor is required with bipolar transistors. This is shown in Figure 6. The correct value for this resistor can be determined as follows: (see Figure 6).

#### Equation 7.

$V_{OH}$  is specified as 80% of  $V_{DD}$  in the *Electrical Characteristics* table;  $V_{BE(SAT)}$  is given in the transistor datasheet. It is now possible to solve for  $R_{BASE}$ .

$$R_{BASE} = \frac{V_{OH} - V_{BE(SAT)} - V_{RSENSE}}{I_{RBASE}}$$

#### Equation 8.

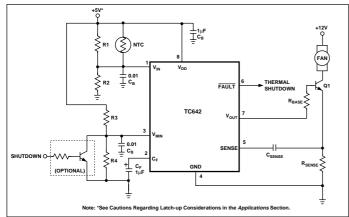

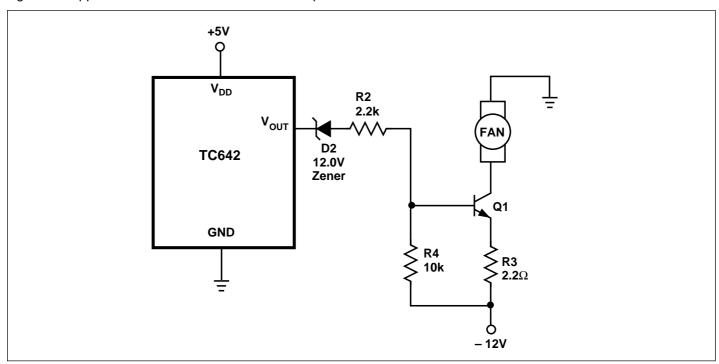

Some applications require the fan to be powered from the negative 12V supply to keep motor noise out of the positive voltage power supplies. As shown in Figure 10, Zener diode D2 offsets the -12V power supply voltage holding transistor Q1 OFF when  $V_{OUT}$  is LOW. When  $V_{OUT}$  is HIGH, the voltage at the anode of D2 increases by  $V_{OH}$ , causing Q1 to turn ON. Operation is otherwise the same as the case of fan operation +12V.

# **Latch-up Considerations**

As with any CMOS IC, the potential exists for latch-up if signals are applied to the device which are outside the power

supply range. This is of particular concern during power-up if the external circuitry, such as the sensor network,  $V_{MIN}$  divider, shutdown circuit, or fan, are powered by a supply different from that of the TC642. Care should be taken to ensure that the TC642's  $V_{DD}$  supply powers-up *first*. If possible, the networks attached to  $V_{IN}$  and  $V_{MIN}$  should connect to the  $V_{DD}$  supply at the same physical location as the IC itself. Even if the IC and any external networks are powered by the same supply, physical separation of the connecting points can result in enough parasitic capacitance and/or inductance in the power supply connections to delay one power supply "routing" versus another.

# **Power Supply Routing and Bypassing**

Noise present on the  $V_{IN}$  and  $V_{MIN}$  inputs may cause erroneous operation of the  $\overline{FAULT}$  output. As a result, these inputs should be bypassed with a  $0.01\mu F$  capacitor mounted as close to the package as possible. This is particularly true of  $V_{IN}$ , which usually is driven from a high impedance source (such as a thermistor). In addition, the  $V_{DD}$  input should be bypassed with a  $1\mu F$  capacitor. Grounds should be kept as short as possible. To keep fan noise off the TC642 ground pin, individual ground returns for the TC642 and the low side of the fan current sense resistor should be used.

Figure 10. Powering Fan From -12V Supply

# **TC642**

Figure 11. Design Example

# **Design Example (Figure 11)**

Step 1. Circulate R1 and R2 based on using an NTC having a resistance of  $4.6k\Omega$  at  $T_{MIN}$  and  $1.1k\Omega$  at  $T_{MAX}$ .

$R1 = 75k\Omega$  $R2 = 1k\Omega$

Step 2. Set minimum fan speed

$V_{MIN}$  = 1.8V Limit the divider current to 100 $\mu A$  from which R5 = 33k and R6 =  $18k\Omega$

# Step 3. Design the output circuit

Maximum fan motor current = 250mA. Q1 beta is chosen at 100 from which R7 =  $1.5k\Omega$

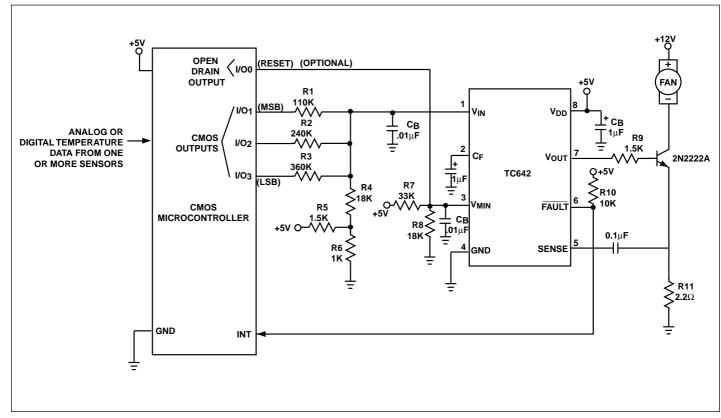

# TC642 as a Microcontroller Peripheral (Figure 12)

In a system containing a microcontroller or other host intelligence, the TC642 can be effectively managed as a CPU peripheral. Routine fan control functions can be performed by the TC642 without processor intervention. The micro-controller receives temperature data from one or more points throughout the system. It calculates a fan operating speed based on an algorithm specifically designed for the application at hand. The processor controls fan speed using complementary port bits I/01 through I/03. Resistors R1 through R6 (5% tolerance) form a crude 3-bit DAC that translates the 3-bit code from the processor's outputs into a 1.6V DC control signal. (A monolithic DAC or digital pot may be used instead of the circuit shown.)

With V<sub>MIN</sub> set to 1.8V, the TC642 has a minimum operating speed of approximately 40% of full rated speed when the processor's output code is 000[B]. Output codes 001[B] to 111[B] operate the fan from roughly 40% to 100% of full speed. An open drain output from the processor can be used to rese<u>t the T</u>C642 following detection of a fault condition. The FAULT output can be connected to the processor's interrupt input, or to an I/O pin for polled operation.

12

Figure 12

# **TC642**

#### **PACKAGE DIMENSIONS**

Trademarks: The Microchip name, logo, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, KEELOQ, SEEVAL, MPLAB and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. Total Endurance, ICSP, In-Circuit Serial Programming, FilterLab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM, MPLINK, MPLIB, PICDEM, ICEPIC, Migratable Memory, FanSense, ECONOMONITOR and SelectMode are trademarks and SQTP is a service mark of Microchip in the U.S.A.

All other trademarks mentioned herein are the property of their respective companies.

# WORLDWIDE SALES AND SERVICE

### **AMERICAS**

#### **Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Austin

Analog Product Sales 8303 MoPac Expressway North Suite A-201 Austin, TX 78759 Tel: 512-345-2030 Fax: 512-345-6085

#### **Boston**

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### **Boston**

Analog Product Sales Unit A-8-1 Millbrook Tarry Condominium 97 Lowell Road Concord, MA 01742 Tel: 978-371-6400 Fax: 978-371-0050

# Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

# Davton

Two Prestige Place, Suite 130 Miamisburg, OH 45342 Tel: 937-291-1654 Fax: 937-291-9175

#### **Detroit**

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

### Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612 Tel: 949-263-1888 Fax: 949-263-1338

# **Mountain View**

Analog Product Sales 1300 Terra Bella Avenue Mountain View, CA 94043-1836 Tel: 650-968-9241 Fax: 650-967-1590

#### **New York**

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### **Toronto**

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

#### China - Beijing

Microchip Technology Beijing Office New China Hong Kong Manhattan Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Shanghai

Microchip Technology Shanghai Office Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

### Hong Kong

Microchip Asia Pacific RM 2101, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 India

Microchip Technology Inc. India Liaison Office Divyasree Chambers 1 Floor, Wing A (A3/A4) No. 11, OíShaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Intl. Inc. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea Tel: 82-2-554-7200 Fax: 82-2-558-5934

### ASIA/PACIFIC (continued)

#### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850

#### Taiwan

Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### **EUROPE**

#### Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

#### Denmark

Microchip Technology Denmark ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

Arizona Microchip Technology SARL Parc díActivite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

#### Germany

Arizona Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

### Germany

Analog Product Sales Lochhamer Strasse 13 D-82152 Martinsried, Germany Tel: 49-89-895650-0 Fax: 49-89-895650-22

Arizona Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### **United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

All rights reserved. © 2001 Microchip Technology Incorporated. Printed in the USA. 1/01

01/09/01

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchipis products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, except as maybe explicitly expressed herein, under any intellectual property rights. The Microchip logo and name are registered trademarks of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.