# **CMX975** 2.7GHz Up/Down-converter, LNA, Dual PLL + VCO

Click here for:

# CMX975 2.7GHz Tx/Rx Mixers, LNA, RF Frac-N Synth, IF Integer-N Synth + VCOs

D/975/3 December 2019

# DATASHEET

**Provisional Information**

# Features

- 1 to 2.7 GHz Up/Down-converter

- Configurable image reject or normal mode Rx mixer Configurable sideband suppression or normal mode Tx mixer

- Combine with CMX973 to implement RF-to-I/Q transceiver

- 1 to 2.7 GHz RF / 10 to 500 MHz IF

- Integrated LNA 1.7dB noise figure at 1.5GHz 18dB programmable gain range

- RF synthesiser/PLL • Fractional-N 24-bit divider Output range 350MHz – 3.6GHz Programmable output divider Fast lock function Programmable charge pump current

- IF synthesiser/PLL Integer-N 14-bit divider Output range 31MHz – 1GHz Programmable output divider

- -209dBc/Hz normalised phase noise

- Integrated low noise LDO regulator

- Single 2.7V to 3.6V supply

- 1.8V digital interface supported

- C-BUS configurable •

- -40° to +85° operating temp. range

- Small outline 6mm x 6mm VQFN package

# Applications

- L-Band / S-Band satcom •

- Military radio

- Wireless microphone

- 2.4GHz ISM transceiver

- Wireless modem

- General purpose RF / IF

# **1** Brief Description

Section

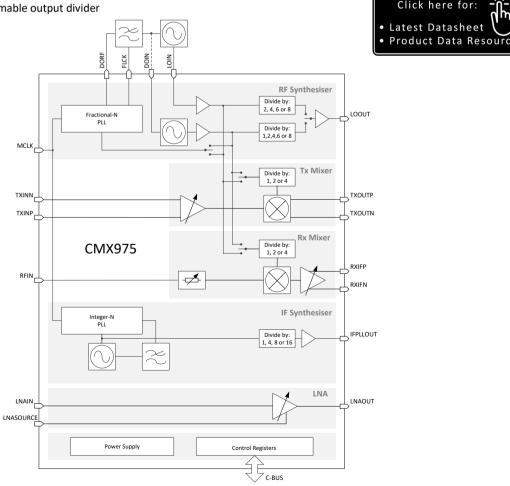

The CMX975 is an RF building block IC that provides multiple functions consisting of: RF PLL/VCO, IF PLL/VCO, Transmit Up-convert mixer, Rx Down-convert mixer, and LNA.

The RF high frequency synthesiser employs a Fractional-N design and will operate at up to 3.6GHz using a fully-integrated internal VCO or at up to 6GHz with an external frequency source. The IF synthesiser employs an integer-N design and will operate at up to 1GHz. It has an integrated VCO requiring only an external inductor to set the frequency. Internal dividers and buffers are provided for each synthesiser/PLL allowing a wide range of frequency generation options.

The Rx mixer can be configured in image reject or normal mode and the Tx mixer can be configured in sideband suppression or normal mode. The integrated LNA offers 18dB of gain reduction in three steps of 6dB.

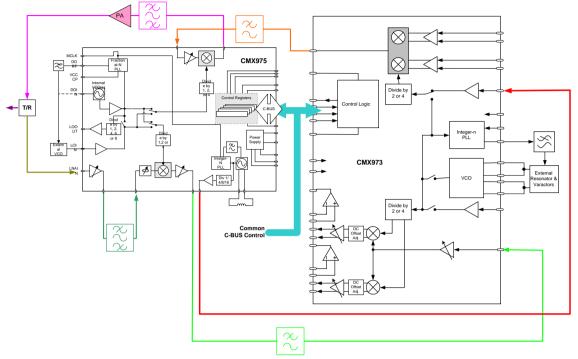

The CMX975 has been designed to work with CML's CMX973 Quadrature Modulator/Demodulator to provide a simple and cost effective high-frequency superhet transceiver operating in the range 1 to 2.7 GHz. The device operates from a single supply voltage and is available in a small 6x6mm VQFN package.

#### CONTENTS

## Page

| 1     | Brief Description                |    |

|-------|----------------------------------|----|

| 1.1   | History                          | 5  |

| 2     | Block Diagram                    | 6  |

| 3     | Performance Specification        | 7  |

| 3.1   | Electrical Performance           | 7  |

| 3.1.1 | Absolute Maximum Ratings         | 7  |

| 3.1.2 | Operating Limits                 | 7  |

| 3.1.3 | Operating Characteristics        |    |

| 4     | Pin and Signal Definitions       |    |

| 4.1   | Pin List                         |    |

| 4.2   | Signal Definitions               |    |

| 5     | Power Supply and Decoupling      |    |

| 6     | Layout Recommendations           |    |

| 7     | Detailed Description             |    |

| 7.1   | Power Management                 | 22 |

| 7.2   | Clock Generator                  |    |

| 7.3   | Tx (Up-conversion) Mixer         | 22 |

| 7.3.1 | Matching Circuits                | 25 |

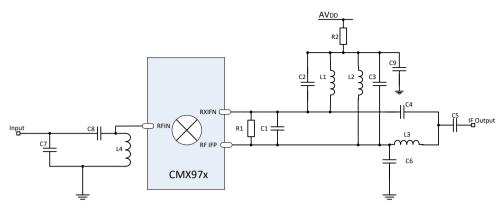

| 7.4   | Rx (Down-conversion) Mixer       | 27 |

| 7.4.1 | Matching Circuits                | 29 |

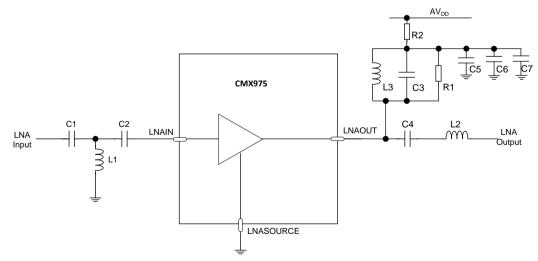

| 7.5   | Low Noise Amplifier (LNA)        |    |

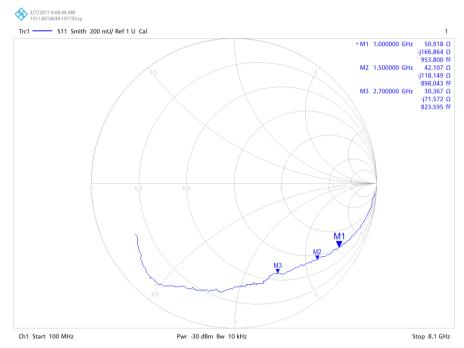

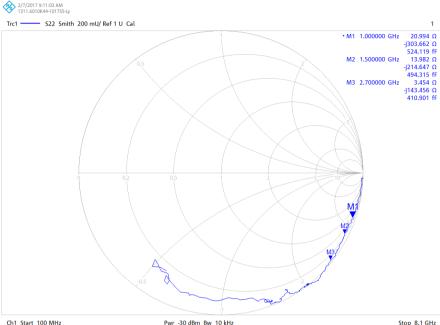

| 7.5.1 | LNA S-parameters                 | 31 |

| 7.5.2 | Matching Circuits                |    |

| 7.6   | RF VCO and Fractional-N PLL      |    |

| 7.6.1 | RF Fractional-N Synthesiser      |    |

| 7.6.2 | Register Loading Order           |    |

| 7.6.3 | Fractional-N Programming Example |    |

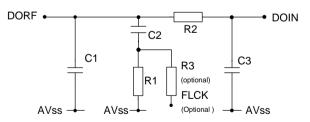

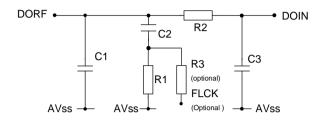

| 7.6.4 | Loop Filter                      | 35 |

| 7.6.5 | RF VCO                           |    |

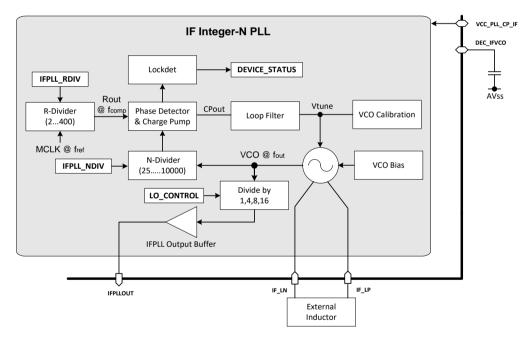

| 7.7   | IF PLL and VCO                   |    |

| 7.7.1 | IF PLL                           |    |

| 7.7.2 | Programming Example              |    |

| 7.7.3 | IF VCO                           |    |

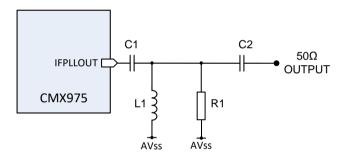

| 7.7.4 | IF PLL Output                    | 40 |

| 7.7.5 | IF PLL Divider                   | 40 |

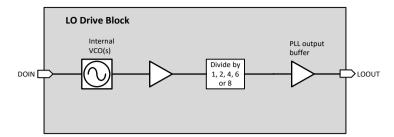

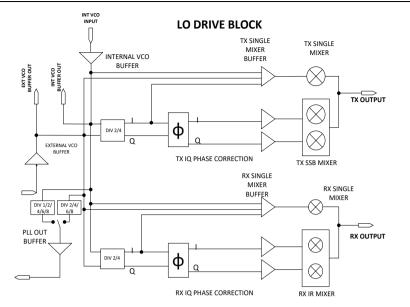

| 7.8   | Local Oscillator (LO)            | 41 |

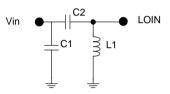

| 7.8.1 | LO Input (LOIN)                  | 43 |

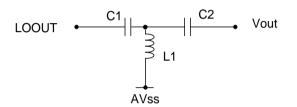

| 7.8.2 | LO Output (LOOUT)                | 43 |

| 7.8.3<br>7.9   | Dividers and LO Output<br>Status and Interrupts |    |

|----------------|-------------------------------------------------|----|

| -              | Register Description and C-BUS Interface        |    |

| 8              |                                                 |    |

| 8.1<br>8.1.1   | General Reset Command<br>GEN RST - \$30         |    |

| -              | General Control Register                        |    |

| 8.2            | -                                               |    |

| 8.2.1          | GCR - \$31                                      |    |

| 8.2.2          | GCR_RD - \$C1                                   |    |

| 8.3<br>8.3.1   | Rx Control Register                             |    |

|                | RX_CON - \$32<br>RX_CON_RD - \$C2               |    |

| 8.3.2          |                                                 |    |

| 8.4<br>8.4.1   | Tx Control Register<br>TX CON - \$33            |    |

| 8.4.1<br>8.4.2 | TX_CON RD - \$C3                                |    |

|                | TX_CON_RD - \$C3<br>RF PLL                      |    |

| 8.5<br>2 F 1   |                                                 |    |

| 8.5.1          | RFPLL_CON - \$34                                |    |

| 8.5.2          | RFPLL_BLEED - \$35                              |    |

| 8.5.3          | RFPLL_LOCKDET - \$36                            |    |

| 8.5.4          | RFPLL_FLCK - \$37                               |    |

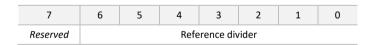

| 8.5.5          | RFPLL_RDIV - \$38                               |    |

| 8.5.6          | RFPLL_IDIV - \$39                               |    |

| 8.5.7          | RFPLL_FDIVO - \$3A                              |    |

| 8.5.8          | RFPLL_FDIV1 - \$38                              |    |

| 8.5.9          | RFPLL_RDIV_RD - \$C8                            |    |

| 8.5.10         | RFPLL_IDIV_RD - \$C9                            |    |

| 8.5.11         | RFPLL_FDIV0_RD - \$CA                           |    |

| 8.5.12         | RFPLL_FDIV1_RD - \$CB                           |    |

| 8.6            | IF PLL                                          |    |

| 8.6.1          | IFPLL_NDIV - \$3C                               |    |

| 3.6.2          | IFPLL_RDIV - \$3D                               |    |

| 3.6.3          | IFPLL_CURRENT - \$3E                            |    |

| 3.6.4          | IFPLL_NDIV_RD - \$CC                            | 55 |

| .6.5           | IFPLL_RDIV_RD - \$CD                            |    |

| .6.6           | IFPLL_CURRENT_RD - \$CE                         | 55 |

| .7             | VCO Calibration                                 | 55 |

| .7.1           | VCO_CAL_CTRL - \$50                             | 55 |

| .7.2           | VCO_BIAS_CAL_WRITE - \$51                       | 56 |

| .7.3           | VCO_BIAS_CAL_TIME - \$52                        | 56 |

| .7.4           | RFVCO_CAL_WRITE - \$53                          | 56 |

| 8.7.5          | RFVCO CAL COUNT - \$54                          | 57 |

| 3.7.6          | RFVCO_CAL_TIME - \$55                           | 57 |

| .7.7           | RFVCO STARTUP TIME - \$56                       |    |

| .7.8           | IFVCO CAL WRITE - \$57                          |    |

| .7.9           | IFVCO_CAL_COUNT - \$58                          |    |

| .7.10          | IFVCO_CAL_TIME - \$59                           |    |

| 3.7.11         | IFVCO_STARTUP_TIME - \$5A                       |    |

| .7.12          | VCO_BIAS_CAL_READ - \$5B                        |    |

| .7.12          | RFVCO_CAL_READ - \$5C                           |    |

| .7.13          | IFVCO_CAL_READ - \$50                           |    |

| .7.14          | VCO_CAL_KLAD - \$50                             |    |

| .8             | LO Control                                      |    |

| .8<br>.8.1     | LO_CONTROL - \$3F                               |    |

| 3.8.1<br>3.8.2 | LO_CONTROL - \$3F<br>LO_CONTROL_RD - \$CF       |    |

|                |                                                 |    |

| 8.9<br>8.9.1   | Device Status Register<br>DEVICE STATUS - \$C4  |    |

|                | -                                               |    |

| 8.10<br>10.1   | Interrupt Enable Register                       |    |

| 8.10.1         | IRQ_ENABLE - \$C5                               |    |

| 3.11           | Power Status Register                           |    |

| 8.11.1         | POWER_STATUS - \$C6                             |    |

| )              | Application Notes                               | 63 |

| 9.1            | Typical Transceiver Configuration               | 63 |

| 9.2            | Loop Filter Design                              | 64 |

| 9.2.1 | RF PLL (Fractional N)          | 64 |

|-------|--------------------------------|----|

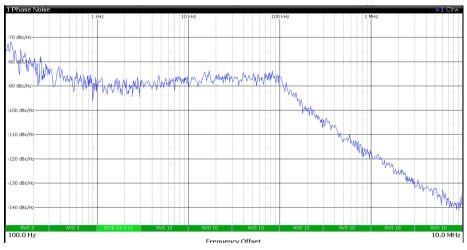

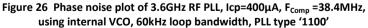

| 9.3   | Phase Noise Performance        | 65 |

| 9.3.1 | RF PLL                         | 65 |

| 9.3.2 | IF PLL Phase Noise             |    |

| 9.4   | RF PLL Lock Time               | 69 |

| 9.5   | RF PLL Spurious                | 70 |

| 9.5.1 | Types of Spurious              | 70 |

| 9.5.2 | MCLK Sidebands                 | 70 |

| 9.5.3 | Comparison Frequency Sidebands |    |

| 9.5.4 | MCLK Boundaries                |    |

| 9.5.5 | FComp Boundaries               | 70 |

| 9.5.6 | Higher Order Boundaries        | 71 |

| 9.6   | IF PLL Spurious                | 71 |

| 10    | Packaging                      |    |

| 10.1  | Ordering Information           | 72 |

|       |                                |    |

# <u>Table</u>

# <u>Page</u>

| Table 1 Definition of Power Supplies                                                          |    |

|-----------------------------------------------------------------------------------------------|----|

| Table 2 Power Supply and Decoupling Component Values                                          |    |

| Table 3 Tx Mixer Input Impedances and Parallel Equivalent Circuit (Normal mode)               | 23 |

| Table 4 Tx Mixer Output Differential Impedances and Parallel Equivalent Circuit (Normal mode) | 24 |

| Table 5 Tx Mixer Input Differential Impedances and Parallel Equivalent Circuit (SSB mode)     |    |

| Table 6 Tx Mixer Output Differential Impdances and Parallel Equivalent Circuit (SSB mode)     | 25 |

| Table 7 Tx Normal Mixer Matching Components                                                   |    |

| Table 8 Tx Single Sideband Mixer Matching Components                                          |    |

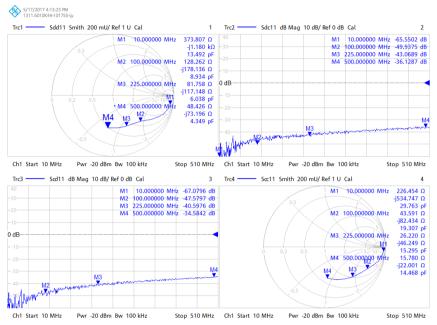

| Table 9 Rx Mixer Input Impedances and Parallel Equivalent Circuit                             |    |

| Table 10 Rx Mixer Output Impedances and Parallel Equivalent Circuit                           |    |

| Table 11 Normal Mixer Mode Components                                                         |    |

| Table 12 Image Reject Mixer Mode Components                                                   |    |

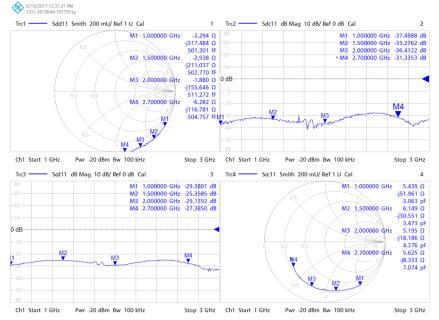

| Table 13 LNA Input Impedances and Parallel Equivalent Circuit                                 |    |

| Table 14 LNA Output Impedances and Parallel Equivalent Circuit                                |    |

| Table 15 LNA Components                                                                       |    |

| Table 16 3rd Order Loop Filter Example Values                                                 |    |

| Table 17 External Inductor Values for IF Centre Frequencies                                   |    |

| Table 18 Typical Matching Components for 900MHz (850 to 950 MHz)                              | 40 |

| Table 19 IF VCO Divider Settings                                                              |    |

| Table 20 LO Connections                                                                       |    |

| Table 21 LOIN Match Components                                                                |    |

| Table 22 RF VCO Frequency Limits with LO Output Divider Value                                 |    |

| Table 23 LOOUT Matching Typical Values                                                        |    |

| Table 24 RF Internal VCO Frequency Limits with LO Output Divider Value                        |    |

| Table 25 C-BUS Register Map                                                                   | 46 |

# Figure

# Page

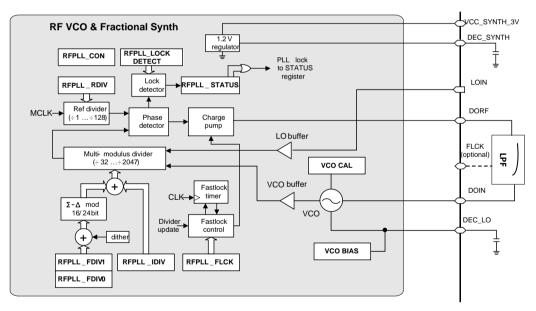

| Figure 17 Fractional-N Frequency Synthesiser                                                                              | 33              |

|---------------------------------------------------------------------------------------------------------------------------|-----------------|

| Figure 17 Fractional Torrequeries Synthesiser                                                                             |                 |

| Figure 19 IF PLL Architecture                                                                                             |                 |

| Figure 20 Typical Matching Values for 900MHz (850 to 950 MHz)                                                             |                 |

| Figure 21 LOIN Match Components                                                                                           |                 |

| Figure 22 LO Drive Block Schematic                                                                                        |                 |

| Figure 22 LO Drive Block Schematic                                                                                        |                 |

|                                                                                                                           |                 |

| Figure 24 LO Drive Block Schematic                                                                                        |                 |

| Figure 25 Typical Application Configuration                                                                               |                 |

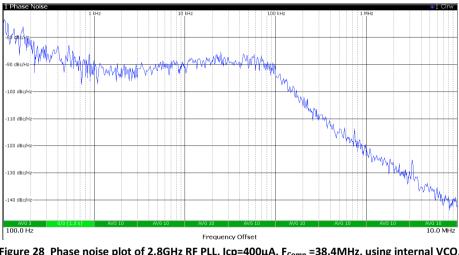

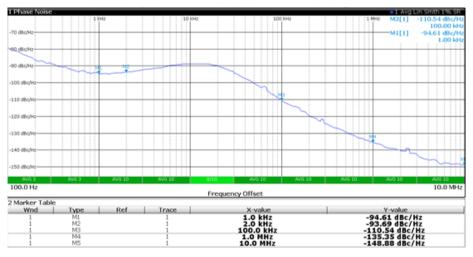

| Figure 26 Phase noise plot of 3.6GHz RF PLL, Icp=400μA, F <sub>Comp</sub> =38.4MHz, using internal VCO, 60kHz loop bandv  |                 |

| '1100'                                                                                                                    |                 |

| Figure 27 Phase noise plot of 3.201GHz RF PLL, Icp=400µA, F <sub>Comp</sub> =38.4MHz, using internal VCO, 60kHz loop ban  |                 |

| '1100' also showing output in /2 mode (1600MHz), /4 mode (800MHz) and /8 mode (400MHz)                                    |                 |

| Figure 28 Phase noise plot of 2.8GHz RF PLL, Icp=400μA, F <sub>Comp</sub> =38.4MHz, using internal VCO, 60kHz loop bandv  |                 |

| '1100'                                                                                                                    |                 |

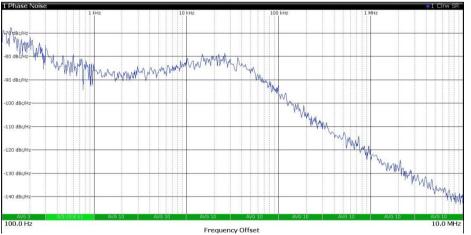

| Figure 29 Phase noise plot of 2.8GHz RF PLL, Icp=400μA, FComp =19.2MHz, using internal VCO, PLL type '1100'.              |                 |

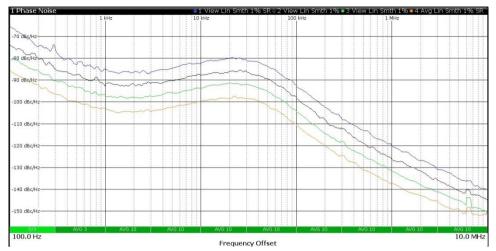

| Figure 30 Phase noise plot of 3.2GHz RF PLL, Icp=400µA, FComp =19.2MHz, using internal VCO, 60kHz loop band               |                 |

| '1100' also showing output in /2 mode (1600MHz), /4 mode (800MHz) and /8 mode (400MHz)                                    |                 |

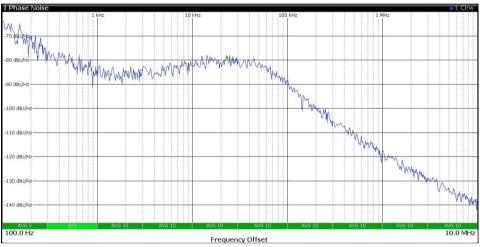

| Figure 31 Phase noise plot of 3.6GHz RF PLL, Icp=400μA, FComp =19.2MHz, using internal VCO, PLL type '1100'.              |                 |

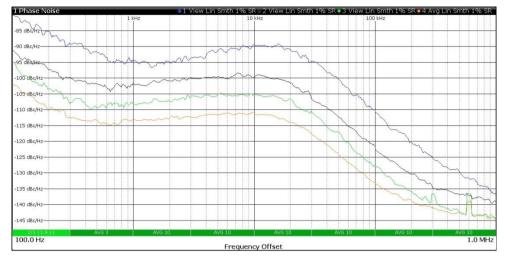

| Figure 32 Phase noise plot of 900MHz IF PLL, Icp=400µA, F <sub>Comp</sub> =1.2MHz, Kvco=10MHz/V                           |                 |

| Figure 33 Phase noise plot of 900 MHz IF PLL, Icp= 400μA, FComp =1.2MHz, also showing the effects of selecting            |                 |

| /8 (112.5MHz) and /16 (56.25 MHz) outputs                                                                                 |                 |

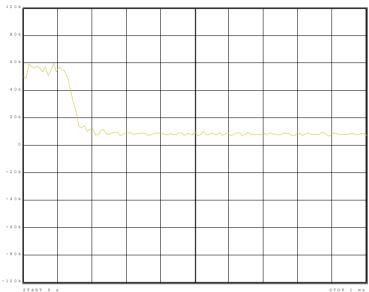

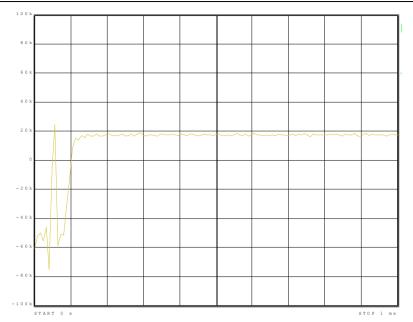

| Figure 34 Lock time for frequency change 2.850GHz to 3.450GHz, Icp=400µA, F <sub>Comp</sub> =19.2MHz, using internal VC   |                 |

| bandwidth, PLL type '1100', without Fastlock function, Jump =300µs                                                        |                 |

| Figure 35 Lock time for frequency change 2.850GHz to 3.450GHz, Icp=400µA, F <sub>Comp</sub> =19.2MHz, using internal VC   | CO , 60kHz loop |

| bandwidth, PLL type '1100', with Fastlock function (x12, 100µs), Jump =200µs                                              | 69              |

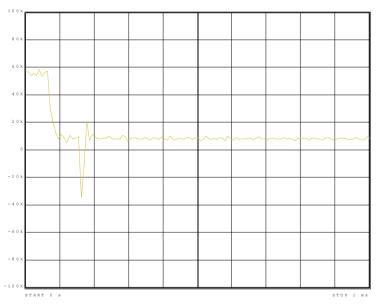

| Figure 36 Lock time for frequency change 3.205 to 3.195GHz, Icp=400µA, F <sub>Comp</sub> =19.2MHz, using internal VCO , 6 | 50kHz loop      |

| bandwidth, PLL type '1100', without Fastlock function, Jump = 150µs                                                       |                 |

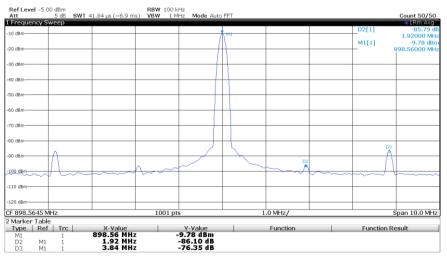

| Figure 37 Reference spur plot of 900MHz IF PLL                                                                            | 71              |

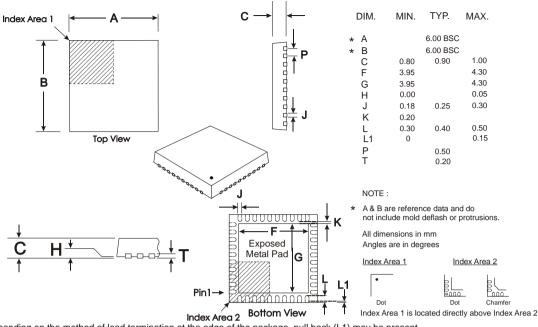

| Figure 38 Q4 Mechanical Outline                                                                                           | 72              |

|                                                                                                                           |                 |

# 1.1 History

| Version | Changes                                | Date          |

|---------|----------------------------------------|---------------|

|         |                                        |               |

| 3       | Section 10: Updated Q4 package diagram | December 2019 |

| 2       | Document updated to Provisional status | March 2018    |

| 1       | First public release                   | December 2017 |

This is Provisional Information; changes and additions may be made to this specification. Parameters marked TBD or left blank will be included in later issues. Items that are highlighted or greyed out should be ignored. These will be clarified in later issues of this document. Information in this datasheet should not be relied upon for final product design.

# 2 Block Diagram

Figure 1 CMX975 Block Diagram

$\ensuremath{\textcircled{}^{\odot}}$  2019 CML Microsystems Plc

# 3 Performance Specification

# 3.1 Electrical Performance

# 3.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

|                                                                                       | Min.                                                        | Max.                    | Units   |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------|---------|

| Supply $(AV_{DD} - AV_{SS})$ or $(DV_{DD} - DV_{SS})$ or                              | -0.3                                                        | +4.0                    | V       |

| (CPV <sub>DD</sub> - AV <sub>SS</sub> )                                               | -0.5                                                        | +4.0                    | v       |

| Voltage on any pin to AV <sub>ss</sub> or DV <sub>ss</sub>                            | -0.3                                                        | *V <sub>max</sub> + 0.3 | V       |

| Voltage between AV <sub>ss</sub> pins and DV <sub>ss</sub>                            | -50                                                         | +50                     | mV      |

| Voltage between AV <sub>DD</sub> and CPV <sub>DD</sub>                                | -0.3                                                        | +0.3                    | V       |

| Current into or out of pins:                                                          | -75                                                         | +75                     | mA      |

| connected to $AV_{DD}$ , $AV_{DDTX_{J}}AV_{SS}$ , $DV_{DD}$ , $DV_{SS}$ or $CPV_{DD}$ | -75                                                         | 775                     | IIIA    |

| any other pin                                                                         | -30                                                         | +30                     | mA      |

| * Vmax The maximum value of the supplies $DV_{DD}$ , $AV_{DD}$ , $AV_{DD}$            | $_{\text{DTX},}$ CPV $_{\text{DD1}}$ and CPV $_{\text{DI}}$ | 02                      |         |

| Q4 Package                                                                            | Min.                                                        | Max.                    | Units   |

| Total Allowable Power Dissipation at T <sub>AMB</sub> = 25°C                          | _                                                           | 1820                    | mW      |

| Derating (see Nate below)                                                             |                                                             | 10.0                    | m)///°C |

| Derating (see Note below)                                    | -                  | 18.2             | mW/°C      |

|--------------------------------------------------------------|--------------------|------------------|------------|

| Storage Temperature                                          | -55                | +125             | °C         |

| Operating Temperature                                        | -40                | +85              | °C         |

| Note: Junction-to-ambient thermal resistance is dependent on | board layout and m | ounting arranger | nents. The |

derating factor stated will be better than this with good connection between the device and a ground plane or heat sink.

# 3.1.2 Operating Limits

|                                                            | Notes | Min. | Max. | Units |

|------------------------------------------------------------|-------|------|------|-------|

| Analogue Supply (AV <sub>DD</sub> – AV <sub>SS</sub> )     |       | 2.7  | 3.6  | V     |

| Charge Pump Supply (CPV <sub>DD</sub> – AV <sub>ss</sub> ) |       | 2.7  | 3.6  | V     |

| Digital Supply (DV <sub>DD</sub> – DV <sub>SS</sub> )      |       | 1.7  | 3.6  | V     |

| Operating Temperature (see Note above)                     |       | -40  | +85  | °C    |

#### 3.1.3 Operating Characteristics

# 3.1.3.1 DC Parameters

For the following conditions unless otherwise specified:

$AV_{DD} = CPV_{DD} = 2.7V$  to 3.6V;  $DV_{DD} = 1.7V$  to 3.6V;  $AV_{SS} = DV_{SS} = 0V$ ; and  $T_{AMB} = +25^{\circ}C$ . External components and values as shown in section 7.5.2.

| DC Parameters                                      | Notes | Min. | Тур. | Max. | Units            |

|----------------------------------------------------|-------|------|------|------|------------------|

| Total Current Consumption                          |       |      |      |      |                  |

| Power save mode                                    | 1     | -    | 64   | _    | μΑ               |

| V <sub>BIAS</sub> only                             | 3     | -    | 1    | -    | mA               |

| Operating Currents                                 |       |      |      |      |                  |

| Tx mixer, normal mode with LO input                | 7     | -    | 40   | _    | mA               |

| Tx mixer, image reject mode with LO input          | 7     | -    | 90   | -    | mA               |

| Rx mixer normal mode with LO input                 | 7     | -    | 30   | _    | mA               |

| Rx mixer, image reject mode with LO input          | 7     | -    | 40   | -    | mA               |

| Rx LNA                                             |       | -    | 9.5  | -    | mA               |

| RF Synth Only (LO input)                           |       | -    | 20   | -    | mA               |

| RF Synth + VCO                                     |       | -    | 30   | _    | mA               |

| IF Synth + VCO                                     |       | -    | 8    | 13   | mA               |

| RF LO Output (Divide by 1, minimum bias)           | 5     | -    | 4.5  | _    | mA               |

| RF LO Output (Divide by 8, maximum bias)           | 5     | -    | 14   | _    | mA               |

| IF LO Divider                                      | 5a    |      | 0.9  |      | mA               |

| Current from DV <sub>DD</sub>                      | 2     | -    | 630  | 900  | μA               |

| Logic "1" Input Level                              |       | 70%  | -    | -    | DV <sub>DD</sub> |

| Logic 'O' Input Level                              |       | -    | -    | 30%  | DV <sub>DD</sub> |

| Output Logic '1' Level (I <sub>OH</sub> = 0.6 mA)  |       | 80%  | -    | -    | DV <sub>DD</sub> |

| Output Logic 'O' Level (I <sub>OL</sub> = -1.0 mA) |       | -    | _    | +0.4 | V                |

| External Bias Voltage (V <sub>BIAS</sub> )         | 6     | -    | 1.2  | -    | V                |

| Power up time                                      |       |      |      |      |                  |

| Voltage Reference                                  | 4     | -    | -    | 0.5  | ms               |

| All blocks except Voltage Reference                | 4     | -    | _    | 10   | μs               |

Notes:

3. The stated current drawn here is with the bandgap reference and accompanying bias current generators enabled only, all other circuitry is disabled.

4. As measured from the rising edge of CSN.

- 5. Additional current when LO Output (to LOOUT pin) is enabled.

- 5a. Additional current when IF LO output divider is enabled, independent of division ratio.

- 6. R1 = 47.5k $\Omega$ , as shown in Figure 4.

7. LO divide by 2 mode.

<sup>1.</sup> Powersave mode includes after a general reset with all analogue and digital supplies applied and also in the case with DV<sub>DD</sub> applied but with all analogue supplies disconnected (i.e. in this later scenario power from DV<sub>DD</sub> will not exceed the specified value whatever the state of the registers).

<sup>2.</sup> Assumes 30pF on each C-BUS interface line and an operating serial clock frequency of 5MHz.

# 3.1.3.2 AC Parameters – Low Noise Amplifier Section

For the following conditions unless otherwise specified:  $AV_{DD} = AV_{DDTX} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0V$ ;  $T_{AMB} = +25^{\circ}C$ . External components and values as shown in section 5.

| LNA                                  | Notes | Min. | Тур.   | Max. | Units |

|--------------------------------------|-------|------|--------|------|-------|

| Gain                                 |       |      | . / P. |      |       |

| 1000 MHz                             |       | _    | 19     | _    | dB    |

| 1500 MHz                             |       | _    | 17     | _    | dB    |

| 2700 MHz                             |       | _    | 14     | _    | dB    |

| Reverse Isolation (S <sub>12</sub> ) |       |      |        |      |       |

| 1000 MHz                             |       | _    | -45    | _    | dB    |

| 1500 MHz                             |       | _    | -30    | _    | dB    |

| 2700 MHz                             |       | _    | -26    | -    | dB    |

| Gain Control Range                   |       | _    | 18     | -    | dB    |

| Gain Control Step Size               |       | 4    | 6      | 8    | dB    |

| Gain Control Step Error              |       | -    | _      | 2    | dB    |

| Noise Figure                         |       |      |        |      |       |

| 1000 MHz                             | 31,32 | -    | 1.75   | -    | dB    |

| 1500 MHz                             | 31,32 | -    | 1.7    | -    | dB    |

| 2700 MHz                             | 31,32 | -    | 2.0    | -    | dB    |

| Third Order Intercept Point (input)  |       |      |        |      |       |

| 1000 MHz                             | 31,32 | -    | 0      | -    | dBm   |

| 1500 MHz                             | 31,32 | -    | 2      | -    | dBm   |

| 2700 MHz                             | 31,32 | -    | 2      | -    | dBm   |

| Variation in IIP3 with Gain Control  | 33    | -    | 5      | -    | dB    |

| 1 dB Gain Compression Point (input)  |       |      |        |      |       |

| 1000 MHz                             | 31,32 | -    | -10    | -    | dBm   |

| 1500 MHz                             | 31,32 | -    | -10    | -    | dBm   |

| 2700 MHz                             | 31,32 | -    | -11    | -    | dBm   |

| Input Impedance                      | 31    | -    | _      | -    | Ω     |

| Output Impedance                     | 31    | -    | 50     | -    | Ω     |

| Operating Frequency Range            |       | 1000 | _      | 2700 | MHz   |

| LO Leakage at LNA Input              |       | _    | -      | -90  | dBm   |

|                                      |       |      |        |      |       |

Notes:

31. External matching may be used to optimise LNA performance for specific frequencies, see section 5.

32. Maximum gain.

33. Change in measured IIP3 between maximum gain and minimum gain, measured at 1500MHz.

# 3.1.3.3 AC Parameters – Receive Mixer

For the following conditions unless otherwise specified:  $AV_{DD} = AV_{DDTX} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0VT_{AMB} = +25^{\circ}C$ . External components and values as shown in section 5.

| Rx Mixer                                                 | Notes | Min. | Тур. | Max. | Units |

|----------------------------------------------------------|-------|------|------|------|-------|

| RF Frequency Range                                       | NOLES | 1000 |      | 2700 | MHz   |

| LO Frequency Range                                       | 43    | 700  | _    | 3000 | MHz   |

| IF Output Range – Image Reject Mode                      | 15    | 200  | 225  | 250  | MHz   |

| IF Output Range – Normal Mode                            |       | 10   | _    | 300  | MHz   |

|                                                          |       |      |      |      |       |

| Gain (Image Reject Mode)                                 |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                               | 40    | _    | 3    | _    | dB    |

| RF= 1500 MHz, IF = 225 MHz                               | 40    | 0    | 3    | _    | dB    |

| RF = 2700 MHz, IF = 225 MHz                              | 40    | _    | 2    | _    | dB    |

| Noise Figure (Image Reject Mode)                         |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                               |       | _    | 14   | -    | dB    |

| RF= 1500 MHz, IF = 225 MHz                               |       | _    | 14   | -    | dB    |

| RF = 2700 MHz, IF = 225 MHz                              |       | _    | 15   | -    | dB    |

| Input Third Order Intercept Point<br>(Image Reject Mode) |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                               | 45    | _    | 6    | -    | dBm   |

| RF= 1500 MHz, IF = 225 MHz                               | 45    | _    | 6    | -    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                              | 45    | _    | 7    | -    | dBm   |

| Input 1dB Compression Point<br>(Image Reject Mode)       |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                               |       | _    | -2   | -    | dBm   |

| RF= 1500 MHz, IF = 225 MHz                               |       | _    | -2   | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                              |       | -    | -2   | _    | dBm   |

| Gain (Normal Mode)                                       |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                               | 40    | _    | 7    | _    | dB    |

| RF= 1500 MHz, IF = 150 MHz                               | 40    | 2    | 6    | -    | dB    |

| RF = 2700 MHz, IF = 225 MHz                              | 40    | _    | 5    | _    | dB    |

| Noise Figure (Normal mode)                               |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                               |       | -    | 10   | -    | dB    |

| RF= 1500 MHz, IF = 150 MHz                               |       | -    | 9    | -    | dB    |

| RF = 2700 MHz, IF = 225 MHz                              |       | -    | 10   | -    | dB    |

| Input Third Order Intercept Point<br>(Normal Mode)       |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                               | 45    | _    | 6    | -    | dBm   |

| RF= 1500 MHz, IF = 150 MHz                               | 45    | _    | 7    | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                              | 45    | -    | 9    | -    | dBm   |

|                                                          |       |      |      |      |       |

|                                | <b></b> . | •    | _         |      |       |

|--------------------------------|-----------|------|-----------|------|-------|

| Rx Mixer (cont'd)              | Notes     | Min. | Тур.      | Max. | Units |

| Input 1dB Compression Point    |           |      |           |      |       |

| (Normal Mode)                  |           |      |           |      |       |

| RF= 1000 MHz, IF = 150 MHz     |           | -    | 0         | -    | dBm   |

| RF= 1500 MHz, IF = 150 MHz     |           | -    | 1         | _    | dBm   |

|                                |           |      | 4         |      |       |

| RF = 2700 MHz, IF = 225 MHz    |           | -    |           | -    | dBm   |

|                                |           |      |           |      |       |

| Image Rejection                | 42        | 30   | 35        | -    | dB    |

| Gain Control Range             |           | -    | 18        | -    | dB    |

| Gain Control Step Size         |           | 5    | 6         | 7    | dB    |

| Gain Control Absolute Error    |           | _    | _         | 2    | dB    |

|                                |           |      |           |      |       |

| LO Divider Ratios (selectable) | 44        | _    | 1, 2 or 4 | _    |       |

| LO Leakage at Input            |           | _    | -40       | _    | dBm   |

|                                |           | _    | -         | _    |       |

| Blocking                       | 41        | 90   | 95        | -    | dB    |

Notes:

40.

External matching (as necessary to 50 $\Omega$ ), see section 5 Test method based on EN 300 113; including operation of selectable dividers, measurements at ±1MHz, ±5MHz 41. and ±10MHz offsets.

42. RF= 1500MHz, IF = 225MHz, LO = 2550MHz

43. After divider

44. Divide by 2 or 4 must be selected in image reject mode.

Input: two-tone signal, -30dBm per tone. 45.

$\ensuremath{\textcircled{}^{\odot}}$  2019 CML Microsystems Plc

CMX975

# 3.1.3.4 AC Parameters – Low Noise Amplifier & Mixer Combined Performance

For the following conditions unless otherwise specified:  $AV_{DD} = AV_{DDTX} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0V$ ;  $T_{AMB} = +25^{\circ}C$ . External components and values as shown in section 4.

| LNA & Mixer                                                          | Notes | Min. | Тур. | Max. | Units      |

|----------------------------------------------------------------------|-------|------|------|------|------------|

| 1.5GHz input @ -30dBm to 225MHz<br>output. Mixer set to divide by 2. |       |      |      |      |            |

| LO = 2.55GHz                                                         |       |      |      |      |            |

| Gain                                                                 | 46    | 17   | 20   | 21   | d <i>B</i> |

| LO = 3.45GHz                                                         |       |      |      |      |            |

| Gain                                                                 | 46    | 18   | 20   | 22   | dB         |

| Input Third Order Intercept Point                                    | 46    |      | -4   |      | dBm        |

Notes:

46. External matching optimised for LNA output to Mixer input connection; no additional image filtering used.

$<sup>\</sup>ensuremath{\textcircled{}^{\odot}}$  2019 CML Microsystems Plc

# 3.1.3.5 AC Parameters – Transmit Mixer

For the following conditions unless otherwise specified:  $AV_{DD} = AV_{DDTX} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0VT_{AMB} = +25$ °C. External components and values as shown in section 5.

| Tx Mixer                                                          | Notes | Min. | Тур. | Max. | Units |

|-------------------------------------------------------------------|-------|------|------|------|-------|

| RF Frequency Range                                                |       | 1000 | -    | 2700 | MHz   |

| LO Frequency Range                                                | 53    | 700  | _    | 3000 | MHz   |

| IF Input Range – Normal Mode                                      |       | 30   | _    | 500  | MHz   |

| IF Input Range – Sideband suppression<br>Mode                     |       | 200  | 225  | 250  | MHz   |

| Gain (Normal Mode)                                                |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                                        | 50    | _    | 2    | _    | dB    |

| RF = 2700 MHz, IF = 225 MHz                                       | 50    | _    | 2    | _    | dB    |

| Noise Figure (Normal Mode)                                        |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                                        |       | -    | 14   | _    | dB    |

| RF = 2700 MHz, IF = 225 MHz                                       |       | -    | 15   | _    | dB    |

| Output Third Order Intercept Point<br>(Normal Mode)               |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                                        |       | _    | TBD  | _    | dBm   |

| RF= 1600 MHz, IF = 225 MHz                                        |       | _    | 20   | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                                       |       | _    | 21   | _    | dBm   |

| Output 1dB Compression Point<br>(Normal Mode)                     |       |      |      |      |       |

| RF= 1000 MHz, IF = 150 MHz                                        |       | _    | 9    | _    | dBm   |

| RF= 1600 MHz, IF = 225 MHz                                        |       | -    | 11   | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                                       |       | -    | 11   | _    | dBm   |

| Gain (Sideband Suppression Mode)                                  |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                                        | 50    | -    | 5    | -    | dB    |

| RF = 2700 MHz, IF = 225 MHz                                       | 50    | -    | 0    | -    | dB    |

| Noise Figure (Sideband Suppression<br>Mode)                       |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                                        |       | -    | 12   | _    | dB    |

| RF = 2700 MHz, IF = 225 MHz                                       |       | -    | 12   | _    | dB    |

| Output Third Order Intercept Point<br>(Sideband Suppression Mode) |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                                        | 56    | _    | 20   | _    | dBm   |

| RF= 1600 MHz, IF = 225 MHz                                        | 56    | _    | 21   | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                                       | 56    | _    | 19   | _    | dBm   |

| Output 1dB Compression Point<br>(Sideband Suppression Mode)       |       |      |      |      |       |

| RF= 1000 MHz, IF = 225 MHz                                        | 56    | -    | 10   | _    | dBm   |

| RF= 1600 MHz, IF = 225 MHz                                        | 56    | -    | 11   | _    | dBm   |

| RF = 2700 MHz, IF = 225 MHz                                       | 56    | -    | 9    | -    | dBm   |

## 2.7GHz Up/Down-converter, LNA, Dual PLL + VCO

| To balance (accepted)          | NI - 4 | N 41 | <b>T</b>  | N.4  | 11     |

|--------------------------------|--------|------|-----------|------|--------|

| Tx Mixer (cont'd)              | Notes  | Min. | Тур.      | Max. | Units  |

| Sideband Suppression Rejection | 52     | 30   | 40        | -    | dB     |

| Gain Control Range             |        | -    | 6         | -    | dB     |

| Gain Control Step Size         |        | 2.5  | 3         | 3.5  | dB     |

| Gain Control Absolute Error    |        | -    | -         | 2    | dB     |

|                                |        |      |           |      |        |

| LO Divider Ratios (selectable) | 55     | -    | 1, 2 or 4 | -    |        |

| LO Leakage at Output           |        | -    | -50       | -30  | dBm    |

| Output Noise Floor             | 51     | -    | -154      | -    | dBm/Hz |

| Output Noise                   | 54     | -    | -145      | -    | dBc/Hz |

|                                |        |      |           |      |        |

Notes:

50. External matching (as necessary to 50Ω), see section 5 not including balun losses

51. Measurement at ±7.5MHz offset, no input signal, 0 dB gain setting

52. Sideband Suppression Mode (Image reject mode) enable

53. After divider

54. Measurement at ±7.5MHz offset, Input signal 0 dBm at 150 MHz, RF output =1.5 GHz, 0 dB gain setting.

55. Divide by 2 or 4 must be selected in the image reject mode.

56. External LO

$<sup>\</sup>ensuremath{\textcircled{}^{\odot}}$  2019 CML Microsystems Plc

### 3.1.3.6 AC Parameters – PLLs

For the following conditions unless otherwise specified:  $AV_{DD} = CPV_{DD} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0V$ ; and  $T_{AMB} = +25$  °C. External components and values as shown in section 5.

| AC Parameters                                | Notes         | Min. | Тур. | Max.                     | Unit   |

|----------------------------------------------|---------------|------|------|--------------------------|--------|

| Clocks                                       |               |      |      |                          |        |

| MCLK frequency (f <sub>MCLK</sub> )          |               | 5    | _    | 40                       | MHz    |

| MCLK sensitivity (AC-coupled)                |               | 0.2  | _    | 1.2                      | Vp-p   |

| MCLK slew rate (AC-coupled)                  |               | 10   | _    | _                        | V/µs   |

| MCLK amplifier phase noise                   |               | -    | -142 | -                        | dBc/Hz |

| RF Synthesiser                               |               |      |      |                          |        |

| RF input frequency                           |               | 700  | -    | 6000                     | MHz    |

| RF slew rate                                 |               | 300  | -    | _                        | V/µs   |

| Charge pump sink/source (programmable)       |               | 25   | _    | 400                      | μA     |

| Charge pump absolute accuracy                |               | -20  | _    | 20                       | %      |

| Charge pump matching                         |               | -4   | -    | 4                        | %      |

| Charge pump compliance range                 |               | 0.5  | _    | CPV <sub>DD1</sub> - 0.5 | V      |

| PD comparison frequency (f <sub>COMP</sub> ) | 10            | 1.2  | _    | 40                       | MHz    |

| N-Divider range (Integer mode)               |               | 32   | _    | 2047                     |        |

| N-Divider range (Fractional mode)            |               | 32   | _    | 2047                     |        |

| 1Hz normalised phase noise floor             | 12, 14        | -    | -209 | _                        | dBc/Hz |

|                                              | 15            | -    | -212 | -                        | dBc/Hz |

| IF Synthesiser                               |               |      |      |                          |        |

| RF frequency                                 |               | 500  | _    | 1000                     | MHz    |

| PD comparison frequency                      |               | 100  | 1000 | 2500                     | kHz    |

| Nominal charge pump current                  |               | 25   | _    | 400                      | μA     |

| N-Divider range                              |               | 25   | _    | 10000                    |        |

| R-Divider range                              |               | 2    | _    | 400                      |        |

| 1Hz normalised phase noise floor             | 11, 12,<br>13 | _    | -211 | -                        | dBc/Hz |

Notes:

10. During internal RF VCO calibration, the comparison frequency should be ≥4.8 MHz.

MCLK = 19.2MHz sinewave, 400mVp-p, measured at 1kHz offset. 11.

12. 1Hz Normalised Phase Noise Floor (PN1Hz) can be used to calculate the phase noise within the PLL loop bandwidth by: Measured Phase Noise (in 1Hz) = -PN1Hz -  $20\log_{10}(N)$  -  $10\log_{10}(f_{comparison})$ . where:  $f_{comparison}$  = Frequency at the output of the reference divider; N = main divider ratio.

IF PLL locked at 900 MHz; IFFPLL\_RDIV = 8 (2.4 MHz), IFPLL\_NDIV = 375, Icp = 200 μA; improves with higher Icp setting. 13.

RF PLL / VCO locked at 3.6GHz; RFPLL\_RDIV = 1 (19.2 MHz), RFPLL\_IDIV = 187, Icp = 400 μA; Fractional-N mode. 14.

15. RF PLL / VCO locked at 3.6GHz;\_RFPLL\_RDIV = 1 (38.4 MHz), RFPLL\_IDIV = 93, Icp = 400 μA; Fractional-N mode.

#### VCO and LO

For the following conditions unless otherwise specified:

$AV_{DD} = CPV_{DD} = 3.3V$ ;  $DV_{DD} = 1.8V$ ;  $AV_{SS} = DV_{SS} = 0V$ ; and  $T_{AMB} = +25$  °C.External components and values as shown in Figure 4 and Table 2.

| AC Parameters                 | Notes | Min.   | Тур. | Max. | Unit   |

|-------------------------------|-------|--------|------|------|--------|

| RF VCO                        |       |        |      |      |        |

| Frequency range               |       | 2800   | -    | 3600 | MHz    |

| K <sub>vco</sub>              |       | -      | 60   | -    | MHz/V  |

| Phase Noise at 100 kHz offset | 20    | -      | -101 | -    | dBc/Hz |

| Phase Noise at 1 MHz offset   | 20    | -      | -126 | _    | dBc/Hz |

| Phase Noise at 10 MHz offset  | 20    | -      | -144 | -    | dBc/Hz |

| LO Input                      |       |        |      |      |        |

| Input level                   |       |        |      |      |        |

| 700 to 4000 MHz               |       | -20    | -10  | 0    | dBm    |

| 4000 to 6000 MHz              |       | -10    | -5   | 0    | dBm    |

| Input Impedance               |       | -      | TBD  | -    | Ω      |

| Frequency range               |       | 700    | _    | 6000 | MHz    |

| RF LO Output                  |       |        |      |      |        |

| Frequency Range               | 21    | 350    | _    | 3600 | MHz    |

| LO Output divide by 2         | 22    | 1400   |      | 1800 | MHz    |

| LO Output divide by 4         | 22    | 700    |      | 900  | MHz    |

| LO Output divide by 6         | 22    | 466.67 |      | 600  | MHz    |

| LO Output divide by 8         | 22    | 350    |      | 450  | MHz    |

| Output Level                  |       | -      | -7   | -    | dBm    |

| IF VCO                        |       |        |      |      |        |

| Frequency range               | 23    | 500    | _    | 1000 | MHz    |

| K <sub>vco</sub>              |       | _      | 11   | _    | MHz/V  |

| Phase Noise at 10kHz offset   | 24    | _      | -86  | -    | dBc/Hz |

| Phase Noise at 100kHz offset  | 24    | _      | -111 | -    | dBc/Hz |

| Phase Noise at 1MHz offset    | 24    | -      | -135 | -    | dBc/Hz |

| IF LO Output                  |       |        |      |      |        |

| Frequency Range               | 21,26 | 500    | _    | 1000 | MHz    |

| LO Output divide by 4         | 22    | 125    |      | 250  | MHz    |

| LO Output divide by 8         | 22    | 62.5   |      | 125  | MHz    |

| LO Output divide by 16        | 22    | 31.25  |      | 62.5 | MHz    |

| Output Level                  | 25    | -20    | -15  | _    | dBm    |

Notes:

20. RF frequency of 1.6GHz (VCO / PLL at 3.2GHz, output divide by 2); loop comparison frequency = 19.2MHz.

21 LO output divide function disabled.

22 LO output divide function enabled.

23 Tuned with external inductor or PCB track. While operation is possible with other inductor values above and below this frequency range, performance is not validated.

24 Operating frequency 500MHz.

25 Unmatched, high current mode

26 The IFVCO frequency is intended to be essentially fixed apart from a small tuning range ±20MHz (e.g. to give a small shift between Tx and Rx); the full tuning capability can then be used to compensate for process, voltage and temperature (PVT) variation and for practical choice of inductor.

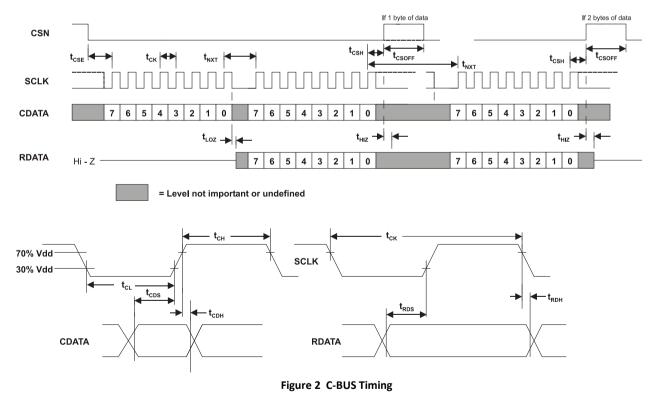

# 3.1.3.7 C-BUS Timing Parameters

For the following conditions unless otherwise specified:  $AV_{DD} = CPV_{DD} = 2.7V$  to 3.6V;  $DV_{DD} = 1.7V$  to 3.6V;  $AV_{SS} = DV_{SS} = 0V$ ;  $T_{AMB} = +25^{\circ}C$ . External components and values as shown in Figure 4 and Table 2.

| C-BUS T            | imings (See Figure 2)                 | Notes | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------------|-------|------|------|------|-------|

| t <sub>cse</sub>   | CSN-enable to clock-high time         |       | 100  | _    | _    | ns    |

| t <sub>сsн</sub>   | Last clock-high to CSN-high time      |       | 100  | -    | -    | ns    |

| t <sub>LOZ</sub>   | Clock-low to reply output enable time |       | 0.0  | _    | -    | ns    |

| t <sub>HIZ</sub>   | CSN-high to reply output 3-state time |       | -    | -    | 1.0  | μs    |

| t <sub>csoff</sub> | CSN-high time between transactions    |       | 1.0  | -    | -    | μs    |

| t <sub>NXT</sub>   | Inter-byte time                       |       | 200  | -    | -    | ns    |

| t <sub>ск</sub>    | Clock-cycle time                      |       | 200  | -    | 100  | ns    |

| t <sub>сн</sub>    | Serial clock-high time                |       | 100  | -    | -    | ns    |

| t <sub>cl</sub>    | Serial clock-low time                 |       | 100  | -    | -    | ns    |

| t <sub>cds</sub>   | Command data set-up time              |       | 75.0 | -    | -    | ns    |

| t <sub>cdh</sub>   | Command data hold time                |       | 25.0 | -    | -    | ns    |

| t <sub>rds</sub>   | Reply data set-up time                |       | 50.0 | -    | -    | ns    |

| t <sub>rdh</sub>   | Reply data hold time                  |       | 0.0  | _    | _    | ns    |

Maximum 30pF load on each C-BUS interface line.

$\odot$  2019 CML Microsystems Plc

CMX975

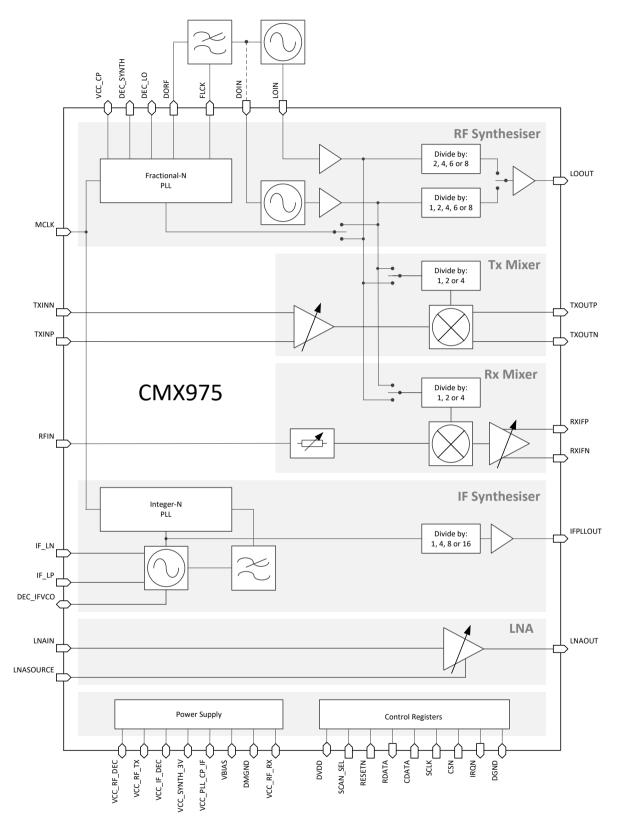

# 4 Pin and Signal Definitions

# Figure 3 Pin Configuration

4.1 Pin List

| Pin No | Pin Name      | Туре | Pin Function                                                                                                                                                                                                                                    |

|--------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | IRQN          | OP   | C-BUS interrupt request. The output is driven low to DGND when active and is high-impedance when inactive. An external 100k $\Omega$ pull-up resistor to DV <sub>DD</sub> should be connected to this pin.                                      |

| 2      | DVDD          | PWR  | Global digital power supply and decoupling                                                                                                                                                                                                      |

| 3      | NC            | NC   | Do not connect to this pin                                                                                                                                                                                                                      |

| 4      | DMGND         | PWR  | Digital Ground (moat connection)                                                                                                                                                                                                                |

| 5      | RDATA         | TS   | A tri-state C-BUS data output. This output is high impedance when not sending data to the host $\mu$ C. Care should be taken to ensure any inputs to which this pin is connected are not left floating when RDATA is in a high impedance state. |

| 6      | CDATA         | IP   | C-BUS data input                                                                                                                                                                                                                                |

| 7      | SCLK          | IP   | C-BUS clock                                                                                                                                                                                                                                     |

| 8      | DGND          | PWR  | Digital Ground                                                                                                                                                                                                                                  |

| 9      | CSN           | IP   | C-BUS chip select                                                                                                                                                                                                                               |

| 10     | RESETN        | IP   | Active low reset pin with internal $75 k\Omega$ pull-up resistor                                                                                                                                                                                |

| 11     | VCC_PLL_CP_IF | PWR  | IF PLL Charge Pump power supply and decoupling; connect to $\mbox{CPV}_{\mbox{DD2}}$ and decouple when PLL not used.                                                                                                                            |

| 12     | IFPLLOUT      | OP   | Single ended IF PLL output                                                                                                                                                                                                                      |

| 13     | VCC_IF_DEC    | PWR  | Decoupling for IF PLL (retain decoupling when IF PLL not used)                                                                                                                                                                                  |

| 14     | IF_LN         | IP   | IF VCO tank negative                                                                                                                                                                                                                            |

| 15     | IF_LP         | IP   | IF VCO tank positive                                                                                                                                                                                                                            |

| 16     | DEC_IFVCO     | PWR  | IF VCO Decoupling decouple when PLL not used.                                                                                                                                                                                                   |

| 17     | LNASOURCE     | IP   | LNA source connection                                                                                                                                                                                                                           |

| 18     | LNAIN         | IP   | LNA RF input                                                                                                                                                                                                                                    |

| 19     | VBIAS         | BIAS | $47.5 k\Omega$ External bias resistor and decoupling to $AV_{SS}.$ This pin should not be used as a voltage reference.                                                                                                                          |

| Pin No               | Pin Name     | Туре | Pin Function                                                                                                              |

|----------------------|--------------|------|---------------------------------------------------------------------------------------------------------------------------|

| 20                   | LNAOUT       | OP   | LNA output (DC connection required to AV <sub>DD</sub> ).                                                                 |

| 21                   | VCC_RF_RX    | PWR  | Rx analogue power supply and decoupling AV <sub>DD</sub> ; decouple when Rx not used.                                     |

| 22                   | RXIFP        | OP   | Rx mixer IF output positive (DC connection required to $AV_{DD}$ ).                                                       |

| 23                   | RFIN         | IP   | Rx mixer input (DC connection required to AV <sub>ss</sub> ).                                                             |

| 24                   | RXIFN        | OP   | Rx mixer IF output negative (DC connection required to AV <sub>DD</sub> ).                                                |

| 25                   | VCC_RF_DEC   | PWR  | 1.2V analogue supply decoupling (Tx and Rx). Decouple when Tx & Rx not used.                                              |

| 26                   | TXINN        | IP   | Tx mixer IF negative input                                                                                                |

| 27                   | TXINP        | IP   | Tx mixer IF positive input                                                                                                |

| 28                   | TXOUTN       | IP   | Tx mixer output negative (DC connection required to AV <sub>DDTX</sub> )                                                  |

| 29                   | TXOUTP       | IP   | Tx mixer output positive (DC connection required to AV <sub>DDTX</sub> )                                                  |

| 30                   | VCC_RF_TX    | PWR  | Tx analogue power supply and decoupling                                                                                   |

| 31                   | DEC_LO       | PWR  | Decoupling for VCO supply and RF PLL loop filter reference point (1.2V)                                                   |

| 32                   | DOIN         | IP   | VCO tuning node (0V to CPV <sub>DD</sub> )                                                                                |

| 33                   | FLCK         | OP   | RF PLL fast lock output                                                                                                   |

| 34                   | DORF         | OP   | Charge pump output                                                                                                        |

| 35                   | VCC_CP       | PWR  | Power supply and decoupling for RF PLL charge pump; connect to $CPV_{DD1}$ and decouple even if not used.                 |

| 36                   | VCC_SYNTH_3V | PWR  | Analogue power supply and decoupling (RF PLL, bias and MCLK buffer); connect to $AV_{DD}$ and decouple when PLL not used. |

| 37                   | LOIN         | IP   | External VCO drive in                                                                                                     |

| 38                   | DEC_SYNTH    | OP   | 1.2V regulator decoupling (RF PLL)                                                                                        |

| 39                   | LOOUT        | OP   | RF VCO/PLL output                                                                                                         |

| 40                   | MCLK         | IP   | Master Clock input used for RF and IF PLLs.                                                                               |

| Exposed<br>Metal Pad | AGND         | PWR  | The exposed metal pad must be electrically connected to analogue ground.                                                  |

Notes:

Total = 41 Pins (40 pins and central, exposed metal ground pad) Unused pins may be left not connected unless otherwise specified.

PWR = Power connection IP = Input OP = Output TS = 3-state output NC = Do not connect to this pin

# 4.2 Signal Definitions

| Signal Name        | Pins                      | Usage                                                                                                      |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------|

| V <sub>max</sub>   |                           | The maximum value of the supplies $DV_{DD}$ , $AV_{DD_{i}}$<br>$AV_{DDTX}$ , $CPV_{DD1}$ , and $CPV_{DD2}$ |

| AV <sub>DD</sub>   | VCC_SYNTH_3V<br>VCC_RF_RX | Power supply for analogue circuits                                                                         |

| AV <sub>DDTX</sub> | VCC_RF_TX                 | Power supply for analogue Tx circuits                                                                      |

| CPV <sub>DD1</sub> | VCC_CP                    | Power supply for RF PLL charge pump                                                                        |

| CPV <sub>DD2</sub> | VCC_PLL_CP_IF             | Power supply for IF PLL charge pump                                                                        |

| $CPV_{DD}$         | VCC_CP,<br>VCC_PLL_CP_IF  | $CPV_{DD1}$ and $CPV_{DD2}$                                                                                |

| DV <sub>DD</sub>   | DVDD                      | Power supply for digital circuits and C-BUS interface                                                      |

| DV <sub>SS</sub>   | DGND, DMGND               | Ground for digital circuits                                                                                |

| AV <sub>SS</sub>   | AGND                      | Ground for analogue circuits                                                                               |

Table 1 Definition of Power Supplies

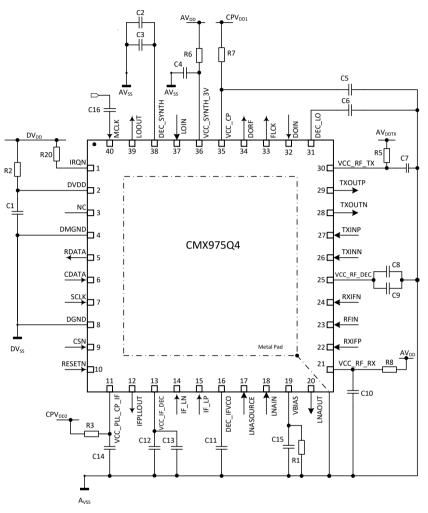

## 5 Power Supply and Decoupling

This device has separate supply pins for the analogue and digital circuitry; a 3.0V nominal supply is recommended for  $AV_{DD}$ ,  $DV_{DD}$ ,  $CPV_{DD1}$  and  $CPV_{DD2}$ . The digital interface can run at a lower voltage than the rest of the device by setting the  $DV_{DD}$  supply to the required interface voltage (see section 3.1.2).

#### Figure 4 Power Supply and AC coupling

| C1 | 10nF   | C9  | NF    |

|----|--------|-----|-------|

| C2 | 100nF  | C10 | 10nF  |

| C3 | 100pF  | C11 | 56nF  |

| C4 | 10nF   | C12 | 100nF |

| C5 | 10nF   | C13 | 100pF |

| C6 | 150nF  | C14 | 10nF  |

| C7 | 10nF   | C15 | 10nF  |

| C8 | 100nF  | C16 | 10nF  |

| R1 | 47.5kΩ | R6  | 3.3Ω  |

| R2 | 10Ω    | R7  | 3.3Ω  |

| R3 | 3.3Ω   | R8  | 3.3Ω  |

| R5 | 3.3Ω   | R20 | 100kΩ |

#### Table 2 Power Supply and Decoupling Component Values

Notes:

- 1. Maximum Tolerances: Capacitors  $\pm 5\%$  Resistors  $\pm 1\%$

- 2. It is expected that any low-frequency interference on the power supplies will be removed by active regulation; a large capacitor is an alternative but may require more board space and so may not be preferred. It is particularly important to ensure that there is no

interference from the  $DV_{DD}$  to sensitive analogue supplies ( $AV_{DD}$ ). It is therefore advisable to use separate power supplies for digital and analogue circuits.

- 3. The supply decoupling shown is intended for RF noise suppression. It is necessary to have a small series impedance prior to the decoupling capacitor for the decoupling to work well. This may be achieved cost effectively by using the resistor and capacitor values shown. The use of resistors results in small dc voltage drops (up to approx 0.1V). Choosing resistor values approximately inversely proportional to the dc current requirements of each supply ensures the dc voltage drop on each supply is reasonably matched. In any case, the resultant dc voltage change is well within the design tolerance of the device. If higher impedance resistors are used (not recommended) then greater care will be needed to ensure the supply voltages are maintained within tolerance, even when parts of the device are enabled or disabled.

- 4. It is advisable to have separate ground planes for analogue and digital circuits.

## 6 Layout Recommendations

The RF performance of the CMX975 is dependant on the PCB design and layout. Grounding arrangements are particularly important to achieving the specified performance. Recommendations are contained in the following guidance:

The evaluation kit has, in general, RF components, connectors and configuration links placed on the top layer, with voltage regulators, supplies and decoupling for the device on the bottom layer. The layout has been optimised for low ground impedance, the shortest possible RF tracking to the pins, and minimal stray capacitance for operation at high frequencies.

To provide all the connections to a small QFN package in a compact layout, along with its associated components and isolation between certain signals, a multi-layer PCB layout is necessary.

A recommended layout may be taken from the evaluation kit (EV9750 / PCB593C), Gerber data for which can be downloaded from the CML website (www.cmlmicro.com).

The LNA is capable of high gain and a low noise figure. As such, care is needed in the layout, decoupling and management of parasitics for optimum performance and stability at all frequencies. This specific LNA output layout requires decoupling to the adjacent VBIAS pin and an additional  $100\Omega$  resistor across the two LNA output tracks to ensure unconditional stability at frequencies above 4GHz. This resistor should not be required if a single track to the LNA output pin is used.

For the Tx and Rx mixers, the RF matching circuits have been placed on the top layer and the IF matching circuits on the bottom layer so that the ground plane in between provides built-in isolation between the circuits.

While values are given for suitable RF matching circuits, the optimum component values required for the operating frequencies shown may change if the recommended layout is not followed (particularly for low-value inductors and capacitors).

A good quality dielectric should be used for low loss and consistent high frequency performance. The EV9750 uses Rogers RO4003C ceramic substrate for the upper layer, with the other layers using FR4 / VT481 2116 dielectric.

The central ground pad should provide a good low impedance to ground plane layers, whilst also allowing for reliable solder reflow. A grid of 5 x 5 plated through vias (0.3mm diameter) is recommended.

© 2019 CML Microsystems Plc

# 7 Detailed Description

# 7.1 Power Management

In total there are four on-chip regulators each with the basic architecture of an error amplifier, with an output pass transistor. Three of the regulators utilise an external capacitor of typically 220nF, these regulators will supply 1.2V to the RF PLL, IF PLL and RF domains respectively. The fourth regulator is used to provide 1.2V for the digital sections of the chip, namely, C-BUS control registers, power control and delta-sigma logic. This regulator is internally stabilised and does not require an external capacitor.

There are two on-chip bandgap reference circuits, one of which provides the 1.2V reference for the three analogue 1.2V supply regulators, while the other provides the 1.2V reference for the digital 1.2V supply regulator.

The on-chip Power On Reset (POR) is used to monitor the digital and analogue supply rails and generate a power down signal in the case of loss of any supply rail. Whenever power is applied to the DVDD pin, the POR circuit ensures that the device powers up into the same state as follows a General Reset command. The RESETN pin on the device will also reset the device to the same state.

## 7.2 Clock Generator

The MCLK amplifier must be enabled when a digital reference clock is required and is enabled automatically when either the RF or IF PLLs are enabled.

The MCLK amplifier receives the output of an external oscillator, which may be a low amplitude sine wave, and turns it into a 1.2V full range digital signal for use by the RF and IF PLL reference clock dividers and as a reference clock for the digital block. As the input to the amplifier is ac coupled and the amplifier may be enabled or disabled dependent on system configuration, the digital output clock may be unstable for a period of time.

A clock generator circuit will "hold off" the clock to the digital block until it is stable and then start the clock with a full and complete cycle. The status of the MCLK is reported in the status register (\$C4, b7), see section 8.9.

### 7.3 Tx (Up-conversion) Mixer

The Tx mixer is an up-converting RF mixer with differential input and output. The mixer may be used single-ended, but that will involve a trade-off with ultimate performance. The Tx mixer has a selectable 'image reject' ('single sideband') mode or may be used in 'normal' mode with reduced current.

If the image reject functionality is enabled the mixer must be used in LO/2 or LO/4 mode (NB: with LO/1 image reject mode is not available). In image reject mode the choice of IF is restricted. High-side or low-side operating modes can be selected by C-BUS command.

The registers associated with initialisation of the Tx Mixer are:

- GCR \$31

- GCR\_RD \$C1

The registers used to configure the Tx Mixer are:

- TX\_CON \$33

- TX\_CON\_RD \$C3

- LO\_CONTROL \$3F

- LO\_CONTROL\_RD \$CF

D/975/3

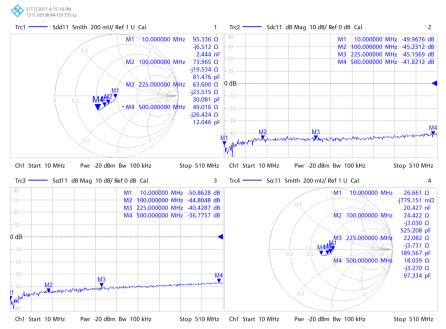

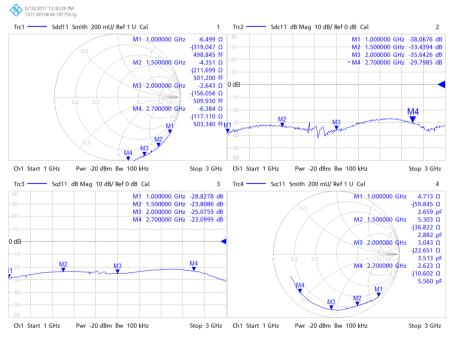

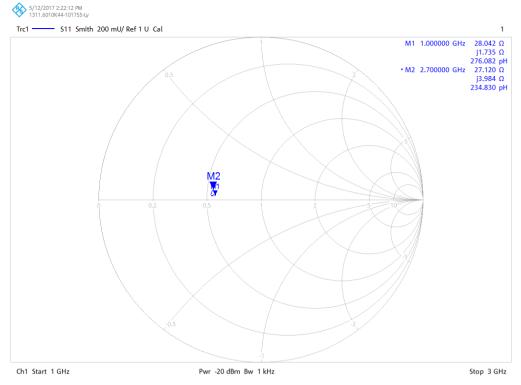

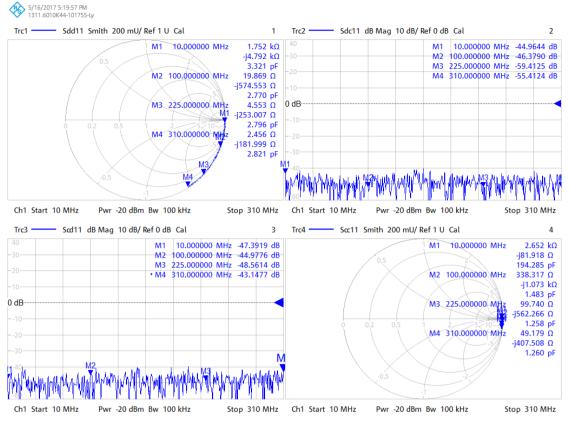

Figure 5 Tx Mixer Impedance (Normal mode, 0dB gain, differential)

| Frequency<br>(MHz) | Impedance<br>(Ω-/+jΩ) | Parallel Equivalent Circuit<br>(R // pF) |

|--------------------|-----------------------|------------------------------------------|

| 10                 | 95.34 -j 6.512        | 95.8 // 11.4                             |

| 100                | 73.97 -j 19.53        | 79 // 5.25                               |

| 225                | 63.6 –j 23.52         | 72.3 // 3.6                              |

| 500                | 49.02 –j 26.42        | 63.4 // 2.72                             |

Table 3 Tx Mixer Input Impedances and Parallel Equivalent Circuit (Normal mode)

Note that selecting either divide by 1, 2 or 4 for the LO mixer mode will make little difference to the impedance.

Figure 6 Tx Mixer Output Impedance (Normal mode, 0dB gain, differential)

| Frequency<br>(MHz) | Differential<br>Impedance<br>(Ω-/+jΩ) | Parallel Equivalent Circuit<br>(R // pF) |

|--------------------|---------------------------------------|------------------------------------------|

| 1000               | 4.71 –j 59.85                         | 764.8 // 2.64                            |

| 1500               | 5.3 –j36.8                            | 259 // 2.82                              |

| 2000               | 3.04 –j 22.65                         | 171 // 3.45                              |

| 2700               | 2.6 –j 10.6                           | 45.6 // 5.24                             |

Table 4 Tx Mixer Output Differential Impedances and Parallel Equivalent Circuit (Normal mode)

Figure 7 Tx Mixer Impedance (SSB mode, 0dB gain, differential)

Note that selecting divide by 2 or 4 for the LO mixer mode will make little difference to the impedance. Image reject mode is only valid for operation around 225MHz due to the internal networks used to provide phase quadrature, Operation at other IF frequencies will give degraded image rejection.

| Frequency | Impedance | Parallel Equivalent |

|-----------|-----------|---------------------|

| (MHz)     | (Ω-/+jΩ)  | Circuit (R // pF)   |

| 225       | 82 –j 117 | 247 // 4            |

Table 5 Tx Mixer Input Differential Impedances and Parallel Equivalent Circuit (SSB mode)

Figure 8 Tx Mixer Output Impedance (SSB mode, 0dB gain, differential)

| Frequency<br>(MHz) | Differential<br>Impedance<br>(Ω-/+jΩ) | Parallel Equivalent Circuit<br>(R // pF) |

|--------------------|---------------------------------------|------------------------------------------|

| 1000               | 5.44 –j 51.96                         | 503 // 3.03                              |

| 1500               | 6.15 –j 30.55                         | 158 // 3.34                              |

| 2000               | 5.2 –j 18.19                          | 68 // 4.05                               |

| 2700               | 5.625 –j 8.33                         | 17.92 // 4.8                             |

Table 6 Tx Mixer Output Differential Impdances and Parallel Equivalent Circuit (SSB mode)

#### 7.3.1 Matching Circuits

# 7.3.1.1 Normal Mixer Mode

Typical matching circuits for the Tx Mixer in normal mode are shown in Figure 9 and Table 7. A LC circuit is shown for the IF input match, alternatively a balun may be used. The mixer may be used single-ended but this will result in degraded performance.

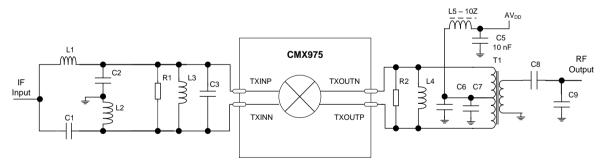

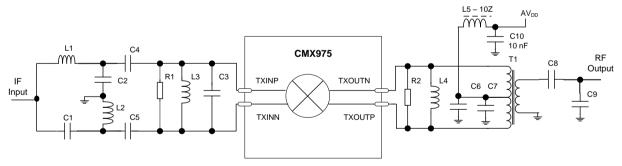

Figure 9 Tx Normal Mixer Matching Circuit

| Reference | 225MHz (IF)    | 150MHz(IF)      | 1GHz(RF)       | 1.6GHz(RF)     | 2.7GHz(RF)      |

|-----------|----------------|-----------------|----------------|----------------|-----------------|

| C1, C2    | 12pF           | 22pF<br>GRM1555 | -              | -              | -               |

| C3        | 5.6pF          | 18pF            | -              | -              | -               |

| C6        |                |                 | 47pF           | 22pF           | 6.8pF           |

| C7        |                |                 | 1nF            | 1nF            | 1nF             |

| C8        |                |                 | 10 nH          | 0Ω             | 0 Ω             |

| C9        |                |                 | NF             | NF             | NF              |

| L1, L2    | 36nH<br>0402CS | 51nH<br>0402CS  |                |                |                 |

| L3        | 56nH<br>0402CS | 56nH<br>0402CS  |                |                |                 |

| L4        | -              | -               | 47nH<br>0402CS | 15nH<br>0402CS | 3.3nH<br>0402HP |

| L5        | -              | -               | 10 Ω Ferrite   | 10 Ω Ferrite   | 10 Ω Ferrite    |

| R1        | NF             | 560 Ω           |                |                |                 |

| R2        | -              | -               | 470 Ω          | 430 Ω          | 82 Ω            |

| T1        | -              | -               | 4:1            | 4:1            | 2:1             |