# Ultralow Power, 1.8 V, 3 mm $\times$ 3 mm, 2-Channel Capacitance Converter

AD7156

#### **FEATURES**

**Ultralow power**

Power supply voltage: 1.8 V to 3.6 V

Operation power supply current: 70 µA typical

Power-down current: 2 μA typical

Fast response time

Conversion time: 10 ms per channel

Wake-up time from serial interface: 300 µs

Adaptive environmental compensation

2 capacitance input channels

Sensor capacitance (Csens): 0 pF up to 13 pF

Sensitivity up to 3 fF 2 modes of operation

Standalone with fixed settings

Interfaced to a microcontroller for user-defined settings

2 detection output flags

2-wire serial interface (I<sup>2</sup>C-compatible)

Operating temperature: -40°C to +85°C

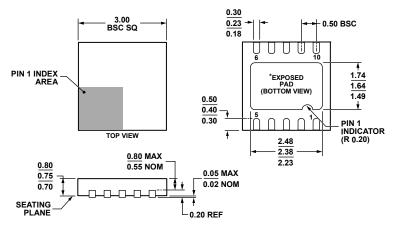

10-lead LFCSP package (3 mm  $\times$  3 mm  $\times$  0.8 mm)

#### **APPLICATIONS**

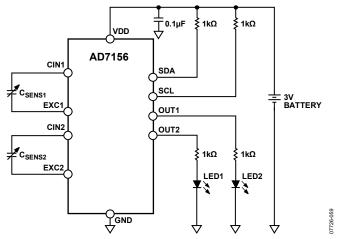

Buttons and switches Proximity sensing Contactless switching Position detection Level detection Portable products

#### **GENERAL DESCRIPTION**

The AD7156 delivers a complete signal processing solution for capacitive sensors, featuring an ultralow power converter with fast response time.

The AD7156 uses an Analog Devices, Inc., capacitance-to-digital converter (CDC) technology, which combines features important for interfacing to real sensors, such as high input sensitivity and high tolerance of both input parasitic ground capacitance and leakage current.

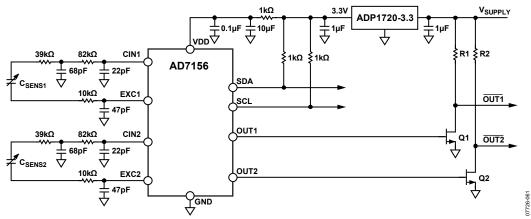

The integrated adaptive threshold algorithm compensates for any variations in the sensor capacitance due to environmental factors like humidity and temperature or due to changes in the dielectric material over time.

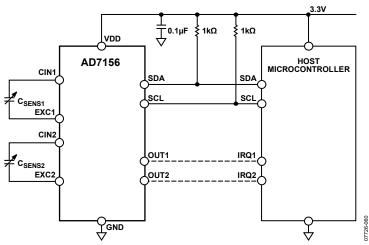

By default, the AD7156 operates in standalone mode using the fixed power-up settings and indicates detection on two digital outputs. Alternatively, the AD7156 can be interfaced to a microcontroller via the serial interface, the internal registers can be programmed with user-defined settings, and the data and status can be read from the part.

The AD7156 operates with a 1.8 V to 3.6 V power supply. It is specified over the temperature range of -40°C to +85°C.

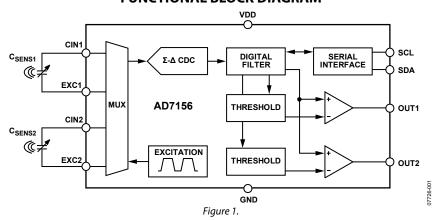

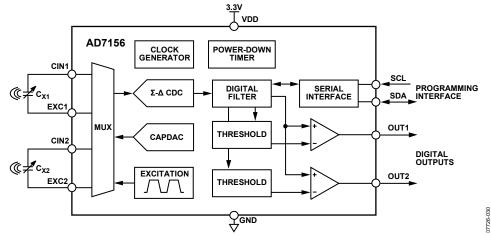

## **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                     | Fixed Threshold Registers             | 18 |

|----------------------------------------------|---------------------------------------|----|

| Applications1                                | Sensitivity Registers                 | 18 |

| General Description1                         | Timeout Registers                     | 18 |

| Functional Block Diagram1                    | Setup Registers                       | 19 |

| Revision History2                            | Configuration Register                | 20 |

| Specifications                               | Power-Down Timer Register             | 21 |

| Timing Specifications                        | CAPDAC Registers                      | 21 |

| Absolute Maximum Ratings6                    | Serial Number Register                | 21 |

| ESD Caution                                  | Chip ID Register                      | 21 |

| Pin Configuration and Function Descriptions7 | Serial Interface                      | 22 |

| Typical Performance Characteristics          | Read Operation                        | 22 |

| Theory of Operation11                        | Write Operation                       | 22 |

| Capacitance-to-Digital Converter11           | AD7156 Reset                          | 23 |

| CAPDAC11                                     | General Call                          | 23 |

| Comparator and Threshold Modes12             | Hardware Design Considerations        | 24 |

| Adaptive Threshold12                         | Overview                              | 24 |

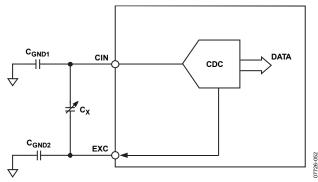

| Sensitivity12                                | Parasitic Capacitance to Ground       | 24 |

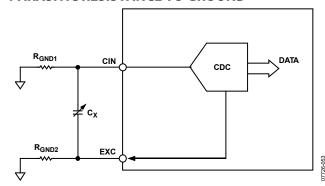

| Data Average                                 | Parasitic Resistance to Ground        | 24 |

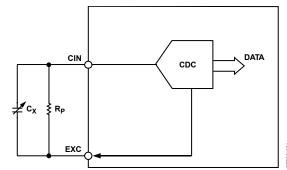

| Hysteresis                                   | Parasitic Parallel Resistance         | 24 |

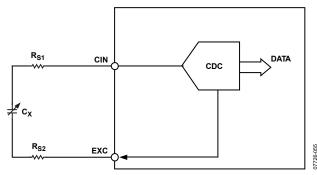

| Timeout                                      | Parasitic Serial Resistance           | 25 |

| Auto-DAC Adjustment14                        | Input Overvoltage Protection          | 25 |

| Power-Down Timer14                           | Input EMC Protection                  | 25 |

| Register Descriptions                        | Power Supply Decoupling and Filtering | 25 |

| Status Register16                            | Application Examples                  | 26 |

| Data Registers17                             | Outline Dimensions                    | 27 |

| Average Registers18                          | Ordering Guide                        | 27 |

# **REVISION HISTORY**

10/08—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD}$  = 1.8 V to 3.6 V, GND = 0 V, temperature range = -40°C to +85°C, unless otherwise noted.

Table 1.

| Parameter                                               | Min            | Тур            | Max      | Unit <sup>1</sup>          | Test Conditions/Comments                       |

|---------------------------------------------------------|----------------|----------------|----------|----------------------------|------------------------------------------------|

| CAPACITIVE INPUT                                        |                |                |          |                            |                                                |

| Conversion Input Range, CIN to EXC <sup>2, 3</sup>      | 3.2            | 4              |          | pF                         | 4 pF input range                               |

|                                                         | 1.6            | 2              |          | pF                         | 2 pF input range                               |

|                                                         | 0.8            | 1              |          | pF                         | 1 pF input range                               |

|                                                         | 0.4            | 0.5            |          | pF                         | 0.5 pF input range                             |

| Resolution <sup>4, 5</sup>                              |                | 2.0            |          | fF                         | 4 pF input range                               |

|                                                         |                | 1.6            |          | fF                         | 2 pF input range                               |

|                                                         |                | 1.4            |          | fF                         | 1 pF input range                               |

|                                                         |                | 1.0            |          | fF                         | 0.5 pF input range                             |

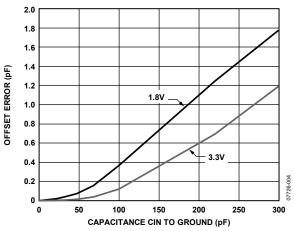

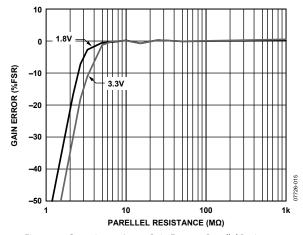

| Maximum Allowed Capacitance, CIN to GND <sup>4, 6</sup> |                | 50             |          | pF                         | See Figure 4, Figure 5, and<br>Figure 6        |

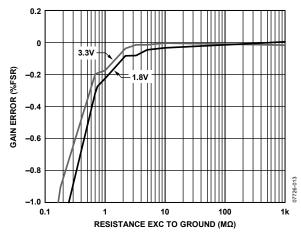

| Minimum Allowed Resistance, CIN to GND <sup>4, 6</sup>  |                | 10             |          | ΜΩ                         | See Figure 10 and Figure 11                    |

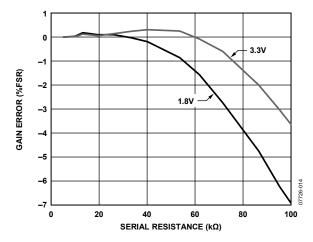

| Maximum Allowed Serial Resistance <sup>4, 6</sup>       |                | 50             |          | kΩ                         | See Figure 14                                  |

| Gain Error                                              | -20            |                | +20      | %                          |                                                |

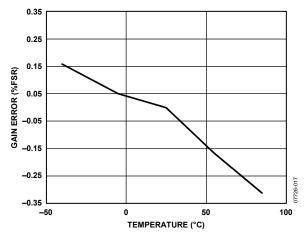

| Gain Deviation over Temperature⁴                        |                | 0.5            |          | %FSR                       | See Figure 17                                  |

| Gain Matching Between Ranges⁴                           | -2             |                | +2       | %                          |                                                |

| Offset Error⁴                                           |                | 50             |          | fF                         | CIN and EXC pins disconnected                  |

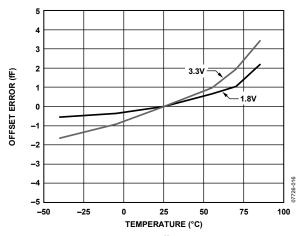

| Offset Deviation over Temperature <sup>4</sup>          |                | 5              |          | fF                         | CIN and EXC pins disconnected<br>See Figure 16 |

| Integral Nonlinearity (INL) <sup>4</sup>                |                | 0.05           |          | %                          |                                                |

| Channel-to-Channel Isolation <sup>4</sup>               |                | 60             |          | dB                         |                                                |

| Power Supply Rejection⁴                                 |                | 4              |          | fF/V                       |                                                |

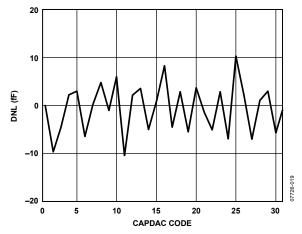

| CAPDAC                                                  |                |                |          |                            |                                                |

| Full Range                                              | 10             | 12.5           |          | pF                         |                                                |

| Resolution (LSB) <sup>4</sup>                           |                | 200            |          | fF                         |                                                |

| Differential Nonlinearity (DNL) <sup>4</sup>            |                |                | 0.25     | LSB                        |                                                |

| Auto-DAC Increment/Decrement <sup>4, 7</sup>            | 25             |                | 75       | % of C <sub>IN</sub> range |                                                |

| EXCITATION                                              |                |                |          |                            |                                                |

| Voltage <sup>4,7</sup>                                  |                | $\pm V_{DD}/2$ | <u> </u> | V                          |                                                |

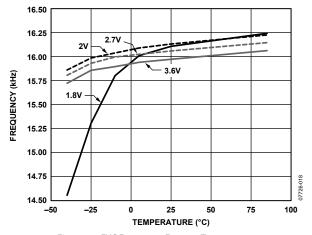

| Frequency                                               |                | 16             |          | kHz                        | See Figure 18                                  |

| Maximum Allowed Capacitance EXC to GND <sup>4, 6</sup>  |                | 1000           |          | pF                         | See Figure 7, Figure 8, and Figure 9           |

| Minimum Allowed Resistance EXC to GND <sup>4, 6</sup>   |                | 1              |          | ΜΩ                         | See Figure 12 and Figure 13                    |

| LOGIC OUTPUTS (OUT1, OUT2)                              |                |                |          |                            |                                                |

| Output Low Voltage (Vol.)                               |                |                | 0.4      | V                          | $I_{SINK} = -3 \text{ mA}$                     |

| Output High Voltage (V <sub>OH</sub> )                  | $V_{DD} - 0.6$ | 5              |          | V                          | $I_{SOURCE} = +3 \text{ mA}$                   |

| SERIAL INTERFACE INPUTS (SCL, SDA)                      |                |                |          |                            |                                                |

| Input High Voltage (V <sub>H</sub> )                    | 70             |                |          | % of V <sub>DD</sub>       |                                                |

| Input Low Voltage (V <sub>I</sub> L)                    |                |                | 25       | % of V <sub>DD</sub>       |                                                |

| Input Leakage Current                                   |                | ±0.1           | ±5       | μΑ                         |                                                |

| Input Pin Capacitance                                   |                | 6              |          | pF                         |                                                |

| OPEN-DRAIN OUTPUT (SDA)                                 |                |                |          |                            |                                                |

| Output Low Voltage (V <sub>OL</sub> )                   |                |                | 0.4      | V                          | $I_{SINK} = -6.0 \text{ mA}$                   |

| Output High Leakage Current (Іон)                       |                | 0.1            | 5        | μΑ                         | $V_{OUT} = V_{DD}$                             |

| Parameter                               | Min | Тур | Max | Unit1 | Test Conditions/Comments                   |

|-----------------------------------------|-----|-----|-----|-------|--------------------------------------------|

| POWER REQUIREMENTS                      |     |     |     |       |                                            |

| V <sub>DD</sub> -to-GND Voltage         | 1.8 |     | 3.6 | V     |                                            |

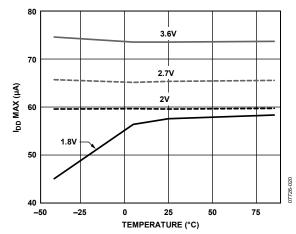

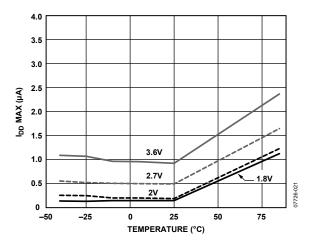

| I <sub>DD</sub> Current <sup>4, 8</sup> |     | 65  | 75  | μΑ    | $V_{DD} \le 2.7 \text{ V}$ , see Figure 20 |

|                                         |     | 70  | 85  | μΑ    | $V_{DD} = 3.6 \text{ V}$ , see Figure 20   |

| IDD Current Power-Down Mode4,8          |     | 2   | 10  | μΑ    | $V_{DD} \le 2.7 \text{ V}$ , see Figure 21 |

|                                         |     | 2   | 17  | μΑ    | $V_{DD} = 3.6 \text{ V}$ , see Figure 21   |

$<sup>^{1}</sup>$  Capacitance units: 1 pF = 1 × 10 $^{-12}$  F; 1 fF = 10 $^{-15}$  F.

<sup>4</sup> The maximum specification is not production tested but is supported by characterization data at initial product release.

<sup>7</sup> Specification is not production tested but is guaranteed by design.

<sup>&</sup>lt;sup>2</sup> The CAPDAC can be used to shift (offset) the input range. The total capacitance of the sensor can therefore be up to the sum of the CAPDAC value and the conversion input range. With the auto-DAC feature, the CAPDAC is adjusted automatically when the CDC input value is lower than 25% or higher than 75% of the CDC nominal input range.

<sup>&</sup>lt;sup>3</sup> The maximum capacitance of the sensor connected between the EXCx and CINx pins is equal to the sum of the minimum guaranteed value of the CAPDAC and the minimum guaranteed input range.

<sup>&</sup>lt;sup>5</sup> The resolution of the converter is not limited by the output data format or output data LSB (least significant bit) size, but by the converter and system noise level. The noise-free resolution is defined as level of peak-to-peak noise coming from the converter itself, with no connection to the CIN and EXC pins.

<sup>&</sup>lt;sup>6</sup> These specifications are understood separately. Any combination of the capacitance to ground and serial resistance may result in additional errors, for example gain error, gain drift, offset error, offset drift, and power supply rejection.

<sup>&</sup>lt;sup>8</sup> Digital inputs equal to V<sub>DD</sub> or GND.

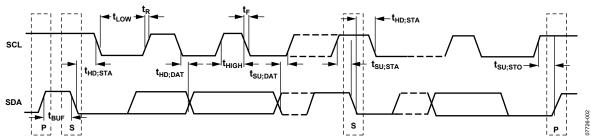

## **TIMING SPECIFICATIONS**

V<sub>DD</sub> = 1.8 V to 3.6 V, GND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = V<sub>DD</sub>, temperature range = -40°C to +85°C, unless otherwise noted.

Table 2.

| Tuble 2.                                                                        |     |     |     |      |                                                  |  |  |  |  |  |

|---------------------------------------------------------------------------------|-----|-----|-----|------|--------------------------------------------------|--|--|--|--|--|

| Parameter                                                                       | Min | Тур | Max | Unit | Test Conditions/Comments                         |  |  |  |  |  |

| CONVERTER                                                                       |     |     |     |      |                                                  |  |  |  |  |  |

| Conversion Time <sup>1</sup>                                                    |     |     | 20  | ms   | Both channels, 10 ms per channel.                |  |  |  |  |  |

| Wake-Up Time from Power-Down Mode <sup>2, 3</sup>                               |     | 0.3 |     | ms   |                                                  |  |  |  |  |  |

| Power-Up Time <sup>2, 4</sup>                                                   |     | 2   |     | ms   |                                                  |  |  |  |  |  |

| Reset Time <sup>2, 5</sup>                                                      |     | 2   |     | ms   |                                                  |  |  |  |  |  |

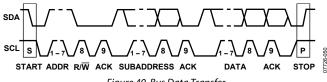

| SERIAL INTERFACE <sup>6, 7</sup>                                                |     |     |     |      | See Figure 2.                                    |  |  |  |  |  |

| SCL Frequency                                                                   | 0   |     | 400 | kHz  |                                                  |  |  |  |  |  |

| SCL High Pulse Width, thigh                                                     | 0.6 |     |     | μs   |                                                  |  |  |  |  |  |

| SCL Low Pulse Width, t <sub>LOW</sub>                                           | 1.3 |     |     | μs   |                                                  |  |  |  |  |  |

| SCL, SDA Rise Time, t <sub>R</sub>                                              |     |     | 0.3 | μs   |                                                  |  |  |  |  |  |

| SCL, SDA Fall Time, t <sub>F</sub>                                              |     |     | 0.3 | μs   |                                                  |  |  |  |  |  |

| Hold Time (Start Condition), thD;STA                                            | 0.6 |     |     | μs   | After this period, the first clock is generated. |  |  |  |  |  |

| Setup Time (Start Condition), t <sub>SU;STA</sub>                               | 0.6 |     |     | μs   | Relevant for repeated start condition.           |  |  |  |  |  |

| Data Setup Time, t <sub>SU;DAT</sub>                                            |     |     |     | μs   |                                                  |  |  |  |  |  |

| Setup Time (Stop Condition), t <sub>SU;STO</sub>                                | 0.6 |     |     | μs   |                                                  |  |  |  |  |  |

| Data Hold Time (Master), t <sub>HD;DAT</sub>                                    | 10  |     |     | ns   |                                                  |  |  |  |  |  |

| Bus-Free Time (Between Stop and Start Conditions), $t_{\text{\scriptsize BUF}}$ | 1.3 |     |     | μs   |                                                  |  |  |  |  |  |

<sup>1</sup> Conversion time is 304 internal clock cycles for both channels (nominal clock 16 kHz); the internal clock frequency is equal to the specified excitation frequency.

<sup>&</sup>lt;sup>7</sup> All input signals are specified with input rise/fall times = 3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Output load = 10 pF.

Figure 2. Serial Interface Timing Diagram

<sup>&</sup>lt;sup>2</sup> Specification is not production tested but is supported by characterization data at initial product release.

<sup>&</sup>lt;sup>3</sup> Wake-up time is the maximum delay between the last SCL edge writing the configuration register and the start of conversion.

<sup>&</sup>lt;sup>4</sup> Power-up time is the maximum delay between the V<sub>DD</sub> crossing the minimum level (1.8 V) and either the start of conversion or when ready to receive a serial interface command.

<sup>&</sup>lt;sup>5</sup> Reset time is the maximum delay between the last SCL edge writing the reset command and either the start of conversion or when ready to receive a serial interface command.

$<sup>^{\</sup>rm 6}$  Sample tested during initial release to ensure compliance.

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 3.

| Parameter                                        | Rating                                     |

|--------------------------------------------------|--------------------------------------------|

| Positive Supply Voltage V <sub>DD</sub> to GND   | -0.3 V to +3.9 V                           |

| Voltage on Any Input or Output to GND            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| ESD Rating                                       |                                            |

| ESD Association Human Body Model, S5.1           | 4 kV                                       |

| Field-Inducted Charged Device Model              | 500 V                                      |

| Operating Temperature Range                      | −40°C to +85°C                             |

| Storage Temperature Range                        | −65°C to +150°C                            |

| Maximum Junction Temperature                     | 150°C                                      |

| LFCSP Package                                    |                                            |

| $\theta_{JA}$ , Thermal Impedance to Air         | 49°C/W                                     |

| $\theta_{\text{JC}}$ , Thermal Impedance to Case | 3°C/W                                      |

| Reflow Soldering (Pb-Free)                       |                                            |

| Peak Temperature                                 | 260(0/-5)°C                                |

| Time at Peak Temperature                         | 10 sec to 40 sec                           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

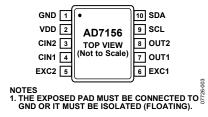

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

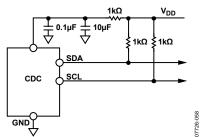

| 2       | VDD      | Power Supply Voltage. This pin should be decoupled to GND using a low impedance capacitor, such as a 0.1 μF X7R multilayer ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                 |

| 3       | CIN2     | CDC Capacitive Input Channel 2. The measured capacitance (sensor) is connected between the EXC2 pin and the CIN2 pin. If not used, this pin can be left open circuit or be connected to GND. When a conversion is performed on Channel 2, the CIN2 pin is internally connected to a high impedance input of the $\Sigma$ - $\Delta$ modulator. When a conversion is performed on the other channel or in idle mode or power-down mode, the CIN2 pin is internally disconnected and left floating by the part. |

| 4       | CIN1     | CDC Capacitive Input Channel 1. The measured capacitance (sensor) is connected between the EXC1 pin and the CIN1 pin. If not used, this pin can be left open circuit or be connected to GND. When a conversion is performed on Channel 1, the CIN1 pin is internally connected to a high impedance input of the $\Sigma$ - $\Delta$ modulator. When a conversion is performed on the other channel or in idle mode or power-down mode, the CIN1 pin is internally disconnected and left floating by the part. |

| 5       | EXC2     | CDC Excitation Output Channel 2. The measured capacitance is connected between the EXC2 pin and the CIN2 pin. If not used, this pin should be left as an open circuit. When a conversion is performed on Channel 2, the EXC2 pin is internally connected to the output of the excitation signal driver. When a conversion is performed on the other channel or in idle mode or power-down mode, the EXC2 pin is internally connected to GND.                                                                  |

| 6       | EXC1     | CDC Excitation Output Channel 1. The measured capacitance is connected between the EXC1 pin and the CIN1 pin. If not used, this pin should be left as an open circuit. When a conversion is performed on Channel 1, the EXC1 pin is internally connected to the output of the excitation signal driver. When a conversion is performed on the other channel or in idle mode or power-down mode, the EXC1 pin is internally connected to GND.                                                                  |

| 7       | OUT1     | Logic Output Channel 1. A high level on this output indicates proximity detected on CIN1.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8       | OUT2     | Logic Output Channel 2. A high level on this output indicates proximity detected on CIN2.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9       | SCL      | Serial Interface Clock Input. This pin connects to the master clock line and requires a pull-up resistor if not provided elsewhere in the system.                                                                                                                                                                                                                                                                                                                                                             |

| 10      | SDA      | Serial Interface Bidirectional Data. This pin connects to the master data line and requires a pull-up resistor if not provided elsewhere in the system.                                                                                                                                                                                                                                                                                                                                                       |

# TYPICAL PERFORMANCE CHARACTERISTICS

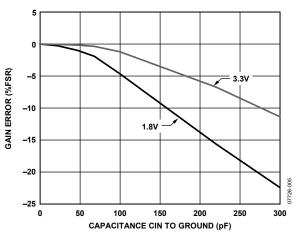

Figure 4. Capacitance Input Offset Error vs. Capacitance CIN to GND,  $V_{\text{DD}}$  = 1.8 V and 3.3 V, EXC Pin Open Circuit

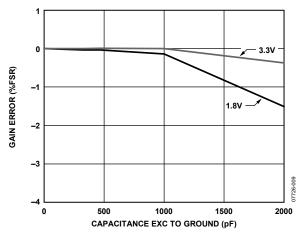

Figure 5. Capacitance Input Gain Error vs. Capacitance CIN to GND,  $V_{\rm DD}=1.8~V$  and 3.3 V, CIN to EXC = 3 pF

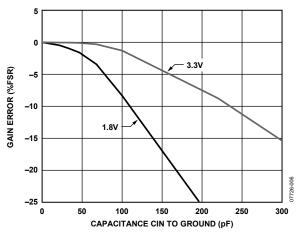

Figure 6. Capacitance Input Gain Error vs. Capacitance CIN to GND,  $V_{\rm DD}=1.8~V$  and 3.3~V, CIN to EXC = 9~pF

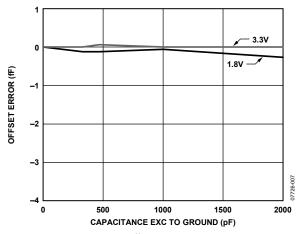

Figure 7. Capacitance Input Offset Error vs. Capacitance EXC to GND,  $V_{DD} = 1.8 \text{ V}$  and 3.3 V, CIN Pin Open Circuit

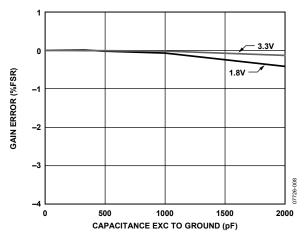

Figure 8. Capacitance Input Gain Error vs. Capacitance EXC to GND,  $V_{DD} = 1.8 \text{ V}$  and 3.3 V, CIN to EXC = 3 pF

Figure 9. Capacitance Input Gain Error vs. Capacitance EXC to GND,  $V_{\rm DD}=1.8~V$  and 3.3~V, CIN to EXC = 9~pF

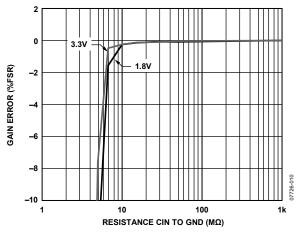

Figure 10. Capacitance Input Gain Error vs. Resistance CIN to GND,  $V_{\rm DD}$  = 1.8 V and 3.3 V, CIN to EXC = 3 pF

Figure 11. Capacitance Input Gain Error vs. Resistance CIN to GND,  $V_{\rm DD}=1.8~V$  and 3.3 V, CIN to EXC = 9 pF

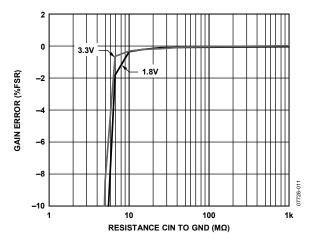

Figure 12. Capacitance Input Gain Error vs. Resistance EXC to GND,  $V_{\rm DD}=1.8~V$  and 3.3 V, CIN to EXC = 3 pF

Figure 13. Capacitance Input Gain Error vs. Resistance EXC to GND,  $V_{DD}=1.8\ V$  and 3.3 V, CIN to EXC = 9 pF

Figure 14. Capacitance Input Gain Error vs. Serial Resistance,  $V_{DD} = 1.8 \text{ V}$  and 3.3 V, CIN to EXC = 3 pF

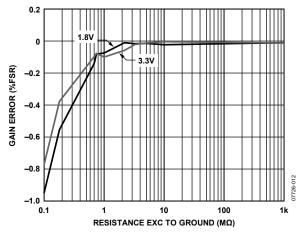

Figure 15. Capacitance Input Gain Error vs. Parallel Resistance,  $V_{\rm DD} = 1.8$  V and 3.3 V, CIN to EXC = 3 pF

Figure 16. Capacitance Input Offset Error vs. Temperature,  $V_{DD} = 1.8 \ V$  and 3.3 V, CIN and EXC Pins Open Circuit

Figure 17. Capacitance Input Gain Error vs. Temperature,  $V_{DD} = 2.7 \text{ V}$ , CIN to EXC = 4 pF

Figure 18. EXC Frequency Error vs. Temperature,  $V_{\rm DD} = 1.8 \text{ V}$ , 2 V, 2.7 V, and 3.6 V

Figure 19. CAPDAC Differential Nonlinearity (DNL),  $V_{DD} = 1.8 \text{ V}$

Figure 20. Current vs. Temperature,  $V_{DD} = 1.8 \text{ V}, 2 \text{ V}, 2.7 \text{ V}, \text{ and } 3.6 \text{ V}$

Figure 21. Power-Down Current vs. Temperature,  $V_{DD} = 1.8 V, 2 V, 2.7 V, and 3.6 V$

# THEORY OF OPERATION

Figure 22. AD7156 Block Diagram

The AD7156 core is a high performance capacitance-to-digital converter (CDC) that allows the part to be interfaced directly to a capacitive sensor.

The comparators compare the CDC results with thresholds, either fixed or dynamically adjusted by the on-chip adaptive threshold algorithm engine. Thus, the outputs indicate a defined change in the input sensor capacitance.

The AD7156 also integrates an excitation source, CAPDAC for the capacitive inputs, an input multiplexer, a complete clock generator, a power-down timer, a power supply monitor, control logic, and an I<sup>2</sup>C\*-compatible serial interface for configuring the part and accessing the internal CDC data and status, if required in the system (see Figure 22).

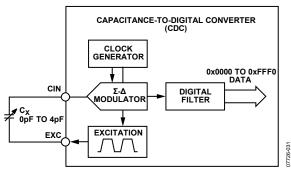

#### **CAPACITANCE-TO-DIGITAL CONVERTER**

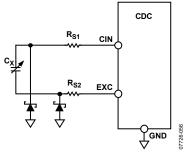

Figure 23 shows the CDC simplified functional diagram. The converter consists of a second-order  $\Sigma$ - $\Delta$  charge balancing modulator and a third-order digital filter. The measured capacitance  $C_X$  is connected between an excitation source and the  $\Sigma$ - $\Delta$  modulator input. The excitation signal is applied on the  $C_X$  capacitor during the conversion, and the modulator continuously samples the charge going through the  $C_X$ . The digital filter processes the modulator output, which is a stream of 0s and 1s containing the information in 0 and 1 density. The data is processed by the adaptive threshold engine and output comparators; the data can also be read through the serial interface.

The AD7156 is designed for floating capacitive sensors. Therefore, both  $C_X$  plates have to be isolated from ground or any other fixed potential node in the system.

The AD7156 features slew rate limiting on the excitation voltage output, which decreases the energy of higher harmonics on the excitation signal and dramatically improves the system electromagnetic compatibility (EMC).

Figure 23. CDC Simplified Block Diagram

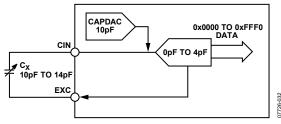

## **CAPDAC**

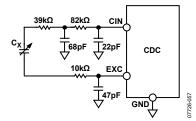

The AD7156 CDC core maximum full-scale input range is 0 pF to 4 pF. However, the part can accept a higher input capacitance, caused, for example, by a nonchanging offset capacitance of up to 10 pF. This offset capacitance can be compensated for by using the programmable on-chip CAPDAC.

Figure 24. Using a CAPDAC

The CAPDAC can be understood as a negative capacitance connected internally to a CIN pin. The CAPDAC has a 6-bit resolution and a monotonic transfer function. Figure 24 shows how to use the CAPDAC to shift the CDC 0 pF to 4 pF input range to measure capacitance between 10 pF and 14 pF.

#### **COMPARATOR AND THRESHOLD MODES**

The AD7156 comparators and their thresholds can be programmed to operate in two modes: fixed and adaptive threshold modes. In an adaptive mode, the threshold is dynamically adjusted and the comparator output indicates fast changes and ignores slow changes in the input (sensor) capacitance. Alternatively, the threshold can be programmed as a constant (fixed) value, and the output then indicates any change in the input capacitance that crosses the defined fixed threshold.

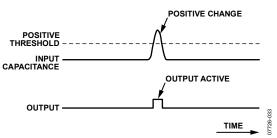

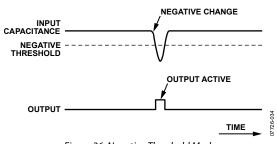

The AD7156 logic output (active high) indicates either a positive or a negative change in the input capacitance, in both adaptive and fixed threshold modes (see Figure 25 and Figure 26).

Figure 25. Positive Threshold Mode Indicates Positive Change in Input Capacitance

Figure 26. Negative Threshold Mode Indicates Negative Change in Input Capacitance

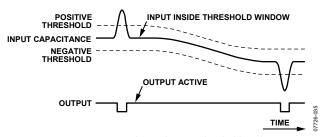

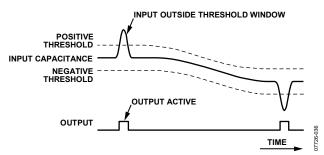

Additionally, for the adaptive mode only, the comparators can work as window comparators, indicating input either inside or outside a selected sensitivity band (see Figure 27 and Figure 28).

Figure 27. In-Window (Adaptive) Threshold Mode

Figure 28. Out-Window (Adaptive) Threshold Mode

## **ADAPTIVE THRESHOLD**

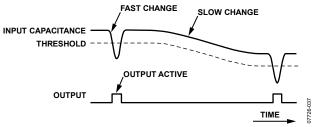

In an adaptive mode, the thresholds are dynamically adjusted, ensuring indication of fast changes (for example, an object moving close to a capacitive proximity sensor) and eliminating slow changes in the input (sensor) capacitance, usually caused by environment changes such as humidity or temperature or changes in the sensor dielectric material over time (see Figure 29).

Figure 29. Adaptive Threshold Indicates Fast Changes and Eliminates Slow Changes in Input Capacitance

## **SENSITIVITY**

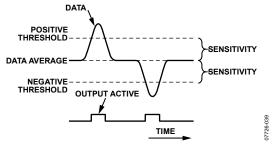

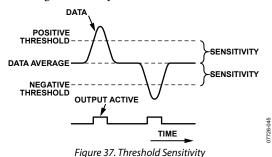

In adaptive threshold mode, the output comparator threshold is set as a defined distance (sensitivity) above the data average, below the data average, or both, depending on the selected threshold mode of operation (see Figure 30). The sensitivity value is programmable in the range of 0 LSB to 255 LSB of the 12-bit CDC converter (see the Register Descriptions section).

Figure 30. Threshold Sensitivity

#### **DATA AVERAGE**

The adaptive threshold algorithm is based on an average calculated from the previous CDC output data, using the following equation:

$$Average(N) = Average(N-1) + \frac{Data(N) - Average(N-1)}{2^{ThrSettling + 1}}$$

where:

Average(N) is the new average value.

Average(N-1) is the average value from the previous cycle. Data(N) is the latest complete CDC conversion result.

*ThrSettling* is a parameter, programmable in the setup registers.

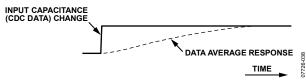

A more specific case of the input capacitance waveform is a step change. The response of the average to an input capacitance step change (more exactly, response to a step change in the CDC output data) is an exponential settling curve, which can be characterized by the following equation:

$$Average(N) = Average(0) + Change(1 - e^{N/TimeConst})$$

where:

*Average*(*N*) is the value of average N complete CDC conversion cycles after a step change on the input.

Average(0) is the value before the step change.

$TimeConst = 2^{(ThrSettling + 1)}$

*ThrSettling* is a parameter, programmable in the setup registers.

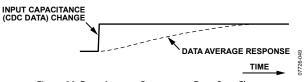

See Figure 31 and the Register Descriptions section for further information.

Figure 31. Data Average Response to Data Step Change

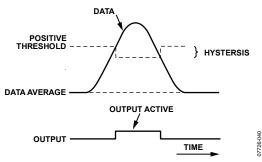

## **HYSTERESIS**

In adaptive threshold mode, the comparator features hysteresis. The hysteresis is fixed to ¼ of the threshold sensitivity and can be programmed on or off. The comparator does not have hysteresis in the fixed threshold mode.

Figure 32. Threshold Hysteresis

#### **TIMEOUT**

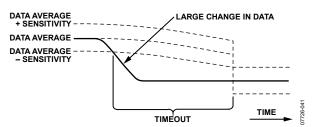

In the case of a large, long change in the capacitive input, when the data average adapting to a new condition takes too long, a timeout can be set.

The timeout becomes active (counting) when the CDC data goes outside the band of data average ± sensitivity. When the timeout elapses (a defined number of CDC conversions is counted), the data average (and thus the thresholds), is forced to follow the new CDC data value immediately (see Figure 33).

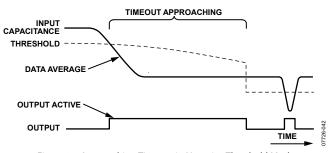

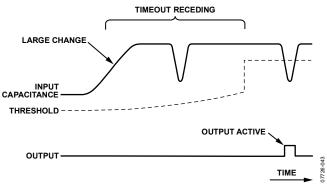

The timeout can be set independently for approaching (for change in data toward the threshold) and for receding (for change in data away from the threshold). See Figure 34, Figure 35, and the Register Descriptions section for further information.

Figure 33. Threshold Timeout After a Large Change in CDC Data

Figure 34. Approaching Timeout in Negative Threshold Mode Shortens False Output Trigger

Figure 35. Positive Timeout in Negative Threshold Mode Shortens Period of Missing Output Trigger

## **AUTO-DAC ADJUSTMENT**

In adaptive threshold mode, the part can dynamically adjust the CAPDAC to keep the CDC in an optimal operating capacitive range. When the auto-DAC function is enabled, the CAPDAC value is automatically incremented when the data average exceeds  $\frac{3}{4}$  of the CDC full range (average > 0xA800), and the CAPDAC value is decremented when the data average goes below  $\frac{1}{4}$  of the CDC full range (average < 0x5800). The auto-DAC increment or decrement step depends on the selected CDC capacitive input range (see the Setup Registers section).

When the CAPDAC value reaches 0, the ¼ threshold for further decrementing is ignored. Similarly, when the CAPDAC value reaches its full range, the ¾ threshold is ignored. The CDC and the rest of the algorithm are continuously working, and they are functional down to a capacitance input of 0 pF or as high as the capacitance input of (CAPDAC full range + CDC full range), respectively.

#### **POWER-DOWN TIMER**

In power sensitive applications, the AD7156 can be set to automatically enter power-down mode after a programmed period of time in which the outputs have not been activated. The AD7156 can then be returned to a normal operational mode either via the serial interface or by the power supply off/on sequence.

# **REGISTER DESCRIPTIONS**

Table 5. Register Summary<sup>1</sup>

|                                          | Addr Pointer |      |        |                          |                            |                  |                         |                |               |             |           |  |  |  |

|------------------------------------------|--------------|------|--------|--------------------------|----------------------------|------------------|-------------------------|----------------|---------------|-------------|-----------|--|--|--|

| Register                                 | Dec          | Hex  | R/W    | Bit 7                    | Bit 6                      | Bit 5            | Bit 4                   | Bit 3          | Bit 2         | Bit 1       | Bit 0     |  |  |  |

| Status                                   | 0            | 0x00 | R      | PwrDown                  | DacStep2                   | OUT2             | DacStep1                | OUT1           | C1/C2         | RDY2        | RDY1      |  |  |  |

|                                          |              |      |        | (0)                      | (1)                        | (0)              | (1)                     | (0)            | (0)           | (1)         | (1)       |  |  |  |

| Ch 1 Data High                           | 1            | 0x01 | R      | 0x00                     |                            |                  |                         |                |               |             |           |  |  |  |

| Ch 1 Data Low                            | 2            | 0x02 | R      |                          | 0x00                       |                  |                         |                |               |             |           |  |  |  |

| Ch 2 Data High                           | 3            | 0x03 | R      |                          | 0x00                       |                  |                         |                |               |             |           |  |  |  |

| Ch 2 Data Low                            | 4            | 0x04 | R      |                          |                            |                  | 0x00                    |                |               |             |           |  |  |  |

| Ch 1 Average High                        | 5            | 0x05 | R      |                          |                            |                  | 0x00                    |                |               |             |           |  |  |  |

| Ch 1 Average Low                         | 6            | 0x06 | R      |                          |                            |                  | 0x00                    |                |               |             |           |  |  |  |

| Ch 2 Average High                        | 7            | 0x07 | R      |                          |                            |                  | 0x00                    |                |               |             |           |  |  |  |

| Ch 2 Average Low                         | 8            | 0x08 | R      |                          |                            |                  | 0x00                    |                |               |             |           |  |  |  |

| Ch 1 Sensitivity/                        | 9            | 0x09 | R/W    | Ch 1 cancitivi           | ity (in adaptive           | threshold mo     | da)/Ch 1 thrach         | old high by    | ta (in fived  | threshold   | l mode)   |  |  |  |

| Ch 1 Threshold High                      |              | 0,09 | IT/ VV | CITTSEIISIUVI            | ity (iii adaptive          | tillesiloid illo | 0x08                    | iola filgif by | te (III IIXeu | tillesiloid | i iiioue) |  |  |  |

| Ch 1 Timeout/                            | 10           | 0x0A | R/W    | Ch 1 timeout             | (in adaptive th            | reshold mode     | e)/CH 1threshol         | d low byte (   | in fixed thi  | reshold m   | ode)      |  |  |  |

| Ch 1 Threshold Low                       |              |      |        |                          |                            |                  | 0x86                    |                |               |             |           |  |  |  |

| Ch 1 Setup                               | 11           | 0x0B | R/W    | RngH1                    | RngL1                      |                  | Hyst1                   | Th             | rSettling1    | (4-bit valu | ıe)       |  |  |  |

|                                          |              |      |        | (0)                      | (0)                        | (0)              | (0)                     |                | (0x           |             |           |  |  |  |

| Ch 2 Sensitivity/<br>Ch 2 Threshold High | 12           | 0x0C | R/W    | Ch 2 sensitivi           | ity (in adaptive           | threshold mo     | de)/Ch 2 thresh<br>0x08 | old high by    | te (in fixed  | threshold   | l mode)   |  |  |  |

| Ch 2 Timeout/                            | 13           | 0x0D | R/W    | Ch 2 timeout             | (in adaptive th            | reshold mode     |                         | ld low byte    | in fixed th   | reshold m   | ode)      |  |  |  |

| Ch 2 Threshold Low                       |              |      |        |                          | . (                        |                  | 0x86                    | ,              | (             |             | ,         |  |  |  |

| Ch 2 Setup                               | 14           | 0x0E | R/W    | RngH2                    | RngL2                      |                  | Hyst2                   | Th             | rSettling2    | (4-bit valu | ıe)       |  |  |  |

|                                          |              |      |        | (0)                      | (0)                        | (0)              | (0)                     |                | (0x           |             | -,        |  |  |  |

| Configuration                            | 15           | 0x0F | R/W    | ThrFixed                 | ThrMD1                     | ThrMD0           | EnCh1                   | EnCh2          | MD2           | MD1         | MD0       |  |  |  |

| -                                        |              |      |        | (0)                      | (0)                        | (0)              | (1)                     | (1)            | (0)           | (0)         | (1)       |  |  |  |

| Power-Down Timer                         | 16           | 0x10 | R/W    |                          |                            |                  | Power-do                | own timeou     | t (6-bit valu | ıe)         |           |  |  |  |

|                                          |              |      |        | (0)                      | (1)                        |                  |                         | (0x00)         |               |             |           |  |  |  |

| Ch 1 CAPDAC                              | 17           | 0x11 | R/W    | DacEn1                   | DacAuto1                   |                  | Dac                     | Value1 (6-b    | it value)     |             |           |  |  |  |

|                                          |              |      |        | (1)                      | (1)                        |                  |                         | (0x00)         |               |             |           |  |  |  |

| Ch 2 CAPDAC                              | 18           | 0x12 | R/W    | DacEn2                   | DacAuto2                   |                  | Dac                     | Value2 (6-b    | it value)     |             |           |  |  |  |

|                                          |              |      |        | (1)                      | (1)                        |                  |                         | (0x00)         |               |             |           |  |  |  |

| Serial Number 3                          | 19           | 0x13 | R      | Serial numbe             | er—Byte 3 (MSE             | )                |                         |                |               |             |           |  |  |  |

| Serial Number 2                          | 20           | 0x14 | R      | Serial numbe             | Serial number—Byte 2       |                  |                         |                |               |             |           |  |  |  |

| Serial Number 1                          | 21           | 0x15 | R      | Serial numbe             | Serial number—Byte 1       |                  |                         |                |               |             |           |  |  |  |

| Serial Number 0                          | 22           | 0x16 | R      | Serial numbe             | Serial number—Byte 0 (LSB) |                  |                         |                |               |             |           |  |  |  |

| Chip ID                                  | 23           | 0x17 | R      | Chip identification code |                            |                  |                         |                |               |             |           |  |  |  |

$<sup>^{\</sup>scriptscriptstyle 1}$  The default values are given in parentheses.

# **STATUS REGISTER**

Address Pointer 0x00 8 Bits, Read Only

# Default Value 0x53 Before Conversion, 0x54 After Conversion

The status register indicates the status of the part. The register can be read via the 2-wire serial interface to query the status of the outputs, check the CDC finished conversion, and check whether the CAPDAC has been changed by the auto-DAC function.

# Table 6. Status Register Bit Map<sup>1</sup>

| Bit 7   | Bit 6    | Bit 5 | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------|----------|-------|-------|-------|-------|

| PwrDown | DacStep2 | OUT2  | DacStep1 | OUT1  | C1/C2 | RDY2  | RDY1  |

| (0)     | (1)      | (0)   | (1)      | (0)   | (0)   | (1)   | (1)   |

<sup>&</sup>lt;sup>1</sup> The default values are given in parentheses.

## Table 7. Status Register Bit Descriptions

| Bit | Mnemonic | Description                                                                                                                                                                                                               |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PwrDown  | PwrDown = 1 indicates that the part is in a power-down.                                                                                                                                                                   |

| 6   | DacStep2 | DacStep2 = 0 indicates that the Channel 2 CAPDAC value was changed after the last CDC conversion as part of the auto-DAC function. The bit value is updated after each finished CDC conversion on this channel.           |

| 5   | OUT2     | OUT2 = 1 indicates that the Channel 2 data (CIN2 capacitance) crossed the threshold, according to the selected comparator mode of operation. The bit value is updated after each finished CDC conversion on this channel. |

| 4   | DacStep1 | DacStep1 = 0 indicates that the Channel 1 CAPDAC value was changed during the last conversion as part of the auto-DAC function. The bit value is updated after each finished CDC conversion on this channel.              |

| 3   | OUT1     | OUT1 = 1 indicates that the Channel 1 data (CIN1 capacitance) crossed the threshold, according to the selected comparator mode of operation. The bit value is updated after each finished CDC conversion on this channel. |

| 2   | C1/C2    | C1/C2 = 0 indicates that the last finished CDC conversion was on Channel 1.<br>C1/C2 = 1 indicates that the last finished CDC conversion was on Channel 2.                                                                |

| 1   | RDY2     | RDY2 = 0 indicates a finished CDC conversion on Channel 2. The bit is reset back to 1 when the Channel 2 data register is read via the serial interface or after a part reset or power-up.                                |

| 0   | RDY1     | RDY1 = 0 indicates a finished CDC conversion on Channel 1. The bit is reset back to 1 when the Channel 1 data register is read via serial interface or after a part reset or power-up.                                    |

#### **DATA REGISTERS**

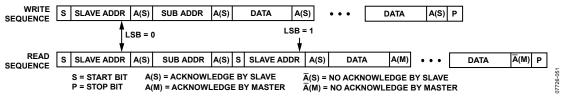

## Ch 1 Address Pointer 0x01, Address Pointer 0x02 Ch 2 Address Pointer 0x03, Address Pointer 0x04 16 Bits, Read Only Default Value 0x0000

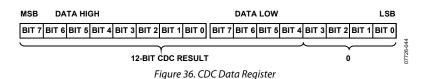

Data from the last complete capacitance-to-digital conversion reflects the capacitance on the input. Only the 12 MSBs of the data registers are used for the CDC result. The 4 LSBs are always 0, as shown in Figure 36.

The data register is updated after a finished conversion on the capacitive channel, with one exception: when the serial interface read operation from the data register is in progress, the data register is not updated and the new capacitance conversion result is lost.

The stop condition on the serial interface is considered to be the end of the read operation. Therefore, to prevent incorrect data reading through the serial interface, the two bytes of a data register should be read sequentially using the register address pointer autoincrement feature of the serial interface.

The nominal AD7156 CDC transfer function (an ideal transfer function excluding offset and/or gain error) maps the input capacitance between zero scale and full scale to output data codes between 0x3000 and 0xD000 only (see Table 8).

For an ideal part, linear, with no offset error and no gain error, the input capacitance can be calculated from the output data using the following equation:

$$C(pF) = \frac{Data - 12,288}{40,960} \times Input \_Range(pF)$$

where Input\_Range = 4 pF, 2 pF, 1 pF, or 0.5 pF.

The following is the same equation written with hexadecimal numbers:

$$C (pF) = \frac{Data - 0x3000}{0xA000} \times Input\_Range (pF)$$

With offset error and gain error included, the equation is:

$$C (pF) = \frac{Data - 12,288}{40,960} \times Input \_Range (pF) \times$$

$$\left(1 + \frac{Gain\_Error(\%)}{100\%}\right) + Offset\_Error (pF)$$

Or the same equation with hexadecimal numbers:

$$C (pF) = \frac{Data - 0x3000}{0xA000} \times Input \_Range (pF) \times$$

$$\left(1 + \frac{Gain\_Error(\%)}{100\%}\right) + Offset\_Error (pF)$$

Table 8. AD7156 Capacitance-to-Data Mapping<sup>1</sup>

| Data   | Input Capacitance                              |

|--------|------------------------------------------------|

| 0x0000 | Under range (below 0 pF)                       |

| 0x3000 | Zero scale (0 pF)                              |

| 0x5800 | Quarter scale (+0.5 pF)—auto-DAC step down     |

| 0x8000 | Midscale (+1 pF)                               |

| 0xA800 | Three-quarter scale (+1.5 pF)—auto-DAC step up |

| 0xD000 | Full scale (+2 pF)                             |

| 0xFFF0 | Over range (above +2 pF)                       |

<sup>&</sup>lt;sup>1</sup> An ideal part with no offset and gain error, values shown in picofarad for 2 pF capacitance input range.

#### **AVERAGE REGISTERS**

Ch 1 Address Pointer 0x05, Address Pointer 0x06 Ch 2 Address Pointer 0x07, Address Pointer 0x08 16 Bits, Read Only Default Value 0x0000

These registers show the average calculated from the previous CDC data. The 12-bit CDC result corresponds to the 12 MSBs of the average register.

The settling time of the average can be set by programming the ThrSettling bits in the setup registers. The average register is overwritten directly with the CDC output data, that is, the history is erased if the timeout is enabled and elapses.

#### FIXED THRESHOLD REGISTERS

Ch 1 Address Pointer 0x09, Address Pointer 0x0A Ch 2 Address Pointer 0x0C, Address Pointer 0x0D 16 Bits, Read/Write, Factory Preset 0x0886

A constant threshold for the output comparator in the fixed threshold mode can be set using these registers. The 12-bit CDC result corresponds to the 12 MSBs of the threshold register. The fixed threshold registers share the address pointer and location on chip with the sensitivity and timeout registers. The fixed threshold registers are not accessible in the adaptive threshold mode.

#### SENSITIVITY REGISTERS

Ch 1 Address Pointer 0x09 Ch 2 Address Pointer 0x0C 8 Bits, Read/Write, Factory Preset 0x08

Sensitivity registers set the distance of the positive threshold above the data average, and the distance of the negative threshold below the data average, in the adaptive threshold mode.

The sensitivity is an 8-bit value and is mapped to the lower eight bits of the 12-bit CDC data, that is, it corresponds to the 16-bit data register as shown in Figure 38.

Figure 38. Relation Between Sensitivity Register and CDC Data Register

For an ideal part with no gain error, the sensitivity can be calculated using the following equation:

$$Sensitivity (pF) = \frac{Sens\_Reg}{2560} \times Input\_Range (pF)$$

Or the same equation with hexadecimal numbers

$$Sensitivity (pF) = \frac{Sens\_Reg}{0xA00} \times Input\_Range (pF)$$

With gain error included, the sensitivity can be calculated using the following equation:

$$Sensitivity (pF) = \frac{Sense\_Reg}{2560} \times Input\_Range (pF) \times$$

$$\left(1 + \frac{Gain\_Error (\%)}{100\%}\right)$$

Or the same equation with hexadecimal numbers

$$Sensitivity (pF) = \frac{Sense\_Reg}{0xA00} \times Input\_Range (pF) \times \left(1 + \frac{Gain\_Error (\%)}{100\%}\right)$$

#### **TIMEOUT REGISTERS**

Ch 1 Address Pointer 0x0A Ch 2 Address Pointer 0x0D 8 Bits, Read/Write, Factory Preset 0x86

Table 9. Timeout Register Bit Map

| Bit   | Mnemonic   | Default |  |  |

|-------|------------|---------|--|--|

| [7:4] | TimeOutApr | 0x08    |  |  |

| [3:0] | TimeOutRec | 0x06    |  |  |

These registers set timeouts for the adaptive threshold mode.

The approaching timeout starts when the CDC data crosses the data average  $\pm$  sensitivity band toward the threshold, according to the selected positive, negative, or window threshold mode. The approaching timeout elapses after the number of conversion cycles equals  $2^{\text{TimeOutApr}}$ , where TimeOutApr is the value of the four most significant bits of the timeout register.

The receding timeout starts when the CDC data crosses the data average  $\pm$  sensitivity band away from the threshold, according to the selected positive or negative threshold mode. The receding timeout is not used in the window threshold mode. The receding timeout elapses after the number of conversion cycles equals  $2^{\text{TimeOutRec}}$ , where TimeOutRec is the value of the four least significant bits of the timeout register.

When either the approaching or receding timeout elapses (that is, after the defined number of CDC conversions is counted), the data average (and thus the thresholds) is forced to follow the new CDC data value immediately.

When the timeout register equals 0, timeouts are disabled.

# **SETUP REGISTERS**

Ch 1 Address Pointer 0x0B Ch 2 Address Pointer 0x0E 8 Bits, Read/Write, Factory Preset 0x0B

Table 10. Setup Registers Bit Map<sup>1</sup>

| Bit 7 | 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                     | Bit 2 | Bit 1 | Bit 0 |  |

|-------|---|-------|-------|-------|---------------------------|-------|-------|-------|--|

| Rngl  | Н | RngL  |       | Hyst  | ThrSettling (4-Bit Value) |       |       |       |  |

| (0)   |   | (0)   | (0)   | (0)   | (0x0B)                    |       |       |       |  |

<sup>&</sup>lt;sup>1</sup> The default values are given in parentheses.

**Table 11. Setup Registers Bit Descriptions**

| Bit   | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                              | า                   |                                                                      |                                    |  |  |  |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|------------------------------------|--|--|--|

| 7     | RngH     | Range bits s                                                                                                                                                                                                                                                                                                                                                                                             | set the CDC input   | range and determine the step for the a                               | uto-DAC function.                  |  |  |  |

| 6     | RngL     | RngH                                                                                                                                                                                                                                                                                                                                                                                                     | RngL                | Capacitive Input Range (pF)                                          | Auto-DAC Step (CAPDAC LSB)         |  |  |  |

|       |          | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 0                   | 2                                                                    | 4                                  |  |  |  |

|       |          | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 1                   | 0.5                                                                  | 1                                  |  |  |  |

|       |          | 1                                                                                                                                                                                                                                                                                                                                                                                                        | 0                   | 1                                                                    | 2                                  |  |  |  |

|       |          | 1                                                                                                                                                                                                                                                                                                                                                                                                        | 1                   | 4                                                                    | 8                                  |  |  |  |

| 5     |          | This bit sho                                                                                                                                                                                                                                                                                                                                                                                             | uld be 0 for the sp | pecified operation.                                                  |                                    |  |  |  |

| 4     | Hyst     |                                                                                                                                                                                                                                                                                                                                                                                                          | •                   | n adaptive threshold mode. This bit has in the fixed threshold mode. | no effect in fixed threshold mode; |  |  |  |

| [3:0] |          | ling time of the adaptive thresholds. Data<br>on:                                                                                                                                                                                                                                                                                                                                                        |                     |                                                                      |                                    |  |  |  |

|       |          | nat is, response to the change in the CDC<br>illowing equation:                                                                                                                                                                                                                                                                                                                                          |                     |                                                                      |                                    |  |  |  |

|       |          | Average(N) = Average(0) + Change(1 – $e^{N/TimeConst}$ )  where:  Average(N) is the value of average N complete CDC conversion cycles after a step change on the inputa Average(0) is the value before the step change.  TimeConst can be selected in the range between 2 and 65,536 conversion cycle multiples, in steps of 2, by programming the ThrSettling bits. $TimeConst = 2^{(ThrSettling + 1)}$ |                     |                                                                      |                                    |  |  |  |

Figure 39. Data Average Response to Data Step Change

# **CONFIGURATION REGISTER**

Address Pointer 0x0F 8 Bits, Read/Write, Factory Preset 0x19

Table 12. Configuration Register Bit Map<sup>1</sup>

| Bit 7    | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------|--------|-------|-------|-------|-------|-------|

| ThrFixed | ThrMD1 | ThrMD0 | EnCh1 | EnCh2 | MD2   | MD1   | MD0   |

| (0)      | (0)    | (0)    | (1)   | (1)   | (0)   | (0)   | (1)   |

$<sup>^{\</sup>mbox{\tiny 1}}$  The default values are given in parentheses.

**Table 13. Configuration Register Bit Descriptions**

| Bit | Mnemonic | Descrip                                                                                                                                                                                                                                                                                                                                                      | tion       |              |                          |                                                                                                                         |                                                            |  |  |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|

| 7   | ThrFixed | ThrFixed = 1 sets the fixed threshold mode; the outputs reflect the comparison of data and a fixed (constant) value of the threshold registers.  ThrFixed = 0 sets the adaptive threshold mode; the outputs reflect the comparison of data to the adaptive thresholds. The adaptive threshold is set dynamically, based on the history of the previous data. |            |              |                          |                                                                                                                         |                                                            |  |  |

| 6   | ThrMD1   | These bi                                                                                                                                                                                                                                                                                                                                                     | ts set the | output co    | omparators mode          | •                                                                                                                       | •                                                          |  |  |

| 5   | ThrMD0   |                                                                                                                                                                                                                                                                                                                                                              |            |              |                          | Output A                                                                                                                | ctive When                                                 |  |  |

|     |          | ThrMD1                                                                                                                                                                                                                                                                                                                                                       | l Th       | rMD0         | Threshold Mode           | Adaptive Threshold Mode                                                                                                 | Fixed Threshold Mode                                       |  |  |

|     |          | 0                                                                                                                                                                                                                                                                                                                                                            | 0          |              | Negative                 | Data < average – sensitivity                                                                                            | Data < threshold                                           |  |  |

|     |          | 0                                                                                                                                                                                                                                                                                                                                                            | 1          |              | Positive                 | Data > average + sensitivity                                                                                            | Data > threshold                                           |  |  |

|     |          | 1                                                                                                                                                                                                                                                                                                                                                            | 0          |              | In-window                | Data > average - sensitivity and                                                                                        |                                                            |  |  |

|     |          | 1                                                                                                                                                                                                                                                                                                                                                            | 1          |              | Out window               | Data < average + sensitivity                                                                                            |                                                            |  |  |

|     |          | I                                                                                                                                                                                                                                                                                                                                                            | '          |              | Out-window               | Data < average – sensitivity or                                                                                         |                                                            |  |  |

|     |          |                                                                                                                                                                                                                                                                                                                                                              |            |              |                          | Data > average + sensitivity                                                                                            |                                                            |  |  |

| 4   | EnCh1    | Enables                                                                                                                                                                                                                                                                                                                                                      | conversio  | on on Cha    | nnel 1                   | 1                                                                                                                       | <u> </u>                                                   |  |  |

| 3   | EnCh2    | Enables                                                                                                                                                                                                                                                                                                                                                      | conversio  | n on Cha     | nnel 2                   |                                                                                                                         |                                                            |  |  |

| 2   | MD2      | Convert                                                                                                                                                                                                                                                                                                                                                      | er mode o  | of operation | on setup                 |                                                                                                                         |                                                            |  |  |

| 1   | MD1      | MD2                                                                                                                                                                                                                                                                                                                                                          | MD1        | MD0          | Mode                     | Description                                                                                                             |                                                            |  |  |

| 0   | MD0      | 0                                                                                                                                                                                                                                                                                                                                                            | 0          | 0            | Idle                     | The part is fully powered up, k                                                                                         | out performing no conversion                               |  |  |