## **Multimodal Sensor Front End**

## ADPD4100/ADPD4101

#### **Data Sheet**

#### **FEATURES**

Multimodal analog front end

8 input channels with multiple operation modes for various sensor measurements

Dual-channel processing with simultaneous sampling 12 programmable time slots for synchronized sensor measurements

Flexible input multiplexing to support differential and single-ended sensor measurements

8 LED drivers, 4 of which can be driven simultaneously Flexible sampling rate from 0.004 Hz to 9 kHz using internal oscillators

**On-chip digital filtering**

SNR of transmit and receive signal chain: 100 dB AC ambient light rejection: 60 dB up to 1 kHz

400 mA total LED peak drive current

Total system power dissipation: 30 μW (combined LED and AFE power), continuous PPG measurement at 75 dB SNR, 25 Hz ODR, 100 nA/mA CTR

SPI and I<sup>2</sup>C communications supported 512-byte FIFO size

#### **APPLICATIONS**

Wearable health and fitness monitors: heart rate monitors (HRMs), heart rate variability (HRV), stress, blood pressure estimation, SpO<sub>2</sub>, hydration, body composition Industrial monitoring: CO, CO<sub>2</sub>, smoke, and aerosol detection Home patient monitoring

#### **GENERAL DESCRIPTION**

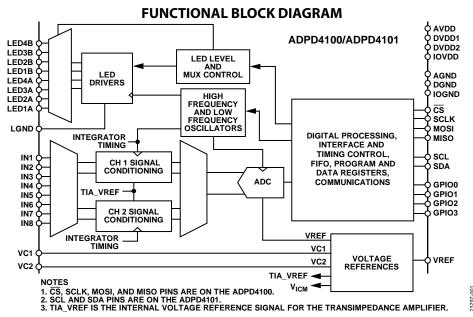

The ADPD4100/ADPD4101 operate as a complete multimodal sensor front end, stimulating up to eight light emitting diodes (LEDs) and measuring the return signal on up to eight separate current inputs. Twelve time slots are available, enabling 12 separate measurements per sampling period.

The data output and functional configuration utilize an I<sup>2</sup>C interface on the ADPD4101 or a serial port interface (SPI) on the ADPD4100. The control circuitry includes flexible LED signaling and synchronous detection. The devices use a 1.8 V analog core and 1.8 V/3.3 V compatible digital input/output (I/O).

The analog front end (AFE) rejects signal offsets and corruption from asynchronous modulated interference, typically from ambient light, eliminating the need for optical filters or externally controlled dc cancellation circuitry. Multiple operating modes are provided, enabling the ADPD4100/ADPD4101 to be a sensor hub for synchronous measurements of photodiodes, biopotential electrodes, resistance, capacitance, and temperature sensors. The multiple operation modes accommodate various sensor measurements, including, but not limited to, photoplethysmography (PPG), electrocardiography (ECG), electrodermal activity (EDA), impedance, capacitance, temperature, gas detection, smoke detection, and aerosol detection for various healthcare, industrial, and consumer applications.

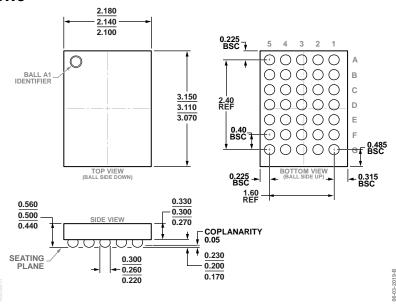

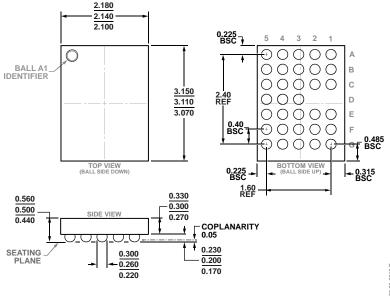

The ADPD4100/ADPD4101 are available in a 3.11 mm  $\times$  2.14 mm, 0.4 mm pitch, 33-ball WLCSP and 35-ball WLCSP.

Figure 1

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagram                     | 1  |

| Revision History                             | 2  |

| Specifications                               | 3  |

| Temperature and Power Specifications         | 3  |

| Performance Specifications                   | 4  |

| Digital Specifications                       | 6  |

| Timing Specifications                        | 6  |

| Absolute Maximum Ratings                     | 9  |

| Thermal Resistance                           | 9  |

| Electrostatic Discharge (ESD) Ratings        | 9  |

| ESD Caution                                  | 9  |

| Pin Configurations and Function Descriptions | 10 |

| Typical Performance Characteristics          | 13 |

| Theory of Operation                          | 15 |

| Introduction                                 | 15 |

| Analog Signal Path                           | 15 |

| LED Drivers                                  | 16 |

| Determining C <sub>VLED</sub>                | 17 |

| Datapath, Decimation, Subsampling, and FIFO  | 18 |

| Clocking                                     | 21 |

| Time Stamp Operation                         | 22 |

| Low Frequency Oscillator Calibration         | 22 |

| High Frequency Oscillator Calibration        | 22 |

| Time Slot Operation                                      |

|----------------------------------------------------------|

| Execution Modes                                          |

| Host Interface                                           |

| Applications Information                                 |

| Operating Mode Overview                                  |

| Analog Integration Mode                                  |

| Digital Integration Mode                                 |

| TIA ADC Mode42                                           |

| Protecting Against TIA Saturation in Normal Operation 42 |

| ECG Measurement with the ADPD4100/ADPD4101 44            |

| Register Map51                                           |

| Register Details                                         |

| Global Configuration Registers70                         |

| Interrupt Status and Control Registers72                 |

| Threshold Setup and Control Registers 82                 |

| Clock and Timestamp Setup and Control Registers 84       |

| System Registers                                         |

| I/O Setup and Control Registers86                        |

| Time Slot Configuration Registers                        |

| AFE Timing Setup Registers94                             |

| LED Control and Timing Registers96                       |

| ADC Offset Registers                                     |

| Output Data Registers                                    |

| Outline Dimensions                                       |

| Ordering Guide                                           |

#### **REVISION HISTORY**

6/2020—Revision 0: Initial Version

## **SPECIFICATIONS**

#### **TEMPERATURE AND POWER SPECIFICATIONS**

**Table 1. Operating Conditions**

| Parameter                                     | Test Conditions/Comments                   | Min | Тур | Max  | Unit |

|-----------------------------------------------|--------------------------------------------|-----|-----|------|------|

| TEMPERATURE RANGE                             |                                            |     |     |      |      |

| Operating                                     |                                            | -40 |     | +85  | °C   |

| Storage                                       |                                            | -65 |     | +150 | °C   |

| POWER SUPPLY VOLTAGE                          |                                            |     |     |      |      |

| Supply, V <sub>DD</sub>                       | Applied at the AVDD, DVDD1, and DVDD2 pins | 1.7 | 1.8 | 1.9  | V    |

| Input/Output Driver Supply, IOV <sub>DD</sub> | Applied at the IOVDD pin                   | 1.7 | 1.8 | 3.6  | V    |

$AVDD = DVDDx = IOVDD = 1.8 \text{ V}, T_A = 25$ °C, unless otherwise noted.

**Table 2. Current Consumption**

| Parameter                                      | Symbol                   | Test Conditions/Comments                                                                                                                                         | Min | Тур  | Max | Unit |

|------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| POWER SUPPLY (V <sub>DD</sub> )<br>CURRENT     |                          |                                                                                                                                                                  |     |      |     |      |

| V <sub>DD</sub> Supply Current <sup>1</sup>    |                          | Signal-to-noise ratio (SNR) = 75 dB, 25 Hz output data rate (ODR), single time slot, 1 MHz low frequency oscillator frequency                                    |     | 10   |     | μΑ   |

|                                                |                          | SNR = 75 dB, 25 Hz ODR, single time slot, 32 kHz low frequency oscillator frequency                                                                              |     | 8    |     | μΑ   |

| Total System Power<br>Dissipation              |                          | Combined LED and AFE power, continuous PPG measurement at 75 dB SNR, 25 Hz ODR, 100 nA/mA current transfer ratio (CTR), 1 MHz low frequency oscillator frequency |     | 30   |     | μW   |

|                                                |                          | Combined LED and AFE power, continuous PPG measurement at 75 dB SNR, 25 Hz ODR, 100 nA/mA CTR, 32 kHz low frequency oscillator frequency                         |     | 26   |     | μW   |

| Peak V <sub>DD</sub> Supply Current<br>(1.8 V) |                          |                                                                                                                                                                  |     |      |     |      |

| 1-Channel Operation                            | IV <sub>DD_PEAK</sub>    | Peak VDD current during time slot sampling                                                                                                                       |     | 3.8  |     | mA   |

| Standby Mode Current                           | IV <sub>DD_STANDBY</sub> |                                                                                                                                                                  |     | 0.20 |     | μΑ   |

$<sup>^{\</sup>rm 1}\,\mbox{V}_{\mbox{\scriptsize DD}}$  is the voltage applied at the AVDD and DVDDx pins.

#### **PERFORMANCE SPECIFICATIONS**

AVDD = DVDDx = IOVDD = 1.8 V, T<sub>A</sub> = full operating temperature range, unless otherwise noted.

Table 3.

| Parameter                                        | Test Conditions/Comments                                  |       | Тур  | Max  | Unit  |

|--------------------------------------------------|-----------------------------------------------------------|-------|------|------|-------|

| DATA ACQUISITION                                 |                                                           |       |      |      |       |

| Datapath Width                                   |                                                           |       |      | 32   | Bits  |

| FIRST IN, FIRST OUT (FIFO) SIZE                  |                                                           |       |      | 512  | Bytes |

| LED DRIVER                                       |                                                           |       |      |      |       |

| LED Peak Current per Driver                      | LED pulse enabled                                         | 1.5   |      | 200  | mA    |

| LED Peak Current, Total                          | Using multiple LED drivers simultaneously                 |       |      | 400  | mA    |

| Driver Compliance Voltage                        | For any LED driver output at LED_CURRENTx_x = 0x7F        |       |      | 300  | mV    |

| LEDxx Pin Voltage <sup>1</sup>                   |                                                           |       |      | 3.6  | V     |

| Highest LED Peak Current per Driver <sup>2</sup> | For any LED driver at LED_CURRENTx_x = 0x7F               | 176   | 200  | 208  | mA    |

| LED PERIOD                                       | AFE width = $4 \mu s^3$                                   | 11    |      |      | μs    |

|                                                  | AFE width = 3 μs                                          | 9     |      |      | μs    |

| SAMPLING RATE <sup>4</sup>                       | Single time slot, four data bytes to FIFO, 2 µs LED pulse | 0.004 |      | 9000 | Hz    |

| OSCILLATOR DRIFT                                 |                                                           |       |      |      |       |

| 32 kHz Oscillator                                | Percent variation from 25°C to 85°C                       |       | 6    |      | %     |

|                                                  | Percent variation from +25°C to -40°C                     |       | -8.5 |      | %     |

| 1 MHz Oscillator                                 | Percent variation from 25°C to 85°C                       |       | 3    |      | %     |

|                                                  | Percent variation from +25°C to -40°C                     |       | -4   |      | %     |

| 32 MHz Oscillator                                | Percent Variation from 25°C to 85°C                       |       | 1    |      | %     |

|                                                  | Percent Variation from +25°C to -40°C                     |       | -1.5 |      | %     |

<sup>&</sup>lt;sup>1</sup> LEDxx refers to LED1A, LED2A, LED3A, LED4A, LED1B, LED2B, LED3B, and LED4B.

Table 4.

| Parameter                                 | Test Conditions/Comments                        | Min  | Тур  | Max | Unit   |

|-------------------------------------------|-------------------------------------------------|------|------|-----|--------|

| TRANSIMPEDANCE AMPLIFIER (TIA) GAIN       |                                                 | 12.5 |      | 200 | kΩ     |

| PULSED SIGNAL CONVERSIONS, 3 μs LED PULSE | 4 μs integration width, continuous connect mode |      |      |     |        |

| ADC Resolution <sup>1</sup>               | TIA feedback resistor                           |      |      |     |        |

|                                           | 12.5 kΩ                                         |      | 6.2  |     | nA/LSB |

|                                           | 25 kΩ                                           |      | 3.1  |     | nA/LSB |

|                                           | 50 kΩ                                           |      | 1.5  |     | nA/LSB |

|                                           | 100 kΩ                                          |      | 0.77 |     | nA/LSB |

|                                           | 200 kΩ                                          |      | 0.38 |     | nA/LSB |

| ADC Saturation Level <sup>2</sup>         | TIA feedback resistor                           |      |      |     |        |

|                                           | 12.5 kΩ                                         |      | 50   |     | μΑ     |

|                                           | 25 kΩ                                           |      | 25   |     | μΑ     |

|                                           | 50 kΩ                                           |      | 12.5 |     | μΑ     |

|                                           | 100 kΩ                                          |      | 6.22 |     | μΑ     |

|                                           | 200 kΩ                                          |      | 3.11 |     | μΑ     |

<sup>&</sup>lt;sup>2</sup> The maximum value in this specification is the maximum value at LED driver current setting = 0x7F on LED Driver LED1A, and the minimum value in this specification is the minimum value at LED driver current setting = 0x7F on LED Driver LED4B. Typically, the LED peak current is the highest on LED1A and the lowest on LED4B, while the rest of the drivers fall in between, and the LED peak current of the LEDxA drivers are higher than that of LEDxB drivers of the same number. For example, the LED peak current of LED3A is higher than that of LED3B.

<sup>&</sup>lt;sup>3</sup> Minimum LED period =  $(2 \times AFE \text{ width}) + 3 \mu s$ .

<sup>&</sup>lt;sup>4</sup> The maximum value in this specification is the internal ADC sampling rate using the internal 1 MHz state machine clock. The I<sup>2</sup>C and SPI read rates in some configurations may limit the ODR.

**Data Sheet**

## ADPD4100/ADPD4101

| Parameter                                 | Test Conditions/Comments                                                                                                                                                                                                                    | Min | Тур       | Max | Unit   |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----|--------|

| PULSED SIGNAL CONVERSIONS, 2 μs LED PULSE | 3 μs integration width, continuous connect mode                                                                                                                                                                                             |     |           |     |        |

| ADC Resolution <sup>1</sup>               | TIA feedback resistor                                                                                                                                                                                                                       |     |           |     |        |

|                                           | 12.5 kΩ                                                                                                                                                                                                                                     |     | 8.2       |     | nA/LSB |

|                                           | 25 kΩ                                                                                                                                                                                                                                       | 4   | 4.1       |     | nA/LSB |

|                                           | 50 kΩ                                                                                                                                                                                                                                       |     | 2.04      |     | nA/LSB |

|                                           | 100 kΩ                                                                                                                                                                                                                                      |     | 1.02      |     | nA/LSB |

|                                           | 200 kΩ                                                                                                                                                                                                                                      |     | 0.51      |     | nA/LSB |

| ADC Saturation Level <sup>2</sup>         | TIA feedback resistor                                                                                                                                                                                                                       |     |           |     |        |

|                                           | 12.5 kΩ                                                                                                                                                                                                                                     | (   | 67        |     | μΑ     |

|                                           | 25 kΩ                                                                                                                                                                                                                                       | :   | 33        |     | μΑ     |

|                                           | 50 kΩ                                                                                                                                                                                                                                       |     | 16.7      |     | μΑ     |

|                                           | 100 kΩ                                                                                                                                                                                                                                      |     | 8.37      |     | μA     |

|                                           | 200 kΩ                                                                                                                                                                                                                                      |     | 4.19      |     | μΑ     |

| FULL SIGNAL CONVERSIONS                   |                                                                                                                                                                                                                                             |     |           |     |        |

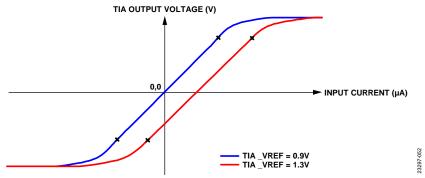

| TIA Linear Dynamic Range (per Channel)    | Total input current, 1% compression point, TIA_VREF = 1.265 V                                                                                                                                                                               |     |           |     |        |

| , , ,                                     | 12.5 kΩ                                                                                                                                                                                                                                     |     | 72        |     | μΑ     |

|                                           | 25 kΩ                                                                                                                                                                                                                                       |     | 38        |     | μA     |

|                                           | 50 kΩ                                                                                                                                                                                                                                       |     | 18.7      |     | μA     |

|                                           | 100 kΩ                                                                                                                                                                                                                                      |     | 9.3       |     | μA     |

|                                           | 200 kΩ                                                                                                                                                                                                                                      |     | 4.6       |     | μA     |

| SYSTEM PERFORMANCE                        |                                                                                                                                                                                                                                             |     |           |     | •      |

| Referred to Input Noise                   | Continuous connect mode, single pulse, single channel, floating input, TIA_VREF = 1.265 V, 3 µs integration time                                                                                                                            |     |           |     |        |

|                                           | 12.5 kΩ TIA gain                                                                                                                                                                                                                            |     | 8.2       |     | nA rms |

|                                           | 25 kΩ TIA gain                                                                                                                                                                                                                              |     | 4.1       |     | nA rms |

|                                           | 50 kΩ TIA gain                                                                                                                                                                                                                              |     | 2.2       |     | nA rms |

|                                           | 100 kΩ TIA gain                                                                                                                                                                                                                             |     | 1.2       |     | nA rms |

|                                           | 200 kΩ TIA gain                                                                                                                                                                                                                             | (   | 0.61      |     | nA rms |

| Referred to Input Noise                   | Continuous connect mode, single pulse, single channel, 90% full-scale input signal, no ambient light, TIA_VREF = 1.265 V, VCx = TIA_VREF + 215 mV, 2 $\mu$ s LED pulse, photodiode capacitance (CPD) = 70 pF, input resistor = 500 $\Omega$ |     |           |     |        |

|                                           | 12.5 kΩ TIA gain                                                                                                                                                                                                                            |     | 10.3      |     | nA rms |

|                                           | 25 kΩ TIA gain                                                                                                                                                                                                                              |     | 5.3       |     | nA rms |

|                                           | 50 kΩ TIA gain                                                                                                                                                                                                                              |     | 2.7       |     | nA rms |

|                                           | 100 kΩ TIA gain                                                                                                                                                                                                                             |     | 1.5       |     | nA rms |

|                                           | 200 kΩ TIA gain                                                                                                                                                                                                                             |     | 0.97      |     | nA rms |

| SNR                                       | 12.5 kΩ TIA gain, single pulse                                                                                                                                                                                                              |     | 76        |     | dB     |

| 5                                         | 25 kΩ TIA gain, single pulse                                                                                                                                                                                                                |     | 76        |     | dB     |

|                                           | 50 kΩ TIA gain, single pulse                                                                                                                                                                                                                |     | 75        |     | dB     |

|                                           | 100 kΩ TIA gain, single pulse                                                                                                                                                                                                               |     | 74        |     | dB     |

|                                           | 200 kΩ TIA gain, single pulse                                                                                                                                                                                                               |     | , .<br>72 |     | dB     |

|                                           | 100 kΩ TIA gain, 100 Hz ODR, 80 pulses, $C_{PD}$ = 70 pF, 0.5 Hz to 20 Hz bandwidth, transmit and receive signal chain                                                                                                                      |     | 100       |     | dB     |

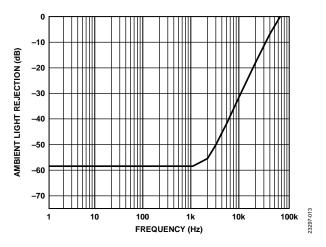

| AC Ambient Light Rejection                | DC to 1 kHz, linear range of TIA, TIA gain = 25 k $\Omega$ , 50 k $\Omega$ , 100 k $\Omega$ , 200 k $\Omega$                                                                                                                                | ,   | 60        |     | dB     |

|                                           | DC to 1 kHz, linear range of TIA, TIA gain = $12.5 \text{ k}\Omega$                                                                                                                                                                         | !   | 55        |     | dB     |

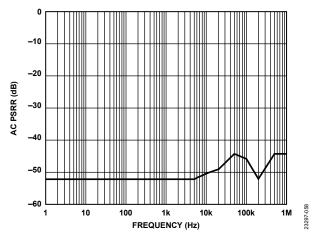

| DC Power Supply Rejection Ratio (PSRR)    | At 75% full scale input                                                                                                                                                                                                                     |     | 50        |     | dB     |

<sup>&</sup>lt;sup>1</sup> ADC resolution is listed per pulse. If using multiple pulses, divide by the number of pulses. <sup>2</sup> ADC saturation level applies to pulsed signal only, because ambient signal is rejected prior to ADC conversion.

#### **DIGITAL SPECIFICATIONS**

IOVDD = 1.7 V to 3.6 V, unless otherwise noted.

**Table 5. Digital Specifications**

| Parameter                   | Symbol           | Test Conditions/Comments       | Min         | Тур | Max                 | Unit |

|-----------------------------|------------------|--------------------------------|-------------|-----|---------------------|------|

| LOGIC INPUTS                |                  |                                |             |     |                     |      |

| Input Voltage Level         |                  |                                |             |     |                     |      |

| SCL, SDA                    |                  |                                |             |     |                     |      |

| High                        | V <sub>IH</sub>  |                                | 0.7 × IOVDD |     | 3.6                 | ٧    |

| Low                         | V <sub>IL</sub>  |                                | -0.3        |     | $+0.3 \times IOVDD$ | ٧    |

| GPIOx, MISO, MOSI, SCLK, CS |                  |                                |             |     |                     |      |

| High                        | V <sub>IH</sub>  |                                | 0.7 × IOVDD |     | IOVDD + 0.3         | ٧    |

| Low                         | V <sub>IL</sub>  |                                | -0.3        |     | $+0.3 \times IOVDD$ | ٧    |

| Input Current Level         |                  | All logic inputs               |             |     |                     |      |

| High                        | I <sub>IH</sub>  |                                |             |     | 10                  | μΑ   |

| Low                         | IIL              |                                | -10         |     |                     | μΑ   |

| Input Capacitance           | C <sub>IN</sub>  |                                |             | 2   |                     | рF   |

| LOGIC OUTPUTS               |                  |                                |             |     |                     |      |

| Output Voltage Level        |                  |                                |             |     |                     |      |

| GPIOx, MISO                 |                  |                                |             |     |                     |      |

| High                        | $V_{OH}$         | 2 mA high level output current | IOVDD – 0.5 |     |                     | ٧    |

| Low                         | V <sub>OL</sub>  | 2 mA low level output current  |             |     | 0.5                 | ٧    |

| SDA                         |                  |                                |             |     |                     |      |

| Low                         | V <sub>OL1</sub> | 3 mA low level output current  |             |     | 0.4                 | ٧    |

| Output Current Level        |                  | SDA                            |             |     |                     |      |

| Low                         | loL              | $V_{OL1} = 0.4 V$              | 20          |     |                     | mA   |

#### **TIMING SPECIFICATIONS**

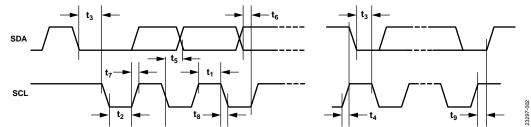

Table 6. I<sup>2</sup>C Timing Specifications for the ADPD4101

| Parameter                          | Symbol                | Test Conditions/Comments | Min | Тур | Max | Unit |

|------------------------------------|-----------------------|--------------------------|-----|-----|-----|------|

| TIMING REQUIREMENTS                |                       | See Figure 2             |     |     |     |      |

| I <sup>2</sup> C Port <sup>1</sup> |                       |                          |     |     |     |      |

| SCL                                |                       |                          |     |     |     |      |

| Frequency                          |                       |                          |     |     | 1   | Mbps |

| Minimum Pulse Width                |                       |                          |     |     |     |      |

| High                               | t <sub>1</sub>        |                          | 260 |     |     | ns   |

| Low                                | t <sub>2</sub>        |                          | 500 |     |     | ns   |

| Start Condition                    |                       |                          |     |     |     |      |

| Hold Time                          | t <sub>3</sub>        |                          | 260 |     |     | ns   |

| Setup Time                         | t <sub>4</sub>        |                          | 260 |     |     | ns   |

| SDA                                |                       |                          |     |     |     |      |

| Hold Time <sup>2</sup>             | t <sub>5</sub>        |                          | 0   |     |     |      |

| Setup Time                         | <b>t</b> <sub>6</sub> |                          | 50  |     |     | ns   |

| SCL and SDA                        |                       |                          |     |     |     |      |

| Rise Time                          | t <sub>7</sub>        |                          |     |     | 120 | ns   |

| Fall Time                          | t <sub>8</sub>        |                          |     |     | 120 | ns   |

| Stop Condition                     |                       |                          |     |     |     |      |

| Setup Time                         | <b>t</b> <sub>9</sub> |                          | 260 |     |     | ns   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

<sup>&</sup>lt;sup>2</sup> Both timing requirement and switching characteristic.

Data Sheet ADPD4100/ADPD4101

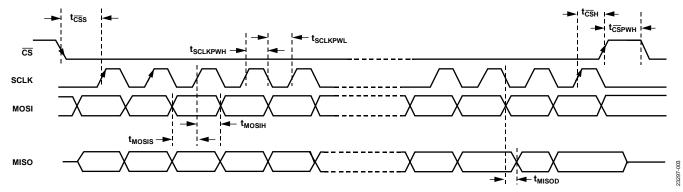

Table 7. SPI Timing Specifications for the ADPD4100

| Parameter                 | Symbol               | Test Conditions/Comments                                                     | Min | Тур | Max  | Unit |

|---------------------------|----------------------|------------------------------------------------------------------------------|-----|-----|------|------|

| TIMING REQUIREMENTS       |                      |                                                                              |     |     |      |      |

| SPI Port                  |                      |                                                                              |     |     |      |      |

| SCLK                      |                      |                                                                              |     |     |      |      |

| Frequency                 | f <sub>SCLK</sub>    |                                                                              |     |     | 24   | MHz  |

| Minimum Pulse Width       |                      |                                                                              |     |     |      |      |

| High                      | t <sub>SCLKPWH</sub> |                                                                              | 15  |     |      | ns   |

| Low                       | t <sub>SCLKPWL</sub> |                                                                              | 15  |     |      | ns   |

| <del>CS</del>             |                      |                                                                              |     |     |      |      |

| Setup Time                | t <sub>css</sub>     | CS setup to SCLK rising edge                                                 | 11  |     |      | ns   |

| Hold Time                 | t <sub>CSH</sub>     | CS hold from SCLK rising edge                                                | 5   |     |      | ns   |

| Pulse Width High          | t                    | CS pulse width high                                                          | 15  |     |      | ns   |

| MOSI                      |                      |                                                                              |     |     |      |      |

| Setup Time                | tmosis               | MOSI setup to SCLK rising edge                                               | 5   |     |      | ns   |

| Hold Time                 | tmosih               | MOSI hold from SCLK rising edge                                              | 5   |     |      | ns   |

| SWITCHING CHARACTERISTICS |                      |                                                                              |     |     |      |      |

| MISO Output Delay         | t <sub>MISOD</sub>   | MISO valid output delay from SCLK falling edge                               |     |     |      |      |

|                           |                      | Register $0x00B4 = 0x0050$ (default)                                         |     |     | 21.5 | ns   |

|                           |                      | Register 0x00B4 = 0x005F (maximum slew rate, maximum drive strength for SPI) |     |     | 14.0 | ns   |

Table 8. Timing Specifications for Provision of External Low Frequency Oscillator

| Parameter                       | Min | Тур | Max  | Unit |

|---------------------------------|-----|-----|------|------|

| FREQUENCY                       |     |     |      |      |

| 1 MHz Low Frequency Oscillator  | 500 |     | 2000 | kHz  |

| 32 kHz Low Frequency Oscillator | 10  |     | 100  | kHz  |

| DUTY CYCLE                      |     |     |      |      |

| 1 MHz Low Frequency Oscillator  | 10  |     | 90   | %    |

| 32 kHz Low Frequency Oscillator | 10  |     | 90   | %    |

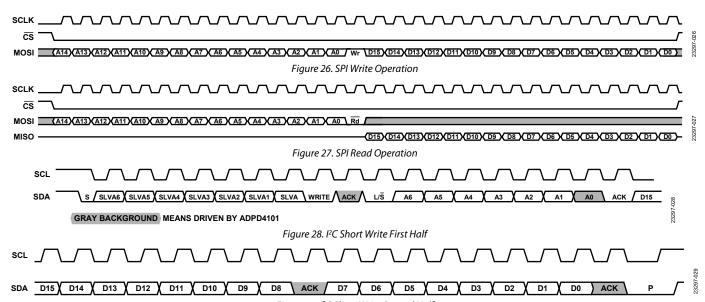

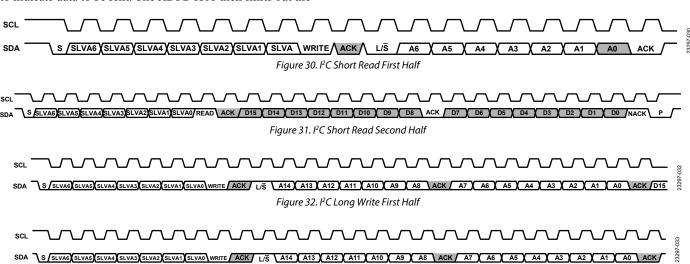

#### Timing Diagrams

Figure 2. I<sup>2</sup>C Timing Diagram for the ADPD4101

Figure 3. SPI Timing Diagram for the ADPD4100

### **ABSOLUTE MAXIMUM RATINGS**

Table 9.

| Parameter                                       | Rating           |

|-------------------------------------------------|------------------|

| AVDD to AGND                                    | -0.3 V to +2.2 V |

| DVDD1, DVDD2 to DGND                            | −0.3 V to +2.2 V |

| IOVDD to DGND                                   | -0.3 V to +3.9 V |

| GPIOx, MOSI, MISO, SCLK, $\overline{CS}$ , SCL, | -0.3 V to +3.9 V |

| SDA to DGND                                     |                  |

| LEDxx to LGND                                   | −0.3 V to +3.9 V |

| Junction Temperature                            | 150°C            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

Table 10. Thermal Resistance

| Package Type <sup>1</sup> | $\Theta_{JA}$ | θıc  | Unit |

|---------------------------|---------------|------|------|

| CB-35-2                   | 41.89         | 0.98 | °C/W |

| CB-33-1                   | 42.15         | 0.98 | °C/W |

<sup>&</sup>lt;sup>1</sup> The thermal resistance values are defined as per the JESD51-12 standard.

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001 and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

#### ESD Ratings for ADPD4100/ADPD4101

Table 11. ADPD4100/ADPD4101, 35-Ball and 33-Ball WLCSP

| ESD Model | Withstand Threshold (V) | Class          |

|-----------|-------------------------|----------------|

| HBM       | 2000                    | 2              |

| CDM       | 1250                    | C3             |

| MM        | 100                     | Not applicable |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

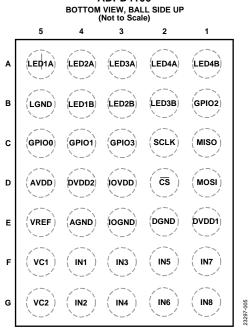

ADPD4100

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

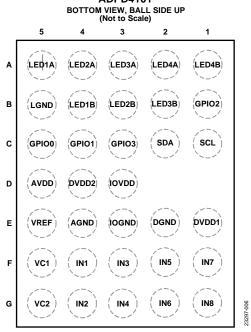

Figure 4. ADPD4100 Pin Configuration

**Table 12. ADPD4100 Pin Function Descriptions**

| Pin No. | Mnemonic  | Type <sup>1</sup> | Description                                                                                |  |

|---------|-----------|-------------------|--------------------------------------------------------------------------------------------|--|

| A5      | LED1A     | AO                | LED Driver 1A Current Sink. If not in use, leave this pin floating.                        |  |

| A4      | LED2A     | AO                | LED Driver 2A Current Sink. If not in use, leave this pin floating.                        |  |

| A3      | LED3A     | AO                | LED Driver 3A Current Sink. If not in use, leave this pin floating.                        |  |

| A2      | LED4A     | AO                | LED Driver 4A Current Sink. If not in use, leave this pin floating.                        |  |

| A1      | LED4B     | AO                | D Driver 4B Current Sink. If not in use, leave this pin floating.                          |  |

| B5      | LGND      | S                 | LED Driver Ground.                                                                         |  |

| B4      | LED1B     | AO                | LED Driver 1B Current Sink. If not in use, leave this pin floating.                        |  |

| B3      | LED2B     | AO                | LED Driver 2B Current Sink. If not in use, leave this pin floating.                        |  |

| B2      | LED3B     | AO                | LED Driver 3B Current Sink. If not in use, leave this pin floating.                        |  |

| B1      | GPIO2     | DIO               | General-Purpose I/O 2. This pin is used for interrupts and various clocking options.       |  |

| C5      | GPIO0     | DIO               | General-Purpose I/O 0. This pin is used for interrupts and various clocking options.       |  |

| C4      | GPIO1     | DIO               | General-Purpose I/O 1. This pin is used for interrupts and various clocking options.       |  |

| C3      | GPIO3     | DIO               | General-Purpose I/O 3. This pin is used for interrupts and various clocking options.       |  |

| C2      | SCLK      | DI                | SPI Clock Input.                                                                           |  |

| C1      | MISO      | DO                | SPI Master Input/Slave Output.                                                             |  |

| D5      | AVDD      | S                 | 1.8 V Analog Supply.                                                                       |  |

| D4      | DVDD2     | S                 | 1.8 V Digital Supply.                                                                      |  |

| D3      | IOVDD     | S                 | 1.8 V/3.3 V I/O Driver Supply.                                                             |  |

| D2      | <u>CS</u> | DI                | SPI Chip Select Input.                                                                     |  |

| D1      | MOSI      | DI                | SPI Master Output/Slave Input.                                                             |  |

| E5      | VREF      | REF               | Internally Generated ADC Voltage Reference. Buffer this pin with a 1 µF capacitor to AGND. |  |

| E4      | AGND      | S                 | Analog Ground.                                                                             |  |

| E3      | IOGND     | S                 | I/O Driver Ground.                                                                         |  |

| E2      | DGND      | S                 | Digital Ground.                                                                            |  |

| E1      | DVDD1     | S                 | 1.8 V Digital Supply.                                                                      |  |

| F5      | VC1       | AO                | Output Voltage Source 1 for Photodiode Common Cathode Bias or Other Sensor Stimulus.       |  |

| F4      | IN1       | Al                | Current Input 1. If not in use, leave this pin floating.                                   |  |

| F3      | IN3       | Al                | Current Input 3. If not in use, leave this pin floating.                                   |  |

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                          |

|---------|----------|-------------------|--------------------------------------------------------------------------------------|

| F2      | IN5      | Al                | Current Input 5. If not in use, leave this pin floating.                             |

| F1      | IN7      | Al                | Current Input 7. If not in use, leave this pin floating.                             |

| G5      | VC2      | AO                | Output Voltage Source 2 for Photodiode Common Cathode Bias or Other Sensor Stimulus. |

| G4      | IN2      | Al                | Current Input 2. If not in use, leave this pin floating.                             |

| G3      | IN4      | Al                | Current Input 4. If not in use, leave this pin floating.                             |

| G2      | IN6      | Al                | Current Input 6. If not in use, leave this pin floating.                             |

| G1      | IN8      | Al                | Current Input 8. If not in use, leave this pin floating.                             |

<sup>&</sup>lt;sup>1</sup> AO means analog output, S means supply, DIO means digital input/output, DI means digital input, DO means digital output, REF means voltage reference, and AI means analog input.

ADPD4101

Figure 5. ADPD4101 Pin Configuration

Table 13. ADPD4101 Pin Function Descriptions

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                |

|---------|----------|-------------------|--------------------------------------------------------------------------------------------|

| A5      | LED1A    | AO                | LED Driver 1A Current Sink. If not in use, leave this pin floating.                        |

| A4      | LED2A    | AO                | LED Driver 2A Current Sink. If not in use, leave this pin floating.                        |

| A3      | LED3A    | AO                | LED Driver 3A Current Sink. If not in use, leave this pin floating.                        |

| A2      | LED4A    | AO                | LED Driver 4A Current Sink. If not in use, leave this pin floating.                        |

| A1      | LED4B    | AO                | LED Driver 4B Current Sink. If not in use, leave this pin floating.                        |

| B5      | LGND     | S                 | LED Driver Ground.                                                                         |

| B4      | LED1B    | AO                | LED Driver 1B Current Sink. If not in use, leave this pin floating.                        |

| B3      | LED2B    | AO                | LED Driver 2B Current Sink. If not in use, leave this pin floating.                        |

| B2      | LED3B    | AO                | LED Driver 3B Current Sink. If not in use, leave this pin floating.                        |

| B1      | GPIO2    | DIO               | General-Purpose I/O 2. This pin is used for interrupts and various clocking options.       |

| C5      | GPIO0    | DIO               | General-Purpose I/O 0. This pin is used for interrupts and various clocking options.       |

| C4      | GPIO1    | DIO               | General-Purpose I/O 1. This pin is used for interrupts and various clocking options.       |

| C3      | GPIO3    | DIO               | General-Purpose I/O 3. This pin is used for interrupts and various clocking options.       |

| C2      | SDA      | DIO               | I <sup>2</sup> C Data Input/Output.                                                        |

| C1      | SCL      | DI                | I <sup>2</sup> C Clock Input.                                                              |

| D5      | AVDD     | S                 | 1.8 V Analog Supply.                                                                       |

| D4      | DVDD2    | S                 | 1.8 V Digital Supply.                                                                      |

| D3      | IOVDD    | S                 | 1.8 V/3.3 V I/O Driver Supply.                                                             |

| E5      | VREF     | REF               | Internally Generated ADC Voltage Reference. Buffer this pin with a 1 µF capacitor to AGND. |

| E4      | AGND     | S                 | Analog Ground.                                                                             |

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                          |  |

|---------|----------|-------------------|--------------------------------------------------------------------------------------|--|

| E3      | IOGND    | S                 | I/O Driver Ground.                                                                   |  |

| E2      | DGND     | S                 | Digital Ground.                                                                      |  |

| E1      | DVDD1    | S                 | 1.8 V Digital Supply.                                                                |  |

| F5      | VC1      | AO                | Output Voltage Source 1 for Photodiode Common Cathode Bias or Other Sensor Stimulus. |  |

| F4      | IN1      | Al                | Current Input 1. If not in use, leave this pin floating.                             |  |

| F3      | IN3      | Al                | Current Input 3. If not in use, leave this pin floating.                             |  |

| F2      | IN5      | Al                | Current Input 5. If not in use, leave this pin floating.                             |  |

| F1      | IN7      | Al                | Current Input 7. If not in use, leave this pin floating.                             |  |

| G5      | VC2      | AO                | Output Voltage Source 2 for Photodiode Common Cathode Bias or Other Sensor Stimulus. |  |

| G4      | IN2      | Al                | Current Input 2. If not in use, leave this pin floating.                             |  |

| G3      | IN4      | Al                | Current Input 4. If not in use, leave this pin floating.                             |  |

| G2      | IN6      | Al                | Current Input 6. If not in use, leave this pin floating.                             |  |

| G1      | IN8      | Al                | Current Input 8. If not in use, leave this pin floating.                             |  |

<sup>&</sup>lt;sup>1</sup> AO means analog output, S means supply, DIO means digital input/output, DI means digital input, DO means digital output, REF means voltage reference, and AI means analog input.

### TYPICAL PERFORMANCE CHARACTERISTICS

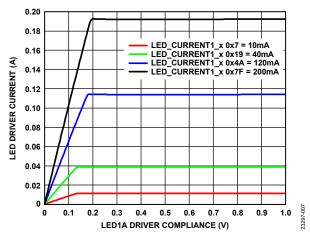

Figure 6. LED Driver Current vs. LED1A Driver Compliance at LED\_CURRENT1\_x = 0x7 (10 mA), 0x19 (40 mA), 0x4A (120 mA), and 0x7F (200 mA)

Figure 7. AC PSRR vs. Frequency

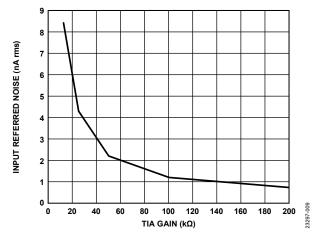

Figure 8. Input Referred Noise vs. TIA Gain,  $C_{PD}$  = 70 pF, Integrator Input Resistor = 400 k $\Omega$

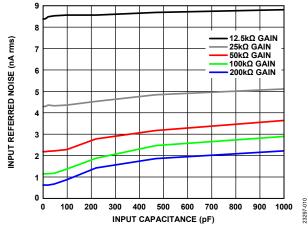

Figure 9. Input Referred Noise vs. Input Capacitance, Integrator Input Resistor = 400 k $\Omega$

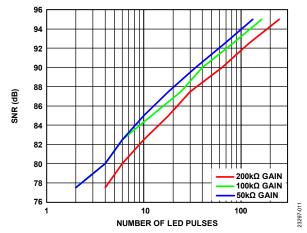

Figure 10. SNR vs. Number of LED Pulses in Continuous Connect Mode,  $C_{PD} = 70$  pF, Integrator Input Resistor = 400 k $\Omega$ , 90% Full Scale

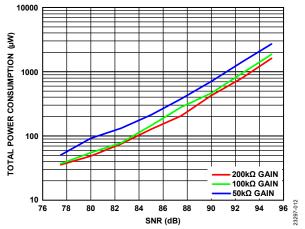

Figure 11. Total Power Consumption vs SNR in Continuous Connect Mode Including LED Power,  $C_{PD} = 70$  pF, Integrator Input Resistor = 400 k $\Omega$ , ODR = 25 Hz, CTR = 150 nA/mA, LED Supply Voltage = 4 V, 90% of Full Scale

Figure 12. Ambient Light Rejection vs. Frequency

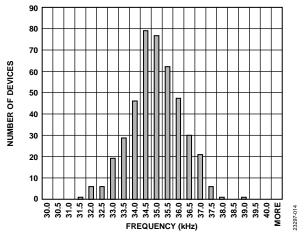

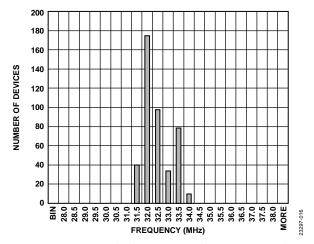

Figure 13. 32 kHz Clock Frequency Distribution, Untrimmed

Figure 14. 1 MHz Clock Frequency Distribution, Untrimmed

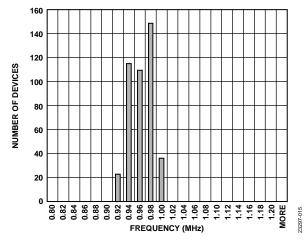

Figure 15. 32 MHz Clock Frequency Distribution, Untrimmed

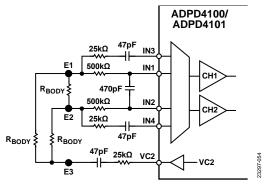

# THEORY OF OPERATION INTRODUCTION

The ADPD4100/ADPD4101 operate as a complete multimodal sensor front end, stimulating up to eight LEDs and measuring the return signal on up to eight separate current inputs. Twelve time slots are available, enabling 12 separate measurements per sampling period. The analog inputs can be driven single-ended or in differential pairs. The eight analog inputs are multiplexed into a single channel or two independent channels, enabling simultaneous sampling of two sensors.

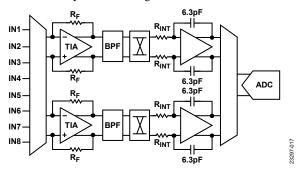

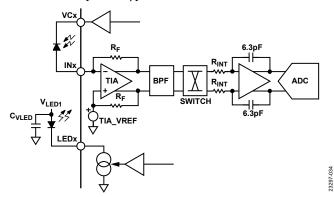

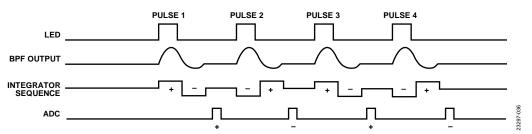

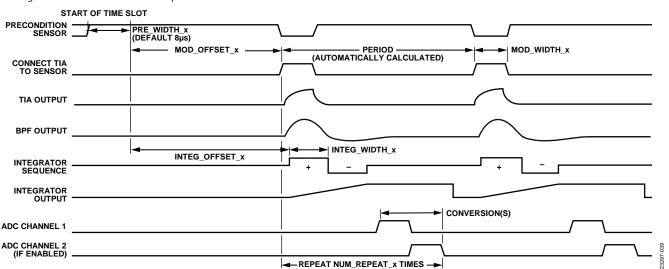

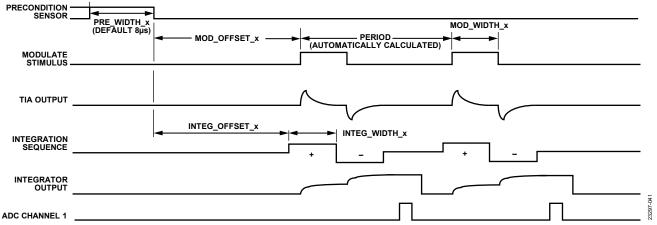

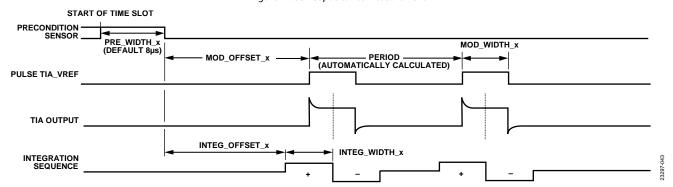

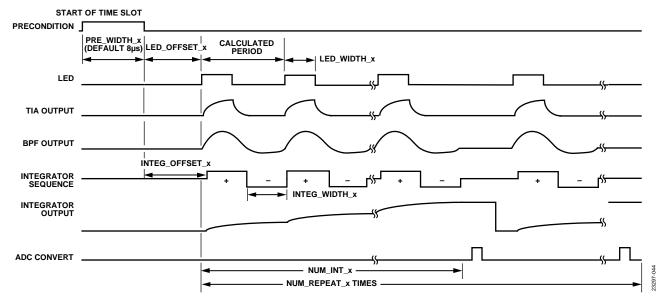

The AFE consists of a TIA, band-pass filter (BPF), integrator, and analog-to-digital converter (ADC). The digital block provides multiple operating modes, programmable timing, four general-purpose input/output (GPIO) pins, block averaging, and a selectable second- through fourth-order cascaded integrator comb (CIC) filter. Eight independent LED drivers are provided that can each drive up to 200 mA. Four LED drivers can be enabled in any time slot and can be programmed from 1.5 mA to 200 mA monotonically, with a 7-bit register setting. The LED drivers enabled in any time slot can provide a total combined maximum of 400 mA of LED current.

The core circuitry provides stimulus to the sensors connected to the inputs of the device and measures the response, storing the results in discrete data locations. The eight inputs can drive two simultaneous input channels, either in a single-ended or differential configuration. Data is read directly by a register or through a FIFO method. This highly integrated system includes an analog signal processing block, digital signal processing block, an I<sup>2</sup>C communication interface on the ADPD4101 or an SPI port on the ADPD4100, programmable pulsed LED current sources, and pulsed voltage sources for sensors that require voltage excitation.

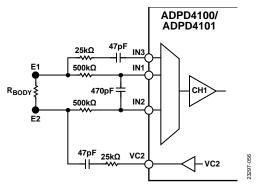

When making optical measurements, the ADPD4100/ADPD4101 provide 60 dB of ac ambient light rejection using a synchronous modulation scheme with pulses as short as 1  $\mu$ s combined with a BPF. Ambient light rejection is automatic without the need of external control loops, dc current subtraction, or digital algorithms.

The LED driver is a current sink and is independent from the LED supply voltage and the LED type. The inputs can be connected to any sensor that provides currents up to 200  $\mu A$ . The ADPD4100/ADPD4101 can also interface with voltage output sensors with a series resistor placed between the sensor output and the ADPD4100/ADPD4101 inputs to convert the voltage to a current. The ADPD4100/ADPD4101 produce a high SNR for relatively low LED power while greatly reducing the effect of ambient light on the measured signal.

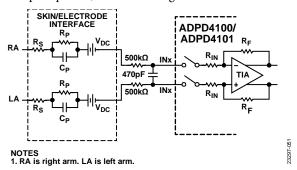

#### **ANALOG SIGNAL PATH**

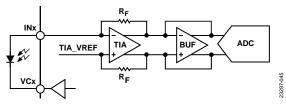

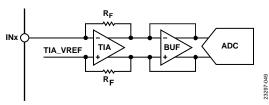

The ADPD4100/ADPD4101 analog signal path consists of eight current inputs that can be configured as single-ended or differential pairs into one of two independent channels. The two channels can be sampled simultaneously for applications

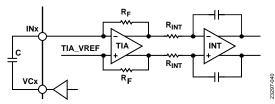

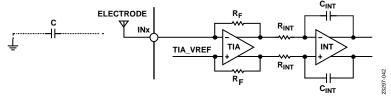

that require instantaneous sampling of two sensors. Each channel contains a TIA with programmable gain, a BPF with a high-pass corner at 100 kHz and a low-pass cutoff frequency of 390 kHz, and an integrator capable of integrating  $\pm 7.5$  pC per sample. Each channel is time multiplexed into a 14-bit ADC. In Figure 16,  $R_F$  is the TIA feedback resistor, and  $R_{\rm INT}$  is the series resistor to the input of the integrator.

Figure 16. Analog Signal Path Block Diagram

#### **Analog Input Multiplexer**

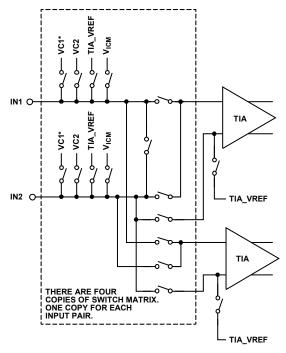

The ADPD4100/ADPD4101 support eight analog input pins. Each input can be used as a single-ended input or as part of a differential pair. Figure 17 shows a single representation of the input switch matrix, which allows programmable connection to the two AFE channels. Each pair of inputs has an exact duplicate of this multiplexer: IN1 and IN2, IN3 and IN4, IN5 and IN6, and IN7 and IN8. The connections are programmable per time slot.

\*ALL BIAS CONNECTIONS SHOWN ARE ONLY AVAILABLE DURING SLEEP AND PRECONDITIONING PERIODS. THE SWITCHES TO THESE BIAS LEVEL ARE OPEN DURING TIME SLOTS WITH THE RESPECTIVE INPUTS SELECTED.

Figure 17. Analog Input Multiplexer

The PAIR12, PAIR34, PAIR36, and PAIR78 bits select whether the matching input pair is used as two single-ended inputs or as a differential pair. This selection is valid for all active time slots. The INP12\_x, INP34\_x, INP56\_x, and INP78\_x bits specify whether the input pair is enabled during the corresponding time slot and, if enabled, which input is connected to which AFE channel.

The sleep conditions are used for any inputs that are not enabled. Sleep conditions are determined by the INP\_SLEEP\_12, INP\_SLEEP\_34, INP\_SLEEP\_56, and INP\_SLEEP\_78 bits, which specify the state for the input pairs during sleep and when the inputs are not active. Inputs are only considered active during the precondition and pulse regions for time slots where they are enabled.

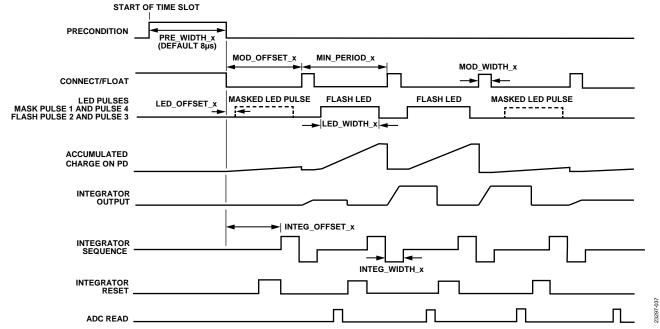

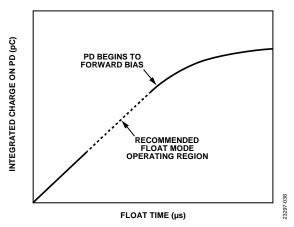

Preconditioning of the sensor connected to the input is provided to set the operating point at the input just prior to sampling. There are several different options for preconditioning determined by the PRECON\_x bits. The PRECON\_x bits are provided for each time slot to specify the precondition for enabled inputs or input pairs during the corresponding time slot. Preconditioning options include: float the input(s), VC1, VC2, input common-mode voltage ( $V_{\rm ICM}$ ), TIA\_VREF, TIA input, and short the input pair. The preconditioning time at the start of each time slot is programmable using the PRE\_WIDTH\_x bits. The default preconditioning period is 8 µs.

The block diagram in Figure 17 shows all the bias levels that can be switched into the input connections during sleep and preconditioning. These connections are not available during the sampling phase of a time slot in which the input is selected.

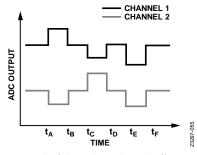

#### Second AFE Channel

The second AFE channel is disabled by default. When disabled, the three amplifiers (TIA, BPF, and integrator) are automatically powered down, and no ADC cycles occur for the second channel. Digital integration and impulse response mode do not use the second channel.

The second AFE channel can be enabled with the CH2\_EN\_x bits on a per time slot basis. When the second channel is enabled, ADC conversions and the datapath bits of the second channel operate. When data is being written to the FIFO, the Channel 2 data is written after the Channel 1 data.

Channel 2 TIA gain, integrator resistor, and buffer gain (when in digital integrate or TIA ADC mode) are set separately from Channel 1.

#### **LED DRIVERS**

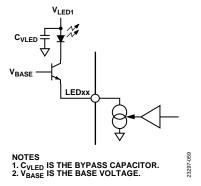

The ADPD4100/ADPD4101 have four LED drivers, each of which is brought out to two LED driver outputs providing a total of eight LED output drivers. The device can drive up to four LEDs simultaneously, one from each driver pair. The LED output driver is a current sink. Figure 18 shows an example of a single LED driver output pair.

Figure 18. Block Diagram of LED Driver Output Pair

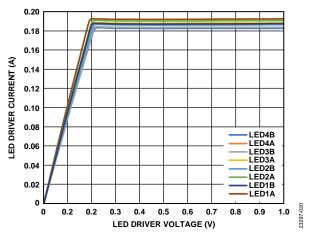

The LED driver output pins (LED1A, LED1B, LED2A, LED2B, LED3A, LED3B, LED4A, and LED4B) have a maximum allowable pin voltage of 3.6 V. Any voltage exposure over this rating affects the reliability of the device operation and, in certain circumstances, causes the device to cease proper operation. The voltage of the LED driver output pins must not be confused with the supply voltages for the LED themselves.  $V_{\text{LEDx}}$  is the voltage applied to the anode of the external LED whereas the LED output driver pin is connected to the cathode of the external LED. The compliance voltage is the amount of headroom voltage at the LED driver pin, measured with respect to ground, required to maintain the programmed LED current level and is a function of the current required. Figure 6 shows the typical compliance voltages required at various LED current settings for LED driver LED1A, and Figure 19 shows the typical compliance voltages for all the LED drivers at the maximum LED current setting. Due to internal layout of the LED driver circuitry, some drivers output more or less current than others at any given setting. Typically, the LED1A and LED1B drivers are ~3% higher than the LED4A and LED4B drivers, respectively, with the 2× and 3× drivers falling somewhere in between. Also, the LEDxA drivers are ~3% higher than the LEDxB driver of the same number.

Figure 19. LED Driver Current vs. LED Driver Voltage for LED Drivers (LEDxA, LEDxB) for LED CURRENTx x = 0x7F

Data Sheet ADPD4100/ADPD4101

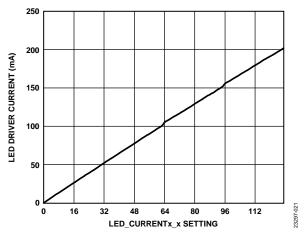

Either side of each LED driver output pair, but not both, can be driven in any of the 12 available time slots. Up to four LED driver outputs can be enabled in any time slot using the LED\_DRIVESIDE1\_x, LED\_DRIVESIDE2\_x, LED\_DRIVESIDE3\_x, and LED\_DRIVESIDE4\_x bits. The current is set on a per driver, per time slot basis using the LED\_CURRENT1\_x, LED\_CURRENT2\_x, LED\_CURRENT3\_x, and LED\_CURRENT4\_x bits. Each driver can be programmed from 1.5 mA to 200 mA with a monotonic 7-bit setting, as shown in Figure 20. Each setting from 1 to 127 increases the LED drive current by ~1.5 mA. Setting LED\_CURRENTx\_x = 0 disables that particular driver.

Although each driver can be programmed to 200 mA and up to four LED drivers can be enabled in any time slot, there is a limitation of a total of 400 mA of combined LED driver current that can be provided in any time slot. It is up to the user to program the LED drivers such that this 400 mA limit is not exceeded. If the 400 mA limit is exceeded by the user settings, priority is given, in the following order, to LED1x, LED2x, LED3x, and LED4x. For example, if the user settings have LED1A set to 150 mA, LED2B set to 150 mA, and LED3A set to 150 mA in a single time slot, LED1A and LED2B both provide 150 mA. However, LED3A is limited to 100 mA to maintain the 400 mA total LED drive current limit for the device.

Figure 20. LED Driver Current vs. LED\_CURRENTx\_x Setting

#### **LED Driver Protection from High Inductance**

If the total inductance in the path between the LED and the ADPD4100/ADPD4101 LED driver pin (LEDxA or LEDxB) and in the path between the LED and the LED supply voltage ( $V_{\text{LEDx}}$ ) is significant due to the use of long wires and multiple connectors, connect a reverse biased protection diode to a suitable high supply voltage such as  $V_{\text{LEDx}}$  at the LED driver pin used. That is, connect a reverse biased protection diode between the LED driver pin used and  $V_{\text{LEDx}}$ .

#### **LED Driver Protection from LED Driver Pin Overvoltage**

In typical designs, no external components are needed on the LED driver. However, in some cases where the LED driver pin voltage has the possibility to be pulled above 3.6 V, an external NPN bipolar junction transistor (BJT) type transistor can be connected to the LED driver pin, as shown in Figure 21. This additional transistor serves as a protection of the LED driver pin from exceeding the maximum allowable LEDxx pin voltage of 3.6 V.

Protecting the LED driver pins from overvoltage is required when  $(V_{\rm LEDx}-LED$  turn on voltage) > 3.6 V, or when the voltage source has a shunt resistance of less than 10  $M\Omega$  and the supply voltage is above 3.6 V. For example,  $V_{\rm LEDx}$  of 6 V can be used without pulling the LED driver pins up past 3.6 V for low leakage LEDs such as some green and blue LEDs. Typically, when  $V_{\rm LEDx}<$  6 V, the protection transistor is not necessary.

Figure 21. LED Driver Overvoltage Protection Circuit

The NPN BJT selection must follow these guidelines:

- The current capacity must match the maximum LED driver current on the LED. The maximum LED driver current is 200 mA for one LED driver and 400 mA for multiple LED drivers connected to the same LED.

- The voltage rating of the transistor must exceed the supply being used on the load.

- The base emitter voltage must be ≤0.9 V at the maximum LED driver current on the LED.

- Lower collector emitter voltages at the maximum LED driver current on the LED provide more operating room for the load being driven.

#### **DETERMINING CYLED**

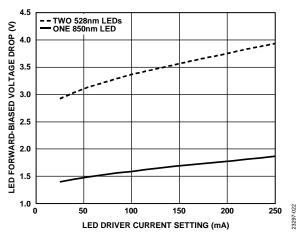

To determine the bypass capacitor ( $C_{VLED}$ ) value, determine the maximum forward-biased voltage,  $V_{FB\_LED\_MAX}$ , of the LED in operation. The maximum LED current,  $I_{LED\_MAX}$ , converts to  $V_{FB\_LED\_MAX}$  as shown in Figure 22. In this example, 125 mA of current through two green LEDs in parallel yields  $V_{FB\_LED\_MAX} = 3.5$  V. Any series resistance in the LED path must also be included in this voltage. When designing the LED path, keep in mind that small resistances can add up to large voltage drops due to the LED peak current being large. In addition, these resistances can be unnecessary constraints on the  $V_{LEDx}$  supply.

Figure 22. Example of the Average LED Forward-Biased Voltage Drop as a Function of the LED Driver Current Setting

To correctly size the  $C_{\text{VLED}}$  capacitor, do not deplete it during the pulse of the LED to the point where the voltage on the capacitor is less than the forward bias on the LED. Calculate the minimum value for  $C_{\text{VLED}}$  as follows:

$$C_{VLED} = (t_{LED\_PW} \times I_{LED\_MAX}) / (V_{LED\_MIN} - (V_{FB\_LED\_MAX} + V_{COMP})) \quad (1)$$

#### where:

$t_{LED\_PW}$  is the LED pulse width.

$I_{LED\_MAX}$  is the maximum forward-biased current on the LED used in operating the devices.

$V_{LED\_MIN}$  is the lowest voltage from the  $V_{LED_x}$  supply with no load.  $V_{FB\_LED\_MAX}$  is the maximum forward-biased voltage required on the LED to achieve  $I_{LED\_MAX}$ .

$V_{COMP}$  is the compliance voltage of the LED driver at the programmed LED drive level.

The numerator of Equation 1 sets up the total discharge amount in coulombs from the bypass capacitor to satisfy a single programmed LED pulse of the maximum current. The denominator represents the difference between the lowest voltage from the  $V_{\rm LEDx}$  supply and the LED required voltage. The LED required

voltage is the voltage of the anode of the LED such that the compliance of the LED driver and the forward-biased voltage of the LED operating at the maximum current is satisfied. At a 125 mA drive current, the compliance voltage of the driver is ~0.4 V. For a typical ADPD4100/ADPD4101 example, assume that the lowest value for the  $V_{\rm LEDx}$  supply is 4.5 V and that the peak current is 125 mA for two 528 nm LEDs in parallel. The minimum value for  $C_{\rm VLED}$  is then equal to 1  $\mu F$ .

$$C_{VLED} = (3 \times 10^{-6} \times 0.125)/(4.5 - (3.5 + 0.4)) = 0.625 \text{ nF}$$

(2)

As shown in Equation 2, as the minimum supply voltage drops close to the maximum anode voltage, the demands on  $C_{VLED}$  become more stringent, forcing the capacitor value higher. It is important to insert the correct values into Equation 2. For example, using an average value for  $V_{LED\_MIN}$  instead of the worst case value for  $V_{LED\_MIN}$  can cause a serious design deficiency, resulting in a  $C_{VLED}$  value that is too small, causing insufficient optical power in the application.

Additionally, multiple pulses can cause further droop on the  $V_{\rm LEDx}$  supply if the  $C_{\rm VLED}$  capacitor is not fully recharged between pulses. Therefore, adding a sufficient margin on  $C_{\rm VLED}$  is strongly recommended. Add additional margin to  $C_{\rm VLED}$  to account for multiple pulses and derating of the capacitor value over voltage, bias, temperature, and other factors over the life of the component.

## DATAPATH, DECIMATION, SUBSAMPLING, AND FIFO

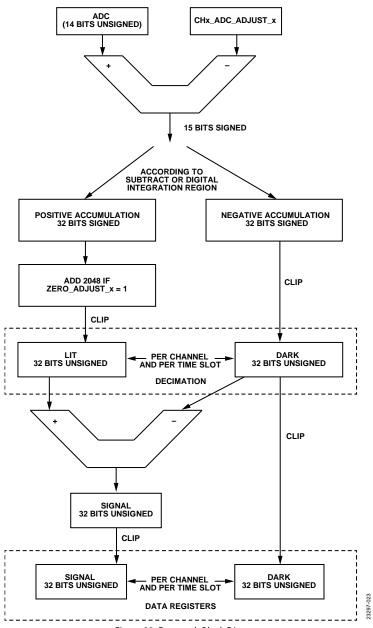

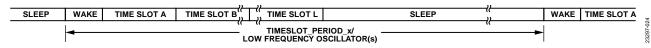

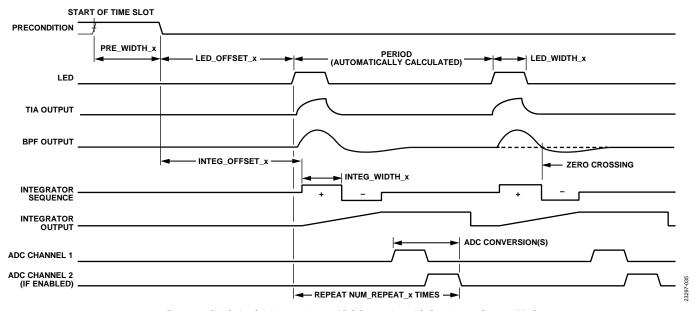

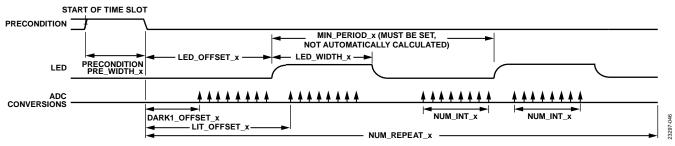

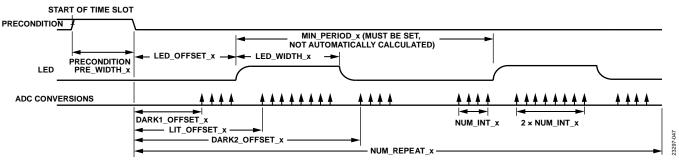

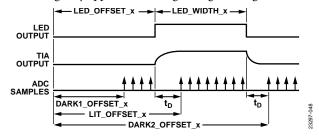

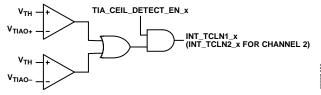

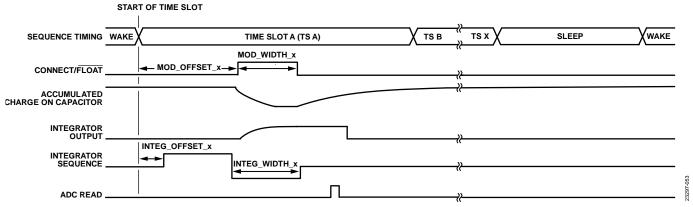

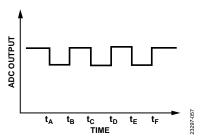

ADC samples are gathered for each pulse in each time slot and combine to create a running positive and negative sum for each time slot. These sums are each kept as a 32-bit unsigned value register and saturate if the values overflow 32 bits. Each ADC sample is added to either the positive or negative sum based on the SUBTRACT\_x bits for the current pulse in standard sampling mode, or in the lit or dark acquisition regions for digital integration mode. Figure 23 shows the datapath structure.

Figure 23. Datapath Block Diagram

At the end of the pulse operations in each time slot, the lit and dark values are clipped to positive numbers and are sent to the decimation unit. At the end of time slot operations, if the decimated value is ready, the signal value is calculated by subtracting the dark value from the lit value. Then, the data registers that are ready are updated, and the selected values are written to the FIFO. The data interrupt for that time slot is also set at this time for each updated time slot.

#### **Decimation**

The DECIMATE\_FACTOR\_x bits determine the number of time slot values used to create a 32-bit final sample value at a rate of

Sample Rate = (1/TIMESLOT\_PERIOD\_x)/(DECIMATE\_FACTOR\_x + 1)

If DECIMATE\_FACTOR\_x is 0, the output sample rate equals the time slot rate. The final value is the sum of the decimated samples. There is no divide by  $(DECIMATE\_FACTOR\_x + 1)$ operation performed on the decimated data, but final data values can be bit shifted to the right before being written to the FIFO, creating a direct average when the number of samples is a power of 2. DECIMATE\_TYPE\_x selects the method of decimation used. A setting of 0 selects a simple block sum with other settings allowing higher order CIC filters up to fourth order. If using higher order CIC filters for the signal data, the dark data still uses the simple block sum at the same decimation rate. Each time slot maintains its own block sum or CIC filter state. The entire decimation path uses a 32-bit datapath. When using the CIC filter, the number of bits required for the result is dependent on the number of pulses, the decimation rate and the order of the CIC filter according to the following equation:

$N_{BITS} = 14 + \log_2(Number \ of \ Pulses) + (\log_2(Decimation \ Rate))(CIC \ Order)$

It is up to the user to ensure that there is no undesired overflow. Final data results can be read from data registers or a 512-byte data FIFO. Data written to the FIFO is configurable to allow the different data registers, formats, and data sizes as required. Each time slot can use its own decimation rate. Data from each time slot is written to the FIFO at its respective ODR.

#### Subsampling

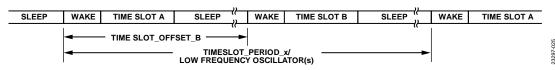

The ADPD4100/ADPD4101 support a subsampling mode that allows selected time slots to run at slower sampling rates than the programmed sampling rate. For example, in a multiparameter application where most of the measurements need to be taken at a sampling rate of 300 Hz but one of the measurements only needs to be taken at 25 Hz, the subsampling mode can be used on the time slot that only needs to operate at 25 Hz. To enable subsampling mode for a specific time slot, set the SUBSAMPLE\_x bit to 1 and set the DECIMATE\_FACTOR\_x bits to the desired subsampling rate. The subsampled time slot then samples only once every (DECIMATE\_FACTOR\_x + 1) cycles, instead of operating every time slot sequence. If other time slots are decimating at the same rate, the subsampled cycles occur at the same

time the decimated data is presented to the FIFO. For example, if Time Slot A is operating at 300 Hz but decimating to 25 Hz, and Time Slot B is set to subsample by 12, both time slots write the FIFO during the same time slot sequence and at the same rate.

More complicated patterns can be made if the decimate and subsample rates for the enabled time slots are different. The user must manage the varying packet sizes by reading the data in multiples of the repeating packet size. For example, if Time Slot A is not decimating or subsampling, Time Slot B is subsampling every second cycle, and Time Slot C is subsampling every fourth cycle, the data pattern written to the FIFO is A, AB, A, ABC, and so on, as the repeating packet.

Decimation and subsampling have the same effect on the output data rate. The only difference is that the decimated time slots operate every input cycle but produce data at the slower rate using the on-chip decimating filter. The subsampling time slots only occur at the slower rate.

Status bytes are written to the FIFO every wake-up period, regardless of which time slots execute. Using the same example as the different decimate and subsample rates scenario, but with a status byte enabled, the pattern is AS, ABS, AS, ABCS, and so on, where S is a status byte.

#### **FIFO**

Data is written to the FIFO at the end of each sampling period. This packet can include 0, 8-, 16-, 24-, or 32-bit data for each of the dark data, lit data, and signal data values. The bit alignment of the data written to the FIFO is selectable with a shift of 0 bits to 31 bits, with saturation provided. Lower bits are ignored. The DARK\_SHIFT\_x, LIT\_SHIFT\_x, and SIGNAL\_SHIFT\_x bits select the number of bits to shift the output data to the right before writing to the FIFO. The DARK\_SIZE\_x, LIT\_SIZE\_x, and SIGNAL\_SIZE\_x bits select the number of bytes of each field to be written from 0 bytes to 4 bytes. When set to 0, no data is written for that data type. If there are any nonzero bits at more significant bit positions than those selected, the data written to the FIFO is saturated. If both channels are enabled, all selected Channel 1 data values are written to the FIFO first, followed by the Channel 2 data.

For example, in modes that utilize dark data, the eight upper bits of the dark data can be stored with 24 appropriately selected bits from the signal data for each time slot to allow detection of whether the ambient light is becoming large, while limiting the size of the amount of data transferred.