## Auto-Reset Electronic Circuit Breaker

## FEATURES

- Programmable Trip Delay: 15µs to >100ms

- Programmable Trip Current: 1mA to >20A

- Programmbale Auto-Reset Time: 1ms to >10 sec.

- 4.5V to 18V Supply Range

- Drives Low R<sub>DS(ON)</sub> N-Channel MOSFETs

- Status Output Indicates Fault Condition

- Thermal Trip with PTC Thermistor

- 8µA I<sub>0</sub> in Standby Mode

- No External Charge Pump Capacitors

- Available in 8-Pin SOIC

# **APPLICATIONS**

- Power Bus Circuit Breaker

- SCSI Termination Power Protection

- Regulator Over-Current Protection

- Battery Short-Circuit Protection

- DC Motor Stall Protection

- Sensitive System Power Interrupt

# DESCRIPTION

The LTC1153 electronic circuit breaker drives a low cost N-channel MOSFET to interrupt power to a sensitive electronic load in the event of an over-current condition. The breaker remains tripped for a period of time set by an external timing capacitor and then is automatically reset. This cycle continues until the over-current condition is removed, protecting both the sensitive load and the MOSFET switch.

The trip current, trip delay time and auto-reset period are programmable over a wide range to accommodate a variety of load impedances. An active high shutdown input is also provided and interfaces directly to a PTC thermistor for thermal circuit breaking. An open-drain output is provided to report breaker status to the  $\mu$ P.

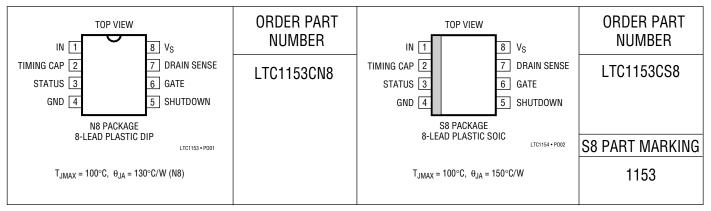

The LTC1153 is available in both 8-pin DIP and 8-pin SOIC packages.

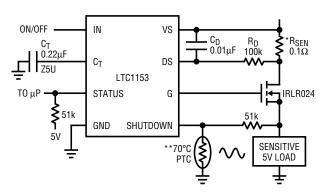

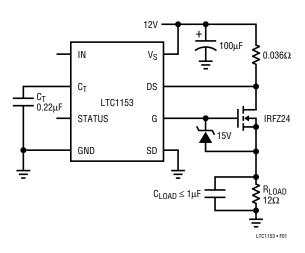

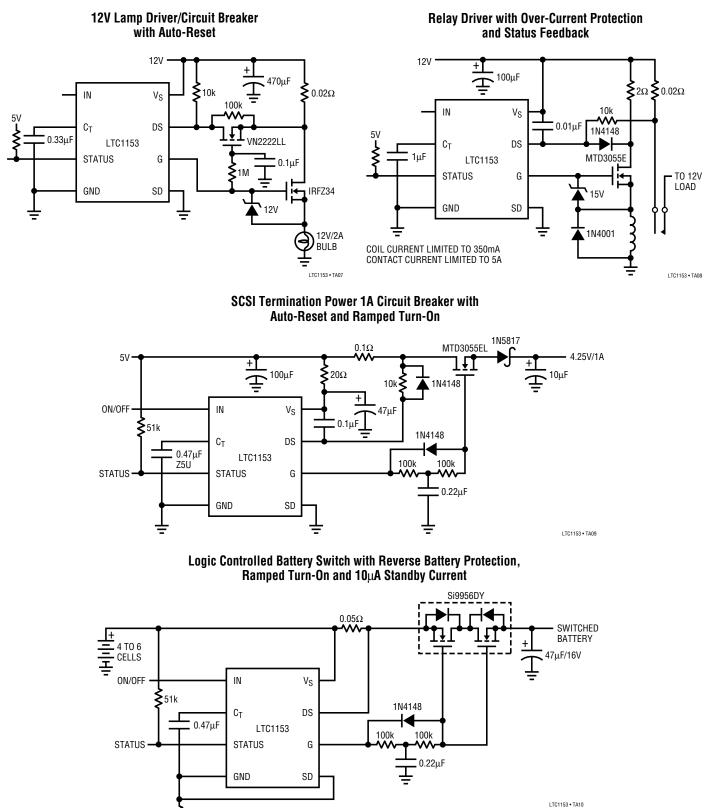

## TYPICAL APPLICATION

5V/1A Electronic Circuit Breaker with 1ms Trip Delay, 200ms Auto-Reset Period and 70°C Thermal Shutdown

ALL COMPONENTS SHOWN ARE SURFACE MOUNT.

\* IMS026 INTERNATIONAL MANUFACTURING SERVICE, INC. (401) 683-9700 \*\* RL2006-100-70-30-PT1 KEYSTONE CARBON COMPANY (814) 781-1591

LTC1153 • TA01

#### **Trip Delay Time**

## **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage                                           |

|----------------------------------------------------------|

| Input Voltage $(V_S + 0.3V)$ to $(GND - 0.3V)$           |

| Timing Capacitor Voltage $(VS + 0.3V)$ to $(GND - 0.3V)$ |

| Gate Voltage $(VS + 24V)$ to $(GND - 0.3V)$              |

| Status Output Voltage 15V                                |

| Current (Any Pin)                      | 50mA           |

|----------------------------------------|----------------|

| Operating Temperature                  |                |

| LTC1153C                               | 0°C to 70°C    |

| Storage Temperature Range              | -65°c to 150°C |

| Lead Temperature (Soldering, 10 sec.). | 300°C          |

## PACKAGE/ORDER INFORMATION

### **ELECTRICAL CHARACTERISTICS** $V_s = 4.5V$ to 18V, $T_A = 25^{\circ}C$ , $C_T = 0.1\mu F$ , $V_{SD} = 0V$ unless otherwise noted.

| SYMBOL           | PARAMETER                          | CONDITIONS                                  | MIN | UNITS      |            |            |          |

|------------------|------------------------------------|---------------------------------------------|-----|------------|------------|------------|----------|

| Vs               | Supply Voltage                     |                                             | •   | 4.5        |            | 18         | V        |

| la               | Quiescent Current OFF              | Vs = 5V, Vin = 0V                           |     |            | 8          | 20         | μA       |

| la               | Quiescent Current ON               | Vs = 5V, Vin = 5V                           |     |            | 85         | 120        | μA       |

| la               | Quiescent Current ON               | Vs =12V, VIN = 5V                           |     |            | 180        | 400        | μA       |

| VINH             | Input High Voltage                 |                                             | •   | 2          |            |            | V        |

| VINL             | Input Low Voltage                  |                                             | •   |            |            | 0.8        | V        |

| lin              | Input Current                      | 0v < Vin < Vs                               | •   |            |            | ±1         | μA       |

| CIN              | Input Capacitance                  |                                             |     |            | 5          |            | pF       |

| Vст              | Timing Capacitor Threshold Voltage | V <sub>S</sub> = 5V<br>V <sub>S</sub> = 12V |     | 2.1<br>2.0 | 2.5<br>2.6 | 2.9<br>3.2 | V<br>V   |

| Іст              | Timing Capacitor Current           | Vs = 12V                                    |     | 3.0        | 4.2        | 6.0        | μA       |

| VSDH             | Shutdown Input High Voltage        |                                             | •   | 2          |            |            | V        |

| V <sub>SDL</sub> | Shutdown Input Low Voltage         |                                             | •   |            |            | 0.8        | V        |

| I <sub>SD</sub>  | Shutdown Input Current             | $0V < V_{IN} < V_S$                         | •   |            |            | ±1         | μA       |

| VSEN             | Drain Sense Threshold Voltage      |                                             | •   | 80<br>75   | 100<br>100 | 120<br>125 | mV<br>mV |

| ISEN             | Drain Sense Input Current          | 0V < V <sub>SEN</sub> < V <sub>S</sub>      | •   |            |            | ±0.1       | μA       |

| SYMBOL                             | PARAMETER                     | CONDITIONS                                                                                                                                          |     | MIN       | LTC1153C<br>TYP | МАХ         | UNITS    |

|------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----------------|-------------|----------|

| V <sub>GATE</sub> – V <sub>S</sub> |                               | $V_{\rm S} = 5V$                                                                                                                                    | 6.0 | 7.0       | 9.0             | V           |          |

| UAIL 5                             |                               | $V_{\rm S} = 6V$                                                                                                                                    | •   | 7.5       | 8.3             | 15.0        | V        |

|                                    |                               | V <sub>S</sub> = 12V                                                                                                                                | •   | 15.0      | 18.0            | 25.0        | V        |

| V <sub>STAT</sub>                  | Status Output Low Voltage     | I <sub>STAT</sub> = 400μA                                                                                                                           | •   |           | 0.05            | 0.4         | V        |

| I <sub>STAT</sub>                  | Status Output Leakage Current | V <sub>STAT</sub> = 12V                                                                                                                             | •   |           |                 | 1           | μA       |

| t <sub>on</sub>                    | Turn-ON Time                  | $\label{eq:VS} \begin{array}{l} V_S = 5V, \ C_{GATE} = 1000 pF \\ Time \ for \ V_{GATE} > V_S + 2V \\ Time \ for \ V_{GATE} > V_S + 5V \end{array}$ |     | 30<br>100 | 110<br>450      | 300<br>1000 | μs<br>μs |

|                                    |                               | $\label{eq:VS} \begin{array}{l} V_S = 12V, \ C_{GATE} = 1000 pF\\ Time \ for \ V_{GATE} > V_S + 5V\\ Time \ for \ V_{GATE} > V_S + 10V \end{array}$ |     | 20<br>50  | 80<br>160       | 200<br>500  | μs<br>μs |

| t <sub>OFF</sub>                   | Turn-OFF Time                 | $V_S$ = 5V, $C_{GATE}$ = 1000pF<br>Time for $V_{GATE}$ < 1V                                                                                         |     | 10        | 36              | 60          | μs       |

|                                    |                               | $V_{S}$ = 12V, $C_{GATE}$ = 1000pF<br>Time for $V_{GATE}$ < 1V                                                                                      |     | 10        | 28              | 60          | μs       |

| t <sub>TD</sub>                    | Minimum Trip Delay            | $V_S$ = 5V, $C_{GATE}$ = 1000pF Time for $V_{GATE}$ < 1V                                                                                            |     | 5         | 25              | 40          | μs       |

|                                    |                               | $V_S$ = 12V, $C_{GATE}$ = 1000pF<br>Time for $V_{GATE}$ < 1V                                                                                        |     | 5         | 23              | 40          | μs       |

| t <sub>SD</sub>                    | Shutdown Turn-OFF Time        | $V_{S}$ = 5V, $C_{GATE}$ = 1000pF<br>Time for $V_{GATE}$ < 1V                                                                                       |     |           | 17              | 40          | μs       |

|                                    |                               | $V_{S}$ = 12V, $C_{GATE}$ = 1000pF<br>Time for $V_{GATE}$ < 1V                                                                                      |     |           | 13              | 35          | μs       |

The • denotes specifications which apply over the operating temperature range.

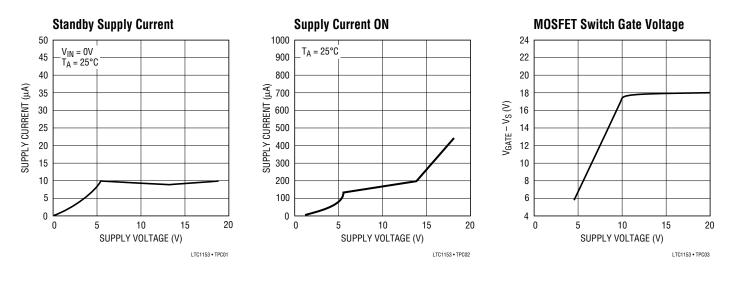

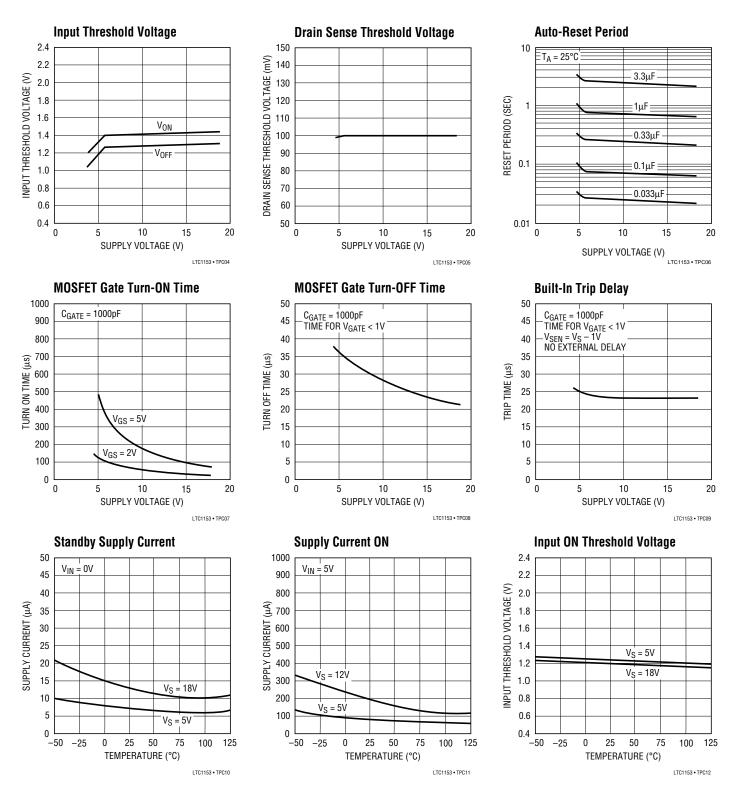

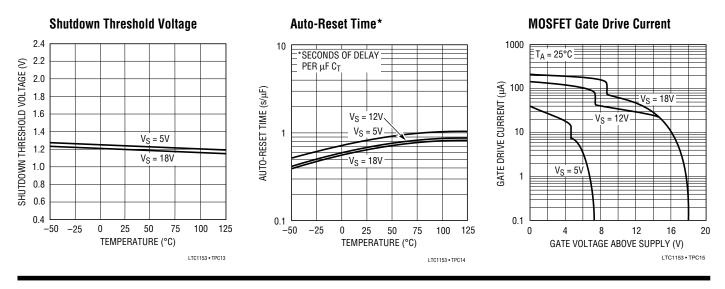

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

#### **Input and Shutdown Pins**

The LTC1153 input pin is active high and activates all of the protection and charge pump circuitry when switched ON. The shutdown pin is designed to break the circuit if a secondary fault condition (over temperature, etc.) is detected. The LTC1153 logic and shutdown inputs are high impedance CMOS gates with ESD protection diodes to ground and supply and therefore should not be forced beyond the power supply rails. The shutdown pin should be connected to ground when not in use.

### Timing Capacitor Pin (Auto-Reset Timer)

The small capacitor charging current  $(4.2\mu A)$  produces large delays with relatively small valued capacitors, but care must be taken to ensure that this current is not shunted to ground through a leaky capacitor or printed circuit board trace. The timing capacitor voltage is sensed by a high impedance CMOS comparator input with ESD clamp diodes to ground and supply and therefore should not be forced beyond the power supply rails. This pin can be grounded if the auto-reset function is not used.

### **MOSFET Gate Drive Pin**

The MOSFET gate drive pin is either driven to ground when the switch is turned OFF or driven above the supply rail when the switch is turned ON. This pin is a relatively high impedance when driven above the rail (the equivalent of a few hundred  $k\Omega$ ). Care should be taken to minimize any loading of this pin by parasitic resistance to ground or supply.

### **Supply Pin**

The supply pin of the LTC1153 serves two vital purposes. The first is obvious: it powers the input, gate drive, regulation and protection circuitry. The second purpose is less obvious: it provides a Kelvin connection to the top of the drain sense resistor for the internal 100mV reference.

The LTC1153 is designed to be *continuously powered* so that the gate of the MOSFET is actively driven at all times. If it is necessary to remove power from the supply pin and then re-apply it, the input pin (or enable pin) should be cycled a few milliseconds *after* the power is re-applied to reset the input latch and protection circuitry. Also, the input and enable pins should be isolated with 10k resistors to limit the current flowing through the ESD protection diodes to the supply pin.

The supply pin of the LTC1153 should never be forced below ground as this may result in permanent damage to the device. A  $300\Omega$  resistor should be inserted in series with the ground pin if negative supply voltage transients are anticipated.

### **PIN FUNCTIONS**

### Drain Sense Pin

The drain sense pin is compared against the supply pin voltage. If the voltage at this pin is more than 100mV below the supply pin, the input latch will trip and the MOSFET switch will be turned off.

This pin is also a high impedance CMOS gate with ESD protection and therefore should not be forced beyond the power supply rails.

Some loads, such as large supply capacitor, lamps, or motors require high inrush currents. An RC time is added between the sense resistor and the drain sense pin to ensure that the drain sense circuitry does not false trigger during start-up. This trip delay can be set from a few microseconds to many seconds. However, very long delays may put the MOSFET switch in risk of being destroyed by a short-circuit condition. (see Applications Information Section).

#### Status Pin

The status pin is an open-drain output which is driven low whenever the breaker is tripped. A 51k pull-up resistor should be connected between this output and a logic supply. The status pins of multiple LTC1153s can be OR'd together if independent fault sensing is not required. No connection is required to this pin when not in use.

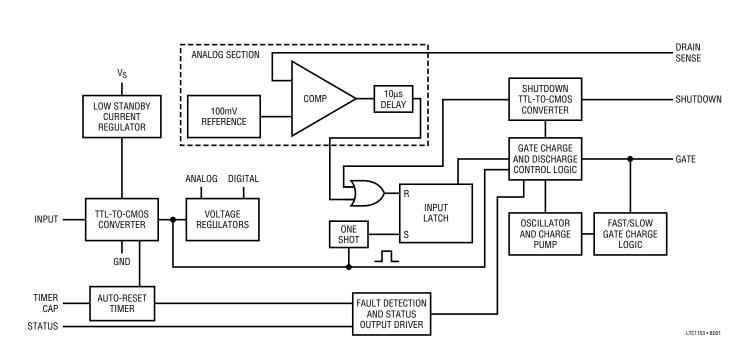

## **BLOCK DIAGRAM**

OFF

LTC1153 • TD01

#### 5V **OVER-CURRENT** NOR-SHUT-(AUTO-CURRENT) MAL DOWN INPUT I IN R<sub>SEN</sub> $V_{S}$ СР INPUT **<** 51k 0.01µF ·\*200µs Ст DS $\sim$ R<sub>D</sub>100k 0.1µF OUTPUT I TC1153 Z5U 3 IRLZ24 STATUS < STATUS G STATUS OUTPUT GND SD S1 TIMING CAP SHUTDOWN **ξ**1Ω \*90ms $10\Omega$ SHUT-DOWN LTC1153 • TC01 S1 CLOSED S1 OPEN \*TIMES FOR COMPONENTS SHOWN IN TEST CIRCUIT

## LTC1153 OPERATION

**TEST CIRCUIT**

The LTC1153 is an electronic circuit breaker with built-in MOSFET gate charge pump, over-current detection and auto-reset circuitry. The LTC1153 consists of the following functional blocks:

### TTL and CMOS Compatible Inputs

The LTC1153 input and shutdown input have been designed to accommodate a wide range of logic families. Both input thresholds are set at about 1.3V with approximately 100mV of hysteresis.

A low standby current voltage regulator provides continuous bias for the TTL-to-CMOS converter. The TTL-to-CMOS converter output enables the rest of the circuitry. In this way the power consumption is kept to a minimum in the standby mode.

### Auto-Reset Timer

An external timing capacitor,  $C_T$ , is ramped up by a small current whenever a fault is detected, i.e., the switch latched off. When the timing capacitor ramps up to approximately 2.5V, the switch is turned back on and the timing capacitor discharged. If the circuit breaker output is still in an overload state, the breaker will latch off and this cycle will continue until the fault condition is removed.

### Internal Voltage Regulation

The output of the TTL-to-CMOS converter drives two regulated supplies which power the low voltage CMOS logic and analog blocks. The regulator outputs are isolated from each other so that the noise generated by the charge pump logic is not coupled into the 100mV reference or the analog comparator.

### Gate Charge Pump

Gate drive for the MOSFET switch is produced by an adaptive charge pump circuit which generates a gate voltage substantially higher than the power supply voltage. The charge pump capacitors are included on-chip and therefore no external components are required to generate the gate drive.

### **Drain Current Sense**

The LTC1153 is configured to sense the current flowing into the drain of an N-channel MOSFET switch. An internal 100mV reference is compared to the drop across a sense resistor (typically  $0.002\Omega$  to  $0.10\Omega$ ) in series with the drain lead. If the drop across this resistor exceeds the internal 100mV threshold, the input latch is reset and the gate is quickly discharged via a relatively large N-channel transistor.

## TIMING DIAGRAM

# LTC1153 OPERATION

### **Controlled Gate Rise and Fall Times**

When the input is switched ON and OFF, the gate is charged by the internal charge pump and discharged in a controlled manner. The charge and discharge rates have been set to minimize RFI and EMI emissions in normal operation. If a short-circuit or current overload condition is encountered, the gate is discharged very quickly (typically a few microseconds) by a large N-channel transistor.

### APPLICATIONS INFORMATION

### **MOSFET and Load Protection**

The LTC1153 protects the power MOSFET switch by removing drive from the gate as soon as an over-current condition is detected and breaking the circuit to the load. Resistive and inductive loads can be protected with no external time delay in series with the drain sense pin. High inrush current loads, however, require that the trip delay time be set long enough to start the load but short enough to ensure the safety of the MOSFET.

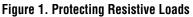

### **Resistive Loads**

Loads that are primarily resistive should be protected with as short a delay as possible to minimize the amount of time that the MOSFET switch or the load is subjected to an overload condition. The drain sense circuitry has a built-in trip delay of approximately 10 $\mu$ s to eliminate false triggering by power supply or load transient conditions. This delay is sufficient to "mask" short load current transients and the starting of a small capacitor (<1 $\mu$ F) in parallel with the load. The drain sense pin can therefore be connected directly to the drain current sense resistor as shown in Figure 1.

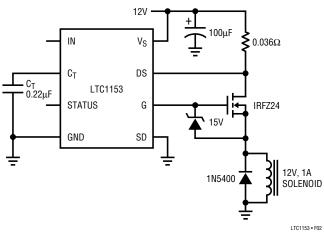

### Inductive Loads

Loads that are primarily inductive, such as relays, solenoids and stepper motor windings should be protected with as short a delay as possible to minimize the amount of time that the MOSFET is subjected to an overload condition. The built-in  $10\mu$ s trip delay will ensure that the breaker is not false-tripped by a supply or load transient. No external delay components are required as shown in Figure 2.

### **Status Output Driver**

The status circuitry continuously monitors the input and the gate charge control logic. The open-drain output is driven low when the input is turned ON and the breaker is latched off. The status circuitry is reset along with the input latch when the auto-reset circuitry retries the breaker or the input is cycled low.

Figure 2. Protecting Inductive Loads

Large inductive loads (>0.1mH) may require diodes connected directly across the inductor to safely divert the stored energy to ground. Many inductive loads have these diodes included. If not, a diode of the proper current rating

## APPLICATIONS INFORMATION

should be connected across the load, as shown in Figure 2, to safely divert the stored energy.

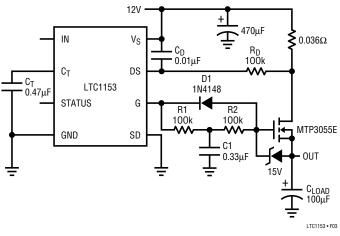

### **Capacitive Loads**

Large capacitive loads, such as complex electrical systems with large bypass capacitors, should be powered using the circuit shown in Figure 3. The gate drive to the power MOSFET switch is passed through an RC delay network, R1 and C1, which greatly reduces the turn on ramp rate of the switch. And since the MOSFET source voltage follows the gate voltage, the load is powered smoothly and slowly from ground. This dramatically reduces the start-up current flowing into the supply capacitor/s which, in turn, reduces supply transients and allows for slower activation of sensitive electrical loads. (Diode, D1, provides a direct path for the LTC1153 protection circuitry to quickly discharge the gate).

Figure 3. Powering Large Capacitive Loads

The RC network,  $R_D$  and  $C_D$ , in series with the drain sense input should be set to trip based on the expected characteristics of the load *after* start-up. With this circuit, it is possible to power a large capacitive load and still react quickly (10µs) to break the circuit if a short-circuit condition is encountered. The ramp rate at the output of the switch as it lifts off ground is approximately:

$dV/dt = (V_{GATE} - V_{TH})/(R1 \times C1)$

And therefore the current flowing into the capacitor during start-up is approximately:

$I_{START-UP} = C_{LOAD} \times dV/dt$

Using the values shown in Figure 3, the start-up current is less than 100mA and does not false-trip the breaker.

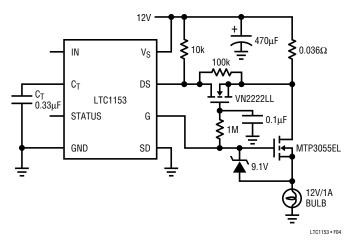

### Lamp Loads

The inrush current created by a lamp during turn-on can be 10 to 20 times greater than the rated operating current. The circuit shown in Figure 4 shifts the trip threshold up by a factor of 11:1 (to 30A) for 100ms while the bulb is turned on. The trip threshold then drops down to 2.7A after the inrush current has subsided.

Figure 4. Lamp Driver with Delayed Protection

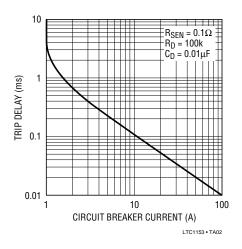

#### Selecting R<sub>D</sub> and C<sub>D</sub>

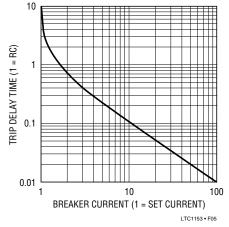

Figure 5 is a graph of normalized breaker trip time versus breaker current. This graph is used to select the two delay components,  $R_D$  and  $C_D$ , which make up a simple RC delay between the drain sense resistor and the drain sense input.

Figure 5. Trip Delay Time vs Breaker Current

# APPLICATIONS INFORMATION

The Y axis of the graph is normalized to one RC time constant. The X axis is normalized to the set current. (The set current is defined as the current required to develop 100mV across the drain sense resistor).

Note that the trip delay time is shorter for increasing levels of MOSFET current. This ensures that the total energy dissipated by the MOSFET is always within the bounds established by the manufacturer for safe operation. (See MOSFET data sheet for further S.O.A. information).

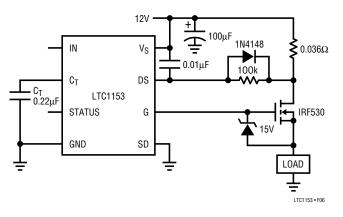

### Using a Speed-Up Diode

Another way to reduce the trip delay time is to "bypass" the delay resistor with a small signal diode as shown in Figure 6. The diode will engage when the drop across the drain sense resistor exceeds about 0.7V, providing a direct path to the sense pin and dramatically reducing the trip delay time. The drain sense resistor value is selected to limit the maximum DC breaker current to 4A.

Figure 6. Using a Speed-Up Diode

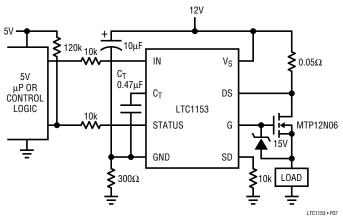

### **Reverse Battery Protection**

The LTC1153 can be protected against reverse battery conditions by connecting a resistor in series with the ground lead as shown in Figure 7. The resistor limits the supply current to less than 50mA with –12V applied. Since the LTC1153 draws very little current while in normal operation, the drop across the ground resistor is minimal. the 5V  $\mu$ P (or control logic) is protected by the 10k resistors in series with the input and status pins.

Figure 7. Reverse Battery Protection

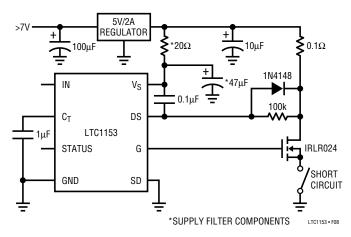

### **Current Limited Power Supplies**

The LTC1153 requires at least 3.5V at the supply pin to ensure proper operation. It is therefore necessary that the supply to the LTC1153 be held higher than 3.5V at all times, even when the output of the switch is short circuited to ground. The output voltage of a current limited regulator may drop very quickly during short-circuit and pull the supply pin of the LTC1153 below 3.5V before the shutdown circuitry has had time to respond and remove drive from the gate of the power MOSFET. A supply filter should be added as shown in Figure 8 which holds the supply pin of the LTC1153 high long enough for the over-current shutdown circuitry to respond and fully discharge the gate, i.e., break the circuit.

Figure 8. Supply Filter for Current Limited Supplies

## APPLICATIONS INFORMATION

Five volt linear regulators with small output capacitors are the most difficult to protect as they can "switch" from a voltage mode to a current limited mode very quickly. The large output capacitors on many switching regulators, on the other hand, may be able to hold the supply pin of the LTC1153 above 3.5V sufficiently long that this extra filtering is not required. Because the LTC1153 is micropower in both the standby and ON state, the voltage drop across the supply filter is less than 2mV, and does not significantly alter the accuracy of the 100mV drain sense threshold voltage.

## TYPICAL APPLICATIONS

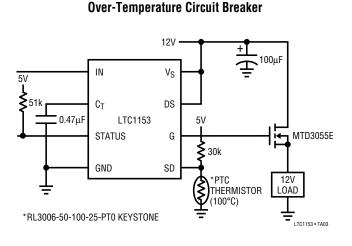

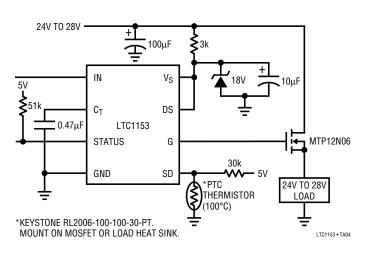

#### 24V to 28V Over-Temperature Circuit Breaker

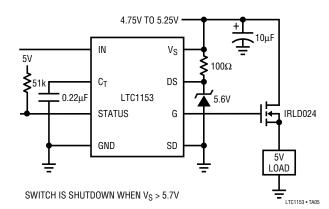

**Over-Voltage Circuit Breaker**

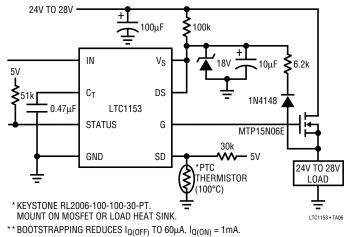

with Bootstrapped Supply

## TYPICAL APPLICATIONS

<u></u> <u>

</u>

300Ω

<u>

</u>

12

TECHNOLOGY

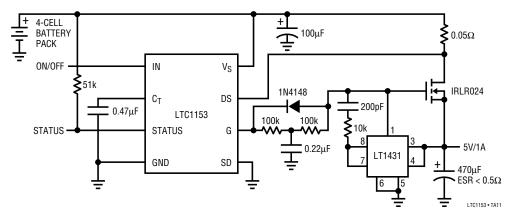

### TYPICAL APPLICATIONS

**LINEAR** TECHNOLOGY

"4 Cell-to-5V" Regulator with 2A Current Limit, Auto-Reset, Ramped Turn-On and 10μA Standby Current

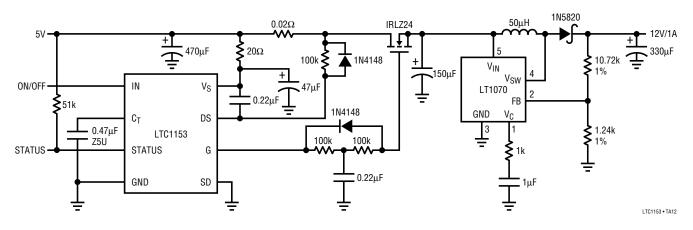

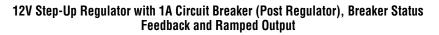

12V Step-Up Regulator with Soft Start, Auto-Reset Circuit Breaker (Pre-Regulator), Status Feedback and 10µA Standby Current

## TYPICAL APPLICATIONS

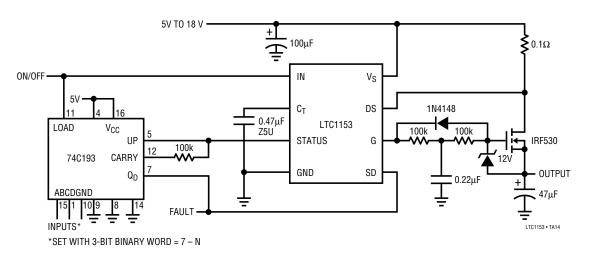

Auto-Reset Circuit Breaker with Programmable (1-6) Number of Retries Using Binary Counter

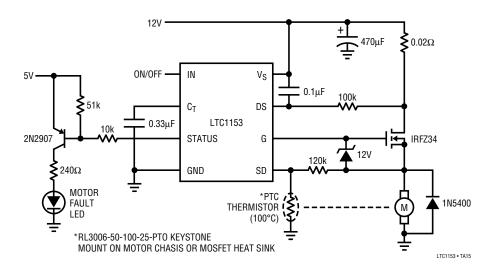

DC Motor Driver with Stall-Current Circuit Breaking (Auto-Reset), Thermal Overload Shutdown and  $10\mu A$  Standby Current

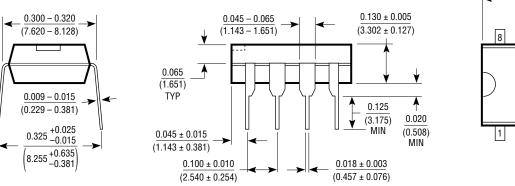

### PACKAGE DESCRIPTION

N8 Package 8-Lead Plastic Lead

N8 0392

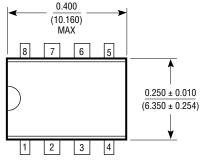

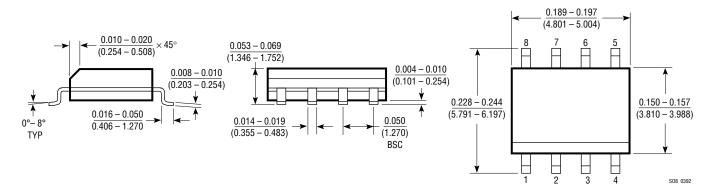

#### S8 Package 8-Lead Plastic SOIC

#### NORTHEAST REGION

#### Linear Technology Corporation One Oxford Valley

2300 E. Lincoln Hwy.,Suite 306 Langhorne, PA 19047 Phone: (215) 757-8578 FAX: (215) 757-5631

#### SOUTHEAST REGION

Linear Technology Corporation 17060 Dallas Parkway Suite 208 Dallas, TX 75248 Phone: (214) 733-3071 FAX: (214) 380-5138

#### **U.S. Area Sales Offices**

#### CENTRAL REGION

Linear Technology Corporation Chesapeake Square 229 Mitchell Court, Suite A-25 Addison, IL 60101 Phone: (708) 620-6910 FAX: (708) 620-6977

#### SOUTHWEST REGION

KOREA

Korea

Linear Technology Corporation 22141 Ventura Blvd. Suite 206 Woodland Hills, CA 91364 Phone: (818) 703-0835 FAX: (818) 703-0517

#### **International Sales Offices**

Linear Technology Korea Branch

Namsong Building, #505

Itaewon-Dong 260-199

Phone: 82-2-792-1617

Linear Technology Pte. Ltd.

#02-15 Kallang Ind. Estates

FAX: 82-2-792-1619

101 Boon Keng Road

Phone: 65-293-5322

FAX: 65-292-0398

SINGAPORE

Singapore 1233

Yongsan-Ku, Seoul

#### Linear Technology S.A.R.L. Immeuble "Le Quartz" 58 Chemin de la Justice 92290 Chatenay Mallabry France Phone: 33-1-46316161 FAX: 33-1-46314613

#### GERMANY

FRANCE

Linear Techonolgy GMBH Untere Hauptstr. 9 D-8057 Eching Germany Phone: 49-89-319741-0 FAX: 49-89-3194821

#### JAPAN

#### Linear Technology KK

5F YZ Building 4-4-12 lidabashi Chiyoda-Ku Tokyo, 102 Japan Phone: 81-3-3237-7891 FAX: 81-3-3237-8010

#### TAIWAN

Linear Technology Corporation Rm. 801, No. 46, Sec. 2 Chung Shan N. Rd. Taipei, Taiwan, R.O.C. Phone: 886-2-521-7575 FAX: 886-2-562-2285

NORTHWEST REGION

Phone: (408) 428-2050

FAX: (408) 432-6331

782 Sycamore Dr.

Milpitas, CA 95035

Linear Technology Corporation

#### UNITED KINGDOM

Linear Technology (UK) Ltd. The Coliseum, Riverside Way Camberley, Surrey GU15 3YL United Kingdom Phone: 44-276-677676 FAX: 44-276-64851

#### World Headquarters

Linear Technology Corporation 1630 McCarthy Blvd. Milpitas, CA 95035-7487 Phone: (408) 432-1900 FAX: (408) 434-0507

10/92

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

LTC1153CS8#PBF LTC1153IN8#PBF LTC1153IS8#TRPBF LTC1153IS8#PBF LTC1153CN8#PBF LTC1153CS8#TRPBF