LTC1472

# FEATURES

- Both V<sub>CC</sub> and VPP Switching in a Single Package

- Built-In Current Limit and Thermal Shutdown

- 16-Pin (Narrow) SOIC Package

- Inrush Current Limited (Drives 150µF Loads)

- Continuous 12V Power Not Required

- Extremely Low R<sub>DS(ON)</sub> NMOS Switches

- Guaranteed 1A V<sub>CC</sub> Current and 120mA VPP Current

- 1µA Quiescent Current in Standby

- No External Components Required

- Compatible with Industry Standard Controllers

- Break-Before-Make Switching

- Controlled Rise and Fall Times

# **APPLICATIONS**

- OpenCable Set Top Box

- Notebook Computers

- Palmtop Computers

- Pen-Based Computers

- Bar-Code Readers

# Protected PCMCIA V<sub>CC</sub> and VPP Switching Matrix

# DESCRIPTION

The LTC<sup>®</sup>1472 switching matrix routes power to both the V<sub>CC</sub> and VPP power supply pins of the PCMCIA compatible card socket. The V<sub>CC</sub> output of the LTC1472 is switched between three operating states: OFF, 3.3V, and 5V. The VPP output is switched between four operating states: OV, V<sub>CC</sub>, 12V, and Hi-Z. The output voltages are selected by two sets of digital inputs which are compatible with industry standard PC Card controllers (see Truth Tables).

The V<sub>CC</sub> output of the LTC1472 can supply up to 1A of current and the VPP output up to 120mA. Both switches have built-in SafeSlot<sup>TM</sup> current limiting and thermal shutdown to protect the card, socket and power supply against accidental short-circuit conditions.

The LTC1472 is designed to conserve power by automatically dropping to  $1\mu$ A standby current when the two outputs are switched OFF. A shutdown pin is provided which holds the external 12V regulator in standby mode except when required for VPP power.

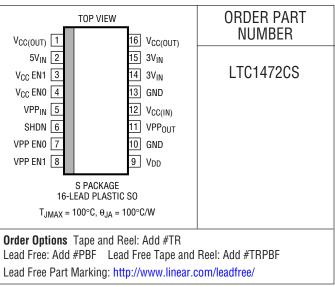

The LTC1472 is available in 16-pin SO package.

∠7, LTC and LT are registered trademarks of Linear Technology Corporation. SafeSlot is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

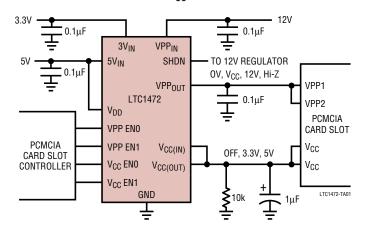

# TYPICAL APPLICATION

## Protected PCMCIA V<sub>CC</sub> and VPP Card Driver

### Linear Technology PCMCIA Product Family

| DEVICE               | DESCRIPTION                                          | PACKAGE     |  |  |

|----------------------|------------------------------------------------------|-------------|--|--|

| LT <sup>®</sup> 1312 | 2 Single PCMCIA VPP Driver/Regulator 8-Pin S         |             |  |  |

| LT1313               | Dual PCMCIA VPP Driver/Regulator                     | 16-Pin S0*  |  |  |

| LTC1314              | Single PCMCIA Switch Matrix                          | 14-Pin SO   |  |  |

| LTC1315              | Dual PCMCIA Switch Matrix                            | 24-Pin SSOP |  |  |

| LTC1470              | Protected V <sub>CC</sub> 5V/3.3V Switch Matrix      | 8-Pin SO    |  |  |

| LTC1471              | Dual Protected V <sub>CC</sub> 5V/3.3V Switch Matrix | 16-Pin S0*  |  |  |

| LTC1472              | Protected V <sub>CC</sub> and VPP Switch Matrix      | 16-Pin S0*  |  |  |

| *Narrow B            | ody                                                  |             |  |  |

T LINEAR TECHNOLOGY

# **ABSOLUTE MAXIMUM RATINGS**

| (Note | 1) |

|-------|----|

|-------|----|

| 5V <sub>IN</sub> Supply Voltage                                | 0.3V to 7V    |

|----------------------------------------------------------------|---------------|

| 3V <sub>IN</sub> Supply Voltage                                | 0.3V to 7V    |

| VPPIN Supply Voltage                                           | 0.3V to 13.2V |

| V <sub>CC(IN)</sub> Supply Voltage                             |               |

| V <sub>DD(IN)</sub> Supply Voltage                             | 0.3V to 7V    |

| V <sub>DD(IN)</sub> Supply Voltage<br>VPP <sub>OUT</sub> (OFF) | 0.3V to 13.2V |

| V <sub>CC(OUT)</sub> (OFF)                                     |               |

| Enable Inputs                                                  |               |

| VPP <sub>OUT</sub> Short-Circuit Duration                      |               |

| V <sub>CC(OUT)</sub> Short-Circuit Duration                    | Indefinite    |

| Operating Temperature Range                                    | 0°C to 70°C   |

| Junction Temperature                                           | 100°C         |

| Storage Temperature Range                                      |               |

| Lead Temperature (Soldering, 10 sec)                           |               |

|                                                                |               |

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> Switch Section) The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. 5V<sub>IN</sub> = 5V, 3V<sub>IN</sub> = 3.3V, VPP ENO = VPP EN1 = 0V, (Note 2) unless otherwise noted.

| SYMBOL             | PARAMETER                                            | CONDITIONS                                                                                                                       |   | MIN  | ТҮР                | MAX              | UNITS          |

|--------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---|------|--------------------|------------------|----------------|

| 5V <sub>IN</sub>   | 5V <sub>IN</sub> Supply Voltage Range                | (Note 3)                                                                                                                         |   | 4.75 |                    | 5.25             | V              |

| 3V <sub>IN</sub>   | 3V <sub>IN</sub> Supply Voltage Range                | (Note 4)                                                                                                                         |   | 0    |                    | 3.60             | V              |

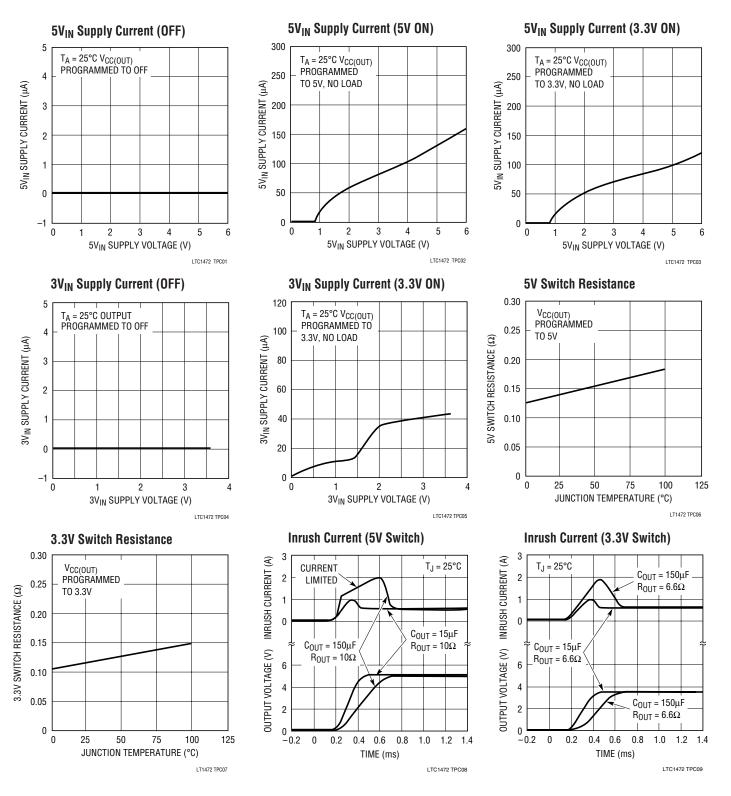

| I <sub>5VIN</sub>  | 5V <sub>IN</sub> Supply Current                      | Program to Hi-Z<br>Program to 5V, No Load<br>Program to 3.3V, No Load                                                            | • |      | 0.01<br>140<br>100 | 10<br>200<br>160 | μΑ<br>μΑ<br>μΑ |

| I <sub>3VIN</sub>  | 3V <sub>IN</sub> Supply Current                      | Program to Hi-Z.<br>Program to 5V, No Load<br>Program to 3.3V, No Load                                                           | • |      | 0.01<br>0.01<br>40 | 10<br>10<br>80   | μΑ<br>μΑ<br>μΑ |

| R <sub>ON</sub>    | 5V Switch On Resistance<br>3.3V Switch On Resistance | Program to 5V, I <sub>OUT</sub> = 500mA<br>Program to 3.3V, I <sub>OUT</sub> = 500mA                                             |   |      | 0.14<br>0.12       | 0.18<br>0.16     | Ω<br>Ω         |

| I <sub>LKG</sub>   | Output Leakage Current OFF                           | $V_{CC} \mbox{ EN0} = V_{CC} \mbox{ EN1} = 0 \mbox{ V or } 5 \mbox{ V},  0 \mbox{ V} \leq V_{CC(0 \mbox{ UT})} \leq 5 \mbox{ V}$ |   |      |                    | ±10              | μA             |

| I <sub>LIM5V</sub> | V <sub>CC(OUT)</sub> 5V Current Limit                | Program to 5V, $V_{CC(OUT)} = 0V$ (Note 5)                                                                                       |   |      | 1                  |                  | A              |

| I <sub>LIM3V</sub> | V <sub>CC(OUT)</sub> 3.3V Current Limit              | Program to 3.3V, V <sub>CC(OUT)</sub> = 0V (Note 5)                                                                              |   |      | 1                  |                  | A              |

| V <sub>CCENH</sub> | V <sub>CC</sub> Enable Input High Voltage            |                                                                                                                                  |   | 2    |                    |                  | V              |

| V <sub>CCENL</sub> | V <sub>CC</sub> Enable Input Low Voltage             |                                                                                                                                  |   |      |                    | 0.8              | V              |

| IVCCEN             | V <sub>CC</sub> Enable Input Current                 | $0V \le V_{CCEN} \le 5V$                                                                                                         |   |      |                    | ±1               | μA             |

| t <sub>VCC1</sub>  | Delay + Rise Time                                    | From 0V to 3.3V, $R_{LOAD} = 100\Omega$ , $C_{LOAD} = 1\mu F$ (Note 6)                                                           |   | 0.2  | 0.32               | 1                | ms             |

| t <sub>VCC2</sub>  | Delay + Rise Time                                    | From 3.3V to 5V, $R_{LOAD} = 100\Omega$ , $C_{LOAD} = 1\mu F$ (Note 6)                                                           |   | 0.2  | 0.52               | 1                | ms             |

| t <sub>VCC3</sub>  | Delay + Rise Time                                    | From 0V to 5V, $R_{LOAD} = 100\Omega$ , $C_{LOAD} = 1\mu F$ (Note 6)                                                             |   | 0.2  | 0.38               | 1                | ms             |

**ELECTRICAL CHARACTERISTICS** (VPP Switch Section) The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{DD} = 5V$ ,  $V_{CC(IN)} = 5V$ ,  $VPP_{IN} = 12V$ ,  $V_{CCENO} = V_{CCEN1} = 0V$ , (Note 2) unless otherwise noted.

| SYMBOL              | PARAMETER                                                                                                                | CONDITIONS                                                                                                                                                                                             |             | MIN | ТҮР                    | MAX                    | UNITS                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------------------------|------------------------|----------------------|

| V <sub>CC(IN)</sub> | V <sub>CC</sub> Input Voltage Range                                                                                      |                                                                                                                                                                                                        | •           | 3   |                        | 5.5                    | V                    |

| VPPIN               | VPP Input Voltage Range                                                                                                  | (Note 7)                                                                                                                                                                                               | •           | 0   |                        | 12.6                   | V                    |

| V <sub>DD</sub>     | Logic Supply Voltage Range                                                                                               | (Note 8)                                                                                                                                                                                               | •           | 4.5 |                        | 5.5                    | V                    |

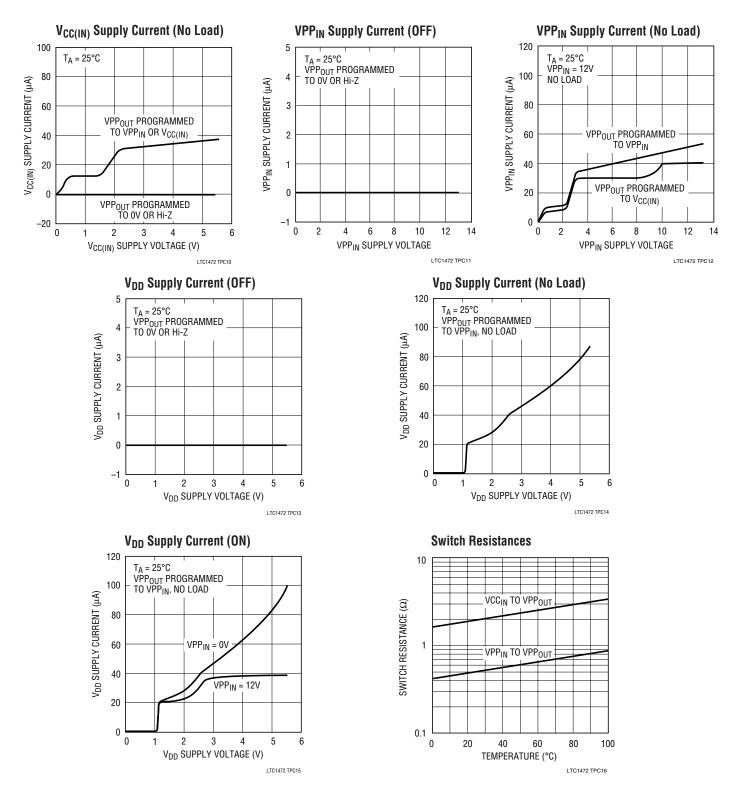

| I <sub>CCIN</sub>   | V <sub>CC(IN)</sub> Supply Current, No Load                                                                              | Program to $VPP_{IN}$ or $V_{CC(IN)}$ $VPP_{IN} = 12V$<br>Program to 0V or Hi-Z                                                                                                                        | •           |     | 35<br>0.01             | 60<br>10               | μA<br>μA             |

| I <sub>PPIN</sub>   | VPP <sub>IN</sub> Supply Current, No Load                                                                                | Program to VPP <sub>IN</sub> or V <sub>CC(IN)</sub><br>Program to 0V or Hi-Z                                                                                                                           | •           |     | 40<br>0.01             | 80<br>10               | μA<br>μA             |

| I <sub>DD</sub>     | V <sub>DD</sub> Supply Current, No Load                                                                                  | $\begin{array}{l} \mbox{Program to VPP}_{IN} \\ \mbox{Program to V}_{CC(IN)}, \mbox{VPP}_{IN} = 0V \\ \mbox{Program to V}_{CC(IN)}, \mbox{VPP}_{IN} = 12V \\ \mbox{Program to 0V or Hi-Z} \end{array}$ | •<br>•<br>• |     | 70<br>85<br>40<br>0.01 | 120<br>150<br>80<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| IVPPOUT             | Hi-Z Output Leakage Current                                                                                              | Program to Hi-Z, 0V < VPP <sub>OUT</sub> < 12V                                                                                                                                                         | •           |     | 0.01                   | 10                     | μA                   |

| R <sub>ON</sub>     | On Resistance $VPP_{OUT}$ to $VPP_{IN}$<br>On Resistance $VPP_{OUT}$ to $V_{CC(IN)}$<br>On Resistance $VPP_{OUT}$ to GND | $\begin{array}{l} VPP_{IN}=12V,\ I_{LOAD}=120mA\\ V_{CC(IN)}=5V,\ I_{LOAD}=5mA\\ V_{DD}=5V,\ I_{SINK}=1mA \end{array}$                                                                                 |             |     | 0.50<br>1.70<br>100    | 1<br>5<br>250          | Ω<br>Ω<br>Ω          |

| VPPENH              | VPP Enable Input High Voltage                                                                                            | V <sub>DD</sub> = 5V                                                                                                                                                                                   | •           | 2   |                        |                        | V                    |

| VPP <sub>ENL</sub>  | VPP Enable Input Low Voltage                                                                                             | V <sub>DD</sub> = 5V                                                                                                                                                                                   | •           |     |                        | 0.8                    | V                    |

| IVPPEN              | VPP Enable Input Current                                                                                                 | 0V < VPP EN < VDD                                                                                                                                                                                      | •           |     |                        | ±1                     | μA                   |

| V <sub>SDH</sub>    | SHDN Output High Voltage                                                                                                 | Program to 0V, $V_{CC(IN)}$ or Hi-Z, $I_{LOAD} = 400 \mu A$                                                                                                                                            | •           | 3.5 |                        |                        | V                    |

| V <sub>SDL</sub>    | SHDN Output Low Voltage                                                                                                  | Program to VPP <sub>IN</sub> , $I_{SINK} = 400 \mu A$                                                                                                                                                  | •           |     |                        | 0.4                    | V                    |

| LIMVCC              | VPP <sub>OUT</sub> Current Limit, V <sub>CC(IN)</sub>                                                                    | Program to $V_{CC(IN)}$ , $VPP_{OUT} = 0V$ (Note 5)                                                                                                                                                    |             |     | 60                     |                        | mA                   |

| ILIMVPP             | VPP <sub>OUT</sub> Current Limit, VPP <sub>IN</sub>                                                                      | Program to VPP <sub>IN</sub> , VPP <sub>OUT</sub> = 0V (Note 5)                                                                                                                                        |             |     | 100                    |                        | mA                   |

| t <sub>VPP1</sub>   | Delay and Rise Time                                                                                                      | From 0V to $V_{CC(IN)}$ , VPP <sub>IN</sub> = 0V (Note 9)                                                                                                                                              |             | 5   | 15                     | 50                     | μs                   |

| t <sub>VPP2</sub>   | Delay and Rise Time                                                                                                      | From 0V to VPP <sub>IN</sub> (Note 9)                                                                                                                                                                  |             | 25  | 85                     | 250                    | μs                   |

| t <sub>VPP3</sub>   | Delay and Rise Time                                                                                                      | From V <sub>CC(IN)</sub> to VPP <sub>IN</sub> (Note 9)                                                                                                                                                 |             | 30  | 100                    | 300                    | μs                   |

| t <sub>VPP4</sub>   | Delay and Fall Time                                                                                                      | From VPP <sub>IN</sub> to V <sub>CC(IN)</sub> (Note 10)                                                                                                                                                |             | 5   | 15                     | 50                     | μs                   |

| t <sub>VPP5</sub>   | Delay and Fall Time                                                                                                      | From VPP <sub>IN</sub> to 0V (Note 11)                                                                                                                                                                 |             | 10  | 35                     | 100                    | μs                   |

| t <sub>VPP6</sub>   | Delay and Fall Time                                                                                                      | From $V_{CC(IN)}$ to 0V, $VPP_{IN} = 0V$ (Note 11)                                                                                                                                                     |             | 10  | 30                     | 100                    | μs                   |

| t <sub>VPP7</sub>   | Output Turn-On Delay                                                                                                     | From Hi-Z to V <sub>CC(IN)</sub> (Note 9)                                                                                                                                                              |             | 5   | 15                     | 50                     | μs                   |

| t <sub>VPP8</sub>   | Output Turn-On Delay                                                                                                     | From Hi-Z to VPP <sub>IN</sub> (Note 9)                                                                                                                                                                |             | 25  | 85                     | 250                    | μs                   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2:  $V_{ENH} = 5V$ ,  $V_{ENL} = 0V$ . See  $V_{CC}$  and VPP Switch Truth Tables for programming enable inputs for desired output states.

**Note 3:** Power for the V<sub>CC</sub> input logic and charge pump circuitry is derived from the 5V<sub>IN</sub> power supply which must be continuously powered. 12V and 3.3V power is not required to control the NMOS V<sub>CC</sub> switches. (See Applications Information.)

Note 4: The two 3V<sub>IN</sub> supply input pins (14 and 15) must be connected together and the two  $V_{CC(OUT)}$  output pins (1 and 16) must be connected together. The 3V<sub>IN</sub> supply pins do not need to be continuously powered and may drop to OV when not required.

Note 5: The V<sub>CC</sub> and VPP output are protected with foldback current limit which reduces the short-circuit (OV) currents below peak permissible current levels at higher output voltages.

Note 6: To 90% of final value.

Note 7: 12V power is only required when VPP<sub>OUT</sub> is programmed to 12V. The external 12V regulator can be shutdown at all other times. Built-in charge pumps power the internal NMOS switches from the 5V V<sub>DD</sub> supply when 12V is not present.

Note 8: Power for the VPP input logic and charge pump circuitry is derived from the V<sub>DD</sub> power supply which must be continuously powered.

Note 9: To 90% of the final value,  $C_{OUT} = 0.1 \mu F$ ,  $R_{OUT} = 2.9 k$ .

Note 10: To 10% of the final value,  $C_{OUT} = 0.1 \mu F$ ,  $R_{OUT} = 2.9 k$ .

Note 11: To 50% of the initial value,  $C_{OUT} = 0.1 \mu F$ ,  $R_{OUT} = 2.9k$ .

# TYPICAL PERFORMANCE CHARACTERISTICS (V<sub>CC</sub> Section) VPP EN0 = VPP EN1 = 0V

# TYPICAL PERFORMANCE CHARACTERISTICS (VPP Section) V<sub>CC</sub> EN0 = V<sub>CC</sub> EN1 = 0V

# PIN FUNCTIONS

## Enable Input (Pins 3,4,7,8)

The two V<sub>CC</sub> and two VPP Enable inputs are designed to interface directly with industry standard PCMCIA controllers. They are high impedance CMOS gates with ESD protection diodes to ground, and should not be forced above  $5V_{IN}$  or below ground. Both sets of inputs have about 100mV of built-in hysteresis to ensure clean switching between operating modes.

## Shutdown Output (Pin 6)

The LTC1472 is designed to operate *without* continuous 12V power. The gates of the V<sub>CC</sub> NMOS switches are powered by charge pumps from the 5V<sub>IN</sub> supply, and the gates of the VPP NMOS switches are powered by charge pumps powered from the V<sub>DD</sub> supply when 12V is not present at the VPP<sub>IN</sub> pin (see Application Information for more details). Therefore, the external 12V regulator can be shut down most of the time, and only turned on when programming the socket VPP pin to 12V.

The shutdown output is active high; i.e. the system 12V regulator is shut down when this output is held high and turned on when this output is held low.

## VPP<sub>IN</sub> Supply (Pin 5)

The VPP<sub>IN</sub> supply pin serves two purposes. The first purpose is to provide power and gate drive for the VPP<sub>IN</sub>-VPP<sub>OUT</sub> switch. The second purpose is to provide optional 12V gate drive for the  $V_{CC(IN)}$ -VPP<sub>OUT</sub> switch. If, however, this 12V power is not available, gate drive is obtained automatically from the 5V V<sub>DD</sub> supply by an internal 5V to 12V charge pump converter.

## V<sub>DD</sub> Supply (Pin 9)

The V<sub>DD</sub> pin provides power for the input, charge pump and control circuitry for the VPP section of the LTC1472 and therefore must be continuously powered. The standby quiescent current is typically 0.1 $\mu$ A when the VPP<sub>OUT</sub> pin is programmed to 0V or Hi-Z and only rises to micropower levels when the VPP switches are active.

## V<sub>CC(IN)</sub> Supply (Pin 12)

The V<sub>CC(IN)</sub> supply pin is typically connected directly to the V<sub>CC(OUT)</sub> pin from the V<sub>CC</sub> switch section of the LTC1472. It can also be connected directly to a 3.3V or 5V power supply if desired. This supply pin does not provide any power to the internal control circuitry and is simply the input to the V<sub>CC(IN)</sub>-VPP<sub>OUT</sub> switch and therefore does not consume any power when unloaded or turned off.

## 5V<sub>IN</sub> Supply (Pin 2)

The 5V<sub>IN</sub> supply pin serves two purposes. The first purpose is as the power supply input for the 5V NMOS switch. The second purpose is to provide power for the input, gate drive and protection circuitry for both the 3.3V and 5V V<sub>CC</sub> switches, *this pin must be continuously powered*.

The enable inputs should be turned off (both asserted high or both asserted low) at least 100 $\mu$ s before the 5V<sub>IN</sub> power is removed to ensure that both V<sub>CC</sub> NMOS switch gates are fully discharged and both switches are in the high impedance mode.

## 3V<sub>IN</sub> Supply (Pins 14,15)

The  $3V_{IN}$  supply pin serves as the power supply input for the 3.3V switch. This pin does not provide any power to the internal control circuitry and therefore does not consume any power when unloaded or turned off.

## V<sub>CC(OUT)</sub> and VPP<sub>OUT</sub> Output (Pins 1,11,16)

The V<sub>CC</sub> output of the LTC1472 is switched between the three operating states: OFF, 3.3V, and 5V. The VPP output is switched between four operating states: 0, V<sub>CC</sub>, 12V and Hi-Z. Both pins are protected against accidental short-circuit conditions to ground by independent SafeSlot foldback current-limit circuitry which protects the socket, card and the system power supplies against damage. A second level of protection is provided by independent thermal shut down circuitry which protects each switch against overtemperature conditions.

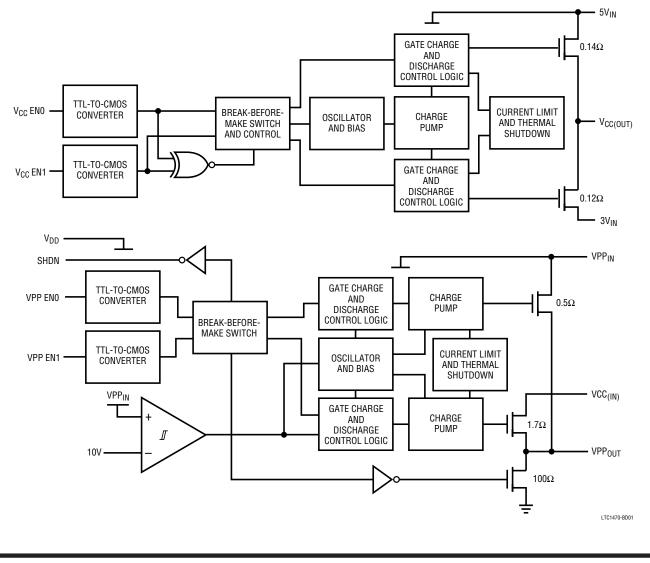

# **BLOCK DIAGRAM**

# OPERATION

The LTC1472 protected switch matrix is designed to be a complete single slot solution for V<sub>CC</sub> and VPP switching in a PCMCIA compatible card system. The LTC1472 consists of two independent functional sections: the V<sub>CC</sub> switching section, and the VPP switching section.

## THE V<sub>CC</sub> SWITCHING SECTION

The  $V_{CC}$  switching section of the LTC1472 consist of the following functional blocks:

## V<sub>CC</sub> Switch Input TTL-CMOS Converters

The LTC1472 V<sub>CC</sub> inputs are designed to accommodate a wide range of 3V and 5V logic families. The input threshold voltage is approximately 1.4V with approximately 100mV of hysteresis. The inputs enable the bias generator, the gate charge pumps and the protection circuity which are powered from the  $5V_{IN}$  supply. Therefore, when the inputs are turned off, the entire circuit is powered down and the  $5V_{IN}$  supply current drops below 1µA.

# OPERATION

## V<sub>CC</sub> XOR Input Circuitry

The LTC1472 ensures that the 3.3V and 5V switches are never turned on at the same time by employing an XOR function which locks out the 3.3V switch when the 5V switch is turned on, and locks out the 5V switch when the 3.3V switch is turned on. This XOR function also makes it possible for the LTC1472 to work with either active-low or active-high PCMCIA V<sub>CC</sub> switch control logic (see Applications Information for further details).

## V<sub>CC</sub> Break-Before-Make Switch Control

The LTC1472 has built-in delays to ensure that the 3.3V and 5V switch are non-overlapping. Further, the gate charge pumps include circuity which ramps the NMOS switches on slowly (400 $\mu$ s typical rise time) but turn off much more quickly (typically 10 $\mu$ s).

## $V_{CC}$ Bias, Oscillator and Gate Charge Pump

When either the 3.3V or 5V switch is enabled, a bias current generator and high frequency oscillator are turned on. An on-chip capacitive charge pump generates approximately 12V of gate drive for the internal low  $R_{DS(ON)}$  NMOS  $V_{CC}$  switches from the 5V<sub>IN</sub> power supply. Therefore, an external 12V supply is not required to switch the  $V_{CC}$  output. The 5V<sub>IN</sub> supply current drops below 1µA when both switches are turned off.

## V<sub>CC</sub> Gate Charge and Discharge Control

Both  $V_{CC}$  switches are designed to ramp on slowly (400 $\mu$ s typical rise time). Turn off time is much quicker (typically 10 $\mu$ s).

To ensure that both  $V_{CC}$  NMOS switch gates are fully discharged, program the switch to the high impedance mode at least 100  $\mu s$  before turning off the  $5V_{IN}$  power supply.

## V<sub>CC</sub> Switch Protection

Two levels of protection are designed into each of the power switches in the LTC1472. Both  $V_{CC}$  switches are protected against accidental short circuits with SafeSlot fold-back current limit circuits which limit the output current to typically 1A when the  $V_{CC(OUT)}$  output is shorted

to ground. Both switches also have independent thermal shutdown which limits the power dissipation to safe levels.

| V <sub>CC</sub> ENO | V <sub>CC</sub> EN1 | V <sub>CC(OUT)</sub> |

|---------------------|---------------------|----------------------|

| 0                   | 0                   | OFF                  |

| 1                   | 0                   | 5V                   |

| 0                   | 1                   | 3.3V                 |

| 1                   | 1                   | OFF                  |

## $V_{\mbox{CC}}$ Switch Truth Table

## THE VPP SWITCHING SECTION

The VPP switching section of the LTC1472 consists of the following functional blocks:

## **VPP Switch Input TTL-CMOS Converters**

The VPP inputs are designed to accommodate a wide range of 3V and 5V logic families. The input threshold voltage is 1.4V with  $\approx$  100mV of hysteresis. The inputs enable the bias generator, the gate charge pumps and the protection circuitry. When the inputs are turned off, the entire circuit is powered down and the V\_{DD} and VPP\_{IN} supply currents drop below 1\muA.

## VPP Break-Before-Make Switch Control

The VPP input section has built-in delays to ensure that the VPP switchs are non-overlapping. Further, the gate charge pumps include circuitry which ramps the NMOS switches on slowly but turns them off quickly.

## VPP Bias, Oscillator and Gate Charge Pump

When either the VPP<sub>IN</sub>-VPP<sub>OUT</sub> or V<sub>CC(IN)</sub>-VPP<sub>OUT</sub> switch is enabled, a bias current generator and high frequency oscillator are turned on. An on-chip capacitive charge pump generates approximately 23V of gate drive for the internal low R<sub>DS(ON)</sub> NMOS VPP<sub>IN</sub>-VPP<sub>OUT</sub> switch from the VPP<sub>IN</sub> power supply. The gate of the V<sub>CC(IN)</sub>-VPP<sub>OUT</sub> NMOS switch is either powered by the external 12V regulator (if left on) or automatically from a built-in charge pump powered from the V<sub>DD</sub> supply when the external 12V supply drops below 10V. The V<sub>DD</sub> supply current drops below 1µA when switched to either the 0V or Hi-Z mode.

# OPERATION

## VPP Gate Charge and Discharge Control

The VPP switches are designed to ramp slowly (typically tens of  $\mu$ s) between output modes to reduce supply glitching when powering large capacitive loads.

## **VPP Switch Protection**

Both VPP power switches are protected against accidental short circuits with SafeSlot fold-back current limit circuits which limit the short-circuit (0V) output current to typi-

# cally 100mA when protecting the 12V VPP<sub>IN</sub> supply and 60mA when protecting the V<sub>CC(IN)</sub> supply. (Higher operating currents are allowed at higher output voltages). Both switches also have thermal shutdown.

**VPP Switch Truth Table**

| VPP EN1 | VPPOUT                      |  |

|---------|-----------------------------|--|

| 0       | 0V                          |  |

| 1       | V <sub>CC(IN)</sub>         |  |

| 0       | VPPIN                       |  |

| 1       | Hi-Z                        |  |

|         | VPP EN1<br>0<br>1<br>0<br>1 |  |

# APPLICATIONS INFORMATION

The LTC1472 is a complete single slot  $V_{CC}$  and VPP power supply switch matrix with SafeSlot current limit protection on both outputs. It is designed to interface directly with industry standard PCMCIA card controllers and to industry standard 12V regulators.

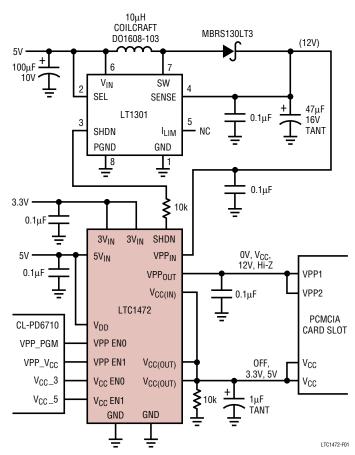

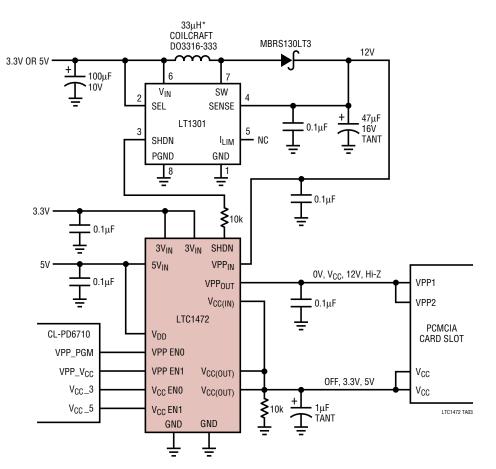

## Interfacing to the CL-PD6710 and the LT®1301

Figure 1 shows the LTC1472 interfaced to a standard PCMCIA slot controller and an LT1301 step-up switching regulator. The LTC1472 accepts logic control directly from the CL-PD6710 and in turn, controls the LT1301 to provide clean 12V VPP programming power when required. The LT1301 is then shutdown ( $10\mu$ A standby current) at all other times to conserve power.

The XOR V<sub>CC</sub> input function allows the LTC1472 to interface directly to the active-low V<sub>CC</sub> control outputs of the CL-PD6710 for 3.3V/5V voltage selection (see the V<sub>CC</sub> Switch Truth Table). Therefore, no "glue" logic is required to interface to this PCMCIA compatible controller.

The LTC1472 provides SafeSlot current-limit protection for the LT1301 step-up regulator, the system 3.3V and 5V regulators, the socket and the card. Further, depending upon the system regulator's own current limits, it may allow the system power supplies to continue operation during a card/slot short circuit without losing data, etc.

Figure 1. Direct Interface to Industry Standard PCMCIA Controller and LT1301 Step-Up Switching Regulator

# **APPLICATIONS INFORMATION**

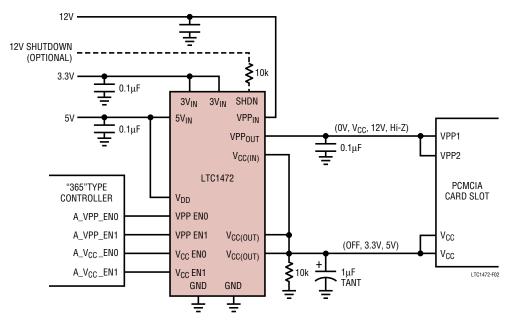

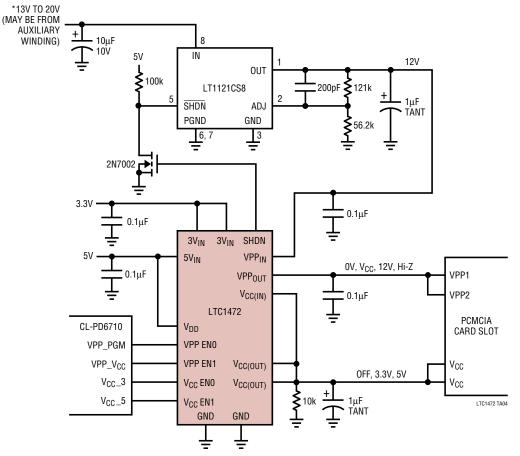

## Interfacing to "365" Type Controllers

The LTC1472 also interfaces directly with "365" type controllers as shown in Figure 2. The V<sub>CC</sub> Enable inputs are connected differently than to the CL-PD6710 controller because the "365" type controllers use active-high logic control of the V<sub>CC</sub> switches (see the V<sub>CC</sub> Switch Truth Table). No "glue logic" is required to interface to this type of PCMCIA compatible controller.

## **12V Power Requirements**

Note that in Figure 2, a "local" 5V to 12V converter is not used. The LTC1472 works equally well with or without continuous 12V power. If the main power supply system has 12V continuously available, simply connect it to the VPP<sub>IN</sub> pin. Internal circuitry automatically senses its presence and uses it to switch the internal VPP switches.

The 12V shutdown output can be used to shut down the system 12V power supply (if not required for any purpose other than VPP programming).

## **5V Power Requirements**

The LTC1472 has been designed to operate without continuous 12V power, but continuous 5V power is required at the  $V_{DD}$  and  $5V_{IN}$  supply pins for proper operation and should always be present when a card is powered (whether it is a 5V or 3.3V only card).

If the 5V power must be turned off, for example, to enter a 3.3V only full system "sleep" mode, the 5V supply must be turned off at least 100 $\mu$ s after the V<sub>CC</sub> and VPP switches have been programmed to the Hi-Z or 0V states. This ensures that the gates of the NMOS switches are completely discharged.

Also, the  $V_{CC}$  switches cannot be operated properly without 5V power. They must be programmed to the off state at least 100 $\mu$ s prior to turning the 5V supply off, or they may be left in an indeterminate state.

## **Supply Bypassing**

For best results, bypass the supply input pins with  $1\mu$ F capacitors as close as possible to the LTC1472. Sometimes, much larger capacitors are already available at the outputs of the 3.3V, 5V and 12V power supply. In this case, it is still good practice to use  $0.1\mu$ F capacitors as close as possible to the LTC1472, especially if the power supply output capacitors are more than 2" away on the printed circuit board.

Figure 2. Direct Interface to Industry Standard PCMCIA Controller and LT1301 Step-Up Switching Regulator

# **APPLICATIONS INFORMATION**

## **Output Capacitors**

The  $V_{CC(OUT)}$  pin is designed to ramp on slowly, typically 400 $\mu s$  rise time. Therefore, capacitors as large as 150 $\mu F$  can be driven without producing voltage spikes on the 5V\_{IN} or 3V\_{IN} supply pins (see graphs in Typical Performance Characteristics). The V<sub>CC(OUT)</sub> pin should have a 0.1 $\mu F$  to 1 $\mu F$  capacitor for noise reduction and smoothing.

The VPP<sub>OUT</sub> pin should have a 0.01 $\mu$ F to 0.1 $\mu$ F capacitor for noise reduction. The VPP<sub>IN</sub> capacitors should be at least equal to the VPP<sub>OUT</sub> capacitors to ensure smooth transitions between output voltages without creating spikes on the system power supply lines.

## **Supply Sequencing**

Because the 5V supply is the source of power for both the  $V_{CC}$  and VPP switch control logic, it is best to sequence the power supplies such that the 5V supply is powered before or simultaneous to the application of 3.3V or 12V power.

It is interesting to note however, that all of the switches in the LTC1472 are NMOS transistors which require charge pumps to generate gate voltages higher than the supply rails for full enhancement. Because the gate voltages start a OV when the supplies are first activated, the switches always start in the off state and do not produce glitches at the output when powered.

Some PCMCIA switch matrix products employ PMOS switches for 12V VPP control and great care must be taken to ensure that the 5V control logic is powered before the 12V supply is turned on. If this sequence is not followed, the PMOS VPP switch gate may start at ground potential and the VPP output may be inadvertently forced to 12V.

Although, not advisable, it is possible to power the 12V VPP<sub>IN</sub> supply pin of the LTC1472 prior to application of 5V power. Only about  $50\mu A$  flows to the VPP<sub>OUT</sub> pin under these conditions.

If the 5V supply must be turned off, it is important to program all switches to the Hi-Z or 0V state at least  $100\mu$ s before the 5V power is removed to ensure that all NMOS switch gates are fully discharged to 0V.

Whenever possible however, it is best to leave the  $5V_{IN}$  and  $V_{DD}$  pins continuously powered. The LTC1472 quiescent current drops to < 1µA with all the switches turned off and therefore no 5V power is consumed in the standby mode.

1472f

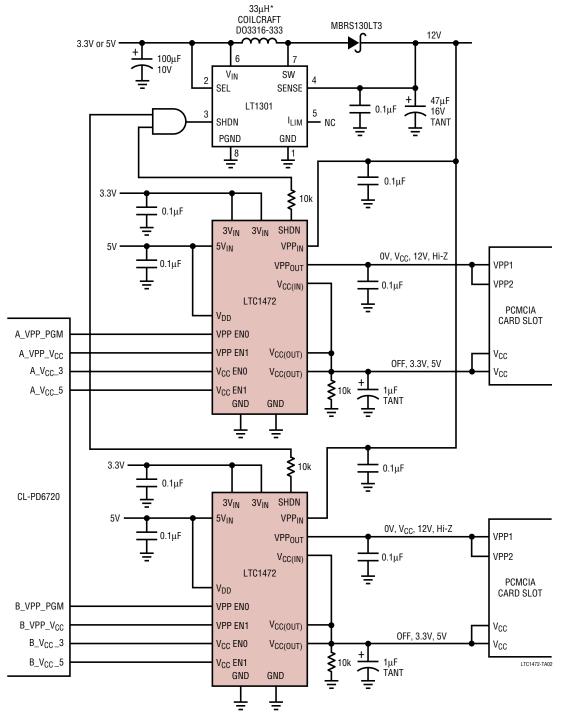

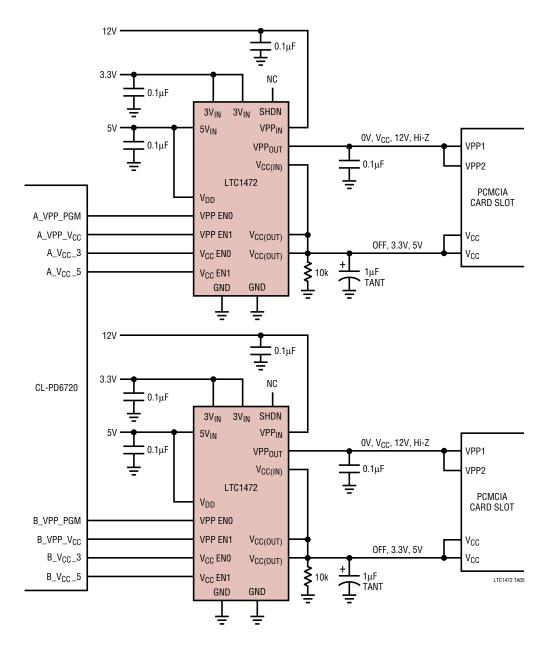

**Dual Protected PCMCIA Power Management System**

\*FOR 5V TO 12V CONVERSION USE  $10\mu H,$  COILCRAFT D01608-103. SEE LT1301 DATA SHEET FOR MORE DETAILED INFORMATION ON INDUCTOR AND CAPACITOR SELECTION.

Single Protected PCMCIA Power Management System Using the LT1301 Powered from 3.3V or 5V

\*FOR 5V TO 12V CONVERSION USE  $10\mu H,$  COILCRAFT D01608-103. SEE LT1301 DATA SHEET FOR MORE DETAILED INFORMATION ON INDUCTION AND CAPACITOR SELECTION.

Single Protected PCMCIA Power Management System Using the LT1121 Powered from an Auxiliary Winding for 12V VPP Power

\*SEE THE LTC1142 DATA SHEET FOR AN EXAMPLE OF A 3.3V/5V DUAL REGULATOR WITH AUXILIARY WINDING 15V OUTPUT

Dual Protected PCMCIA Power Management System Powered by System 12V Supply

15

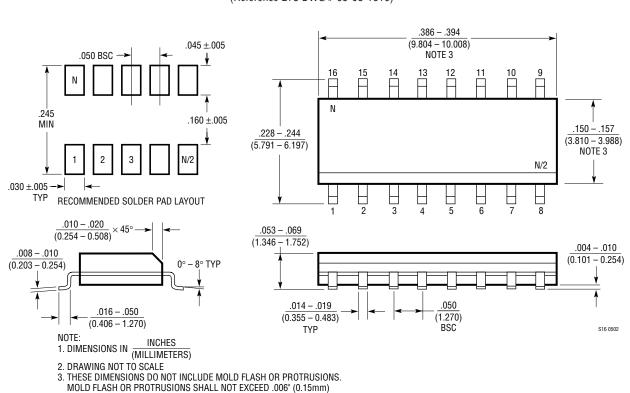

# PACKAGE DESCRIPTION

## S Package 16-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

# **RELATED PARTS**

| PART NUMBER                                      | DESCRIPTION                                                                                                   | COMMENTS                                                                                                                                       |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3405/LTC3405A<br>LTC3405A-1.5<br>LTC3405A-1.8 | 300mA (I <sub>OUT</sub> ), 1.5MHz, Synchronous Step-Down<br>DC/DC Converters                                  | 95% Efficiency, $V_{IN}$ = 2.7V to 6V, $V_{OUT}$ = 0.8V, $I_Q$ = 20µA $I_{SD}$ = <1µA, ThinSOT Package                                         |

| LTC3406/LTC3406B                                 | 600mA (I <sub>OUT</sub> ) 1.5MHz, Synchronous Step-Down<br>DC/DC Converter                                    | 95% Efficiency, $V_{IN}$ = 2.5V to 5.5V, $V_{OUT}$ = 0.6V, $I_Q$ = 20µA $I_{SD}$ = <1µA, ThinSOT Package                                       |

| LTC3411                                          | 1.25A (I <sub>OUT</sub> ), 4MHz, Synchronous Step-Down<br>DC/DC Converter                                     | 95% Efficiency, $V_{IN}$ = 2.5V to 5.5V, $V_{OUT}$ = 0.8V, $I_Q$ = 60µA $I_{SD}$ = <1µA, MS10 Package                                          |

| LTC3412                                          | 2.5A (I <sub>OUT</sub> ), 4MHz, Synchronous Step-Down<br>DC/DC Converter                                      | 95% Efficiency, $V_{IN}$ = 2.5V to 5.5V, $V_{OUT}$ = 0.8V, $I_Q$ = 60µA $I_{SD}$ = <1µA, TSSOP16E Package                                      |

| LTC3413                                          | 3A (I <sub>OUT</sub> ), Sink/Source, 2MHz, Monolithic Synchronous<br>Regulator for DDR/QDR Memory Termination | 90% Efficiency, $V_{IN}$ = 2.25V to 5.5V, $V_{OUT}$ = $V_{REF/2},$ $I_Q$ = 280µA $I_{SD}$ = <1µA, TSSOP16E Package                             |

| LT3430                                           | 60V, 2.75A (I <sub>OUT</sub> ), 200kHz, High Efficiency Step-Down DC/DC Converter                             | 90% Efficiency, V <sub>IN</sub> = 5.5V to 60V, V <sub>OUT</sub> = 1.20V, I <sub>Q</sub> = 2.5mA I <sub>SD</sub> = 25 $\mu$ A, TSSOP16E Package |

| LTC3440                                          | 600mA (I <sub>OUT</sub> ), 2MHz, Synchronous Buck-Boost<br>DC/DC Converter                                    | 95% Efficiency, $V_{IN}$ = 2.5V to 5.5V, $V_{OUT}$ = 2.5V, $I_Q$ = 25µA $I_{SD}$ = <1µA, MS Package                                            |

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: <u>LTC1472CS#PBF</u> LTC1472CS#TRPBF