### **General Description**

The MAX4991-MAX4994 low on-resistance analog switches operate from a single +1.8V to +5.5V supply. The MAX4991/MAX4993 feature a slow turn-on time to reduce clicks and pops due to coupling capacitors and audio amplifiers with a DC output bias. This feature provides click-and-pop reduction without adding additional parts for existing architectures.

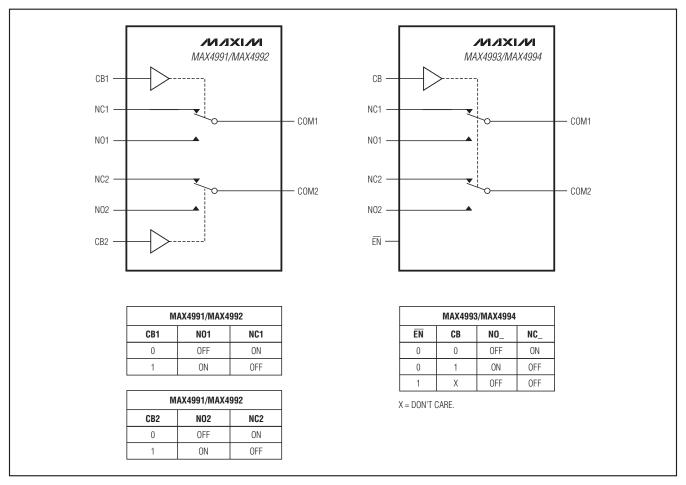

The MAX4991/MAX4992 are dual single-pole/doublethrow (SPDT) switches, while the MAX4993/MAX4994 are double-pole/double-throw (DPDT) switches. The MAX4993/MAX4994 feature an active-low enable input (EN) that sets all the channels to high impedance and reduces supply current when driven high. These devices have  $0.3\Omega$  on-resistance and 0.004% THD+N to route high fidelity audio signals.

The MAX4991-MAX4994 are available in space-saving 10-pin UTQFN (1.4mm x 1.8mm) package, and are specified for operation over the -40°C to +85°C extended temperature range.

#### **Applications**

Speaker Headset Source Switching Cellular Phones Portable MP3 Players Audio Signal Routing

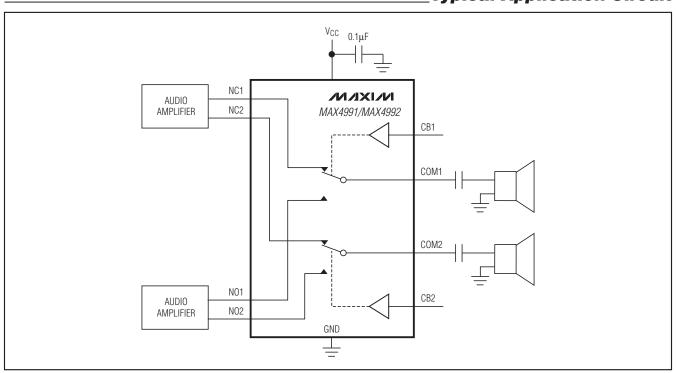

Typical Application Circuit appears at end of data sheet.

#### **Features**

- Slow Turn-On for Click-and-Pop Reduction Without **Additional Parts**

- ♦ Low 0.3Ω On-Resistance

- ♦ Low Ron Flatness (1mΩ)

- ♦ Low THD+N: 0.004%

- ♦ +1.8V to +5.5V Single-Supply Operation

- ♦ 1.2µA (typ) Supply Current

- ♦ Space-Saving Packages 10-Pin UTQFN (1.4mm x 1.8mm x 0.55mm)

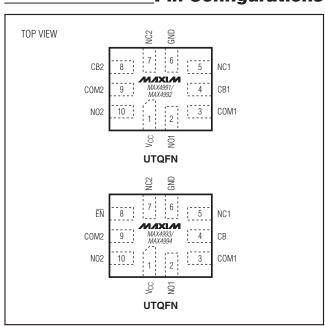

### Pin Configurations

## **Ordering Information/Selector Guide**

| PART         | PIN-PACKAGE | CONFIGURATION SLOW-SWITCHING TIME ENABLE LINE |     | TOP<br>MARK |     |

|--------------|-------------|-----------------------------------------------|-----|-------------|-----|

| MAX4991EVB+* | 10 UTQFN    | Dual SPDT                                     | Yes | No          | AAD |

| MAX4992EVB+  | 10 UTQFN    | Dual SPDT                                     | No  | No          | AAE |

| MAX4993EVB+  | 10 UTQFN    | DPDT                                          | Yes | Yes         | AAF |

| MAX4994EVB+* | 10 UTQFN    | DPDT                                          | No  | Yes         | AAG |

**Note:** All devices operate over -40°C to +85°C extended temperature range.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>Future product—contact factory for availability.

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)                         |            |

|-------------------------------------------------------|------------|

| V <sub>CC</sub> , CB_, <del>EN</del> 0.3\             | √ to +6.0V |

| COM_, NC_, NO0.3V to (V <sub>C</sub>                  | 2C + 0.3V  |

| Continuous Current COM_, NC_, NO                      | ±350mA     |

| Peak Current COM_, NC_, NO_ (pulsed at 1ms,           |            |

| 50% duty cycle)                                       | ±700mA     |

| Peak Current COM_, NC_, NO_ (pulsed at 1ms,           |            |

| 10% duty cycle)                                       | ±1.5A      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |            |

| 10-Pin UTQFN (derate 6.9mW/°C above +70°C)            | 559mW      |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) (N 10-Pin UTQFN | ,      |

|------------------------------------------------------------------------|--------|

| Junction-to-Ambient Thermal Resistance (θ,JA)                          |        |

| 10-Pin UTQFN                                                           | , ,    |

| Operating Temperature Range                                            |        |

| Junction Temperature Range                                             | +150°C |

| Storage Temperature Range                                              |        |

| Lead Temperature (soldering, 10s)                                      | +300°C |

|                                                                        |        |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.7 \text{V to } +5.5 \text{V}, T_A = -40 ^{\circ} \text{C to } +85 ^{\circ} \text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.0 \text{V}, T_A = +25 ^{\circ} \text{C.})$  (Note 2)

| PARAMETER                               | SYMBOL                                                     | CONDITIONS                                                                                                                           |                              | MIN | TYP | MAX | UNITS             |

|-----------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|-------------------|

| Power-Supply Range                      | Vcc                                                        |                                                                                                                                      |                              | 1.8 |     | 5.5 | V                 |

| Undervoltage Lockout                    | V <sub>UVLO</sub>                                          |                                                                                                                                      |                              |     | 1.4 |     | V                 |

|                                         |                                                            | V <sub>CB1</sub> = V <sub>CB2</sub> = 0V or V <sub>CC</sub>                                                                          | V <sub>C</sub> C = +3V       |     | 1.2 | 2.5 |                   |

| Supply Current                          | 1                                                          |                                                                                                                                      | $V_{CC} = +5.5V$             |     | 3.1 | 6   |                   |

| (MAX4991/MAX4992)                       | lcc                                                        | $V_{CB1} = V_{CB2} = +0.5V$ or                                                                                                       | $V_{CC} = +2.7V$             |     |     | 3   | μA                |

|                                         |                                                            | +1.4V                                                                                                                                | $V_{CC} = +5.5V$             |     |     | 14  | 1                 |

|                                         |                                                            | $V_{\overline{EN}} = V_{CC}$ , $V_{CB} = 0V$ or $V_{CC}$                                                                             | $V_{CC} = +5.5V$             |     | 0.1 | 1   | μΑ                |

|                                         |                                                            | \ <del></del>                                                                                                                        | VCC = +3V                    |     | 1.2 | 2.5 |                   |

| Supply Current<br>(MAX4993/MAX4994)     | Icc                                                        | $V_{\overline{EN}} = 0V$ , $V_{CB} = 0V$ or $V_{CC}$                                                                                 | $V_{CC} = +5.5V$             |     | 3.1 | 6   |                   |

| (IVIANAGGO)IVIANAGGA)                   |                                                            | $V_{\overline{EN}} = V_{CB} = +0.5V \text{ or } +1.4V$                                                                               | $V_{CC} = +2.7V$             |     |     | 3   |                   |

|                                         |                                                            |                                                                                                                                      | $V_{CC} = +5.5V$             |     |     | 8.5 |                   |

| Power-Supply Rejection<br>Ratio         | PSRR                                                       | $R_L = R_S = 50\Omega$ , $f = 20kHz$                                                                                                 |                              |     | 80  |     | dB                |

| Analog Signal Range                     | V <sub>NC_</sub> , V <sub>NO_</sub> ,<br>V <sub>COM_</sub> |                                                                                                                                      |                              | 0   |     | Vcc | V                 |

| On Desistance                           | Ron                                                        | V <sub>CC</sub> = +2.7V, V <sub>NC</sub> or V <sub>NO</sub> = 0<br>to V <sub>CC</sub> , I <sub>COM</sub> = 100mA                     | T <sub>A</sub> = +25°C       |     | 0.3 | 0.5 | Ω                 |

| On-Resistance                           |                                                            |                                                                                                                                      | $T_A = T_{MIN}$ to $T_{MAX}$ |     |     | 0.6 |                   |

| On-Resistance Match<br>Between Channels | ΔR <sub>ON</sub>                                           | V <sub>CC</sub> = +2.7V, between NC_, NO_ only, I <sub>COM_</sub> = 100mA, V <sub>NC_</sub> or V <sub>NO_</sub> = V <sub>CC</sub> /2 |                              |     | 3   |     | mΩ                |

| On-Resistance Flatness                  | R <sub>FLAT</sub>                                          | $V_{CC} = +2.7V$ , $V_{NC}$ or $V_{NO} = 0$ to $V_{CC}$ , $I_{COM} = 100$ mA (Note 3)                                                |                              |     | 1   |     | mΩ                |

| COM Output Noice                        | NCOM_                                                      | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                                               | f = 20Hz to 20kHz            |     | 1   |     | 11/27.42          |

| COM_ Output Noise                       |                                                            | $V_{NC} = V_{NO} = 0V, R_L = 50\Omega$                                                                                               | f = 0Hz to 1MHz              |     | 50  |     | μV <sub>RMS</sub> |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.7 \text{V to } +5.5 \text{V}, T_A = -40 ^{\circ} \text{C to } +85 ^{\circ} \text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.0 \text{V}, T_A = +25 ^{\circ} \text{C}.)$  (Note 2)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                                                                                                               | MIN    | TYP   | MAX  | UNITS |

|-----------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|-------|

| NC_, NO_, Off-Leakage<br>Current              | I <sub>L(OFF)</sub> | V <sub>CC</sub> = +2.7V, switch open, V <sub>NC</sub> or V <sub>NO</sub> = 0V or V <sub>CC</sub> , V <sub>COM</sub> = V <sub>CC</sub> or 0V                              | -100   |       | +100 | nA    |

| COM_ Off-Leakage Current<br>(MAX4993/MAX4994) | ICOM_L(OFF)         | $V_{CC} = +2.7V$ , $V_{\overline{EN}} = V_{CC}$ , $V_{NC}$ or $V_{NO} = 0V$ or $V_{CC}$ , $V_{COM} = V_{CC}$ or $0V$                                                     | -100   |       | +100 | nA    |

| COM_ On-Leakage Current                       | ICOM_L(ON)          | V <sub>CC</sub> = +2.7V, switch closed, V <sub>NC</sub> or V <sub>NO</sub> = 0V, V <sub>CC</sub> or unconnected, V <sub>COM</sub> = 0V, V <sub>CC</sub> , or unconnected | 60 140 |       | 140  | nA    |

| DYNAMIC                                       |                     |                                                                                                                                                                          |        |       |      |       |

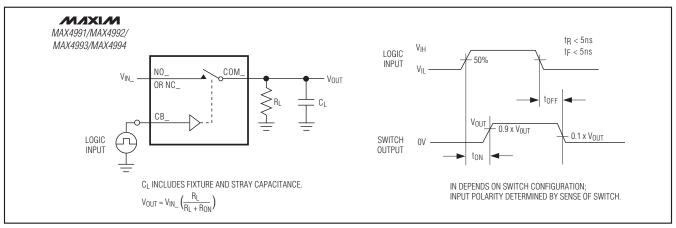

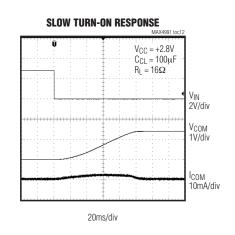

| Turn-On Time                                  | 4                   | $V_{CC} = +2.7V$ , $V_{NC}$ or $V_{NO} = +1.5V$ , $R_L = 50\Omega$ , $C_L = 35pF$ (MAX4991/MAX4993)                                                                      | 120    | 360   | 630  | ms    |

| (Note 4) (Figure 1)                           | ton                 | $V_{CC}$ = +2.7V, $V_{NC}$ or $V_{NO}$ = +1.5V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (MAX4992/MAX4994)                                                                     |        | 20    | 150  | μs    |

| Turn-Off Time                                 | toff                | $V_{CC}$ = +2.7V, $V_{NC}$ or $V_{NO}$ = +1.5V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF, Figure 1 (Note 4)                                                                    |        | 0.5   | 2    | μs    |

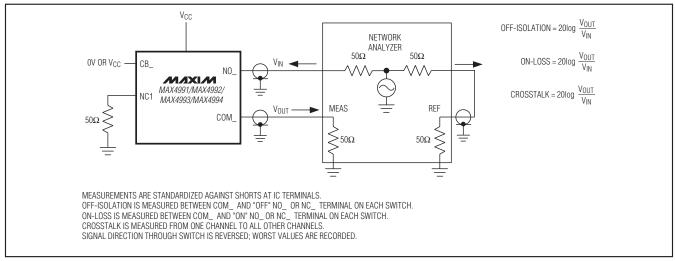

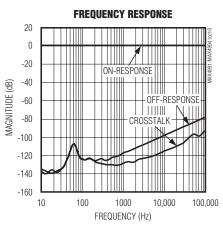

| Off-Isolation                                 | V <sub>ISO</sub>    | $R_S = R_L = 50\Omega$ , $f = 20kHz$ , $V_{COM} = 1V_{P-P}$ , Figure 2 (Note 5)                                                                                          |        | -90   |      | dB    |

| Crosstalk                                     | VCT                 | $R_S = R_L = 50\Omega$ , $f = 20kHz$ , $V_{COM} = 1V_{P-P}$ , Figure 2 (Note 6)                                                                                          |        | -110  |      | dB    |

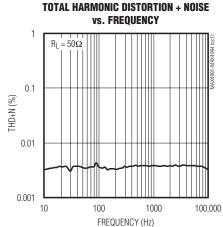

| Total Harmonic Distortion                     | THD+N               | $f$ = 20Hz to 20kHz, $V_{COM}$ = 0.5 $V_{P-P}$ , $R_S$ = $R_L$ = 50 $\Omega$ , DC bias = 0 $V$                                                                           |        | 0.004 |      | %     |

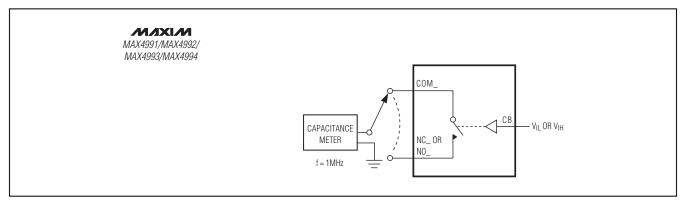

| NC_, NO_ Off-Capacitance                      | Coff                | COM_ = GND (DC bias), f = 1MHz,<br>V <sub>NO(NC)</sub> = 100mV <sub>P-P</sub> , (Figure 3)                                                                               |        | 45    |      | pF    |

| COM_ On-Capacitance                           | Con                 | COM_ = GND (DC bias), f = 1MHz,<br>VCOM = 100mV <sub>P-P</sub> (Figure 3)                                                                                                |        | 65    |      | pF    |

| DIGITAL I/O (CB, CB1, CB2, EN)                |                     |                                                                                                                                                                          |        |       |      | •     |

| Input Logic-High                              | VIH                 |                                                                                                                                                                          | 1.4    |       |      | V     |

| Input Logic-Low                               | VIL                 |                                                                                                                                                                          |        |       | 0.5  | V     |

| Input Leakage Current                         | ICB                 | $V_{CB} = V_{\overline{EN}} = 0V \text{ or } V_{CC}$                                                                                                                     | -1     |       | +1   | μΑ    |

**Note 2:** All devices are 100% production tested at  $T_A = +25$ °C. All temperature limits are guaranteed by design.

**Note 3:** Flatness is defined as the difference between the maximum and minimum values of on-resistance as measured over the specified analog ranges.

Note 4: All timing is measured using 10% and 90% levels.

Note 5: Off-isolation =  $20log [V_{COM}/(V_{NO} \text{ or } V_{NC})]$ ,  $V_{COM} = output$ ,  $V_{NO} \text{ or } V_{NC} = input$  to off switch.

Note 6: Between any two switches.

### **Test Circuits/Timing Diagrams**

Figure 1. Switching Time

Figure 2. On-Loss, Off-Isolation, and Crosstalk

Figure 3. Channel Off-/On-Capacitance

4 \_\_\_\_\_\_\_\_\_/VIXI/VI

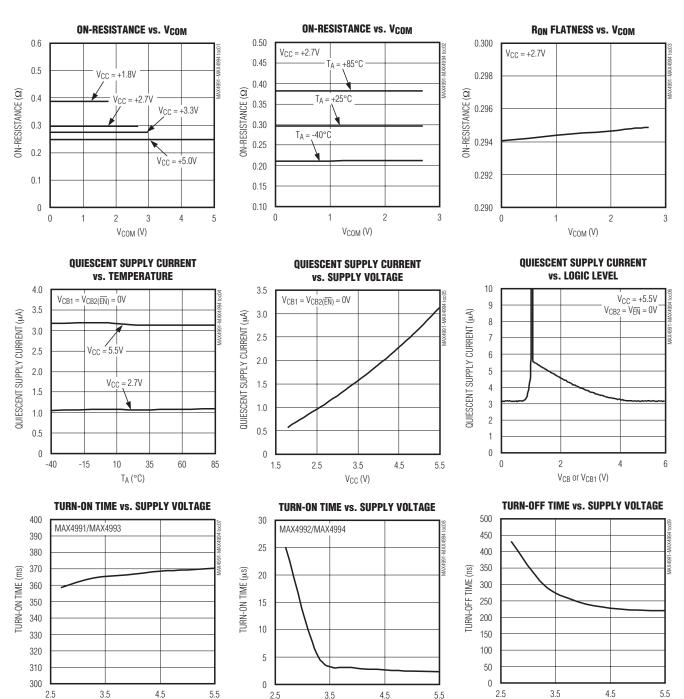

## Typical Operating Characteristics

$(V_{CC} = +3.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

SUPPLY VOLTAGE (V)

SUPPLY VOLTAGE (V)

SUPPLY VOLTAGE (V)

## Typical Operating Characteristics (continued)

$(V_{CC} = +3.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Pin Description**

| PIN             |                 | NAME   | FUNCTION                                                                                                                                            |  |

|-----------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX4991/MAX4992 | MAX4993/MAX4994 | NAIVIE | FUNCTION                                                                                                                                            |  |

| 1               | 1               | Vcc    | Positive-Supply Voltage Input. Bypass $V_{CC}$ to GND with a $0.1\mu F$ capacitor as close as possible to the device.                               |  |

| 2               | 2               | NO1    | Analog Switch 1—Normally Open Terminal                                                                                                              |  |

| 3               | 3               | COM1   | Analog Switch 1—Common Terminal. COM1 must be connected to the speaker load for click-and-pop reduction.                                            |  |

| 4               | _               | CB1    | Digital Control Input for Switch 1                                                                                                                  |  |

| _               | 4               | СВ     | Digital Control Input for Switch 1 and Switch 2                                                                                                     |  |

| 5               | 5               | NC1    | Analog Switch 1—Normally Closed Terminal                                                                                                            |  |

| 6               | 6               | GND    | Ground                                                                                                                                              |  |

| 7               | 7               | NC2    | Analog Switch 2—Normally Closed Terminal                                                                                                            |  |

| 8               | _               | CB2    | Digital Control Input for Switch 2                                                                                                                  |  |

| _               | 8               | ĒN     | Active-Low Enable Input—Drive $\overline{\text{EN}}$ high to put switches in high impedance. Drive $\overline{\text{EN}}$ low for normal operation. |  |

| 9               | 9               | COM2   | Analog Switch 2—Common Terminal. COM2 must be connected to the speaker load for click-and-pop reduction.                                            |  |

| 10              | 10              | NO2    | Analog Switch 2—Normally Open Terminal                                                                                                              |  |

## **Functional Diagram**

## **Detailed Description**

The MAX4991–MAX4994 low  $0.3\Omega$  (typ) on-resistance analog switches have break-before-make switching and operate from a single +1.8V to +5.5V supply. The MAX4991/MAX4993 provide a slow turn-on time, and with COM\_ used as the output, reduce clicks and pops due to coupling capacitors and audio amplifiers with a DC output bias. This feature is important for existing architectures with coupling capacitors at the output that need click-and-pop reduction.

The MAX4993/MAX4994 DPDT switches with an active-low enable input  $\overline{(EN)}$  set all channels to high impedance and reduce supply current when driven high. The MAX4991–MAX4994 have a low 0.004% THD+N to route high-fidelity audio signals.

#### **Digital Control Input**

The MAX4991/MAX4992 have two digital control logic inputs, CB1 and CB2. The MAX4993/MAX4994 have a single digital-control logic input, CB. The digital control logic inputs control the position of the corresponding switch as shown in the *Functional Diagram*. Driving logic inputs rail-to-rail minimizes power consumption.

#### Enable Input (MAX4993/MAX4994)

The MAX4993/MAX4994 feature an active-low enable input  $(\overline{EN})$ . When  $\overline{EN}$  is driven high, the switches are high impedance and reduce supply current. When  $\overline{EN}$  is driven low, the MAX4993/MAX4994 operate in normal mode. Driving  $\overline{EN}$  rail-to-rail minimizes power consumption.

#### **Analog Signal Levels**

The MAX4991–MAX4994 have a very low and stable RON,  $0.3\Omega$  (typ), as the analog input signals are swept from ground to VCC (see *Typical Operating Characteristics*). These switches are bidirectional, allowing NO\_, NC\_, and COM\_ to be configured as either inputs or outputs; however, click-and-pop reduction is only operational when COM\_ is used as the output.

#### **Power-Supply Rejection Ratio**

PSRR is the measurement of AC power-supply ripple or noise that couples to the output. Variations in supply voltage corrupt the audio signal due to changes in the RON value by supply modulation. The MAX4991–MAX4994 maintain a 80dB (typ) PSRR across the supply-voltage range, eliminating any corruption of the audio signal from supply variations. Therefore, with no audio signal, the RON variation due to supply-voltage ripple does not contribute to any output signal modulation.

### **Applications Information**

#### **Click-Pop Reduction**

The MAX4991/MAX4993 feature a slow switch turn-on that can reduce click-and-pop noise caused by abrupt changes in voltage across a speaker. These voltage

changes usually occur when a single-supply audio amplifier with a DC bias is turned on, causing a spike of current in the speaker while the coupling capacitor charges (see the *Typical Operating Circuit*). If the audio amplifier connected to the unused input is powered up before the switch position changes, the MAX4991/MAX4993 reduce the current spike to COM\_. The speaker load must be present so that the current charging the coupling capacitor has a path to ground.

#### Layout

Good layout improves performance by decreasing the amount of stray capacitance and noise. Minimize PCB trace lengths and resistor leads and place external components as close as possible to the device.

#### **Power-Supply Sequencing**

Caution: Do not exceed the absolute maximum ratings because stresses beyond the listed ratings may cause permanent damage to the device.

Proper power-supply sequencing is recommended for all devices. Always apply V<sub>CC</sub> before applying analog signals especially if the analog signal is not current limited.

\_\_\_ /VI/IXI/VI

## **Typical Application Circuit**

## **Chip Information**

PROCESS: BiCMOS

## Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 10 UTQFN     | V101AICN-1   | <u>21-0028</u> |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                        | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 5/08             | Initial release.                                                                                                                                                                                                                   | _                |

| 1                  | 6/09             | <ul> <li>Corrected names of power pins (added subscripting) in <i>Electrical Characteristics</i>.</li> <li>Changed the name of <i>TOC 10</i> to "Frequency Response."</li> <li>Added units of measure to <i>TOC 12</i>.</li> </ul> | 2, 6             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Maxim Integrated:

MAX4992ELB+T MAX4992EVB+T MAX4993EVB+T MAX4992EVB+ MAX4993EVB+