# **ISO150**

# Dual, Isolated, Bi-Directional DIGITAL COUPLER

# **FEATURES**

- REPLACES HIGH-PERFORMANCE OPTOCOUPLERS

- DATA RATE: 80M Baud, typ

- LOW POWER CONSUMPTION:

25mW Per Channel, max

- TWO CHANNELS, EACH BI-DIRECTIONAL, PROGRAMMABLE BY USER

- PARTIAL DISCHARGE TESTED: 2400Vrms

- CREEPAGE DISTANCE OF 16.5mm (DIP)

- **LOW COST PER CHANNEL**

- PLASTIC DIP AND SOIC PACKAGES

# **APPLICATIONS**

- DIGITAL ISOLATION FOR A/D, D/A CONVERSION

- ISOLATED UART INTERFACE

- MULTIPLEXED DATA TRANSMISSION

- ISOLATED PARALLEL TO SERIAL INTERFACE

- **TEST EQUIPMENT**

- MICROPROCESSOR SYSTEM INTERFACE

- ISOLATED LINE RECEIVER

- GROUND LOOP ELIMINATION

## DESCRIPTION

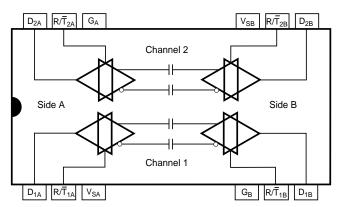

The ISO150 is a two-channel, galvanically isolated data coupler capable of data rates of 80MBaud, typical. Each channel can be individually programmed to transmit data in either direction.

Data is transmitted across the isolation barrier by coupling complementary pulses through high voltage 0.4pF capacitors. Receiver circuitry restores the pulses to standard logic levels. Differential signal transmission rejects isolation-mode voltage transients up to  $1.6kV/\mu s$ .

ISO150 avoids the problems commonly associated with optocouplers. Optically isolated couplers require high current pulses and allowance must be made for LED aging. The ISO150's Bi-CMOS circuitry operates at 25mW per channel.

ISO150 is available in a 24-pin DIP package and in a 28-lead SOIC. Both are specified for operation from –40°C to 85°C.

International Airport Industrial Park

• Mailing Address: PO Box 11400

• Tucson, AZ 85734

• Street Address: 6730 S. Tucson Blvd.

• Tucson, AZ 85706

Tel: (520) 746-1111

• Tucson, AZ 85706

• Tucson, AZ 85706

• FAX: (520) 889-1510

• Immediate Product Info: (800) 548-6132

# **SPECIFICATIONS**

$T_A = +25$ °C,  $V_S = +5V$  unless otherwise noted.

| PARAMETER                                           | CONDITION                    | ISO150AP, AU      |            |       |          |

|-----------------------------------------------------|------------------------------|-------------------|------------|-------|----------|

|                                                     |                              | MIN               | TYP        | MAX   | UNITS    |

| ISOLATION PARAMETERS                                |                              |                   |            |       |          |

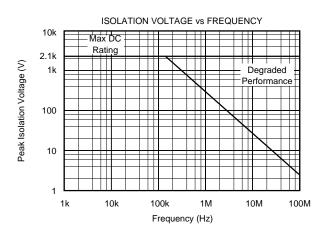

| Rated Voltage, Continuous                           | 60Hz                         | 1500              |            |       | Vrms     |

| Partial Discharge, 100% Test(1)                     | 1s, 5pC                      | 2400              |            |       | Vrms     |

| Creepage Distance (External)                        |                              |                   |            |       |          |

| DIP—"P" Package                                     |                              |                   | 16         |       | mm       |

| SOIC—"U" Package                                    |                              |                   | 7.2        |       | mm       |

| Internal Isolation Distance                         |                              |                   | 0.10       |       | mm       |

| Isolation Voltage Transient Immunity <sup>(2)</sup> |                              |                   | 1.6        |       | kV/μs    |

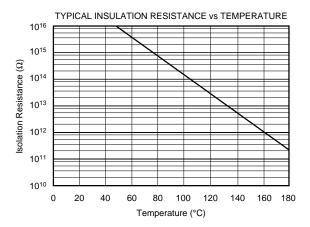

| Barrier Impedance                                   |                              |                   | >1014    7 |       | Ω    pF  |

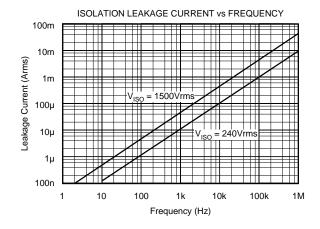

| Leakage Current                                     | 240Vrms, 60Hz                |                   | 0.6        |       | μArms    |

| DC PARAMETERS                                       |                              |                   |            |       |          |

| Logic Output Voltage, High, V <sub>OH</sub>         | $I_{OH} = 6mA$               | V <sub>S</sub> -1 |            | $V_S$ | V        |

| Low, V <sub>OL</sub>                                | $I_{OL} = 6mA$               | 0                 |            | 0.4   | V        |

| Logic Output Short-Circuit Current                  | Source or Sink               |                   | 30         |       | mA       |

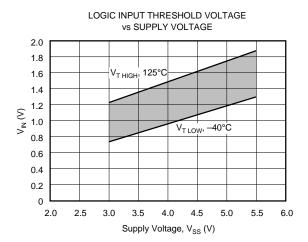

| Logic Input Voltage, High <sup>(3)</sup>            |                              | 2                 |            | $V_S$ | V        |

| Low <sup>(3)</sup>                                  |                              | 0                 |            | 0.8   | V        |

| Logic Input Capacitance                             |                              |                   | 5          |       | pF       |

| Logic Input Current                                 |                              |                   | <1         |       | nA       |

| Power Supply Voltage Range <sup>(3)</sup>           |                              | 3                 | 5          | 5.5   | V        |

| Power Supply Current <sup>(4)</sup>                 |                              |                   |            |       |          |

| Transmit Mode                                       | DC                           |                   | 0.001      | 100   | μA       |

|                                                     | 50MBaud                      |                   | 14         |       | mA       |

| Receive Mode                                        | DC                           |                   | 7.2        | 10    | mA       |

|                                                     | 50MBaud                      |                   | 16         |       | mA       |

| AC PARAMETERS                                       | 0 50 5                       |                   |            |       |          |

| Data Rate, Maximum <sup>(5)</sup>                   | $C_L = 50pF$                 | 50<br>DC          | 80         |       | MBaud    |

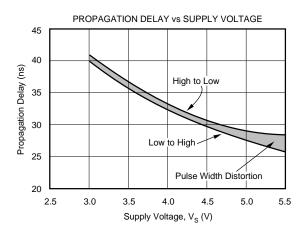

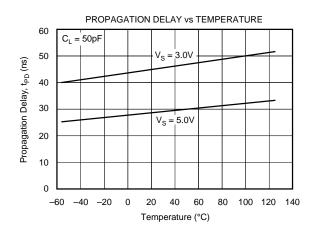

| Data Rate, Minimum Propagation Time(6)              | C 50=E                       | 20                | 27         | 40    |          |

| Propagation Delay Skew <sup>(7)</sup>               | $C_L = 50pF$<br>$C_L = 50pF$ | 20                | 0.5        | 2     | ns       |

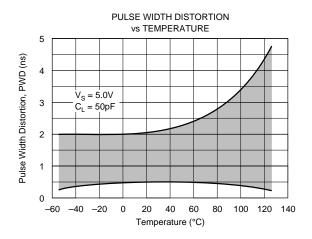

| Pulse Width Distortion <sup>(8)</sup>               | $C_L = 50pF$<br>$C_1 = 50pF$ |                   | 1.5        | 6     | ns<br>ns |

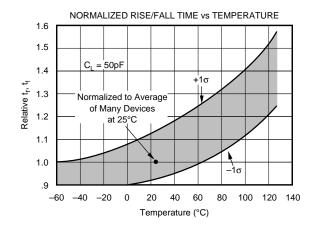

| Output Rise/Fall Time, 10% to 90%                   | $C_L = 50pF$<br>$C_1 = 50pF$ |                   | 9          | 14    | ns       |

| Mode Switching Time                                 | OL = JOH                     |                   | 9          | 14    | 113      |

| Receive-to-Transmit                                 |                              |                   | 13         |       | ns       |

| Transmit-to-Receive                                 |                              |                   | 75         |       | ns       |

| TEMPERATURE RANGE                                   |                              |                   |            |       |          |

| Operating Range                                     |                              | -40               |            | 85    | °C       |

| Storage                                             |                              | -40               |            | 125   | °C       |

| Thermal Resistance,θ <sub>JA</sub>                  |                              |                   | 75         |       | °C/W     |

NOTES: (1) All devices receive a 1s test. Failure criterion is  $\geq$ 5 pulses of  $\geq$ 5pC. (2) The voltage rate-of-change across the isolation barrier that can be sustained without data errors. (3) Logic inputs are HCT-type and thresholds are a function of power supply voltage with approximately 0.4V hystersis—see text. (4) Supply current measured with both tranceivers set for the indicated mode. Supply current varies with data rate—see typical curves. (5) Calculated from the maximum Pulse Width Distortion (PWD), where Data Rate = 0.3/PWD. (6) Propagation time measured from  $V_{IN} = 1.5V$  to  $V_O = 2.5V$ . (7) The difference in propagation time of channel A and channel B in any combination of transmission directions. (8) The difference between progagation time of a rising edge and a falling edge.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                       | 40°C to +125°C               |

|-------------------------------------------|------------------------------|

| Supply Voltages, V <sub>s</sub>           | 0.5 to 6V                    |

| Transmitter Input Voltage, V,             |                              |

| Receiver Output Voltage, Vo               | 0.5 to V <sub>s</sub> + 0.5V |

| R/T <sub>x</sub> Inputs                   | 0.5 to V <sub>s</sub> + 0.5V |

| Isolation Voltage dV/dt, V <sub>ISO</sub> | 500kV/μs                     |

| D <sub>x</sub> Short to Ground            | Continuous                   |

| Junction Temperature, T,                  | 175°C                        |

| Lead Temperature (soldering, 10s)         | 260°C                        |

| 1.6mm below seating plane (DIP package)   | 300°C                        |

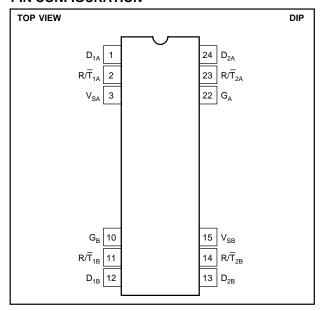

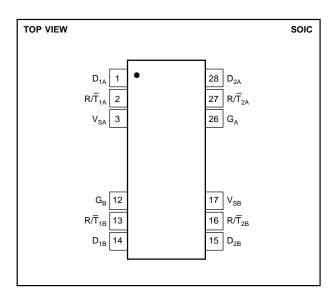

## **PIN CONFIGURATION**

## PACKAGE INFORMATION(1)

| MODEL PACKAGE |                        | PACKAGE DRAWING<br>NUMBER |  |

|---------------|------------------------|---------------------------|--|

| ISO150AP      | 24-Pin Single-Wide DIP | 243-1                     |  |

| ISO150AU      | 28-Lead SOIC           | 217-2                     |  |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## **PIN DESCRIPTIONS**

| NAME              | FUNCTION                                                                                                  |

|-------------------|-----------------------------------------------------------------------------------------------------------|

| D <sub>1A</sub>   | Data in or data out for transceiver 1A. $R/\overline{T}_{1A}$ held low makes $D_{1A}$ an input pin.       |

| R/T <sub>1A</sub> | Receive/Transmit switch controlling transceiver 1A.                                                       |

| V <sub>SA</sub>   | +5V supply pin for side A which powers transceivers 1A and 2A.                                            |

| G <sub>B</sub>    | Ground pin for transceivers 1B and 2B.                                                                    |

| R/T <sub>1B</sub> | Receive/Transmit switch controlling transceiver 1B.                                                       |

| D <sub>1B</sub>   | Data in or data out for transceiver 1B. $R\overline{T}_{_{1B}}$ held low makes $D_{_{1B}}$ an input pin.  |

| D <sub>2B</sub>   | Data in or data out for transceiver 2B. $R/\overline{T}_{2B}$ held low makes $D_{2B}$ an input pin.       |

| R/T <sub>2B</sub> | Receive/Transmit switch controlling D <sub>2B</sub> .                                                     |

| V <sub>SB</sub>   | +5V supply pin for side B which powers transceivers 1B and 2B.                                            |

| $G_{A}$           | Ground pin for transceivers 1A and 2A.                                                                    |

| R/T <sub>2A</sub> | Receive/Transmit switch controlling transceiver 2A.                                                       |

| D <sub>2A</sub>   | Data in or data out for transceiver 2A. $R/\overline{T}_{_{2A}}$ held low makes $D_{_{2A}}$ in input pin. |

# **(X)**

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

BURR-BROWN®

**ISO150**

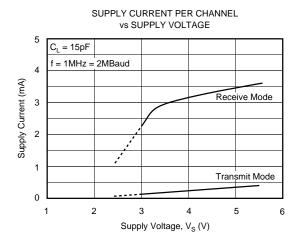

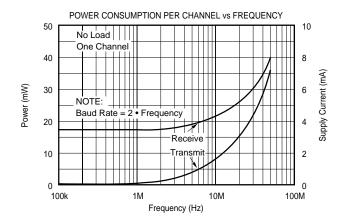

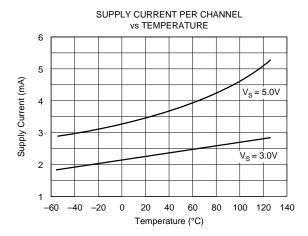

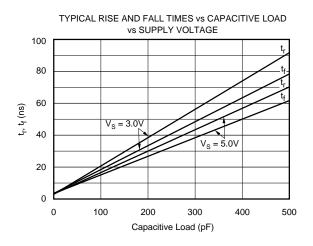

# **TYPICAL PERFORMANCE CURVES**

$T_A = +25$ °C,  $V_S = +5$ V unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

$T_A = +25$ °C,  $V_S = +5V$  unless otherwise noted.

# TYPICAL PERFORMANCE CURVES (CONT)

$T_A = +25$ °C,  $V_S = +5$ V unless otherwise noted.

## **ISOLATION BARRIER**

Data is transmitted by coupling complementary logic pulses to the receiver through two 0.4pF capacitors. These capacitors are built into the ISO150 package with Faraday shielding to guard against false triggering by external electrostatic fields.

The integrity of the isolation barrier of the ISO150 is verified by partial discharge testing. 2400Vrms, 60Hz, is applied across the barrier for one second while measuring any tiny discharge currents that may flow through the barrier. These current pulses are produced by localized ionization within the barrier. This is the most sensitive and reliable indicator of barrier integrity and longevity, and does not damage the barrier. A device fails the test if five or more current pulses of 5pC or greater are detected.

Conventional isolation barrier testing applies test voltage far in excess of the rated voltage to catastrophically break down a marginal device. A device that passes the test may be weakened, and lead to premature failure.

## **APPLICATIONS INFORMATION**

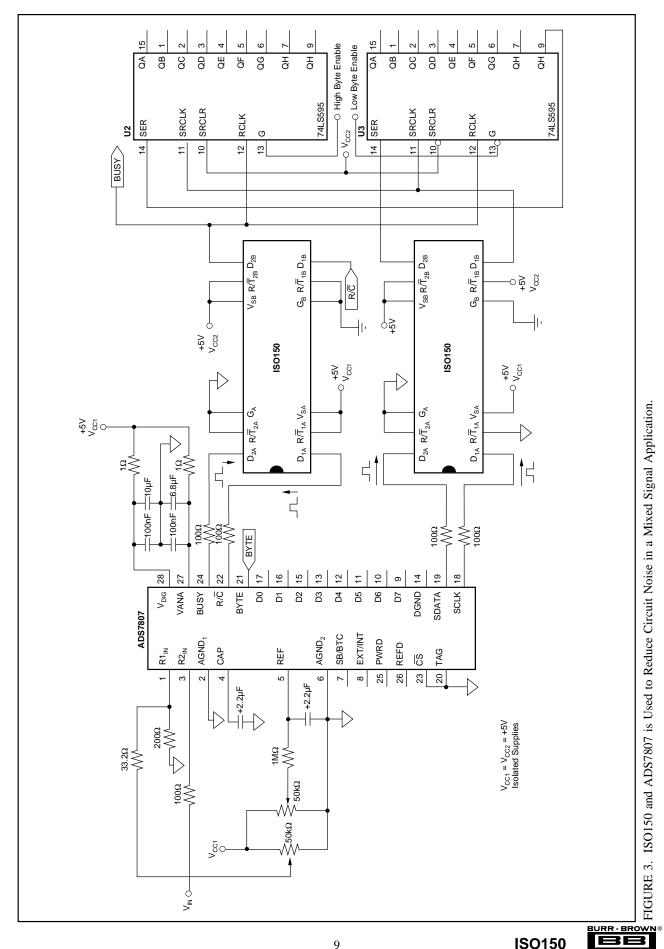

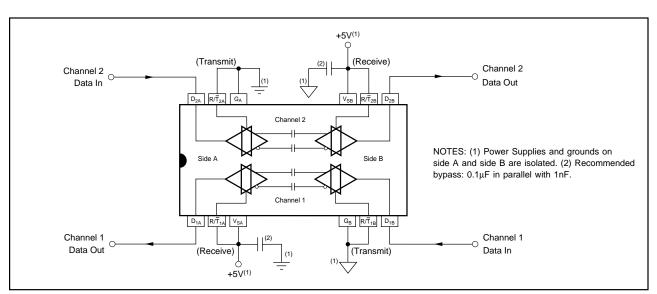

Figure 1 shows the ISO150 connected for basic operation. Channel 1 is configured to transmit data from side B to A. Channel 2 is set for transmission from side A to B. The  $R/\overline{T}$  pins for each of the four transceivers are shown connected to the required logic level for the transmission direction shown. The transmission direction can be controlled by logic signals applied to the  $R/\overline{T}$  pins. Channel 1 and 2 can be independently controlled for the desired transmission direction.

FIGURE 1. Basic Operation Diagram.

### **LOGIC LEVELS**

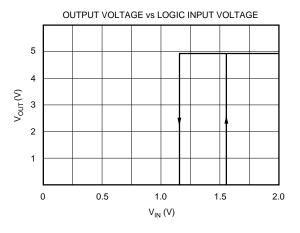

A single pin serves as a data input or output, depending on the mode selected. Logic inputs are CMOS with thresholds set for TTL compatibility. The logic threshold is approximately 1.3V with 5V supplies and with approximately 400mV of hysteresis. Input logic thresholds vary with the power supply voltage. Drive the logic inputs with signals that swing the full logic voltage swing. The ISO150 will use somewhat greater quiescent current if logic inputs do not swing within 0.5V of the power supply rails.

In receive mode, the data output can drive 15 standard LS-TTL loads. It will also drive CMOS loads. The output drive circuits are CMOS.

## **POWER SUPPLY**

Separate, isolated power supplies must be connected to side A and side B to provide galvanic isolation. Nominal rated supply voltage is 5V. Operation extends from 3V to 5.5V. Power supplies should be bypassed close to the device pins on both sides of the isolation barrier.

The  $V_S$  pin for each side powers the transceivers for both channel 1 and 2. The specified supply current is the total of both transceivers on one side, both operating in the indicated mode. Supply current for one transceiver in transmit mode and one in receive mode can be estimated by averaging the specifications for transmit and receive operation. Supply current varies with the data transmission rate—see typical curves.

## **POWER-UP STATE**

The ISO150 transmits information across the barrier only when the input-side data changes logic state. When a transceiver is first programmed for receive mode, or is powered-up in receive mode, its output is initialized "high". Subsequent changes of data applied to the input side will cause the output to properly reflect the input side data.

## SIGNAL LOSS

The ISO150's differential-mode signal transmission and careful receiver design make it highly immune to voltage across the isolation barrier (isolation-mode voltage). Rapidly changing isolation-mode voltage can cause data errors. As the rate of change of isolation voltage is increased, there is a very sudden increase in data errors. Approximately 50% of ISO150s will begin to produce data errors with isolation-mode transients of  $1.6kV/\mu s$ . This may occur as low as  $500V/\mu s$  in some devices. In comparison, a 1000V rms, 60Hz isolation-mode voltage has a rate of change of approximately  $0.5V/\mu s$ .

Still, some applications with large, noisy isolation-mode voltage can produce data errors by causing the receiver output to change states. After a data error, subsequent changes in input data will produce correct output data.

## PROPAGATION DELAY AND SKEW

Logic transitions are delayed approximately 27ns through the ISO150. Some applications are sensitive to data skew—the difference in propagation delay between channel 1 and channel 2. Skew is less than 2ns between channel 1 and channel 2. Applications using more than one ISO150 must allow for somewhat greater skew from device to device. Since all devices are tested for delay times of 20ns min to 40ns max, 20ns is the largest device-to-device data skew.

## **MODE CHANGES**

The transmission direction of a channel can be changed "on the fly" by reversing the logic levels at the channel's  $R/\overline{T}$  pins on both side A and side B. Approximately 75ns after the transceiver is programmed to receive mode its output is initialized "high", and will respond to subsequent input-side changes in data.

#### STANDBY MODE

Quiescent current of each transceiver circuit is very low in transmit mode when input data is not changing (1nA typical). To conserve power when data transmission is not required, program both side A and B transceivers for transmit mode. Input data applied to either transceiver is ignored by the other side. High speed data applied to either transceiver will increase quiescent current.

## CIRCUIT LAYOUT

The high speed of the ISO150 and its isolation barrier require careful circuit layout. Use good high speed logic layout techniques for the input and output data lines. Power supplies should be bypassed close to the device pins on both sides of the isolation barrier. Use low inductance connections. Ground planes are recommended.

Maintain spacing between side 1 and side 2 circuitry equal or greater than the spacing between the missing pins of the ISO150 (approximately 16mm for the DIP version). Sockets are not recommended.

**ISO150**

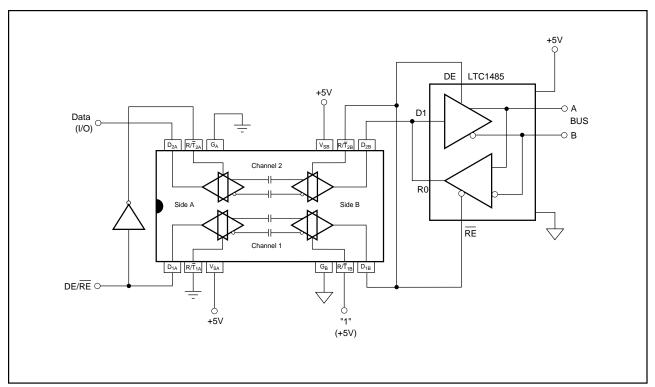

FIGURE 2. Isolated RS-485 Interface.