# AUIR3241S/AUIR3242S - Board Back to Back 12V

### **User Guide**

### **About this document**

#### Scope and purpose

Help customers to "plug and play" AUIR3241S/AUIR3242S back-to-back board in order to assess the features of the underlying product AUIR3241S/AUIR3242S.

For sake of simplicity this document is valid for both AUIR3241S back-to-back board and AUIR3242S back-to-back board.

Difference between AUIR3241S and AUIR3242 is Vin pin logic:

AUIR3242S ON → Vin= low AUIR3241S ON → Vin= high

### **Table of contents**

| Abo  | ut this documentut this document   | 1 |

|------|------------------------------------|---|

| Tab  | le of contents                     | 1 |

|      | Overview                           |   |

|      | Connecting and operating the board |   |

| 3    |                                    |   |

| 4    | Mechanicals                        |   |

| 5    | Electrical schematic               | 6 |

| 5.1  | Electrical diagram                 | 6 |

| 5.2  | Bill of materials                  | 7 |

| 6    | PCB details                        | 8 |

| Revi | ision history                      | 9 |

## Overview

## 1 Overview

AUIR3241S/AUIR3242S board back-to-back is a semiconductor-based solution of a fail-safe/fail operational power switch for automotive applications.

AUIR3241S/AUIR3242S board has a back-to-back, N-channel MOSFET common <u>source</u> structure and allows replacement of any mechanical relay by cutting the current flow in both directions. Additionally, the back-to-back structure blocks current in case of reverse battery situation.

The MOSFET are protected against linear mode by UVLO (Under voltage lock-out) feature, integrated in the driver. See driver datasheet for more information on the feature.

An analog and digital circuit are implemented to monitor driver's boost converter activity and detect gatesource leakage of MOSFET.

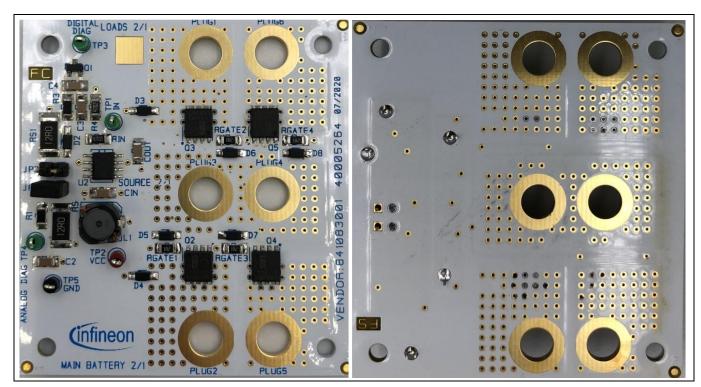

Figure 1 Top & Bottom view

Table 1 Infineon parts used

| Туре              | Reference        | PCS | Comment                                  |

|-------------------|------------------|-----|------------------------------------------|

| Driver            | AUIR3241S        | 1   | Full analog driver, AUIR3241S board only |

| Driver            | AUIR3242S        | 1   | Full analog driver, AUIR3242S board only |

| MOSFET Trench 40V | IAUC120N04S6N009 | 4   | Also exists in $0.60 m\Omega$ version    |

### AUIR3241S - AUIR3242S - Board Back to Back 12V

### **User Guide**

### Connecting and operating the board

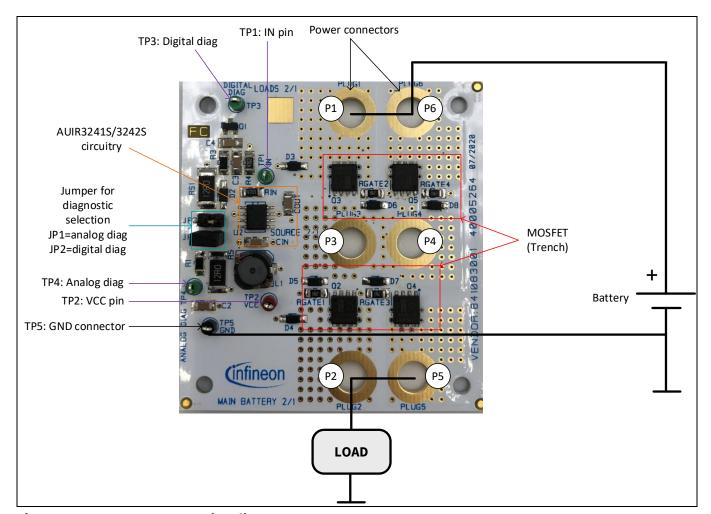

## 2 Connecting and operating the board

This chapter describes how to connect the board and gives a non-exhaustive list of actions to avoid in order to keep AUIR3241S/AUIR3242S and the board operational.

The board is designed for 50A continuous, 80A for one-minute operation.

Note: It is important to always connect TP5 GND to the battery or power supply negative/ground terminal.

#### **Important tips:**

- Connect both power connectors (P5&P6, P2&P5) if using continuous currents >10A.

- Do not connect P1 and P2 jumper at the same time. Start by connecting P1, analog diag.

Figure 2 Power connection diagram

## Please Avoid the following:

- Short between Cout and GND as this will lead to driver destruction—Short Vout to Vcc to try UVLO feature.

- Do not connect two batteries/power sources together as there is no protection implemented.

User Guide

### **Switching behaviour**

#### **Switching behaviour** 3

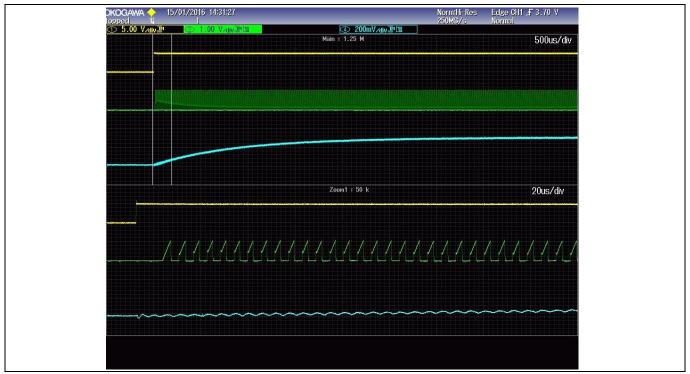

Values shown in this chapter are measured under lab conditions and will vary for different cooling Note: conditions and setups, and samples used.

Figure 3 Waveforms from OFF to ON mode [Yellow V<sub>IN</sub>; Green V<sub>RS</sub>; Blue V<sub>GS(AUIR3241S)</sub>; Purple V<sub>LOAD</sub>]

Figure 4 shows the behavior of the RS pin and analog diagnostic during turn-on, assuming that a short-circuit is present across gate-source of one of the MOSFET. This can be tested by replacing one of the diodes (D5, D6, D7, D8) across a MOSFET gate-source by an appropriate SMD resistor.

Waveforms from OFF to ON mode with  $R_{GS(SHORT)}=100\Omega$  [Yellow  $V_{IN}$ ; Green  $V_{RS}$ ; Blue  $V_{DIAG\_ANALOG}$ ] Figure 4 4 of 10

**Mechanicals**

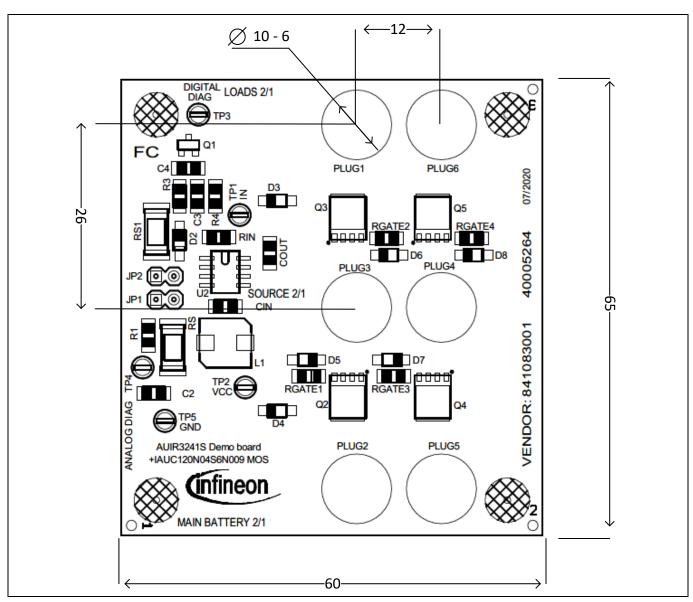

## 4 Mechanicals

Figure 5 Top Assembly [mm]

V2.1

## Electrical schematic

## **5** Electrical schematic

## 5.1 Electrical diagram

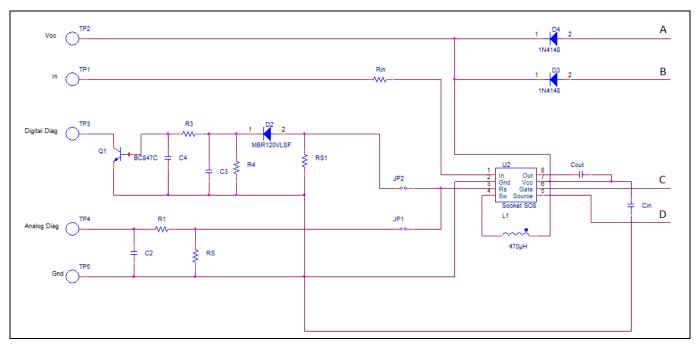

Figure 6 Driver side, valid for both AUIR3241S and AUIR3242S

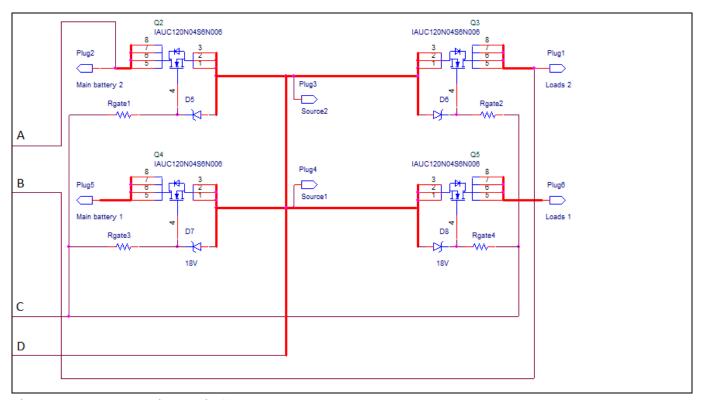

Figure 7 Power side, valid for both AUIR3241S and AUIR3242S

V2.1

## AUIR3241S - AUIR3242S - Board Back to Back 12V

## **User Guide**

## **Electrical schematic**

## 5.2 Bill of materials

Table 2 Bill of material

| ltem       | Quantity                   | Reference in electrical diagram | Value / Type                  | Package / brand when available |

|------------|----------------------------|---------------------------------|-------------------------------|--------------------------------|

| 1          | 1 Cin                      |                                 | 470 nF, 50V                   | Package 1206                   |

| <b>2</b> 3 |                            | C2,C3,C4                        | 100nF, 25V                    | Package 1206                   |

| 3          | 6                          | D6,D5,D7,D8                     | 18V<br>MMSZ5248BT1G           | SOD-123                        |

| 4          | 2                          | D3, D4                          | 1N4148W                       | SOD-123                        |

| 5          | 2                          | JP1,JP2                         | Multicomp-pro 2pins           | + 1 Jumper per board           |

| 6          | 1                          | L1                              | 470μΗ                         | CLF7045NIT-471M-D              |

| 7          | 1                          | Q1                              | BC847C                        | TO-236AB                       |

| 8          | 1                          | Rin                             | 4.7kΩ                         | SMD1206                        |

| 9          | 6                          | Rgate1 to 8                     | 1kΩ                           | SMD1206                        |

| 10         | 2                          | RS, RS1                         | 12Ω / 1W                      | SMD1812                        |

| 11         | 2                          | R1,R3                           | 10kΩ                          | SMD1206                        |

| 12         | 5                          | TP1,TP2,TP3,TP4,TP5             | Test point                    | Test point                     |

| 13         | 1                          | U2                              | AUIR3241S or<br>AUIR3242S     | SOIC8                          |

| 14         | <b>14</b> 6 Q2, Q3, Q4, Q5 |                                 | IAUC120N04S6N009              | SSO8: PG-TDSON-8               |

| 15         |                            |                                 | 1μF, 25V                      | SMD1206                        |

| 16         | <b>16</b> 1 D2             |                                 | 20V Schottky<br>MBR120VLSFT1G | SOD-123                        |

| 17         | 1 R4                       |                                 | 47kΩ                          | SMD1206                        |

**PCB** details

## 6 PCB details

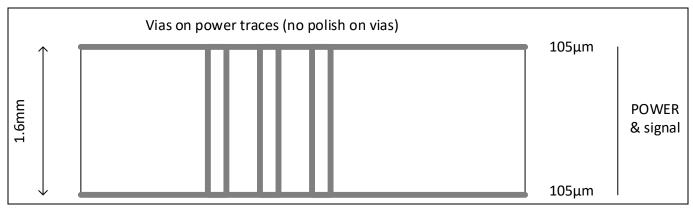

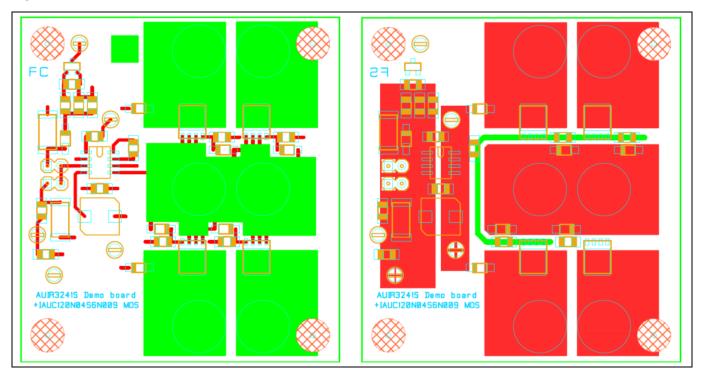

AUIR3241S/AUIR3242S PCB is a 2-layer, FR4 material board. Figure 8 describes the layer arrangements; layer details can be found in figure 9.

Figure 8 PCB layers

Vias were used to connect the two layers on the power side to allow better thermal flow and current sharing between layers. However, the number of vias is not optimized and can be reduced without reducing the board thermal performance.

The layout choice offers many MOSFET test possibilities: back-to-back, Q-diode, one MOSFET + 3 Q-diodes or high-side switch MOSFET.

Figure 9 Top layer (left) and bottom layer (right) [105μm]

## **AUIR3241S - Board Back to Back 12V**

## **User Guide**

**Revision history**

## **Revision history**

| Document version | Date of release    | Description of changes                              |

|------------------|--------------------|-----------------------------------------------------|

| A1               | November 30, 2015  | Initial document                                    |

| A2               | December 10, 2015  | BOM modification                                    |

| A3               | December 28, 2015  | Update digital diagnostic schematic                 |

| A4               | April 26, 2016     | Add measure and labels updated                      |

| 2.0              | August 24, 2020    | New board version: Mechanicals, BOM, layout updated |

|                  |                    | One user guide for AUIR3241S and AUIR3242S boards.  |

| 2.1              | September 09, 2020 | Updated current capability and layer thickness      |

#### Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-09-09

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference ifx1

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or charactercharacteristics (enheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contair dangerous substances. For information on the types in question please contact your nearest Infineor Technologies office.

Except as otherwise explicitly approved by Infineor Technologies in a written document signed by authorized representatives of Infineor Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof car reasonably be expected to result in personal injury.