# ANALOG 4-Channel, Low Noise, Low Power, 24-Bit, DEVICES Sigma-Delta ADC with PGA and Reference Sigma-Delta ADC with PGA and Reference

AD7124-4-EP **Enhanced Product**

#### **FEATURES**

3 power modes **RMS** noise

Low power: 24 nV rms at 1.17 SPS, gain = 128 (255  $\mu$ A typical) Mid power: 20 nV rms at 2.34 SPS, gain = 128 (355  $\mu$ A typical) Full power: 23 nV rms at 9.4 SPS, gain = 128 (930 µA typical) Up to 22 noise free bits in all power modes (gain = 1)

**Output data rate**

Full power: 9.38 SPS to 19,200 SPS Mid power: 2.34 SPS to 4800 SPS Low power: 1.17 SPS to 2400 SPS Rail-to-rail analog inputs for gains > 1

Simultaneous 50 Hz/60 Hz rejection at 25 SPS (single cycle

Diagnostic functions (which aid safe integrity level (SIL)

certification)

**Crosspoint multiplexed analog inputs**

4 differential/7 pseudo differential inputs

Programmable gain (1 to 128)

Band gap reference with 10 ppm/°C drift maximum (70 µA)

Matched programmable excitation currents Internal clock oscillator and temperature sensor

On-chip bias voltage generator

Low-side power switch

**Multiple filter options**

**Sensor burnout detection**

**Automatic channel sequencer**

Per channel configuration

Power-down current: 5 µA maximum

24-lead TSSOP

3-wire or 4-wire serial interface

SPI, QSPI, MICROWIRE, and DSP compatible

Schmitt trigger on SCLK

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard)

Full military temperature range: -55°C to +125°C

Controlled manufacturing baseline

1 assembly/test site

1 fabrication site

**Product change notification**

Qualification data available on request

#### **APPLICATIONS**

Military and space

**Avionics**

Pressure measurement

Instrumentation

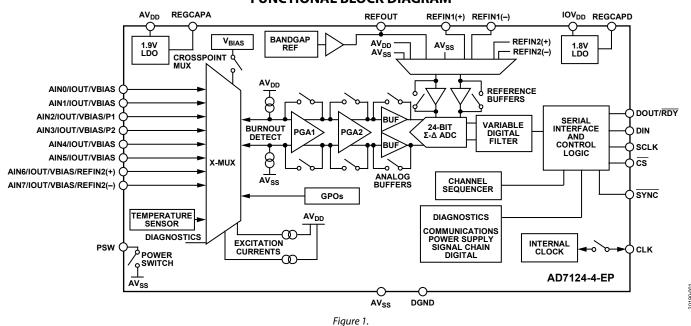

## FUNCTIONAL BLOCK DIAGRAM

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **TABLE OF CONTENTS**

| Features                  | 1  |

|---------------------------|----|

| Enhanced Product Features | 1  |

| Applications              | 1  |

| Functional Block Diagram  | 1  |

| Revision History          | 2  |

| General Description       | 3  |

| Specifications            | 4  |

| Absolute Maximum Ratings  | 10 |

| Thermal Resistance                            |

|-----------------------------------------------|

| ESD Caution                                   |

| Pin Configuration and Function Descriptions11 |

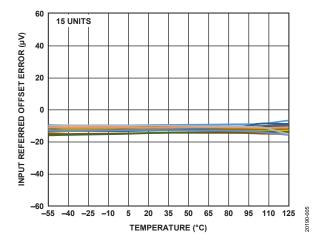

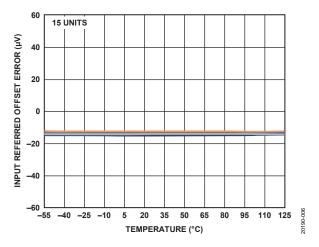

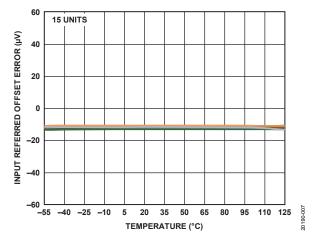

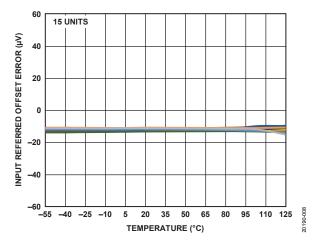

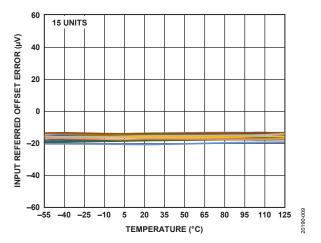

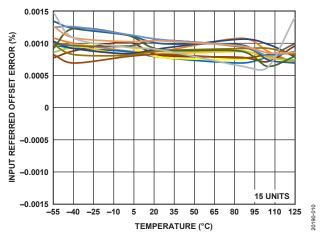

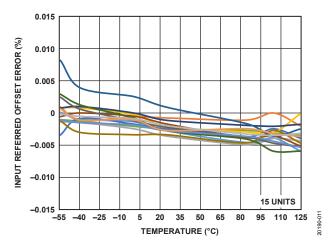

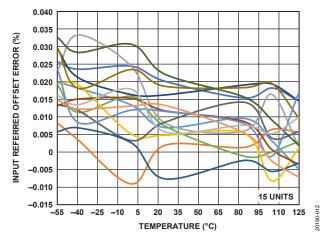

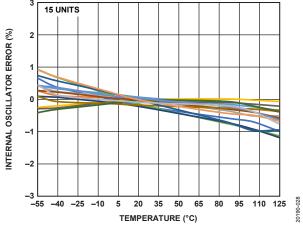

| Typical Performance Characteristics           |

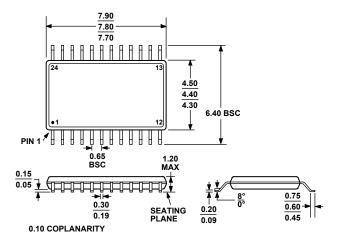

| Outline Dimensions                            |

| Ordering Guide17                              |

## **REVISION HISTORY**

4/2019—Revision 0: Initial Version

## **GENERAL DESCRIPTION**

The AD7124-4-EP is a low power, low noise, completely integrated analog front end for high precision measurement applications. The device contains a low noise, 24-bit  $\Sigma$ - $\Delta$  analog-to-digital converter (ADC), and can be configured to have four differential inputs or seven single-ended or pseudo differential inputs. The on-chip low gain stage ensures that signals of small amplitude can be interfaced directly to the ADC.

One of the major advantages of the AD7124-4-EP is that it gives the user the flexibility to employ one of three integrated power modes. The current consumption, range of output data rates, and rms noise can be tailored with the power mode selected. The device also offers a multitude of filter options, ensuring that the user has the highest degree of flexibility.

The AD7124-4-EP can achieve simultaneous 50 Hz and 60 Hz rejection when operating at an output data rate of 25 SPS (single cycle settling), with rejection in excess of 80 dB achieved at lower output data rates.

The AD7124-4-EP establishes the highest degree of signal chain integration. The device contains a precision, low noise, low drift internal band gap reference, and also accepts an external differential reference, which can be internally buffered. Other key integrated features include programmable low drift excitation current sources, burnout currents, and a bias voltage generator, which sets the common-mode voltage of a channel to  $AV_{\rm DD}/2$ . The low-side power switch enables the user to power down bridge sensors between conversions, ensuring the absolute minimal power consumption of the system. The device also allows the user the option of operating with either an internal clock or an external clock.

The integrated channel sequencer allows several channels to be enabled simultaneously, and the AD7124-4-EP sequentially

converts on each enabled channel, simplifying communication with the device. As many as 16 channels can be enabled at any time; a channel being defined as an analog input or a diagnostic such as a power supply check or a reference check. This unique feature allows diagnostics to be interleaved with conversions. The AD7124-4-EP also supports per channel configuration. The device allows eight configurations or setups. Each configuration consists of gain, filter type, output data rate, buffering, and reference source. The user can assign any of these setups on a channel by channel basis.

The AD7124-4-EP also has extensive diagnostic functionality integrated as part of its comprehensive feature set. These diagnostics include a cyclic redundancy check (CRC), signal chain checks, and serial interface checks, which lead to a more robust solution. These diagnostics reduce the need for external components to implement diagnostics, resulting in reduced board space needs, reduced design cycle times, and cost savings. The failure modes effects and diagnostic analysis (FMEDA) of a typical application has shown a safe failure fraction (SFF) greater than 90% according to IEC 61508.

The device operates with a single analog power supply from 2.7 V to 3.6 V or a dual 1.8 V power supply. The digital supply has a range of 1.65 V to 3.6 V. It is specified for the full military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The AD7124-4-EP is housed in a 24-lead TSSOP package.

Note that, throughout this data sheet, multifunction pins, such as  $\overline{DOUT}/\overline{RDY}$ , are referred to either by the entire pin name or by a single function of the pin, for example,  $\overline{RDY}$ , when only that function is relevant.

Additional application and technical information can be found in the AD7124-4 data sheet.

## **SPECIFICATIONS**

$AV_{DD} = 2.9 \text{ V}$  to 3.6 V (full power mode), 2.7 V to 3.6 V (mid and low power mode),  $IOV_{DD} = 1.65 \text{ V}$  to 3.6 V,  $AV_{SS} = DGND = 0 \text{ V}$ , REFINx(+) = 2.5 V,  $REFINx(-) = AV_{SS}$ , master clock = 614.4 kHz, all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                                    | Min                 | Тур               | Max     | Unit       | <b>Test Conditions/Comments</b>                |

|-----------------------------------------------------------|---------------------|-------------------|---------|------------|------------------------------------------------|

| ADC                                                       |                     |                   |         |            |                                                |

| Output Data Rate, f <sub>ADC</sub>                        |                     |                   |         |            |                                                |

| Low Power Mode                                            | 1.17                |                   | 2400    | SPS        |                                                |

| Mid Power Mode                                            | 2.34                |                   | 4800    | SPS        |                                                |

| Full Power Mode                                           | 9.38                |                   | 19,200  | SPS        |                                                |

| No Missing Codes <sup>2</sup>                             | 24                  |                   |         | Bits       | FS <sup>3</sup> > 2, sinc <sup>4</sup> filter  |

| <u> </u>                                                  | 24                  |                   |         | Bits       | FS <sup>3</sup> > 8, sinc <sup>3</sup> filter  |

| Resolution                                                |                     |                   |         |            |                                                |

| RMS Noise and Update Rates                                |                     |                   |         |            |                                                |

| Integral Nonlinearity (INL)                               | -4                  | ±1                | +4      | ppm of FSR | $Gain = 1^2$                                   |

| , , ,                                                     | -15                 | ±2                | +15     | ppm of FSR | Gain > 1 <sup>4</sup>                          |

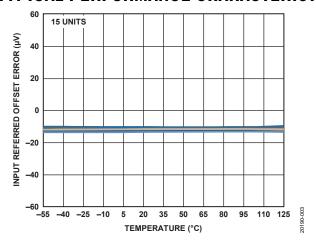

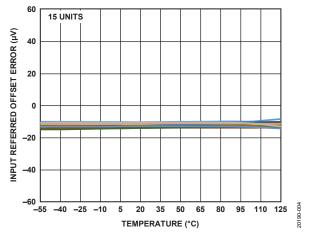

| Offset Error⁵                                             |                     |                   |         |            |                                                |

| Before Calibration                                        |                     | ±15               |         | μV         | Gain = 1 to 8                                  |

|                                                           |                     | 200/gain          |         | μV         | Gain = 16 to 128                               |

| After Internal Calibration/System                         |                     | In order of       |         | F          |                                                |

| Calibration                                               |                     | noise             |         |            |                                                |

| Offset Error Drift vs. Temperature <sup>6</sup>           |                     |                   |         |            |                                                |

| Low Power Mode                                            |                     | 10                |         | nV/°C      | Gain = 1 or gain > 16                          |

|                                                           |                     | 80                |         | nV/°C      | Gain = 2 to 8                                  |

|                                                           |                     | 40                |         | nV/°C      | Gain = 16                                      |

| Mid Power Mode                                            |                     | 10                |         | nV/°C      | Gain = 1 or gain > 16                          |

| ma rewer mode                                             |                     | 40                |         | nV/°C      | Gain = 2 to 8                                  |

|                                                           |                     | 20                |         | nV/°C      | Gain = 16                                      |

| Full Power Mode                                           |                     | 10                |         | nV/°C      | Gain = 10                                      |

| Gain Error <sup>5, 7</sup>                                |                     | 10                |         | 110/ C     |                                                |

| Before Internal Calibration                               | -0.0025             |                   | +0.0025 | %          | Gain = 1, T <sub>A</sub> = 25°C                |

| before internal Calibration                               | -0.0023             | -0.3              | +0.0023 | %          | Gain > 1                                       |

| After Internal Calibration                                | -0.016              | +0.004            | +0.016  | %          | Gain = 2 to 8, $T_A = 25^{\circ}C$             |

| After internal Calibration                                | -0.016              | ±0.004<br>±0.025  | +0.016  |            | Gain = 2 to 8, 1 <sub>A</sub> = 25 C           |

| After Contain Calibration                                 |                     |                   |         | %          | Gain = 16 to 128                               |

| After System Calibration                                  |                     | In order of noise |         |            |                                                |

| Gain Error Drift vs. Temperature                          |                     | 1                 | 2       | ppm/°C     |                                                |

| Power Supply Rejection                                    |                     | '                 | 2       | рріп/ С    | A <sub>IN</sub> = 1 V/gain, external reference |

| Low Power Mode                                            | 87                  |                   |         | dB         | Gain = $2 \text{ to } 16$                      |

| LOW I OWEI MODE                                           | 96                  |                   |         | dB         | Gain = 1 or gain > 16                          |

| Mid Power Mode <sup>2</sup>                               | 90                  |                   |         | dB         | Gain = 2 to 16                                 |

| Mid Power Mode                                            |                     |                   |         | dB         |                                                |

| Full Dower Made                                           | 100                 |                   |         |            | Gain = 1 or gain > 16                          |

| Full Power Mode                                           | 99                  |                   |         | dB         |                                                |

| Common-Mode Rejection <sup>8</sup>                        | 0.5                 | 00                |         | JD.        | A 41/ 1                                        |

| At DC <sup>2</sup>                                        | 85                  | 90                |         | dB         | $A_{IN} = 1 \text{ V, gain} = 1$               |

|                                                           | 105                 | 115               |         | dB         | $A_{IN} = 1 \text{ V/gain, gain 2 or 4}$       |

|                                                           | 102 <sup>9, 2</sup> | 120               |         | dB         | $A_{IN} = 1 \text{ V/gain, gain 2 or 4}$       |

|                                                           | 115                 | 120               |         | dB         | $A_{IN} = 1 \text{ V/gain, gain } \ge 8$       |

|                                                           | 105 <sup>9, 2</sup> |                   |         | dB         | A <sub>IN</sub> = 1 V/gain, gain ≥ 8           |

| Sinc <sup>3</sup> , Sinc <sup>4</sup> Filter <sup>2</sup> |                     |                   |         |            |                                                |

| At 50 Hz, 60 Hz                                           | 120                 |                   |         | dB         | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz             |

| At 50 Hz                                                  | 120                 |                   |         | dB         | 50 SPS, 50 Hz ± 1 Hz                           |

| At 60 Hz                                                  | 120                 |                   |         | dB         | 60 SPS, 60 Hz ± 1 Hz                           |

| Parameter <sup>1</sup>                                      | Min T | ур Мах | Unit | Test Conditions/Comments                                       |

|-------------------------------------------------------------|-------|--------|------|----------------------------------------------------------------|

| Fast Settling Filters <sup>2</sup>                          |       |        |      |                                                                |

| At 50 Hz                                                    | 115   |        | dB   | First notch at 50 Hz, 50 Hz ± 1 Hz                             |

| At 60 Hz                                                    | 115   |        | dB   | First notch at 60 Hz, 60 Hz ± 1 Hz                             |

| Post Filters <sup>2</sup>                                   |       |        |      |                                                                |

| At 50 Hz, 60 Hz                                             | 130   |        | dB   | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

| ,                                                           | 130   |        | dB   | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

| Normal Mode Rejection <sup>2</sup> Sinc <sup>4</sup> Filter | 1.55  |        |      | 20 01 0,00 112 = 1 112                                         |

| External Clock                                              |       |        |      |                                                                |

|                                                             | 120   |        | dB   | 10 CDC FOLI-   111- 6011-   111-                               |

| At 50 Hz, 60 Hz                                             | -     |        |      | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

|                                                             | 80    |        | dB   | 50 SPS, REJ60 <sup>10</sup> =1, 50 Hz ± 1 Hz,<br>60 Hz ± 1 Hz  |

| At 50 Hz                                                    | 120   |        | dB   | 50 SPS, 50 Hz ± 1 Hz                                           |

| At 60 Hz                                                    | 120   |        | dB   | 60 SPS, 60 Hz ± 1 Hz                                           |

| Internal Clock                                              |       |        |      |                                                                |

| At 50 Hz, 60 Hz                                             | 98    |        | dB   | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

|                                                             | 66    |        | dB   | 50 SPS, REJ60 <sup>10</sup> = 1, 50 Hz ± 1 Hz,<br>60 Hz ± 1 Hz |

| At 50 Hz                                                    | 92    |        | dB   | 50 SPS, 50 Hz ± 1 Hz                                           |

| At 60 Hz                                                    | 92    |        | dB   | 60 SPS, 60 Hz ± 1 Hz                                           |

| Sinc <sup>3</sup> Filter                                    |       |        |      | ,                                                              |

| External Clock                                              |       |        |      |                                                                |

| At 50 Hz, 60 Hz                                             | 100   |        | dB   | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

|                                                             | 65    |        | dB   | 50 SPS, REJ60 <sup>10</sup> = 1, 50 Hz ± 1 Hz,<br>60 Hz ± 1 Hz |

| At 50 Hz                                                    | 100   |        | dB   | 50 SPS, 50 Hz ± 1 Hz                                           |

| At 60 Hz                                                    | 100   |        | dB   | 60 SPS, 60 Hz ± 1 Hz                                           |

| Internal Clock                                              |       |        |      | 33 3, 33 1.2 = 1.1.2                                           |

| At 50 Hz, 60 Hz                                             | 73    |        | dB   | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

| 71. 30 112, 00 112                                          | 52    |        | dB   | 50 SPS, REJ60 <sup>10</sup> = 1, 50 Hz ± 1 Hz,<br>60 Hz ± 1 Hz |

| At 50 Hz                                                    | 68    |        | dB   | 50 SPS, 50 Hz ± 1 Hz                                           |

| At 60 Hz                                                    | 68    |        | dB   | 60 SPS, 60 Hz ± 1 Hz                                           |

| Fast Settling Filters                                       | 00    |        | ab   | 00 31 37 00 112 2 1 112                                        |

| External Clock                                              |       |        |      |                                                                |

| At 50 Hz                                                    | 40    |        | dB   | First notch at 50 Hz, 50 Hz $\pm$ 0.5 Hz                       |

| At 60 Hz                                                    | 40    |        | dB   | First notch at 60 Hz, 60 Hz $\pm$ 0.5 Hz                       |

| Internal Clock                                              | 40    |        | ab   | 1 113t 110tc11 at 00 112, 00 112 ± 0.5 112                     |

|                                                             | 24.5  |        | ЧD   | First notch at FO Hz FO Hz + O F H-                            |

| At 50 Hz                                                    | 24.5  |        | dB   | First notch at 50 Hz, 50 Hz ± 0.5 Hz                           |

| At 60 Hz                                                    | 24.5  |        | dB   | First notch at 60 Hz, 60 Hz $\pm$ 0.5 Hz                       |

| Post Filters                                                |       |        |      |                                                                |

| External Clock                                              | 0.6   |        | l In | 20 CDC FOLL 1411 COLL 111                                      |

| At 50 Hz, 60 Hz                                             | 86    |        | dB   | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

|                                                             | 62    |        | dB   | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

| Internal Clock                                              |       |        |      |                                                                |

| At 50 Hz, 60 Hz                                             | 67    |        | dB   | 20 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

|                                                             | 50    |        | dB   | 25 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                             |

| Parameter <sup>1</sup>                               | Min                     | Тур                     | Max                  | Unit    | Test Conditions/Comments                                  |

|------------------------------------------------------|-------------------------|-------------------------|----------------------|---------|-----------------------------------------------------------|

| ANALOG INPUTS <sup>11</sup>                          |                         |                         |                      |         |                                                           |

| Differential Input Voltage Ranges <sup>12</sup>      |                         | ±V <sub>REF</sub> /gain |                      | V       | $V_{REF} = REFINx(+) - REFINx(-)$ , or internal reference |

| Absolute A <sub>IN</sub> Voltage Limits <sup>2</sup> |                         |                         |                      |         |                                                           |

| Gain = 1 (Unbuffered)                                | AV <sub>SS</sub> - 0.05 |                         | $AV_{DD} + 0.05$     | V       |                                                           |

| Gain = 1 (Buffered)                                  | $AV_{SS} + 0.1$         |                         | $AV_{\text{DD}}-0.1$ | V       |                                                           |

| Gain > 1                                             | AV <sub>SS</sub> - 0.05 |                         | $AV_{DD} + 0.05$     | V       |                                                           |

| Analog Input Current                                 |                         |                         |                      |         |                                                           |

| Gain $> 1$ or Gain $= 1$ (Buffered)                  |                         |                         |                      |         |                                                           |

| Low Power Mode                                       |                         |                         |                      |         |                                                           |

| Absolute Input Current                               |                         | ±1                      |                      | nA      |                                                           |

| Differential Input Current                           |                         | ±0.2                    |                      | nA      |                                                           |

| Analog Input Current Drift                           |                         | 25                      |                      | pA/°C   |                                                           |

| Mid Power Mode                                       |                         |                         |                      |         |                                                           |

| Absolute Input Current                               |                         | ±1.2                    |                      | nA      |                                                           |

| Differential Input Current                           |                         | ±0.4                    |                      | nA      |                                                           |

| Analog Input Current Drift                           |                         | 25                      |                      | pA/°C   |                                                           |

| Full Power Mode                                      |                         |                         |                      |         |                                                           |

| Absolute Input Current                               |                         | ±3.3                    |                      | nA      |                                                           |

| Differential Input Current                           |                         | ±1.5                    |                      | nA      |                                                           |

| Analog Input Current Drift                           |                         | 25                      |                      | pA/°C   |                                                           |

| Gain = 1 (Unbuffered)                                |                         |                         |                      |         | Current varies with input voltage                         |

| Absolute Input Current                               |                         | ±2.65                   |                      | μA/V    |                                                           |

| Analog Input Current Drift                           |                         | 1.1                     |                      | nA/V/°C |                                                           |

| REFERENCE INPUT                                      |                         |                         |                      |         |                                                           |

| Internal Reference                                   |                         |                         |                      |         |                                                           |

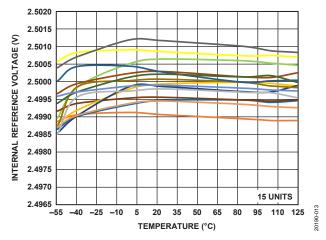

| Initial Accuracy                                     | 2.5 - 0.2%              | 2.5                     | 2.5 + 0.2%           | V       | T <sub>A</sub> = 25°C                                     |

| Drift                                                |                         | 2                       | 10                   | ppm/°C  |                                                           |

| Output Current                                       |                         |                         | 10                   | mA      |                                                           |

| Load Regulation                                      |                         | 50                      |                      | μV/mA   |                                                           |

| Power Supply Rejection                               |                         | 85                      |                      | dB      |                                                           |

| External Reference                                   |                         |                         |                      |         |                                                           |

| External REFIN Voltage <sup>2</sup>                  | 0.5                     | 2.5                     | $AV_DD$              | V       | REFIN = REFINx(+) - REFINx(-)                             |

| Absolute REFIN Voltage Limits <sup>2</sup>           | AV <sub>ss</sub> – 0.05 |                         | $AV_{DD} + 0.05$     | V       | Unbuffered                                                |

| •                                                    | AV <sub>ss</sub> + 0.1  |                         | $AV_{DD} - 0.1$      | V       | Buffered                                                  |

| Reference Input Current                              |                         |                         |                      |         |                                                           |

| Buffered                                             |                         |                         |                      |         |                                                           |

| Low Power Mode                                       |                         |                         |                      |         |                                                           |

| Absolute Input Current                               |                         | ±0.5                    |                      | nA      |                                                           |

| Reference Input Current Drift                        |                         | 10                      |                      | pA/°C   |                                                           |

| Mid Power Mode                                       |                         |                         |                      | 1       |                                                           |

| Absolute Input Current                               |                         | ±1                      |                      | nA      |                                                           |

| Reference Input Current Drift                        |                         | 10                      |                      | pA/°C   |                                                           |

| Full Power Mode                                      |                         |                         |                      |         |                                                           |

| Absolute Input Current                               |                         | ±3                      |                      | nA      |                                                           |

| Reference Input Current Drift                        |                         | 10                      |                      | pA/°C   |                                                           |

| Unbuffered                                           |                         |                         |                      | 1       |                                                           |

| Absolute Input Current                               |                         | ±12                     |                      | μA      |                                                           |

| Reference Input Current Drift                        |                         | 6                       |                      | nA/°C   |                                                           |

| Normal Mode Rejection                                |                         |                         |                      |         | Same as for analog inputs                                 |

| Common-Mode Rejection                                |                         | 100                     |                      | dB      |                                                           |

| Parameter <sup>1</sup>                    | Min                                             | Тур                               | Max                            | Unit     | <b>Test Conditions/Comments</b>                                                                                     |

|-------------------------------------------|-------------------------------------------------|-----------------------------------|--------------------------------|----------|---------------------------------------------------------------------------------------------------------------------|

| EXCITATION CURRENT SOURCES (IOUTO/IOUT1)  |                                                 |                                   |                                |          | Available on any analog input pin                                                                                   |

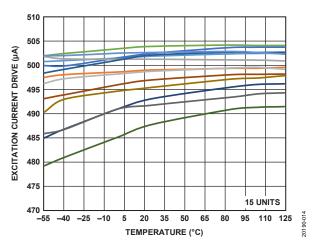

| Output Current                            |                                                 | 50/100/250/<br>500/750/1000       |                                | μΑ       |                                                                                                                     |

| Initial Tolerance                         |                                                 | ±4                                |                                | %        | $T_A = 25$ °C                                                                                                       |

| Drift                                     |                                                 | 50                                |                                | ppm/°C   |                                                                                                                     |

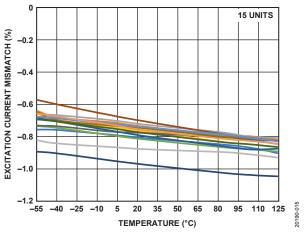

| Current Matching                          |                                                 | ±0.5                              |                                | %        | Matching between IOUT0 and IOUT1, V <sub>OUT</sub> = 0 V                                                            |

| Drift Matching <sup>2</sup>               |                                                 | 5                                 | 30                             | ppm/°C   |                                                                                                                     |

| Line Regulation (AV <sub>DD</sub> )       |                                                 | 2                                 |                                | %/V      | $AV_{DD} = 3 V \pm 5\%$                                                                                             |

| Load Regulation                           |                                                 | 0.2                               |                                | %/V      |                                                                                                                     |

| Output Compliance <sup>2</sup>            | AV <sub>SS</sub> – 0.05                         |                                   | $AV_{DD} - 0.37$               | V        | 50 μA/100 μA/250 μA/500 μA current sources, 2% accuracy                                                             |

|                                           | AV <sub>SS</sub> – 0.05                         |                                   | $AV_{DD} - 0.48$               | V        | 750 μA and 1000 μA current sources, 2% accuracy                                                                     |

| BIAS VOLTAGE (VBIAS) GENERATOR            |                                                 |                                   |                                |          | Available on any analog input pin                                                                                   |

| $V_{BIAS}$                                |                                                 | $AV_{SS} + (AV_{DD} - AV_{SS})/2$ |                                | V        |                                                                                                                     |

| V <sub>BIAS</sub> Generator Start-Up Time |                                                 | 6.7                               |                                | μs/nF    | Dependent on the capacitance connected to AINx                                                                      |

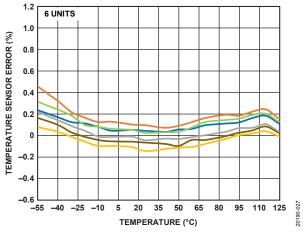

| TEMPERATURE SENSOR                        |                                                 | .0.5                              |                                | 0.0      |                                                                                                                     |

| Accuracy                                  |                                                 | ±0.5                              |                                | °C       |                                                                                                                     |

| Sensitivity                               |                                                 | 13,584                            |                                | Codes/°C |                                                                                                                     |

| LOW-SIDE POWER SWITCH                     |                                                 | _                                 |                                |          |                                                                                                                     |

| On Resistance (R <sub>ON</sub> )          |                                                 | 7                                 | 10                             | Ω        | 1                                                                                                                   |

| Allowable Current <sup>2</sup>            |                                                 |                                   | 30                             | mA       | Continuous current                                                                                                  |

| BURNOUT CURRENTS                          |                                                 |                                   |                                |          |                                                                                                                     |

| A <sub>IN</sub> Current                   |                                                 | 0.5/2/4                           |                                | μΑ       | Analog inputs must be buffered                                                                                      |

| DIGITAL OUTPUTS (P1 AND P2)               |                                                 |                                   |                                |          |                                                                                                                     |

| Output Voltage                            |                                                 |                                   |                                |          | 1                                                                                                                   |

| High, V <sub>OH</sub>                     | $AV_{DD} - 0.6$                                 |                                   |                                | V        | I <sub>SOURCE</sub> = 100 μA                                                                                        |

| Low, V <sub>OL</sub>                      |                                                 |                                   | 0.4                            | V        | I <sub>SINK</sub> = 100 μA                                                                                          |

| DIAGNOSTICS                               |                                                 |                                   |                                |          |                                                                                                                     |

| Power Supply Monitor Detect Level         |                                                 |                                   | 1.6                            | .,       | AV AV . 27V                                                                                                         |

| Analog Low Dropout Regulator (ALDO)       |                                                 |                                   | 1.6                            | V        | $AV_{DD} - AV_{SS} \ge 2.7 \text{ V}$                                                                               |

| Digital LDO (DLDO)                        | 0.7                                             |                                   | 1.55                           | V        | $ OV_{DD} \ge 1.75 \text{ V} $                                                                                      |

| Reference Detect Level                    | 0.7                                             |                                   | 1                              | V        | REF_DET_ERR bit active if $V_{REF} < 0.7  \text{V}$                                                                 |

| AINM/AINP Undervoltage Detect Level       | $AV_{DD} + 0.04$                                |                                   | ۸۷/ ۵۵/                        | V        |                                                                                                                     |

| AINM/AINP Undervoltage Detect Level       | 1                                               |                                   | AV <sub>SS</sub> – 0.04        | V        |                                                                                                                     |

| INTERNAL/EXTERNAL CLOCK                   |                                                 |                                   |                                |          |                                                                                                                     |

| Internal Clock                            | 614.4 – 5%                                      | 614.4                             | 6144 + 50/                     | kHz      |                                                                                                                     |

| Frequency<br>Duty Cycle                   | 014.4 - 5%                                      | 50:50                             | 614.4 + 5%                     | %        |                                                                                                                     |

| External Clock                            |                                                 | 50.50                             |                                | 70       |                                                                                                                     |

|                                           |                                                 | 2.4576                            |                                | MHz      | Internal divide by 4                                                                                                |

| Frequency<br>Duty Cycle Range             |                                                 | 45:55 to 55:45                    |                                | %        | internal divide by 4                                                                                                |

| LOGIC INPUTS <sup>2</sup>                 |                                                 | 45.55 10 55.45                    |                                | 70       |                                                                                                                     |

| Input Voltage                             |                                                 |                                   |                                |          |                                                                                                                     |

| Low, V <sub>INL</sub>                     |                                                 |                                   | $0.3 \times IOV_{DD}$          | V        | 1.65 V ≤ IOV <sub>DD</sub> < 1.9 V                                                                                  |

| LOW, VINL                                 |                                                 |                                   | $0.3 \times 10 \text{ V}_{DD}$ | V        | $1.9 \text{ V} \le 10 \text{ V}_{DD} < 1.9 \text{ V}$                                                               |

|                                           |                                                 |                                   | 0.33 × 10 V DD                 | V        | $1.9 \text{ V} \le 10 \text{ V}_{DD} < 2.3 \text{ V}$<br>$2.3 \text{ V} \le 10 \text{ V}_{DD} \le 3.6 \text{ V}$    |

| High, V <sub>INH</sub>                    | $0.7 \times IOV_{DD}$                           |                                   | 0.7                            | V        | $2.3 \text{ V} \le 10 \text{ V}_{DD} \le 3.6 \text{ V}$<br>$1.65 \text{ V} \le 10 \text{ V}_{DD} < 1.9 \text{ V}$   |

| I IIGII, VINH                             | $0.7 \times 10V_{DD}$<br>$0.65 \times 10V_{DD}$ |                                   |                                | V        | $1.05 \text{ V} \le 10 \text{ V}_{DD} < 1.9 \text{ V}$<br>$1.9 \text{ V} \le 10 \text{ V}_{DD} < 2.3 \text{ V}$     |

|                                           | 1.7                                             |                                   |                                | V        | $1.9 \text{ V} \le 10 \text{ V}_{DD} < 2.3 \text{ V}$<br>$2.3 \text{ V} \le 10 \text{ V}_{DD} < 2.7 \text{ V}$      |

|                                           | 2                                               |                                   |                                | V        | $2.3 \text{ V} \le 10 \text{ V}_{DD} < 2.7 \text{ V}$<br>$2.7 \text{ V} \le 10 \text{ V}_{DD} \le 3.6 \text{ V}$    |

| Hysteresis                                | 0.2                                             |                                   | 0.6                            | V        | $2.7 \text{ V} \le 10 \text{ V}_{DD} \le 3.6 \text{ V}$<br>$1.65 \text{ V} \le 10 \text{ V}_{DD} \le 3.6 \text{ V}$ |

| Input Currents                            | 0.2<br>-1                                       |                                   | 0.6<br>+1                      | - ·      | $V_{IN} = IOV_{DD} \le 3.6 \text{ V}$<br>$V_{IN} = IOV_{DD} \text{ or GND}$                                         |

| •                                         | -'                                              | 10                                | ті                             | μA       |                                                                                                                     |

| Input Capacitance                         |                                                 | 10                                |                                | pF       | All digital inputs                                                                                                  |

Rev. 0 | Page 7 of 17

| Parameter <sup>1</sup>                                           | Min                      | Тур           | Max              | Unit | Test Conditions/Comments                                                                    |

|------------------------------------------------------------------|--------------------------|---------------|------------------|------|---------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (INCLUDING CLK)                                    |                          |               |                  |      |                                                                                             |

| Output Voltage <sup>2</sup>                                      |                          |               |                  |      |                                                                                             |

| High, V <sub>он</sub>                                            | IOV <sub>DD</sub> - 0.35 |               |                  | V    | $I_{SOURCE} = 100  \mu A$                                                                   |

| Low, V <sub>OL</sub>                                             |                          |               | 0.4              | V    | $I_{SINK} = 100 \mu A$                                                                      |

| Floating State Leakage Current                                   | -1                       |               | +1               | μΑ   | ·                                                                                           |

| Floating State Output Capacitance                                |                          | 10            |                  | pF   |                                                                                             |

| Data Output Coding                                               |                          | Offset binary |                  | '    |                                                                                             |

| SYSTEM CALIBRATION <sup>2</sup>                                  |                          | -             |                  |      |                                                                                             |

| Calibration Limit                                                |                          |               |                  |      |                                                                                             |

| Full Scale (FS)                                                  |                          |               | $1.05 \times FS$ | V    |                                                                                             |

| Zero Scale                                                       | −1.05 × FS               |               |                  | V    |                                                                                             |

| Input Span                                                       | 0.8 × FS                 |               | $2.1 \times FS$  | V    |                                                                                             |

| POWER SUPPLY VOLTAGES FOR ALL POWER MODES                        |                          |               |                  |      |                                                                                             |

| AV <sub>DD</sub> to AV <sub>SS</sub>                             |                          |               |                  |      |                                                                                             |

| Low Power Mode                                                   | 2.7                      |               | 3.6              | V    |                                                                                             |

| Mid Power Mode                                                   | 2.7                      |               | 3.6              | V    |                                                                                             |

| Full Power Mode                                                  | 2.9                      |               | 3.6              | V    |                                                                                             |

| IOV <sub>DD</sub> to GND                                         | 1.65                     |               | 3.6              | V    |                                                                                             |

| AV <sub>ss</sub> to GND                                          | -1.8                     |               | 0                | V    |                                                                                             |

| IOV <sub>DD</sub> to AV <sub>SS</sub>                            |                          |               | 5.4              | V    |                                                                                             |

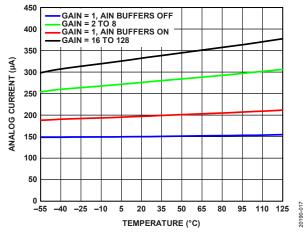

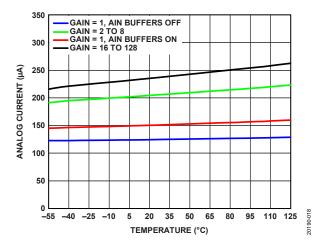

| POWER SUPPLY CURRENTS <sup>11,13</sup>                           |                          |               |                  |      |                                                                                             |

| I <sub>AVDD</sub> , External Reference                           |                          |               |                  |      |                                                                                             |

| Low Power Mode                                                   |                          |               |                  |      |                                                                                             |

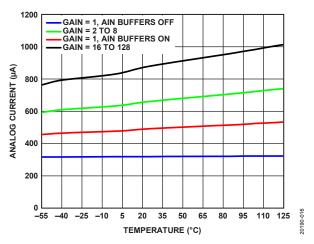

| $Gain = 1^2$                                                     |                          | 125           | 140              | μΑ   | All buffers off                                                                             |

| Gain = 1 I <sub>AVDD</sub> Increase per AINx Buffer <sup>2</sup> |                          | 15            | 25               | μA   |                                                                                             |

| Gain = 2 to 8                                                    |                          | 205           | 250              | μA   |                                                                                             |

| Gain = 16 to 128                                                 |                          | 235           | 300              | μA   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup>     |                          | 10            | 20               | μΑ   | All gains                                                                                   |

| Mid Power Mode                                                   |                          |               | 20               | μ, , | 7.11 gan 5                                                                                  |

| Gain = 1 <sup>2</sup>                                            |                          | 150           | 170              | μA   | All buffers off                                                                             |

| Gain = 1 I <sub>AVDD</sub> Increase per AINx Buffer <sup>2</sup> |                          | 30            | 40               | μΑ   | 7 iii buileis oii                                                                           |

| Gain = 2 to 8                                                    |                          | 275           | 345              | μΑ   |                                                                                             |

| Gain = 16 to 128                                                 |                          | 330           | 430              | μΑ   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup>     |                          | 20            | 30               | μΑ   | All gains                                                                                   |

| Full Power Mode                                                  |                          | 20            | 50               | μ,   | 7 iii gairis                                                                                |

| Gain = $1^2$                                                     |                          | 315           | 350              | μΑ   | All buffers off                                                                             |

| Gain = 1 I <sub>AVDD</sub> Increase per AINx Buffer <sup>2</sup> |                          | 90            | 135              | μΑ   | 7 III Ballets on                                                                            |

| Gain = 2 to 8                                                    |                          | 660           | 830              | μΑ   |                                                                                             |

| Gain = 16 to 128                                                 |                          | 875           | 1200             | μΑ   |                                                                                             |

| I <sub>AVDD</sub> Increase per Reference Buffer <sup>2</sup>     |                          | 85            | 1200             | μΑ   | All gains                                                                                   |

| l <sub>AVDD</sub> Increase                                       |                          | 55            | 120              | μ, ι | , in gains                                                                                  |

| Due to Internal Reference <sup>2</sup>                           |                          | 50            | 70               | μА   | Independent of power mode; the reference buffers are not required when using this reference |

| Due to V <sub>BIAS</sub> <sup>2</sup>                            |                          | 15            | 20               | μΑ   | Independent of power mode                                                                   |

| Due to Diagnostics <sup>2</sup>                                  |                          | 4             | 5                | μA   |                                                                                             |

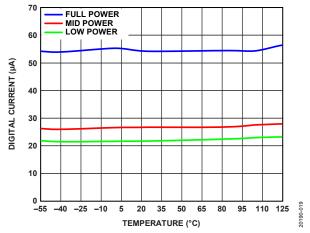

| liovad                                                           |                          |               |                  |      |                                                                                             |

| Low Power Mode                                                   |                          | 20            | 35               | μΑ   |                                                                                             |

| Mid Power Mode                                                   |                          | 25            | 40               | μA   |                                                                                             |

| Full Power Mode                                                  |                          | 55            | 80               | μA   |                                                                                             |

| Parameter <sup>1</sup>            | Min | Тур | Max | Unit | Test Conditions/Comments  |

|-----------------------------------|-----|-----|-----|------|---------------------------|

| POWER-DOWN CURRENTS <sup>13</sup> |     |     |     |      | Independent of power mode |

| Standby Current                   |     |     |     |      |                           |

| lavdd                             |     | 7   | 15  | μΑ   | LDOs on only              |

| I <sub>IOVDD</sub>                |     | 8   | 20  | μΑ   |                           |

| Power-Down Current                |     |     |     |      |                           |

| I <sub>AVDD</sub>                 |     | 1   | 3   | μΑ   |                           |

| I <sub>IOVDD</sub>                |     | 1   | 2   | μΑ   |                           |

$<sup>^{1}</sup>$  Temperature range =  $-55^{\circ}$ C to  $+125^{\circ}$ C.

<sup>&</sup>lt;sup>2</sup> These specifications are not production tested but are supported by characterization data at the initial product release.

<sup>&</sup>lt;sup>3</sup> FS is the decimal equivalent of the FS[10:0] bits in the filter registers.

<sup>&</sup>lt;sup>4</sup> The integral nonlinearity is production tested in full power mode only. For other power modes, the specification is supported by characterization data at the initial product release.

<sup>&</sup>lt;sup>5</sup> Following a system or internal zero-scale calibration, the offset error is in the order of the noise for the programmed gain and output data rate selected. A system fullscale calibration reduces the gain error to the order of the noise for the programmed gain and output data rate.

<sup>&</sup>lt;sup>6</sup> Recalibration at any temperature removes these errors.

<sup>&</sup>lt;sup>7</sup> Gain error applies to both positive and negative full-scale. A factory calibration is performed at gain = 1, T<sub>A</sub> = 25°C.

<sup>&</sup>lt;sup>8</sup> When gain > 1, the common-mode voltage is between  $(AV_{SS} + 0.1 + 0.5/gain)$  and  $(AV_{DD} - 0.1 - 0.5/gain)$ .

$<sup>^{9}</sup>$  Specification is for a wider common-mode voltage between (AV<sub>SS</sub> - 0.05 + 0.5/gain) and (AV<sub>DD</sub> - 0.1 - 0.5/gain).

<sup>10</sup> REJ60 is a bit in the filter registers. When the first notch of the sinc filter is at 50 Hz, a notch is placed at 60 Hz when REJ60 is set to 1. This gives simultaneous 50 Hz and 60 Hz rejection.

When the gain is greater than 1, the analog input buffers are enabled automatically. The buffers can only be disabled when the gain equals 1.

When  $V_{REF} = (AV_{DD} - AV_{SS})$ , the typical differential input equals  $0.92 \times V_{REF}/gain$  for the low and mid power modes and  $0.86 \times V_{REF}/gain$  for full power mode when gain > 1.

<sup>&</sup>lt;sup>13</sup> The digital inputs are equal to IOV<sub>DD</sub> or DGND with excitation currents and bias voltage generator disabled.

## ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 2.

| Parameter                                     | Rating                                      |

|-----------------------------------------------|---------------------------------------------|

| AV <sub>DD</sub> to AV <sub>SS</sub>          | -0.3 V to +3.96 V                           |

| IOV <sub>DD</sub> to DGND                     | -0.3 V to +3.96 V                           |

| IOV <sub>DD</sub> to AV <sub>SS</sub>         | −0.3 V to +5.94 V                           |

| AV <sub>ss</sub> to DGND                      | -1.98 V to +0.3 V                           |

| Analog Input Voltage to AVss                  | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |

| Reference Input Voltage to AV <sub>SS</sub>   | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |

| Digital Input Voltage to DGND                 | $-0.3$ V to $IOV_{DD} + 0.3$ V              |

| Digital Output Voltage to DGND                | $-0.3$ V to $IOV_{DD} + 0.3$ V              |

| AINx/Digital Input Current                    | 10 mA                                       |

| Operating Temperature Range                   | −55°C to +125°C                             |

| Storage Temperature Range                     | −65°C to +150°C                             |

| Maximum Junction Temperature                  | 150℃                                        |

| Lead Temperature, Soldering                   |                                             |

| Reflow                                        | 260°C                                       |

| ESD Ratings                                   |                                             |

| Human Body Model (HBM)                        | 4 kV                                        |

| Field-Induced Charged Device<br>Model (FICDM) | 1250 V                                      |

| Machine Model                                 | 400 V                                       |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC}$  is the junction to case thermal resistance.

**Table 3. Thermal Resistance**

| Package Type <sup>1</sup> | θιΑ | θις | Unit |

|---------------------------|-----|-----|------|

| RU-24                     | 128 | 42  | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board. See JEDEC JESD51.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

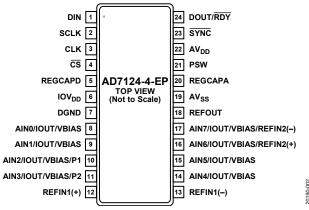

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DIN                | Serial Data Input to the Input Shift Register on the ADC. Data in the input shift register is transferred to the control registers within the ADC, with the register selection bits of the communications register identifying the appropriate register.                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | SCLK               | Serial Clock Input. This serial clock input is for data transfers to and from the ADC. The SCLK pin has a Schmitt-triggered input, making the interface suitable for opto-isolated applications. The serial clock can be continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data.                                                                                                                                                                                                       |

| 3       | CLK                | Clock Input/Clock Output. The internal clock can be made available at this pin. Alternatively, the internal clock can be disabled, and the ADC can be driven by an external clock. This allows several ADCs to be driven from a common clock, allowing simultaneous conversions to be performed.                                                                                                                                                                                                                                                                                                                                          |

| 4       | <u>cs</u>          | Chip Select Input. This is an active low logic input that selects the ADC. Use $\overline{CS}$ to select the ADC in systems with more than one device on the serial bus or as a frame synchronization signal in communicating with the device. $\overline{CS}$ can be hardwired low if the serial peripheral interface (SPI) diagnostics are unused, allowing the ADC to operate in 3-wire mode with SCLK, DIN, and DOUT interfacing with the device.                                                                                                                                                                                     |

| 5       | REGCAPD            | Digital LDO Regulator Output. Decouple this pin to DGND with a 0.1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6       | IOV <sub>DD</sub>  | Serial Interface Supply Voltage, 1.65 V to 3.6 V. IOV <sub>DD</sub> is independent of AV <sub>DD</sub> . Therefore, the serial interface can operate at 1.65 V with AV <sub>DD</sub> at 3.6 V, for example.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7       | DGND               | Digital Ground Reference Point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8       | AINO/IOUT/VBIAS    | Analog Input 0/Output of Internal Excitation Current Source/Bias Voltage. This input pin is configured via the configuration registers to be the positive or negative terminal of a differential or pseudo differential input. Alternatively, the internal programmable excitation current source can be made available at this pin. Either IOUT0 or IOUT1 can be switched to this output. A bias voltage midway between the analog power supply rails can be generated at this pin.                                                                                                                                                      |

| 9       | AIN1/IOUT/VBIAS    | Analog Input 1/Output of Internal Excitation Current Source/Bias Voltage. This input pin is configured via the configuration registers to be the positive or negative terminal of a differential or pseudo differential input. Alternatively, the internal programmable excitation current source can be made available at this pin. Either IOUT0 or IOUT1 can be switched to this output. A bias voltage midway between the analog power supply rails can be generated at this pin.                                                                                                                                                      |

| 10      | AIN2/IOUT/VBIAS/P1 | Analog Input 2/Output of Internal Excitation Current Source/Bias Voltage/General-Purpose Output 1. This input pin is configured via the configuration registers to be the positive or negative terminal of a differential or pseudo differential input. Alternatively, the internal programmable excitation current source can be made available at this pin. Either IOUT0 or IOUT1 can be switched to this output. A bias voltage midway between the analog power supply rails can be generated at this pin. This pin can also be configured as a general-purpose output bit, referenced between AV <sub>SS</sub> and AV <sub>DD</sub> . |

| Pin No. | Mnemonic                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | AIN3/IOUT/VBIAS/P2            | Analog Input 3/Output of Internal Excitation Current Source/Bias Voltage/General-Purpose Output 2. This input pin is configured via the configuration registers to be the positive or negative terminal of a differential or pseudo differential input. Alternatively, the internal programmable excitation current source can be made available at this pin. Either IOUT0 or IOUT1 can be switched to this output. A bias voltage midway between the analog power supply rails can be generated at this pin. This pin can also be configured as a general-purpose output bit, referenced between AV <sub>SS</sub> and AV <sub>DD</sub> .                                                                                                                                                                                               |