A Product Line of Diodes Incorporated

PI4IOE5V9554/9554A

# 8-bit I<sup>2</sup>C-Bus and SMBus I/O Port with Interrupt

## **Features**

- → Operation Power Supply Voltage from 2.3V to 5.5 V

- → 8-bit I<sup>2</sup>C-bus GPIO with Interrupt and Reset

- → 5V Tolerant I/Os

- → Polarity Inversion Register

- → Active LOW Interrupt Output

- → Low Current Consumption

- → 0Hz to 400KHz Clock Frequency

- → Noise Filter on SCL/SDA Inputs

- ➔ Power-on Reset

- → ESD Protection (4KV HBM and 1KV CDM)

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

- ➔ For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please <u>contact us</u> or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

- ➔ Offered in Three Different Packages:

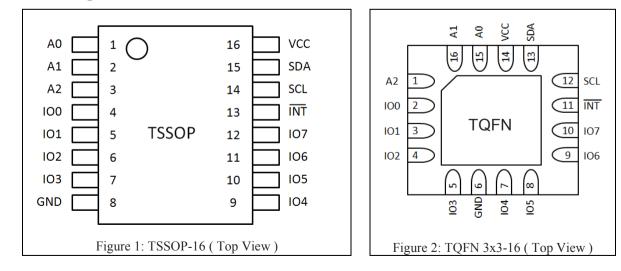

- TSSOP-16 and TQFN 3x3-16

# Description

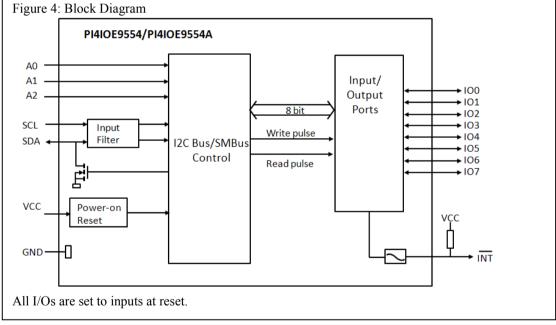

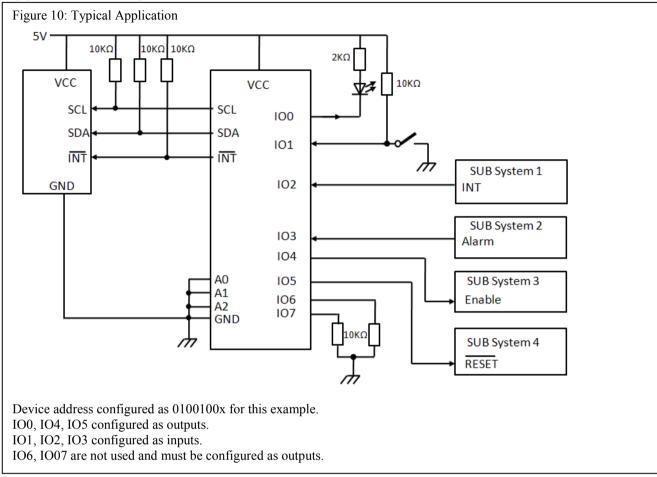

The PI4IOE5V9554 and PI4IOE5V9554A provide 8 bits of general purpose parallel input/output (GPIO) expansion for I<sup>2</sup>C-bus/SMBus applications. The device includes features such as higher driving capability, 5V tolerance, lower power supply, individual I/O configuration, and smaller packaging. It provides a simple solution when additional I/O is required for ACPI power switches, sensors, push buttons, LEDs, fans, etc.

The PI4IOE5V9554/PI4IOE5V9554A consists of an 8-bit register to configure the I/Os as either inputs or outputs and an 8-bit polarity register to change the polarity of the input port register data. The data for each input or output is kept in the corresponding input port or output port register. All registers can be read by the system master.

The PI4IOE5V9554/PI4IOE5V9554A open-drain interrupt output is activated and indicates to the system when any input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine.

Three hardware pins (A0, A1, A2) vary the fixed I<sup>2</sup>C-bus address and allow up to eight devices to share the same I<sup>2</sup>C-bus/SMBus. The PI4IOE5V9554A is identical to the PI4IOE5V9554 except the fixed I<sup>2</sup>C-bus address is different, allowing up to sixteen of these devices (eight of each) on the same I<sup>2</sup>C-bus/SMBus.

# **Pin Configuration**

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.</li>

PI4IOE5V9554/ PI4IOE5V9554A Document Number DS40769 Rev 3 - 2

A Product Line of Diodes Incorporated

# **Pin Description** Table 1: Pin Description

| Pin     |        | Nama | <b>T</b> 0 | Description                   |  |  |  |

|---------|--------|------|------------|-------------------------------|--|--|--|

| TSSOP16 | TQFN16 | Name | Туре       | Description                   |  |  |  |

| 1       | 15     | A0   | Ι          | Address Input 0               |  |  |  |

| 2       | 16     | A1   | Ι          | Address Input 1               |  |  |  |

| 3       | 1      | A2   | Ι          | Address Input 2               |  |  |  |

| 4       | 2      | IO0  | I/O        | Input/Output 0                |  |  |  |

| 5       | 3      | IO1  | I/O        | Input/Output 1                |  |  |  |

| 6       | 4      | IO2  | I/O        | Input/Output 2                |  |  |  |

| 7       | 5      | IO3  | I/O        | Input/Output 3                |  |  |  |

| 8       | 6      | GND  | G          | Supply Ground                 |  |  |  |

| 9       | 7      | IO4  | I/O        | Input/Output 4                |  |  |  |

| 10      | 8      | IO5  | I/O        | Input/Output 5                |  |  |  |

| 11      | 9      | IO6  | I/O        | Input/Output 6                |  |  |  |

| 12      | 10     | IO7  | I/O        | Input/Output 7                |  |  |  |

| 13      | 11     | INT  | 0          | Interrupt Output (Open Drain) |  |  |  |

| 14      | 12     | SCL  | Ι          | Serial Clock Line             |  |  |  |

| 15      | 13     | SDA  | Ι          | Serial Data Line              |  |  |  |

| 16      | 14     | VCC  | Р          | Supply Voltage                |  |  |  |

\* I = Input; O = Output; P = Power; G = Ground

# **Maximum Ratings**

| Power Supply                          | 0.5V to +6.0V         |

|---------------------------------------|-----------------------|

| Voltage on I/O pin                    | GND-0.5V to +6.0V     |

| Input Current                         | ±20mA                 |

| Output Current on an I/O pin          |                       |

| Supply Current                        | ±160mA                |

| Ground Supply Current                 |                       |

| Total Power Dissipation               |                       |

| Operation Temperature                 | 40°C ~ $85^{\circ}$ C |

| Storage Temperature                   | 65°C ~ 150°C          |

| Maximum Junction Temperature, Tj(max) |                       |

|                                       |                       |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Static Characteristics**

VCC = 2.3V to 5.5V; GND = 0 V; Tamb=  $-40^{\circ}$ C to  $+85^{\circ}$ C; unless otherwise specified.

| Table 2: Static Characteristics |  |

|---------------------------------|--|

|---------------------------------|--|

| Symbol           | Parameter                             | Conditions                                                                       | Min.      | Тур. | Max.    | Unit |

|------------------|---------------------------------------|----------------------------------------------------------------------------------|-----------|------|---------|------|

| Power Sup        | ply                                   |                                                                                  | · · · · · |      |         |      |

| V <sub>CC</sub>  | Supply Voltage                        | —                                                                                | 2.3       |      | 5.5     | V    |

|                  |                                       | Operating mode<br>VCC = 5.5V<br>No load<br>fSCL = 400kHz                         | _         | 40   | 60      | μΑ   |

| I <sub>CC</sub>  | I <sub>CC</sub> Supply Current        | Operating mode<br>VCC = 2.3V<br>No load<br>fSCL = 400kHz                         | _         | 10   | 20      | μΑ   |

| Ţ                |                                       | Standby mode<br>VCC = 5.5V<br>No load<br>VI = GND<br>fSCL = 0kHz<br>I/O = inputs | _         | 500  | 700     | μΑ   |

| I <sub>stb</sub> | Standby Current                       | Standby mode<br>VCC = 5.5V<br>No load<br>VI = VCC<br>fSCL = 0kHz<br>I/O = inputs | _         | 0.25 | 1       | μΑ   |

| V <sub>POR</sub> | Power-on Reset Voltage <sup>[1]</sup> |                                                                                  |           | 1.16 | 1.41    | V    |

| nput SCL         | , Input/Output SDA                    | •                                                                                | I         |      |         |      |

| V <sub>IL</sub>  | Low Level Input Voltage               | —                                                                                | -0.5      |      | +0.3VCC | V    |

| $V_{IH}$         | High Level Input Voltage              | —                                                                                | 0.7VCC    |      | 5.5     | V    |

| I <sub>OL</sub>  | Low Level Output Current              | V <sub>OL</sub> =0.4V; VCC=2.3V                                                  | 3         | 6    |         | mA   |

| IL               | Leakage Current                       | $V_{I} = VCC \text{ or } GND$                                                    | -1        |      | 1       | μΑ   |

| Ci               | Input Capacitance                     | $V_I = GND$                                                                      |           | 6    | 10      | pF   |

A Product Line of Diodes Incorporated

Symbol Parameter Conditions Min. Typ. Max. Unit I/Os Low Level Input Voltage V VIL -0.5 +0.81VIH High Level Input Voltage +1.85.5 V  $VCC = 2.3V; V_{OL} = 0.5V^{[2]}$ 8 10 mA  $VCC = 2.3V; V_{OL} = 0.7V^{[2]}$ 10 13 mA  $VCC = 3.0V; V_{OL} = 0.5V^{[2]}$ 8 14 \_\_\_\_ mA Low Level Output Current IOL  $VCC = 3.0V; V_{OL} = 0.7V^{[2]}$ 10 19 mA  $VCC = 4.5V; V_{OL} = 0.5V^{[2]}$ 17 8 mA  $VCC = 4.5V; V_{OL} = 0.7V^{2}$ 10 24 mA \_\_\_\_  $I_{OH} = -8 mA; VCC = 2.3 V^{[3]}$ V 1.8 \_\_\_\_  $I_{OH} = -10 \text{mA}; \text{VCC} = 2.3 \text{V}^{[3]}$ V 1.7  $I_{OH} = -8 \text{mA}; \text{VCC} = 3.0 \text{V}^{[3]}$ V 2.6 VOH High Level Output Current  $I_{OH} = -10 \text{mA}; \text{VCC} = 3.0 \text{V}^{[3]}$ 2.5 V  $I_{OH} = -8mA; VCC = 4.5V^{[3]}$ V 4.1  $I_{OH} = -10 \text{mA}; \text{VCC} = 4.5 \text{V}^{[3]}$ V 4.0 \_\_\_\_ \_\_\_\_ Low Level Input Leakage  $VCC = 3.6V; V_I = VCC$ -1 1  $I_{LI}$ μΑ Current Leakage Current  $VCC = 5.5V; V_I = GND$ -100  $I_{\rm L}$ μA 10  $C_i$ Input Capacitance 3.7 pF \_\_\_\_\_ Co 3.7 10 pF **Output Capacitance** \_\_\_\_ Interrupt INT Low Level Output Current  $V_{OL} = 0.4V$ 3 mA  $I_{OL}$ \_\_\_\_ \_\_\_\_ Select Inputs A0, A1, A2  $V_{IL}$ Low Level Input Voltage -0.5 +0.81V  $V_{IH}$ High Level Input Voltage +1.85.5 V  $I_{\rm L}$ Input Leakage Current -1 1 μA

Note:

1. VCC must be lowered to 0.2V for at least 20µs in order to reset part.

2. Each I/O must be limited to a maximum current of 25mA and the device must be limited to a maximum current of 100mA.

3. The total current sourced by all I/Os must be limited to 85mA.

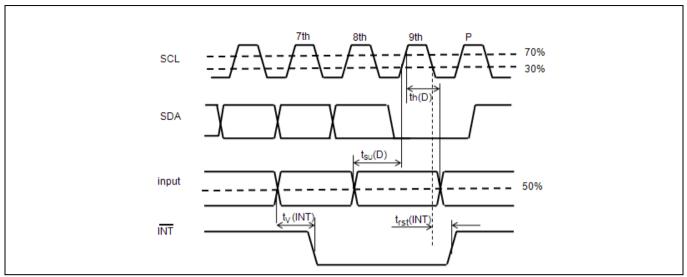

**Dynamic Characteristics** Table 3: Dynamic Characteristics

| Symbol                             | Parameter                                                            | Test Conditions |     | dard<br>e I <sup>2</sup> C | Fast M | Unit |     |

|------------------------------------|----------------------------------------------------------------------|-----------------|-----|----------------------------|--------|------|-----|

|                                    |                                                                      |                 | Min | Max                        | Min    | Max  |     |

| $\mathbf{f}_{\text{SCL}}$          | SCL Clock Frequency                                                  | —               | 0   | 100                        | 0      | 400  | kHz |

| t <sub>BUF</sub>                   | Bus Free Time Between a STOP and START Condition                     | _               | 4.7 |                            | 1.3    |      | μs  |

| t <sub>HD;STA</sub>                | Hold Time (Repeated) START<br>Condition                              | _               | 4.0 |                            | 0.6    | _    | μs  |

| t <sub>SU;STA</sub>                | Setup Time for a Repeated START<br>Condition                         | _               | 4.7 |                            | 0.6    | _    | μs  |

| t <sub>SU;STO</sub>                | Setup Time for STOP Condition                                        | —               | 4.0 |                            | 0.6    | _    | μs  |

| t <sub>VD;ACK</sub> <sup>[1]</sup> | Data Valid Acknowledge Time                                          | —               |     | 3.45                       |        | 0.9  | μs  |

| $t_{\rm HD;DAT}^{[2]}$             | Data Hold Time                                                       | —               | 0   |                            | 0      | _    | ns  |

| t <sub>VD;DAT</sub>                | Data Valid Time                                                      | —               | _   | 3.45                       |        | 0.9  | μs  |

| t <sub>SU;DAT</sub>                | Data Setup Time                                                      | —               | 250 | _                          | 100    |      | ns  |

| $t_{\text{LOW}}$                   | LOW Period of the SCL Clock                                          | —               | 4.7 | _                          | 1.3    |      | μs  |

| t <sub>HIGH</sub>                  | HIGH Period of the SCL Clock                                         | —               | 4.0 | _                          | 0.6    |      | μs  |

| $t_{\rm f}$                        | Fall Time of Both SDA and SCL<br>Signals                             | _               |     | 300                        |        | 300  | ns  |

| t <sub>r</sub>                     | Rise Time of Both SDA and SCL<br>Signals                             |                 |     | 1000                       | _      | 300  | ns  |

| t <sub>SP</sub>                    | Pulse Width of Spikes that must be<br>Suppressed by the Input Filter |                 |     | 50                         |        | 50   | ns  |

| Port Timin                         | Ig                                                                   |                 |     |                            |        |      |     |

| $t_{v(Q)}$                         | Data Output Valid Time <sup>[3]</sup>                                | —               | —   | 200                        |        | 200  | ns  |

| t <sub>su(D)</sub>                 | Data Input Setup Time                                                | —               | 100 |                            | 100    |      | ns  |

| t <sub>h(D)</sub>                  | Data Input Hold Time                                                 | —               | 1   |                            | 1      |      | μs  |

| Interrupt 7                        | Fiming                                                               |                 |     |                            |        |      |     |

| t <sub>v(INT)</sub>                | Valid Time on pin INT                                                | —               |     | 4                          |        | 4    | μs  |

| $t_{rec(INT)}$                     | Reset Time on pin INT                                                | —               |     | 4                          |        | 4    | μs  |

Note:

1.  $t_{VD;ACK}$  = time for acknowledgement signal from SCL LOW to SDA (out) LOW. 2.  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW. 3.  $t_{v(Q)}$  measured from 0.7VCC on SCL to 50% I/O output.

Figure 3: Timing Parameters for INT Signal

# **Details Description**

# a. Device Address

Following a START condition, the bus master must output the address of the slave it is accessing. The address of the PI4IOE5V9554/54A is shown below. To conserve power, no internal pullup resistors are incorporated on the hardware selectable address pins, and they must be pulled HIGH or LOW.

Table 4: Device Address Byte

| acte il Bellee ilaai | •00 ± j •• |    |    |    |    |    |    |     |

|----------------------|------------|----|----|----|----|----|----|-----|

|                      | b7(MSB)    | b6 | b5 | b4 | b3 | b2 | b1 | b0  |

| PI4IOE5V9554         | 0          | 1  | 0  | 0  | A2 | A1 | A0 | R/W |

| PI4IOE5V9554A        | 0          | 1  | 1  | 1  | A2 | A1 | A0 | R/W |

| NT ( D 1((1)) I      | T : ((0))  |    |    |    |    |    |    |     |

Note: Read "1", Write "0"

### **b.** Register Description

#### i. Command Byte

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers are written or read.

| Table 5 <sup>.</sup> | Command Byte |  |

|----------------------|--------------|--|

| 1 4010 5.            | Command Dyte |  |

| Command | Protocol        | Function                    |

|---------|-----------------|-----------------------------|

| 0       | Read Byte       | Input port register         |

| 1       | Read/Write Byte | Output port register        |

| 2       | Read/Write Byte | Polarity Inversion register |

| 3       | Read/Write Byte | Configuration register      |

#### ii. Register 0: Input Port Register

This register is a read-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

The default 'X' is determined by the externally applied logic level, which is normally '1' when no external signal externally applied because of the internal pullup resistors.

Table 6: Input Port Register

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|--------|----|----|----|----|----|----|----|----|

| Symbol | Ι7 | I6 | 15 | I4 | I3 | I2 | I1 | 10 |

#### iii. Register 1: Output Port Register

This register reflects the outgoing logic levels of the pins defined as outputs by Register 3.Bit values in this register have no effect on pins defined as inputs. Reads from this register return the value that is in the flip-flop controlling the output selection—**not** the actual pin value.

Table 7: Output Port Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | 07 | 06 | 05 | O4 | 03 | 02 | 01 | O0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### iv. Register 2: Polarity Inversion Register

This register allows the user to invert the polarity of the input port register data. If a bit in this register is set (written with '1'), the corresponding input port data is inverted. If a bit in this register is cleared (written with a '0'), the input port data polarity is retained.

Table 8: Polarity Inversion Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0 |

| Default | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### v. Register 3: Configuration Register

This register configures the directions of the I/O pins. If a bit in this register is set, the corresponding port pin is enabled as an input with high-impedance output driver. If a bit in this register is cleared, the corresponding port pin is enabled as an output. At reset, the I/Os are configured as inputs with a weak pullup to VCC.

Table 9: Configuration Register

| Bit     | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|---------|----|----|----|----|----|----|----|----|

| Symbol  | C7 | C6 | C5 | C4 | C3 | C2 | C1 | C0 |

| Default | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

#### **Power-on Reset**

When power is applied to VCC, an internal power-on reset (POR) holds thePI4IOE5V9554/PI4IOE5V9554A in a reset condition until VCC has reached VPOR. At that point, the reset condition is released and thePI4IOE5V9554/PI4IOE5V9554A registers and state machine initialize to their default states. Thereafter, VCC must be lowered below 0.2 V to reset the device.

For a power reset cycle, VCC must be lowered below 0.2 V and then restored to the operating voltage.

#### c. Interrupt Output

The open-drain interrupt output is activated when one of the port pins change state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the input port register is read.

Note that changing an I/O from and output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the input port register.

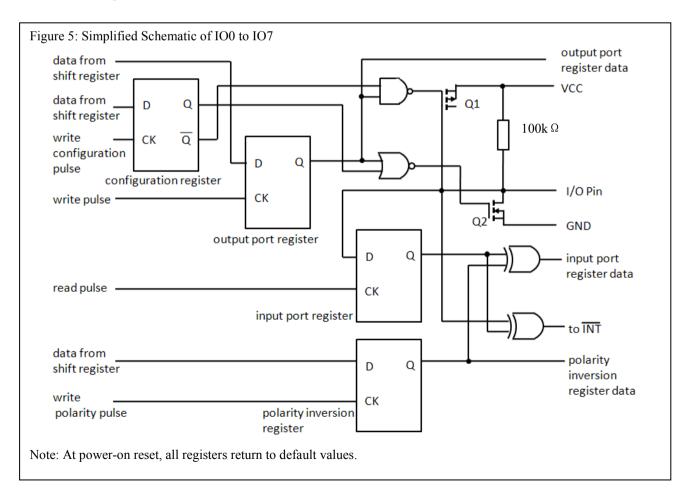

### d. I/O Port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high-impedance input with a weak pullup (100 k $\Omega$  typ.) to VCC. The input voltage may be raised above VCC to a maximum of 5.5V.

If the I/O is configured as an output, then either Q1 or Q2 is enabled, depending on the state of the output port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance paths that exist between the pin and either VCC or GND.

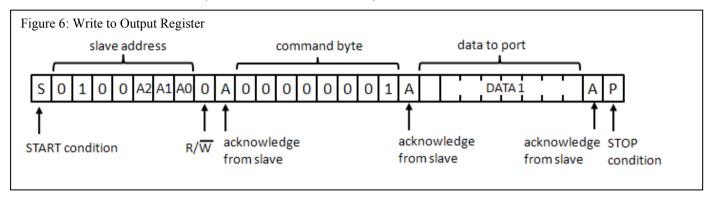

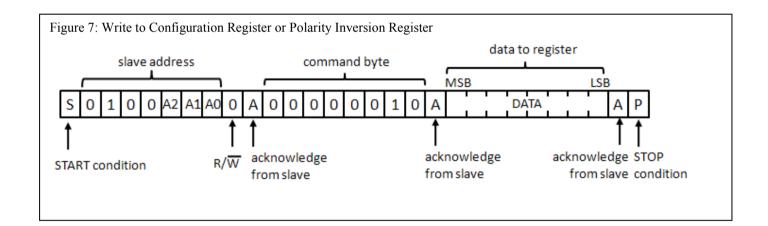

# e. Bus Transaction

Data is transmitted to the PI4IOE5V9554/PI4IOE5V9554A registers using the write mode as shown in Figure 6 and Figure 7.

These devices do not implement an auto-increment function, so once a command byte has been sent, the register which was addressed continues to be accessed by reads until a new command byte is sent.

Figure 8: Read from Register slave address command byte 0 0 Δ2 cont.... O Δ Δ S 0 1 acknowledge acknowledge START condition R/W from slave from slave data to register data to register slave address MSB LSB MSB LSB DATA first byte DATA last byte ...cont Ρ S 0 0 C Δ0 1 А 1 acknowledge no acknowledge STOP acknowledge START condition R/W from slave from master from master condition Figure 9: Read Input Port Register slave address Data from port Data from port 5 3 2 3 6 4 1 0 6 5 2 1 Δ0 1 7 Δ 0 cont.... 1 acknowledge R/W acknowledge acknowledge START condition from mater from slave from mater Data from port Data from port 5 3 2 0 6 5 4 3 2 0 ....cont 6 acknowledge no acknowledge STOP from mater from mater condition This figure assumes the command byte has previously been programmed with 00h. Transfer of data can be stopped at any moment by a STOP condition.

Data is read from the PI4IOE5V9554/PI4IOE5V9554A registers using the read mode as shown in Figure 8 and Figure 9.

# **Application Design-in Information**

A Product Line of Diodes Incorporated

# Part Marking PI4IOE5V9554

L Package

Z: Die Rev Y: Year W: Workweek 1st X: Assembly Site Code 2nd X: Fab Site Code

#### PI4IOE5V9554A

L Package

Z: Die Rev Y: Year W: Workweek 1st X: Assembly Site Code 2nd X: Fab Site Code ZH Package

tSZHE \*YWXX Ο

\*: Die Rev Y: Date Code (Year) W: Date Code (Workweek) 1st X: Assembly Site Code 2nd X: Wafer Fab Site Code

A Product Line of Diodes Incorporated

# **Packaging Mechanical**

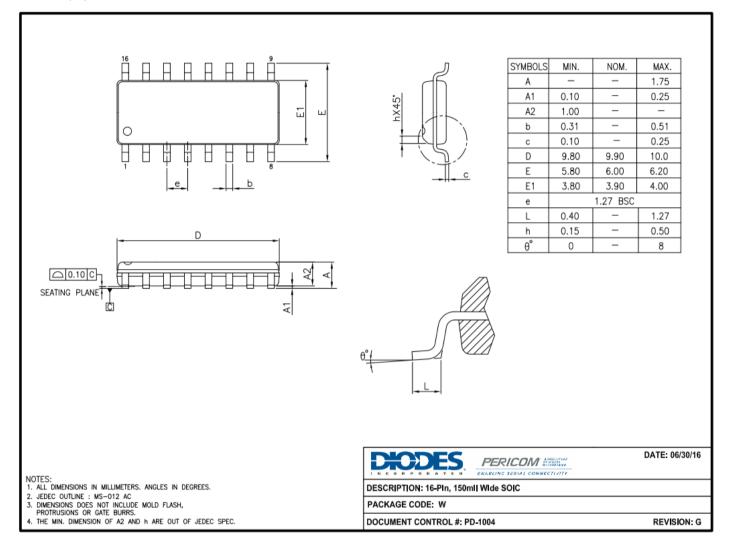

SOIC-16(W)

A Product Line of Diodes Incorporated

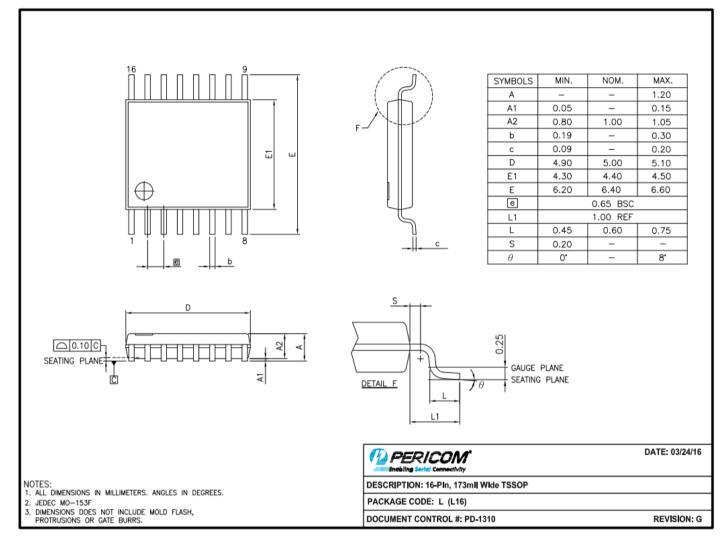

#### TSSOP-16(L)

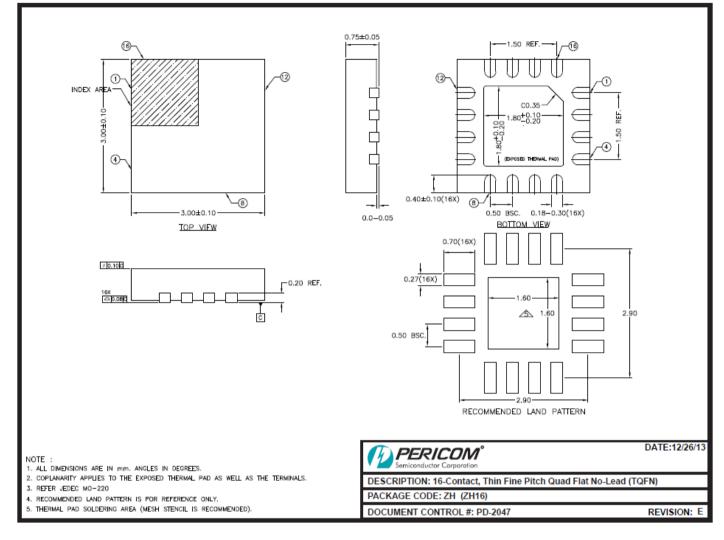

#### TQFN 3x3-16(ZH)

For latest package information:

$See \ http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/.interval \ the support \ the sup$

### **Ordering Information**

| Part Numbers     | Package Code | Package Description                                          |

|------------------|--------------|--------------------------------------------------------------|

| PI4IOE5V9554LEX  | L            | 16-pin, 173 mil Wide (TSSOP)                                 |

| PI4IOE5V9554ALEX | L            | 16-pin, 173 mil Wide (TSSOP)                                 |

| PI4IOE5V9554ZHEX | ZH           | 16-contact, Thin Fine Pitch Quad Flat No-Lead (TQFN) 3.0×3.0 |

Notes:

1. 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

PI4IOE5V9554/9554A

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated www.diodes.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Diodes Incorporated: PI4IOE5V9554LEX PI4IOE5V9554ALEX PI4IOE5V9554ZHEX